June 2007

# FAN50FC3 — 8-Bit Programmable, 2- to 3-Phase FastvCore™ Buck Controller

#### **Features**

- FastvCore<sup>™</sup> nonlinear control for fast transient and to minimizes the number of output caps required

- Selectable 2- or 3-phase operation at up to 1MHz per phase

- ±7.7mV worst-case differential sensing error over temperature

- Active current balancing between output phases

- Power Good and Crowbar blanking supports on-the-fly VID code changes

- 0.5V to 1.6V output

- Usable for Intel<sup>®</sup> VR10 and VR11 designs

- Selectable VR10 extended (7-bit) and VR11 (8-bit) VID tables

- Programmable soft-start ramp

- Programmable short-circuit protection and latch-off delay

## **Applications**

- Desktop PC/Server processor power supplies for existing and next-generation Intel<sup>®</sup> processors

- VRM modules

## **Related Applications Notes**

AN-6052 — Instructions for the Multi-Phase VR11 MathCad® Design Tool

## Description

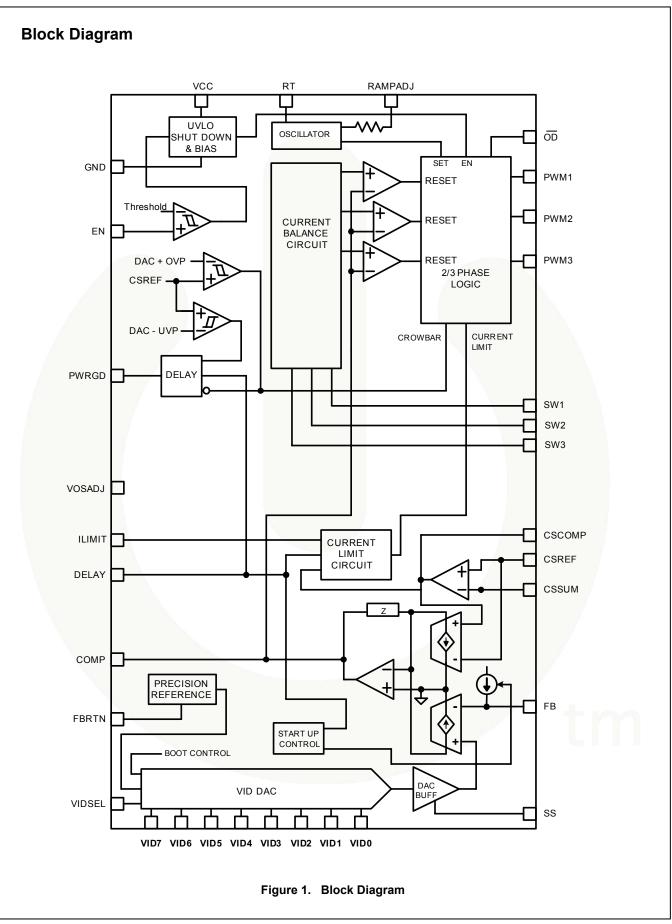

The FAN50FC3 device is a multi-phase buck switching regulator controller optimized to convert a 12V input supply to the processor core voltage required by high-performance Intel® processors. It has an internal, 8-bit DAC that converts a digital voltage identification (VID) code sent from the processor, to set the output voltage between 0.5V and 1.6V in 6.25mV steps. It outputs PWM signals to external MOSFET drivers that drive the switching power MOSFETs. The switching frequency of the design is programmable by a single resistor value and the number of phases can be programmed to support 2- or 3-phase applications.

The FAN50FC3 also includes programmable no-load offset and droop functions to adjust the output voltage as a function of the load current, as required by the Intel<sup>®</sup> specifications. The FAN50FC3 also provides an accurate and reliable short-circuit protection function with an adjustable over-current set point.

FastvCore<sup>™</sup> technology greatly improves the fast transient response required by today's high-performance processors. This allows fewer output capacitors to be used in the application.

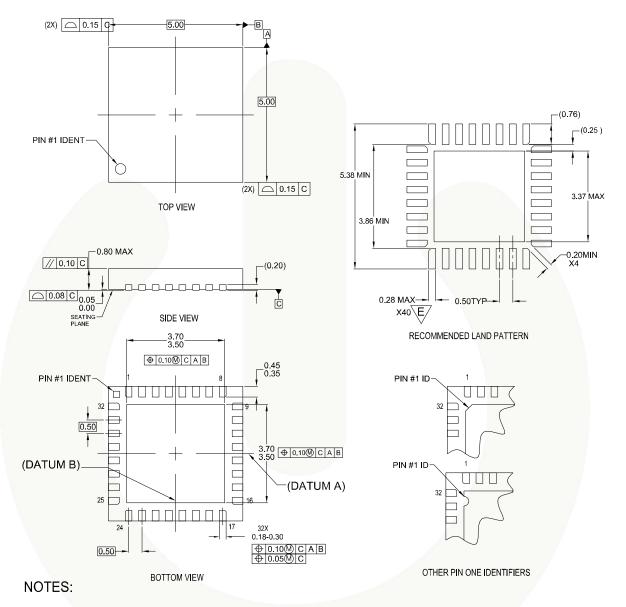

The FAN50FC3 is specified over the commercial temperature range of 0°C to +85°C and is available in a 32-lead MLP package.

## **Ordering Information**

| Part Number | Pb-Free | Operating<br>Temperature Range | Package                                   | Packing Method |

|-------------|---------|--------------------------------|-------------------------------------------|----------------|

| FAN50FC3MPX | Yes     | 0 to 85°C                      | 32-Lead, Molded Leadless<br>Package (MLP) | Tape and Reel  |

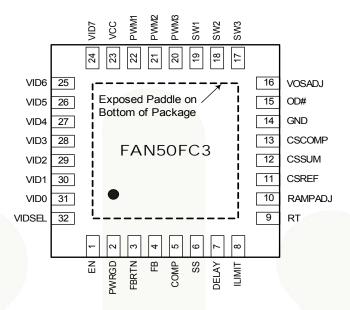

## **Pin Assignments**

Figure 2. Pin Assignments

## **Pin Definitions**

| Pin# | Name    | Description                                                                                                                                                                                                       |

|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | EN      | <b>Power Supply Enable Input</b> . Analog comparator input with hysteresis. If the input voltage is higher than the internal threshold, the controller is enabled; if lower, the controller is disabled.          |

| 2    | PWRGD   | <b>Power Good Output</b> . Open-drain output that pulls to GND when the output voltage is outside the proper operating range.                                                                                     |

| 3    | FBRTN   | <b>Feedback Return</b> . VID DAC and error amplifier reference for remote sensing output voltage.                                                                                                                 |

| 4    | FB      | <b>Feedback Input</b> . Error amplifier input for remote sensing output voltage. A positive internal current source is connected to this pin to allow the output voltage to be offset lower than the DAC voltage. |

| 5    | COMP    | Error Amplifier Output. For loop compensation.                                                                                                                                                                    |

| 6    | SS      | <b>Soft-Start Input</b> . An external capacitor connected between this pin and GND sets the soft-start ramp-up time.                                                                                              |

| 7    | DELAY   | <b>Delay Timer Input</b> . An external capacitor connected between this pin and GND sets the over-current latch-off delay time, BOOT voltage hold time, EN delay time, and PWRGD delay time.                      |

| 8    | ILIMIT  | Current Limit Set. An external resistor from this pin to GND sets the current limit threshold of the converter.                                                                                                   |

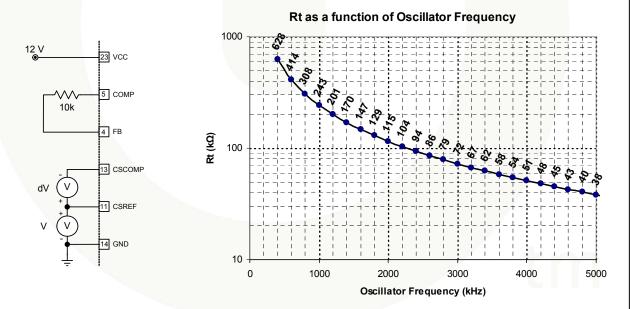

| 9    | RT      | <b>Frequency Set Input</b> . An external resistor connected between this pin and GND sets the oscillator frequency of the device.                                                                                 |

| 10   | RAMPADJ | <b>PWM Ramp Set Input</b> . An external resistor connected between this pin and the converter input voltage sets the internal PWM ramp.                                                                           |

| 11   | CSREF   | Current-Sense Amplifier Positive Input. The voltage on this pin is used as the reference for the current-sense amplifier. The Power Good and Crowbar functions are internally connected to this pin.              |

| 12   | CSSUM   | Current-Sense Amplifier Negative Input.                                                                                                                                                                           |

| 13   | CSCOMP  | Current-Sense Amplifier Compensation Output.                                                                                                                                                                      |

## Pin Definitions (Continued)

| GND             | <b>Ground</b> . Biasing and logic output signals of the device are referenced to this ground.                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OD#             | Output Disable. This pin is actively pulled LOW when the EN input is low or when $V_{\rm CC}$ is below the UVLO threshold, to disable the external MOSFET drivers.                                                                         |

| VOSADJ          | FastvCore™ Vos Adjustment Input. This signal is used as a control input for the FastvCore™ circuit.                                                                                                                                        |

| SW3 to<br>SW1   | <b>Switching Node Current Balance Inputs</b> . Sense the switching side of the inductor and used to measure the current level in each phase. The SW pins of unused phases should be left open.                                             |

| PWM3 to<br>PWM1 | <b>PWM Outputs</b> . Each output is connected to the input of an external MOSFET driver, such as the FAN5109. Connecting the PWM3 output to V <sub>CC</sub> disables that phase, allowing the FAN50FC3 to operate as a 2-phase controller. |

| VCC             | Supply Voltage.                                                                                                                                                                                                                            |

| VID7 to<br>VID0 | Voltage Identification Code Inputs. These digital inputs are connected to the internal DAC and used to program the output voltage. These pins have 1µA internal pull-down; if they are left open, the input state is decoded as logic LOW. |

| VIDSEL          | VID Table Select Input. A logic LOW selects the extended VR10 DAC table and a logic HIGH selects the VR11 DAC table. This pin has a 1μA internal pull-down; if left open, the input state is decoded as logic LOW.                         |

| Exposed Paddle  | Internally Connected to Die Ground. May be connected to ground or left floating. Connect to ground for lowest package thermal resistance.                                                                                                  |

|                 | OD#  VOSADJ  SW3 to SW1  PWM3 to PWM1  VCC  VID7 to VID0  VIDSEL  Exposed                                                                                                                                                                  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                              | Min. | Max.                 | Unit |

|------------------|--------------------------------------------------------|------|----------------------|------|

|                  | Supply Voltage, VCC                                    | -0.3 | +15                  | V    |

|                  | FBRTN                                                  | -0.3 | +0.3                 | V    |

|                  | RAMPADJ, PWM3                                          | -0.3 | V <sub>CC</sub> +0.3 | V    |

|                  | SW1 – SW3                                              | -10  | +25                  | V    |

|                  | All Other Inputs and Outputs                           | -0.3 | +5.5                 | V    |

| TJ               | Operating Junction Temperature                         | 0    | +125                 | °C   |

| T <sub>STG</sub> | Storage Temperature                                    | -65  | +150                 | °C   |

| T <sub>LS</sub>  | Lead Soldering Temperature (10 Seconds)                |      | 300                  | °C   |

| T <sub>LI</sub>  | Lead Infrared Temperature (15 Seconds)                 |      | 260                  | °C   |

| $\theta_{JA}$    | Thermal Resistance, Junction-to-Ambient <sup>(1)</sup> |      | 45                   | °C/W |

#### Note

Junction-to-ambient thermal resistance, θ<sub>JA</sub>, is a strong function of PCB material, board thickness, thickness and number of copper planes, number of via used, diameter of via used, available copper surface, and attached heat sink characteristics.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-----------------|---------------------|------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage      | VCC to GND | 9.6  | 12.0 | 14.4 | V    |

| T <sub>A</sub>  | Ambient Temperature |            | 0    | 9/6. | +85  | °C   |

### **Electrical Characteristics**

$V_{CC}$  = 12V, FBRTN = GND, and  $T_A$  = +25°C. The • denotes specifications which apply over the full operating temperature range.

| Symbol                   | Parameter                            | Conditions                                                                         |                                                | Min.  | Тур.     | Max.  | Unit |

|--------------------------|--------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------|-------|----------|-------|------|

| Error Am                 | plifier                              |                                                                                    | <u>                                       </u> |       | I.       | I.    |      |

| $V_{COMP}$               | Output Voltage Range                 |                                                                                    | •                                              | 0.5   |          | 4.0   | V    |

| $V_{FB}$                 | Accuracy                             | Relative to nominal DAC output, referenced to FBRTN. (see Figure 3)                | •                                              | -7.7  |          | +7.7  | mV   |

| $V_{FB(BOOT)}$           | Accuracy                             | VRM11 VID Range: 1.00625V to 1.60000V During Start-up                              | •                                              | 1.092 | 1.100    | 1.108 | V    |

|                          | Load Line Droop Accuracy             | CSREF-CSCOMP= 80mV (see Figure 5)                                                  | •                                              | -78   | -80      | -82   | mV   |

|                          | Differential Non-Linearity           |                                                                                    | •                                              | -1    |          | +1    | LSE  |

| $\Delta V_FB$            | Line Regulation                      | V <sub>CC</sub> =10V to 14V                                                        |                                                |       | 0.05     |       | %    |

| I <sub>FB</sub>          | Input Bias Current                   |                                                                                    | •                                              | 13.5  | 15       | 16.5  | μA   |

| I <sub>FBRTN</sub>       | FBRTN Current                        |                                                                                    | •                                              |       | 70       | 95    | μΑ   |

| I <sub>O(ERR)</sub>      | Output Current                       | FB forced to V <sub>OUT</sub> -3%                                                  |                                                |       | 500      |       | μA   |

| GBW <sub>(ERR)</sub>     | Gain Bandwidth Product               | COMP = FB <sup>(3)</sup>                                                           |                                                |       | 20       |       | MHz  |

| ,                        | Slew Rate                            | $COMP = FB^{(3)}$                                                                  |                                                |       | 25       |       | V/µs |

| V <sub>CSCOMP</sub>      | CSCOMP Voltage Range                 | Relative to CSREF                                                                  | •                                              | -250  |          | +250  | mV   |

| t <sub>BOOT</sub>        | BOOT Voltage Hold Time               | C <sub>DELAY</sub> = 10nF                                                          |                                                |       | 2        |       | ms   |

|                          | s and VIDSEL                         |                                                                                    | <u>                                       </u> |       | <u>I</u> |       |      |

| V <sub>IL(VID)</sub>     | Input Low Voltage                    | VIDx, VIDSEL                                                                       | •                                              |       |          | 0.4   | V    |

| V <sub>IH(VID)</sub>     | Input High Voltage                   | VIDx, VIDSEL                                                                       | •                                              | 0.8   |          | 3.3   | V    |

| V <sub>IL(VID)</sub>     | Select VR10 Table                    | VIDSEL Logic LOW                                                                   |                                                |       |          | 0.4   | ٧    |

| V <sub>IH(VID)</sub>     | Select VR11 Table                    | VIDSEL Logic HIGH                                                                  |                                                | 0.8   |          | 3.3   | ٧    |

| I <sub>IN(VID)</sub>     | Input Current, VID Low               |                                                                                    |                                                |       | -1       |       | μA   |

| t <sub>DLY(VID)</sub>    | VID Transition Delay Time            | VID code change to FB change <sup>(3)</sup>                                        | •                                              | 200   |          |       | ns   |

| t <sub>DLY(CPU)</sub>    | No CPU Detection Turn-off Delay Time | VID code change to off state to PWM going LOW <sup>(3)</sup>                       | •                                              | 200   |          |       | ns   |

| Oscillato                |                                      |                                                                                    | <u> </u>                                       |       |          |       |      |

| f <sub>OSC</sub>         | Frequency                            |                                                                                    | •                                              | 0.25  |          | 4.50  | MHz  |

| f <sub>PHASE</sub>       | Frequency Variation                  | $T_A = 25C, R_T = 200K, 3-phase$                                                   |                                                | -20%  | 400      | 20%   | kHz  |

| V <sub>RT</sub>          | Output Voltage                       | $R_T = 100 k\Omega$ to GND                                                         | •                                              | 1.9   | 2.0      | 2.1   | ٧    |

| V <sub>RAMPADJ</sub>     | RAMPADJ Output Voltage               | $V_{RAMPADJ} = V_{DAC} + 2k\Omega * (V_{CC} - V_{DAC}) / (R_{RAMPADJ} + 2k\Omega)$ | •                                              | -50   |          | +50   | mV   |

| I <sub>RAMPADJ</sub>     | RAMPADJ Input Current<br>Range       |                                                                                    |                                                | 1     |          | 50    | μA   |

| Current-S                | Sense Amplifier                      |                                                                                    | •                                              |       |          |       |      |

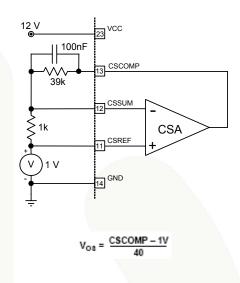

| V <sub>OS(CSA)</sub>     | Offset Voltage                       | CSSUM – CSREF (see Figure 4)                                                       | •                                              | -1.0  |          | +1.0  | mV   |

| I <sub>BIAS(CSSUM)</sub> | Input Bias Current (for CSSUM)       |                                                                                    | •                                              | -50   |          | +50   | nA   |

| I <sub>BIAS(CSREF)</sub> | Input Current (for CSREF)            | Current drawn by CSREF Pin                                                         | •                                              | -3    |          | +3    | μA   |

| GBW <sub>(CSA)</sub>     | Gain Bandwidth Product               | CSSUM = CSCOMP <sup>(3)</sup>                                                      |                                                |       | 10       |       | MHz  |

| ()                       | Slew Rate                            | $C_{CSCOMP} = 10pF^{(3)}$                                                          |                                                |       | 10       |       | V/µs |

| V <sub>CSACM</sub>       | Input Common-Mode Range              | CSSUM and CSREF                                                                    | •                                              | 0     |          | 3.2   | V    |

## **Electrical Characteristics** (Continued)

$V_{CC}$  = 12V, FBRTN = GND, and  $T_A$  = +25°C. The • denotes specifications which apply over the full operating temperature range.

| Symbol                 | Parameter Conditions                   |                                                                           |   | Min. | Тур. | Max. | Unit  |

|------------------------|----------------------------------------|---------------------------------------------------------------------------|---|------|------|------|-------|

| Current-Sens           | e Amplifier (Continued)                |                                                                           |   |      |      |      | ul    |

|                        | Output Voltage Range                   |                                                                           | • | 0.05 |      | 3.20 | V     |

| I <sub>CSCOMP</sub>    | Output Current                         |                                                                           |   |      | 1    |      | mA    |

| Current Balar          | nce Circuit                            |                                                                           |   |      |      |      |       |

| $V_{SW(x)CM}$          | Common Mode Range <sup>(3)</sup>       |                                                                           | • | -600 |      | +200 | mV    |

| R <sub>SW(x)</sub>     | Input Resistance                       | SW(x) = 0V                                                                | • | 35   | 50   | 65   | kΩ    |

| I <sub>SW(x)</sub>     | Input Current                          | SW(x) = 0V                                                                | • | 1.6  | 3.3  | 5.0  | μA    |

| $\Delta I_{SW(x)}$     | Input Current Matching                 | SW(x) = 0V                                                                | • | -5   |      | +5   | %     |

| <b>Current Limit</b>   | Comparator                             |                                                                           |   |      |      |      | l     |

| V <sub>ILIMIT</sub>    | Output Voltage                         | R <sub>ILIMT</sub> = 143kΩ                                                | • | 1.6  | 1.7  | 1.8  | V     |

| I <sub>ILIMIT</sub>    | Output Current                         | $R_{ILIMT} = 143k\Omega$                                                  |   |      | 12   |      | μA    |

|                        | Maximum Output Current                 |                                                                           | • | 60   |      |      | μA    |

| V <sub>CL</sub>        | Current Limit Threshold Voltage        | $V_{CSREF} - V_{CSCOMP}$ , $R_{ILIMT} = 143k\Omega$                       | • | 100  | 120  | 140  | mV    |

|                        | Current Limit Setting Ratio            | V <sub>CL</sub> / I <sub>ILIMT</sub>                                      |   |      | 10   |      | mV/μA |

| Delay Timer            |                                        |                                                                           |   |      |      |      | l     |

| I <sub>DELAY</sub>     | Normal Mode Output Current             |                                                                           | • | 12   | 15   | 18   | μA    |

| I <sub>DELAY(CL)</sub> | Output Current in Current Limit        |                                                                           | • | 3.00 | 3.75 | 4.50 | μA    |

| V <sub>DELAY(TH)</sub> | Threshold Voltage                      |                                                                           | • | 1.6  | 1.7  | 1.8  | V     |

| Soft-Start             |                                        |                                                                           |   |      |      |      | l     |

| I <sub>(SS)</sub>      | Output Current                         | During Start-up                                                           | • | 12   | 15   | 18   | μA    |

| Enable Input           |                                        |                                                                           | 1 |      |      |      |       |

| $V_{TH(EN)}$           | Threshold Voltage                      |                                                                           | • | 800  | 850  | 900  | mV    |

| V <sub>HYS(EN)</sub>   | Threshold Hysteresis                   |                                                                           | • | 80   | 100  | 130  | mV    |

| I <sub>IN(EN)</sub>    | Enable Input Current                   |                                                                           |   |      | 1    |      | μA    |

| t <sub>DELAY(EN)</sub> | Turn-On Delay                          | Start-up sequence, EN>950mV, C <sub>DELAY</sub> = 10nF                    |   |      | 2    |      | ms    |

| #OD Output             |                                        |                                                                           |   |      |      |      |       |

| $V_{OL(ODB)}$          | Output Voltage LOW                     | I <sub>PWM(SINK)</sub> = 400μA                                            | • |      | 160  | 400  | mV    |

| V <sub>OH(ODB)</sub>   | Output Voltage HIGH                    | I <sub>PWM(SOURCE)</sub> = 400μA                                          | • | 4    | 5    |      | V     |

| Power-Good             | Comparator                             |                                                                           |   |      |      |      |       |

| $V_{PWRGD(UV)}$        | Under-Voltage Threshold                | Relative to Nominal DAC Output                                            | • | -300 | -250 | -200 | mV    |

| V <sub>PWRGD(OV)</sub> | Over-Voltage Threshold                 | Relative to Nominal DAC Output                                            | • | 100  | 150  | 200  | mV    |

| V <sub>OL(PWRGD)</sub> | Output Low Voltage                     | I <sub>PWRGD(SINK)</sub> = -4mA                                           | • |      | 200  | 300  | mV    |

| t1 <sub>PG(DLY)</sub>  | Power Good Delay Time 1                | Start-up Sequence; C <sub>DELAY</sub> = 10nF;<br>Power Good Blanking Time |   |      | 2    |      | ms    |

| t2 <sub>PG(DLY)</sub>  | Power Good Delay Time 2                | VID Code Changing; C <sub>DELAY</sub> = 10nF;<br>Power Good Blanking Time |   | 100  | 250  |      | μs    |

| t3 <sub>PG(DLY)</sub>  | Power Good Delay Time 3 <sup>(3)</sup> | VID Code Static; C <sub>DELAY</sub> = 10nF;<br>Power Good Blanking Time   | • | 100  | 200  |      | ns    |

## **Electrical Characteristics** (Continued)

$V_{CC}$  = 12V, FBRTN = GND, and  $T_A$  = +25°C. The • denotes specifications which apply over the full operating temperature range.

| Symbol                | Parameter              | Conditions                                                                            |   | Min.              | Тур. | Max. | Unit |

|-----------------------|------------------------|---------------------------------------------------------------------------------------|---|-------------------|------|------|------|

| Power-Good            | Comparator (Continued) | •                                                                                     |   |                   |      |      | I    |

| V <sub>CROWBAR</sub>  | Crowbar Trip Point     | Relative to Nominal DAC Output                                                        | • | 100               | 150  | 200  | mV   |

| V <sub>CR_RST</sub>   | Crowbar Reset Point    | Relative to FBRTN                                                                     | • | 250               | 300  | 350  | mV   |

| t1 <sub>CROWBAR</sub> | Crowbar Delay Time 1   | VID Code Change<br>Over-Voltage to PWM Going LOW<br>Crowbar Blanking Time             | • | 100               | 250  |      | μs   |

| t2 <sub>CROWBAR</sub> | Crowbar Delay Time 2   | VID Code Static<br>Over-Voltage to PWM going LOW<br>Crowbar Blanking Time             | • |                   | 400  |      | ns   |

| PWM Outputs           | 3                      |                                                                                       | • |                   |      |      | •    |

| V <sub>OL(VRTM)</sub> | Output Voltage Low     | $I_{PWM(SINK)} = 400\mu A$                                                            | • |                   | 160  | 400  | mV   |

| V <sub>OH(VRTM)</sub> | Output Voltage High    | I <sub>PWM(SOURCE)</sub> = 400μA                                                      | • | 4                 | 5    |      | V    |

| $V_{DIS}$             | Phase Disable Voltage  | Applicable to PWM3 pins only.<br>Connect this pin to VCC to disable<br>the phase. (4) | • | V <sub>CC</sub> 1 |      |      | V    |

| Input Supply          |                        |                                                                                       | • |                   |      |      | •    |

| I <sub>DC</sub>       | DC Supply Current      | EN = Logic HIGH                                                                       | • |                   | 8    | 12   | mA   |

| $V_{\text{UVLO}}$     | UVLO Threshold         | V <sub>CC</sub> Rising                                                                | • | 6.5               | 6.9  | 7.3  | V    |

| V <sub>UVLO_HYS</sub> | UVLO Hysteresis        |                                                                                       | • | 0.7               | 0.9  | 1.1  | V    |

#### Notes:

- 2. Limits at operating temperature extremes are guaranteed by design, characterization, and statistical quality control.

- 3. AC specifications are guaranteed by design and characterization; not production tested.

- 4. To operate the FAN50FC3 with fewer than three phases, PWM3 should be connected to V<sub>CC</sub> to disable this phase. See the Theory of Operation section for details.

## **Test Diagrams**

Figure 3. Closed-Loop Output Voltage Accuracy

Figure 4. Current-Sense Amplifier Vos

Figure 5. Droop Voltage Accuracy

Figure 6. R<sub>T</sub> Required to Set Oscillator Frequency

Table 1. Output Voltage Programming Codes (extended VR10); 0 = logic LOW; 1 = logic HIGH.

| VID4          | VID3 | VID2 | VID1 | VID0 | VID5 | VID6          | V <sub>OUT</sub> (V) |

|---------------|------|------|------|------|------|---------------|----------------------|

| 1             | 1    | 1    | 1    | 1    | 1    | 0             | OFF                  |

| 1             | 1    | 1    | 1    | 1    | 1    | 1             | OFF                  |

| 1             | 1    | 1    | 1    | 1    | 0    | 0             | OFF                  |

| 1             | 1    | 1    | 1    | 1    | 0    | 1             | OFF                  |

| 1             | 1    | 1    | 1    | 0    | 1    | 0             | 1.09375              |

| 1             | 1    | 1    | 1    | 0    | 1    | 1             | 1.10000              |

| 1             | 1    | 1    | 1    | 0    | 0    | 0             | 1.10625              |

| 1             | 1 1  | 1    | 1    | 0    | 0    | 1             | 1.11250              |

| 1             | 1 1  | 1    | 0    | 1    | 1    | 0             | 1.11230              |

| 1             | 1    | 1    | 0    | 1    | 1    | 1             | 1.12500              |

|               |      |      |      |      |      |               |                      |

| 1             | 1 1  | 1    | 0    | 1    | 0    | 0             | 1.13125              |

| 1             | 1    | 1    | 0    | 1    | 0    | 1             | 1.13750              |

| 1             | 1    | 1    | 0    | 0    | 1    | 0             | 1.14375              |

| 1             | 1    | 1    | 0    | 0    | 1    | 1             | 1.15000              |

| 11            | 11   | 1    | 0    | 0    | 0    | 0             | 1.15625              |

| 1             | 1    | 1    | 0    | 0    | 0    | 1             | 1.16250              |

| 1             | 1    | 0    | 1    | 1    | 1    | 0             | 1.16875              |

| 1             | 1    | 0    | 1    | 1    | 1    | 1             | 1.17500              |

| 1             | 1    | 0    | 1    | 1    | 0    | 0             | 1.18125              |

| 1             | 1    | 0    | 1    | 1    | 0    | 1             | 1.18750              |

| 1             | 1 1  | 0    | 1    | 0    | 1    | 0             | 1.19375              |

| 1             | 1 1  | 0    | 1    | 0    | 1    | 1             | 1.20000              |

| 1             | 1 1  | 0    | 1    | 0    | 0    | 0             | 1.20625              |

| 1             | 1    | 0    | 1    | 0    | 0    | 1             | 1.21250              |

| 1             | 1    | 0    | 0    | 1    | 1    | 0             | 1.21250              |

| 1             | 1    |      |      |      | 1    |               |                      |

| •             |      | 0    | 0    | 1    |      | 1             | 1.22500              |

| 1             | 1    | 0    | 0    | 1    | 0    | 0             | 1.23125              |

| 1             | 1    | 0    | 0    | 1    | 0    | 1             | 1.23750              |

| 1             | 1    | 0    | 0    | 0    | 1    | 0             | 1.24375              |

| 1             | 1    | 0    | 0    | 0    | 1    | 1             | 1.25000              |

| 11            | 1    | 0    | 0    | 0    | 0    | 0             | 1.25625              |

| 1             | 1    | 0    | 0    | 0    | 0    | 1             | 1.26250              |

| 1             | 0    | 1    | 1    | 1    | 1    | 0             | 1.26875              |

| 1             | 0    | 1    | 1    | 1    | 1    | 1             | 1.27500              |

| 1             | 0    | 1    | 1    | 1    | 0    | 0             | 1.28125              |

| 1             | 0    | 1    | 1    | 1    | 0    | 1             | 1.28750              |

| 1             | 0    | 1    | 1    | 0    | 1    | 0             | 1.29375              |

| <u>·</u><br>1 | 0    | 1    | 1    | 0    | 1    | 1             | 1.30000              |

| 1             | 0    | 1    | 1    | 0    | 0    | 0             | 1.30625              |

| 1             | 0    | 1    | 1    | 0    | 0    | 1             | 1.31250              |

| 1             | 0    | 1    | 0    | 1    | 1    | 0             |                      |

|               |      | 1    |      |      |      |               | 1.31875              |

| 1             | 0    | 1    | 0    | 1    | 1    | 1             | 1.32500              |

| 1             | 0    | 1    | 0    | 1    | 0    | 0             | 1.33125              |

| 1             | 0    | 1    | 0    | 1    | 0    | 1             | 1.33750              |

| 1             | 0    | 1    | 0    | 0    | 1    | 0             | 1.34375              |

| 1             | 0    | 1    | 0    | 0    | 1    | 1 /           | 1.35000              |

| 1             | 0    | 1    | 0    | 0    | 0    | 0             | 1.35625              |

| 1             | 0    | 1    | 0    | 0    | 0    | 1             | 1.36250              |

| 1             | 0    | 0    | 1    | 1    | 1    | 0             | 1.36875              |

| 1             | 0    | 0    | 1    | 1    | 1    | 1             | 1.37500              |

| 1             | 0    | 0    | 1    | 1    | 0    | 0             | 1.38125              |

| 1             | 0    | 0    | 1    | 1    | 0    | 1             | 1.38750              |

| 1             | 0    | 0    | 1 1  | 0    | 1    | 0             | 1.39375              |

| 1             | 0    | 0    | 1    | 0    | 1    | 1             | 1.40000              |

| 1             | 0    | 0    | 1    | 0    | 0    | 0             | 1.40625              |

| 1             | 0    | 0    | 1    | 0    | 0    | <u>0</u><br>1 | 1.40625              |

|               |      |      | ·    |      |      |               |                      |

| 1             | 0    | 0    | 0    | 1    | 1    | 0             | 1.41875              |

| 1             | 0    | 0    | 0    | 1    | 1    | 1             | 1.42500              |

| 1             | 0    | 0    | 0    | 1    | 0    | 0             | 1.43125              |

| 1             | 0    | 0    | 0    | 1    | 0    | 1             | 1.43750              |

| 1             | 0    | 0    | 0    | 0    | 1    | 0             | 1.44375              |

| 1             | 0    | 0    | 0    | 0    | 1    | 1             | 1.45000              |

| 1             | 0    | 0    | 0    | 0    | 0    | 0             | 1.45625              |

| 1             | 0    | 0    | 0    | 0    | 0    | 1             | 1.46250              |

| 0             | 1    | 1    | 1    | 1    | 1    | 0             | 1.46875              |

|               |      |      |      |      |      | -             | 1.47500              |

| VID4 | VID3 | VID2 | VID1 | VID0 | VID5 | VID6 | V <sub>OUT</sub> (V) |

|------|------|------|------|------|------|------|----------------------|

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1.48125              |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1.48750              |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1.49375              |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1.50000              |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1.50625              |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1.51250              |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1.51875              |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1.52500              |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1.53125              |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1.53750              |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1.54375              |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1.55000              |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1.55625              |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1.56250              |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1.56875              |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1.57500              |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1.58125              |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1.58750              |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1.59375              |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1.60000              |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.83125              |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.83750              |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.84375              |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.85000              |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.85625              |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.86250              |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.86875              |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.87500              |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.88125              |

| 0    | 1/   | 0    | 0    | 0    | 0    | 1    | 0.88750              |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.89375              |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.90000              |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.90625              |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.91250              |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.91875              |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.92500              |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.93125              |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.93750              |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.94375              |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.95000              |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.95625              |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.96250              |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.96875              |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.97500              |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.98125              |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.98750              |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.99375              |

| 0    | 0    | 0    | 1    | 1    | . 1  | 1    | 1.00000              |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1.00625              |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1.01250              |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1.01875              |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1.02500              |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1.03125              |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1.03750              |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1.04375              |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1.05000              |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.05625              |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.06250              |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.06875              |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.07500              |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1.08125              |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1.08750              |

Table 2. Output Voltage Programming Codes (8 Bit) 0 = logic LOW; 1 = logic HIGH. (MSB: VID7, LSB: VID0; 11110001b = F1h)

| HEX        | Voltage            | Tolerance                        | HEX        | Voltage            | Tolerance                                        | HEX        | Voltage           | Tolerance              | HEX        | Voltage            | Tolerance                |

|------------|--------------------|----------------------------------|------------|--------------------|--------------------------------------------------|------------|-------------------|------------------------|------------|--------------------|--------------------------|

| 0 0        | OFF                |                                  | 4 0        | 1.21250            | +-15mV LL (0 - 110A)                             | 8 0        | 0.81250           | Monotonic              | C 0        | 0.4125             | Don't Care               |

| 0 1        | OFF                |                                  | 4 1        | 1.20625            | +-15mV LL (0 - 110A)                             | 8 1        | 0.80625           | Monotonic              | C 1        | 0.40625            | Don't Care               |

| 02         | 1.60000            | +-15mV LL (0 -                   | 4 2        | 1.20000            | +-15mV LL (0 - 110A)                             | 8 2        | 0.8               | Monotonic              | C 2        | 0.40000            | Don't Care               |

| 03         | 1.59375            | +-15mV LL (0 -                   | 4 3        | 1.19375            | +-15mV LL (0 - 110A)                             | 8 3        | 0.79375           | Monotonic              | C 3        | 0.39375            | Don't Care               |

| 0 4        | 1.58750            | +-15mV LL (0 -                   | 4 4        | 1.18750            | +-15mV LL (0 - 110A)                             | 8 4        | 0.7875            | Monotonic              | C 4        | 0.38750            | Don't Care               |

| 0.5        | 1.58125            | +-15mV LL (0 -                   | 4 5        | 1.18125            | +-15mV LL (0 - 110A)                             | 8 5        | 0.78125           | Monotonic              | C 5        | 0.38125            | Don't Care               |

| 0 6        | 1.57500            | +-15mV LL (0 -                   | 4 6        | 1.17500            | +-15mV LL (0 - 110A)                             | 8 6        | 0.775             | Monotonic              | C 6        | 0.37500            | Don't Care               |

| 07         | 1.56875            | +-15mV LL (0 -                   | 47         | 1.16875            | +-15mV LL (0 - 110A)                             | 8 7        | 0.76875           | Monotonic              | C 7        | 0.36875            | Don't Care               |

| 8 0        | 1.56250            | +-15mV LL (0 -                   | 4 8        | 1.16250            | +-15mV LL (0 - 110A)                             | 8 8        | 0.7625            | Monotonic              | C 8        | 0.36250            | Don't Care               |

| 0 9        | 1.55625            | +-15mV LL (0 -                   | 4 9        | 1.15625            | +-15mV LL (0 - 110A)                             | 8 9        | 0.75625           | Monotonic              | C 9        | 0.35625            | Don't Care               |

| 0 A        | 1.55000            | +-15mV LL (0 -                   | 4 A        | 1.15000            | +-15mV LL (0 - 110A)                             | 8 A        | 0.75              | Monotonic              | CA         | 0.35000            | Don't Care               |

| 0 B        | 1.54375            | +-15mV LL (0 -                   | 4 B        | 1.14375            | +-15mV LL (0 - 110A)                             | 8 B        | 0.74375           | Monotonic              | СВ         | 0.34375            | Don't Care               |

| 0 C        | 1.53750            | +-15mV LL (0 -                   | 4 C        | 1.13750            | +-15mV LL (0 - 110A)                             | 8 C        | 0.7375            | Monotonic              | CC         | 0.33750            | Don't Care               |

| 0 D        | 1.53125            | +-15mV LL (0 -                   | 4 D        | 1.13125            | +-15mV LL (0 - 110A)                             | 8 D        | 0.73125           | Monotonic              | CD         | 0.33125            | Don't Care               |

| 0 E        | 1.52500            | +-15mV LL (0 -                   | 4 E        | 1.12500            | +-15mV LL (0 - 110A)                             | 8 E        | 0.725             | Monotonic              | CE         | 0.32500            | Don't Care               |

| 0 F        | 1.51875            | +-15mV LL (0 -                   | 4 F        | 1.11875            | +-15mV LL (0 - 110A)                             | 8 F        | 0.71875           | Monotonic              | CF         | 0.31875            | Don't Care               |

| 10         | 1.51250            | +-15mV LL (0 -                   | 50         | 1.11250            | +-15mV LL (0 - 110A)                             | 9 0        | 0.7125            | Monotonic              | D 0        | 0.31250            | Don't Care               |

| 11         | 1.50625            | +-15mV LL (0 -                   | 51         | 1.10625            | +-15mV LL (0 - 110A)                             | 9 1        | 0.70625           | Monotonic              | D 1        | 0.30625            | Don't Care               |

| 12         | 1.50000            | +-15mV LL (0 -<br>+-15mV LL (0 - | 5 2<br>5 3 | 1.10000<br>1.09375 | +-15mV LL (0 - 110A)<br>+-15mV LL (0 - 110A)     | 92         | 0.7<br>0.69375    | Monotonic<br>Monotonic | D 2        | 0.30000<br>0.29375 | Don't Care<br>Don't Care |

| 1 4        | 1.49375<br>1.48750 | +-15mV LL (0 -<br>+-15mV LL (0 - | 5 4        | 1.09375            | +-15mV LL (0 - 110A)<br>+-15mV LL (0 - 110A)     | 9 3        | 0.69375           | Monotonic<br>Monotonic | D 3        | 0.29375            | Don't Care Don't Care    |

| 15         | 1.48750            | +-15mV LL (0 -                   | 55         | 1.08730            | +-15mV LL (0 - 110A)<br>+-15mV LL (0 - 110A)     | 9 5        | 0.68125           | Monotonic              | D 5        | 0.28750            | Don't Care               |

| 16         | 1.47500            | +-15mV LL (0 -                   | 56         | 1.07500            | +-15mV LL (0 - 110A)                             | 96         | 0.675             | Monotonic              | D 6        | 0.27500            | Don't Care               |

| 17         | 1.46875            | +-15mV LL (0 -                   | 57         | 1.06875            | +-15mV LL (0 - 110A)                             | 97         | 0.66875           | Monotonic              | D 7        | 0.26875            | Don't Care               |

| 18         | 1.46250            | +-15mV LL (0 -                   | 58         | 1.06250            | +-15mV LL (0 - 110A)                             | 98         | 0.6625            | Monotonic              | D 8        | 0.26250            | Don't Care               |

| 19         | 1.45625            | +-15mV LL (0 -                   | 59         | 1.05625            | +-15mV LL (0 - 110A)                             | 99         | 0.65625           | Monotonic              | D 9        | 0.25625            | Don't Care               |

| 1 A        | 1.45000            | +-15mV LL (0 -                   | 5 A        | 1.05000            | +-15mV LL (0 - 110A)                             | 9 A        | 0.65              | Monotonic              | DA         | 0.25000            | Don't Care               |

| 1 B        | 1.44375            | +-15mV LL (0 -                   | 5 B        | 1.04375            | +-15mV LL (0 - 110A)                             | 9 B        | 0.64375           | Monotonic              | DB         | 0.24375            | Don't Care               |

| 1 C        | 1.43750            | +-15mV LL (0 -                   | 5 C        | 1.03750            | +-15mV LL (0 - 110A)                             | 9 C        | 0.6375            | Monotonic              | DC         | 0.23750            | Don't Care               |

| 1 D        | 1.43125            | +-15mV LL (0 -                   | 5 D        | 1.03125            | +-15mV LL (0 - 110A)                             | 9 D        | 0.63125           | Monotonic              | DD         | 0.23125            | Don't Care               |

| 1 E        | 1.42500            | +-15mV LL (0 -                   | 5 E        | 1.02500            | +-15mV LL (0 - 110A)                             | 9 E        | 0.625             | Monotonic              | DE         | 0.22500            | Don't Care               |

| 1 F        | 1.41875            | +-15mV LL (0 -                   | 5 F        | 1.01875            | +-15mV LL (0 - 110A)                             | 9 F        | 0.61875           | Monotonic              | DF         | 0.21875            | Don't Care               |

| 20         | 1.41250            | +-15mV LL (0 -                   | 60         | 1.01250            | +-15mV LL (0 - 110A)                             | A 0        | 0.6125            | Monotonic              | E 0        | 0.21250            | Don't Care               |

| 21         | 1.40625            | +-15mV LL (0 -                   | 61         | 1.00625            | +-15mV LL (0 - 110A)                             | A 1        | 0.60625           | Monotonic              | E 1        | 0.20625            | Don't Care               |

| 22         | 1.40000            | +-15mV LL (0 -                   | 62         | 1.00000            | Monotonic DAC (6.25 mV)                          | A 2        | 0.6               | Monotonic              | E 2        | 0.20000            | Don't Care               |

| 23         | 1.39375            | +-15mV LL (0 -                   | 63         | 0.99375            | Monotonic DAC (6.25 mV)                          | A 3        | 0.59375           | Monotonic              | E 3        | 0.19375            | Don't Care               |

| 24         | 1.38750            | +-15mV LL (0 -                   | 6 4        | 0.98750            | Monotonic DAC (6.25 mV)                          | A 4        | 0.5875            | Monotonic              | E 4        | 0.18750            | Don't Care               |

| 25         | 1.38125            | +-15mV LL (0 -                   | 6.5        | 0.98125            | Monotonic DAC (6.25 mV)                          | A 5        | 0.58125           | Monotonic              | E 5        | 0.18125            | Don't Care               |

| 26         | 1.37500            | +-15mV LL (0 -                   | 66         | 0.97500            | Monotonic DAC (6.25 mV)                          | A 6        | 0.575             | Monotonic              | E 6        | 0.17500            | Don't Care               |

| 27         | 1.36875            | +-15mV LL (0 -                   | 67         | 0.96875            | Monotonic DAC (6.25 mV)                          | A 7        | 0.56875           | Monotonic              | E 7        | 0.16875            | Don't Care               |

| 28         | 1.36250            | +-15mV LL (0 -                   | 68         | 0.96250            | Monotonic DAC (6.25 mV)                          | A 8        | 0.5625            | Monotonic              | E 8        | 0.16250            | Don't Care               |

| 29         | 1.35625            | +-15mV LL (0 -                   | 69         | 0.95625            | Monotonic DAC (6.25 mV)                          | A 9        | 0.55625           | Monotonic              | E 9        | 0.15625            | Don't Care               |

| 2 A        | 1.35000            | +-15mV LL (0 -                   | 6 A        | 0.95000            | Monotonic DAC (6.25 mV)                          | AA         | 0.55              | Monotonic              | EA         | 0.15000            | Don't Care               |

| 2 B<br>2 C | 1.34375<br>1.33750 | +-15mV LL (0 -<br>+-15mV LL (0 - | 6 B<br>6 C | 0.94375<br>0.93750 | Monotonic DAC (6.25 mV)                          | A B<br>A C | 0.54375<br>0.5375 | Monotonic<br>Monotonic | E B<br>E C | 0.14375<br>0.13750 | Don't Care<br>Don't Care |

| 2 D        | 1.33750            | +-15mV LL (0 -                   | 6 D        | 0.93730            | Monotonic DAC (6.25 mV)  Monotonic DAC (6.25 mV) | A D        | 0.5375            | Monotonic              | ED         | 0.13750            | Don't Care               |

| 2 E        | 1.32500            | +-15mV LL (0 -                   | 6 E        | 0.93123            | Monotonic DAC (6.25 mV)                          | AE         | 0.525             | Monotonic              | EE         | 0.13125            | Don't Care               |

| 2 F        | 1.31875            | +-15mV LL (0 -                   | 6 F        | 0.92300            | Monotonic DAC (6.25 mV)                          | AF         | 0.51875           | Monotonic              | EF         |                    | Don't Care               |

| 30         | 1.31250            | +-15mV LL (0 -                   | 70         | 0.91250            | Monotonic DAC (6.25 mV)                          | B 0        | 0.5125            | Monotonic              | F 0        |                    | Don't Care               |

| 31         | 1.30625            | +-15mV LL (0 -                   | 71         | 0.90625            | Monotonic DAC (6.25 mV)                          | B 1        | 0.50625           | Monotonic              | F 1        | 0.10625            | Don't Care               |

| 32         | 1.30000            | +-15mV LL (0 -                   | 72         | 0.90000            | Monotonic DAC (6.25 mV)                          | B 2        | 0.5               | Monotonic              | F 2        | 0.10000            | Don't Care               |

| 33         | 1.29375            | +-15mV LL (0 -                   | 73         | 0.89375            | Monotonic DAC (6.25 mV)                          | B 3        | 0.49375           | Don't Care             | F 3        | 0.09375            | Don't Care               |

| 3 4        | 1.28750            | +-15mV LL (0 -                   | 7 4        | 0.88750            | Monotonic DAC (6.25 mV)                          | B 4        | 0.4875            | Don't Care             | F 4        | 0.08750            | Don't Care               |

| 3.5        | 1.28125            | +-15mV LL (0 -                   | 7.5        | 0.88125            | Monotonic DAC (6.25 mV)                          | B 5        | 0.48125           | Don't Care             | F 5        | 0.08125            | Don't Care               |

| 36         | 1.27500            | +-15mV LL (0 -                   | 76         | 0.87500            | Monotonic DAC (6.25 mV)                          | B 6        | 0.475             | Don't Care             | F6         | 0.07500            | Don't Care               |

| 3 7        | 1.26875            | +-15mV LL (0 -                   | 77         | 0.86875            | Monotonic DAC (6.25 mV)                          | В7         | 0.46875           | Don't Care             | F 7        | 0.06875            | Don't Care               |

| 38         | 1.26250            | +-15mV LL (0 -                   | 78         | 0.86250            | Monotonic DAC (6.25 mV)                          | В8         | 0.4625            | Don't Care             | F 8        | 0.06250            | Don't Care               |

| 3 9        | 1.25625            | +-15mV LL (0 -                   | 79         | 0.85625            | Monotonic DAC (6.25 mV)                          | В9         | 0.45625           | Don't Care             | F 9        | 0.05625            | Don't Care               |

| 3 A        | 1.25000            | +-15mV LL (0 -                   | 7 A        | 0.85000            | Monotonic DAC (6.25 mV)                          | ВА         | 0.45              | Don't Care             | FA         | 0.05000            | Don't Care               |

| 3 B        | 1.24375            | +-15mV LL (0 -                   | 7 B        | 0.84375            | Monotonic DAC (6.25 mV)                          | ВВ         | 0.44375           | Don't Care             | FΒ         | 0.04375            | Don't Care               |

| 3 C        | 1.23750            | +-15mV LL (0 -                   | 7 C        | 0.83750            | Monotonic DAC (6.25 mV)                          | ВС         | 0.4375            | Don't Care             | FC         | 0.03750            | Don't Care               |

| 3 D        | 1.23125            | +-15mV LL (0 -                   | 7 D        | 0.83125            | Monotonic DAC (6.25 mV)                          | B D        | 0.43125           | Don't Care             | FD         | 0.03125            | Don't Care               |

| 3 E        | 1.22500            | +-15mV LL (0 -                   | 7 E        | 0.82500            | Monotonic DAC (6.25 mV)                          | BE         | 0.425             | Don't Care             | FE         | OFF                |                          |

| 3 F        | 1.21875            | +-15mV LL (0 -                   | 7 F        | 0.81875            | Monotonic DAC (6.25 mV)                          | BF         | 0.41875           | Don't Care             | FF         | OFF                | 1                        |

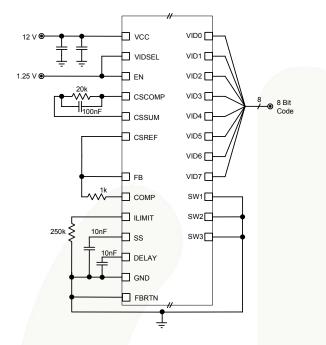

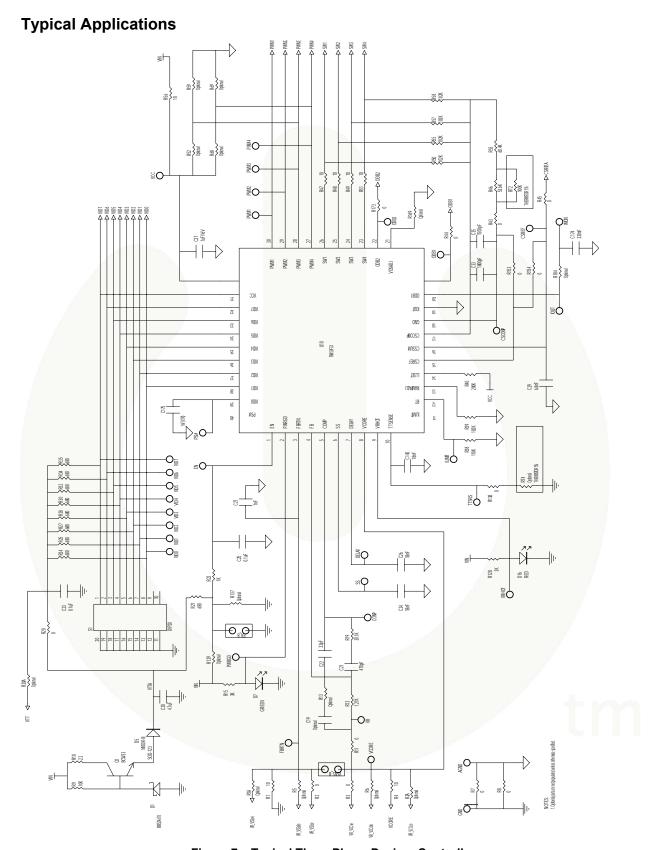

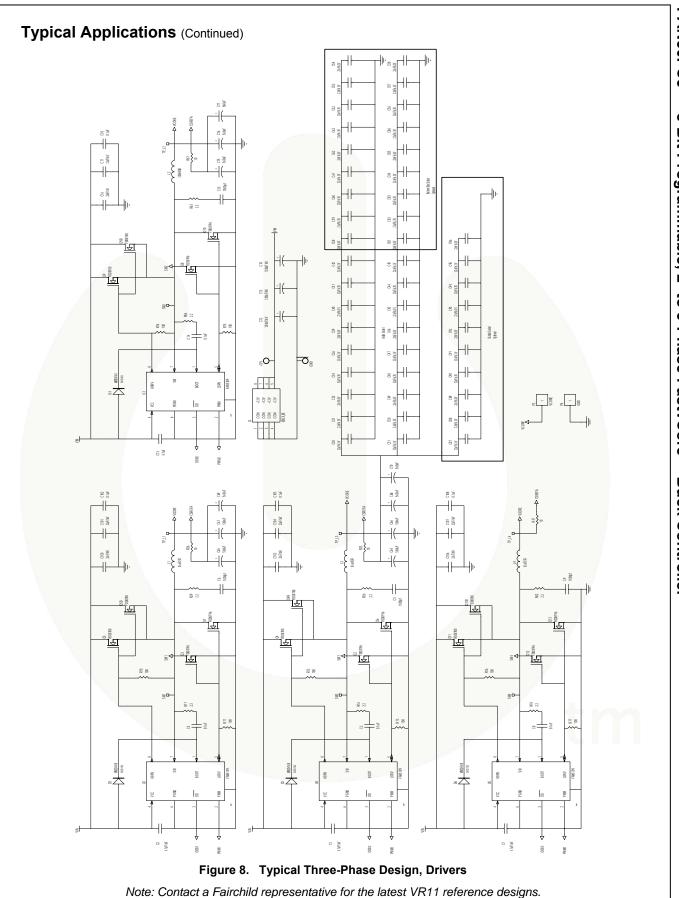

Figure 7. Typical Three-Phase Design, Controller

Note: Contact a Fairchild representative for the latest VR11 reference designs.

#### **Theory of Operation**

**Note**: The values shown in this section are for reference only. See the parametric tables for actual values.

The FAN50FC3 is a fixed-frequency PWM control with multi-phase logic outputs for use in 2- and 3-phase synchronous buck CPU power supplies. It has an internal VID DAC designed to interface directly with 8-bit VRD/VRM 11 and 7-bit VRD/VRM 10.x compatible CPUs. Multiphase operation is required for the high currents and low voltages of today's microprocessors that can require up to 150A of current.

The integrated features of the FAN50FC3 ensure a stable, high-performance topology for:

- Balanced currents and thermals between phases

- High-speed response at the lowest possible switching frequency and output decoupling capacitors

- Tight load line regulation and accuracy

- High current output by allowing up to 3-phase designs

- Reduced output ripple due to multiphase operation

- Good PC board layout noise immunity

- Easily settable and adjustable design parameters with simple component selection

- 2- to 3-phase operation allows optimizing designs for cost/performance and support a wide range of applications.

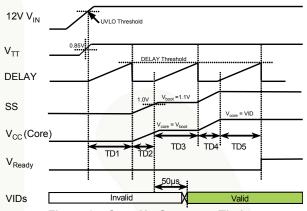

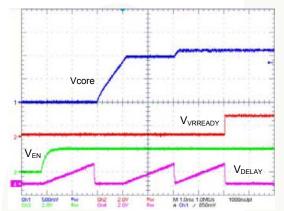

#### **Start-Up Sequence**

The start-up sequence is shown in Figure 9. Once the EN and UVLO conditions are met, the DELAY pin goes through one cycle (TD1), after which, the internal oscillator starts. The first two clock cycles are used for phase detection. The soft-start ramp is then enabled (TD2), raising the output voltage up to the boot voltage of 1.1V. The boot hold time (TD3) allows the processor VID pins to settle to the programmed VID code. After TD3 timing is finished, the output soft starts, either up or down, to the final VID voltage (during TD4). TD5 is the time between the output reaching the VID voltage and the PWRGD being presented to the system.

#### **Phase-Detection Sequence**

During start-up, the number of operational phases and their phase relationship is determined by the internal circuitry that monitors the PWM outputs. Normally, the FAN50FC3 operates as a 3-phase PWM controller. For 2-phase operation, connect the PWM3 pin to  $V_{\text{CC}}$ .

The PWM logic, which is driven by the master oscillator, directs the phase sequencer and channel detectors. Channel detection is carried out during the first two clock cycles after the chip is enabled. During the detection period, PWM3 is connected to a 100µA sinking current source and two internal voltage comparators check the pin voltage of PWM3 versus a threshold of 3V typical. If

the pin is tied to  $V_{\text{IN}}$ , the pin voltage is above 3V and that phase is disabled and put in a tri-state mode. Otherwise, the internal 100µA current source pulls PWM pin below the 3V threshold. After channel detection, the current source is removed.

Shorting PWM3 to  $V_{\text{CC}}$  configures the system into 2-phase operation.

Figure 9. Start-Up Sequence Timing

After detection time is complete, the PWM outputs not sensed as "pulled HIGH" function as normal PWM outputs. PWM outputs sensed as "pulled HIGH" are put into a high-impedance state.

The PWM signals are logic-level outputs intended for driving external gate drivers, such as the FAN5109. Since each phase is monitored independently; operation approaching 100% duty cycle is possible. More than one output can be on at the same time to allow phase overlap.

#### **Master Clock Frequency**

The clock frequency is set with an external resistor connected from the RT pin to ground. The frequency-to-resistor relationship is shown in the graph in Figure 6. To determine the frequency per phase, divide the clock by the number of enabled phases.

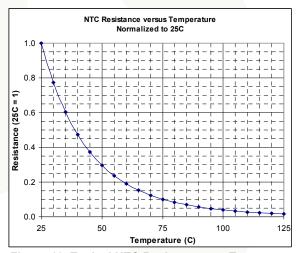

#### **Output Current Sensing**

The FAN50FC3 provides a dedicated current-sense amplifier (CSA) to monitor the output current for proper voltage positioning and for current limit detection (see Figure 1). It differentially senses the voltage drop across the DCR of the inductors to give the total average current being delivered to the load. This method is inherently more accurate than peak current detection or sampling the voltage across the low-side MOSFETs. The CSA implementation can be configured for the objectives of the system. It can use output inductor DCR sensing without a thermistor for lowest cost or output inductor DCR sensing with a thermistor for improved accuracy with tracking of inductor temperature.

To measure the differential voltage across the output inductors, the positive input of the CSA (CSREF pin) is connected, using equal value resistors, to the output capacitor side of the inductors. The negative input of the CSA (CSSUM pin) is connected, using equal value resistors, to the MOSFET side of the inductors. The CSA's output (CSCOMP) is a voltage equal to the voltage dropped across the inductors, times the gain of the CSA, and is inversely proportional to the output current.

The gain of the CSA is set by connecting an external feedback resistor between the CSA's CSCOMP and CSSUM pins. A capacitor, connected across the resistor, is used to create a low-pass filter to remove high frequency switching effects and create a RC pole to cancel the zero created by the L/DCR of the inductor. The end result is that the voltage between the CSCOMP and CSREF pins is inversely proportional to the output current (CSCOMP goes negative relative to CSREF as current increases) and the CSA gain sets the ratio of the CSA output voltage change as a function of output current change. This difference in voltage is used by the current limit comparator and by the droop amplifier to create the output load line.

The CSA is designed to have a low offset input voltage. The sensing gain is determined by external resistors, so it can be made extremely accurate.

#### **Load Line Impedance Control**

The FAN50FC3 has an internal "Droop Amp" that effectively subtracts the voltage applied between the CSCOMP and CSREF pins from the FB pin voltage of the error amplifier, allowing the output voltage to be varied independent of the DAC setting. A positive voltage on CSCOMP (relative to CSREF) increases the output voltage and a negative voltage decreases it. Since the voltage between the CSA's CSCOMP and CSREF pins is inversely proportional to the output, current causes the output voltage to decrease an amount directly proportional to the increase in output current creating a droop or load line. The ratio of output voltage decrease to output current increase is the effective R<sub>o</sub> of the power supply and is set by the DC gain of the CSA.

#### **Current Control Mode & Thermal Balance**

The FAN50FC3 has individual SW inputs for each phase. They are used to measure the voltage drop across the bottom FETs to determine the current in each phase. This information is combined with an internal ramp to create a current balancing feedback system. This gives good current balance accuracy that takes into account, not only the current, but also the thermal balance between the bottom FETs in each phase.

External resistors  $R_{\rm SW1}$  through  $R_{\rm SW3}$  can be placed in series with individual SW inputs to create an intentional current imbalance, such as in cases where one phase may have better cooling and can support higher currents. It is best to have the ability to add these resistors in the initial design, to ensure that placeholders are provided in the layout. To increase the current in a phase, increase  $R_{\rm SW}$  for that phase. Adding a resistor of

a few hundred ohms can make a noticeable increase in current, so use small steps.

The amplitude of the internal ramp is set by a resistor connected between the input voltage and the RAMPADJ pin. This method also implements the voltage feedforward function.

#### **Output Voltage Differential Sensing**

The FAN50FC3 uses differential sensing in conjunction with a high-accuracy DAC and a low-offset error amplifier to maintain a worst-case specification of ±7.7mV differential sensing accuracy over its specified operating range.

A high gain-bandwidth error amplifier is used for the voltage control loop. The voltage on the FB pin is compared to the DAC voltage to control the output voltage. The FB voltage is also effectively offset by the CSA output voltage for accurately positioning the output voltage as a function of current. The output of the error amplifier is the COMP pin, which is compared to the internal PWM ramps to create the PWM pulse widths.

The negative input (FB) is tied to the output sense location with a resistor  $R_{\rm B}$  and is used for sensing and controlling the output voltage at this point. Additionally a current source is connected internally to the FB pin, which causes a fixed DC current to flow through  $R_{\rm B}.$  This current creates a fixed voltage drop (offset voltage) across  $R_{\rm B}.$  The offset voltage adds to the sensed output voltage, which causes the error amplifier to regulate the actual output voltage lower than the programmed VID voltage by this amount. The main loop compensation is incorporated into the feedback by an external network connected between FB and COMP.

#### **Delay Timer**

The delay times for the start-up timing sequence are set with a capacitor from the DELAY pin to ground, as stated in the Start-Up Sequence section. In UVLO or when EN is logic LOW, the DELAY pin is held at ground. Once the UVLO and EN are asserted, a 15 $\mu$ A current flows out of the DELAY pin to charge C<sub>DLY</sub>. A comparator, with a threshold of 1.7V, monitors the DELAY pin voltage. The delay time is therefore set by the 15 $\mu$ A charging the delay capacitor from 0V to 1.7V. This DELAY pin is used for multiple delay timings (TD1, TD3, and TD5) during start-up. DELAY is also used for timing the current-limit latch-off, as explained in the *Current Limit* section.

#### Soft-Start

The soft-start times for the output voltage are set with a capacitor from the SS pin to ground. After TD1 and the phase-detection cycle are complete, the SS time (TD2 in Figure 9) starts. The SS pin is disconnected from GND and the capacitor is charged up to the 1.1V boot voltage by the SS amplifier, which has a limited output current of 15 $\mu$ A. The voltage at the FB pin follows the ramping voltage on the SS pin, limiting the inrush current during start-up. The soft-start time depends on the value of the boot voltage and  $C_{\rm SS}$ .

Once the SS voltage is within 100mV of the boot voltage, the boot voltage delay time (TD3) is started. The end of the boot voltage delay time signals the beginning of the second soft-start time (TD4). The SS voltage changes from the boot voltage to the programmed VID DAC voltage (either higher or lower) using the SS amplifier with the limited output current of 15 $\mu$ A. The voltage of the FB pin follows the ramping voltage of the SS pin, limiting the inrush current during the transition from the boot voltage to the final DAC voltage. The second soft-start time depends on the boot voltage, the programmed VID DAC voltage, and CSS.

If either EN is taken LOW or  $V_{\rm CC}$  drops below UVLO, DELAY and SS are reset to ground to be ready for another soft-start cycle. Figure 10 shows typical start-up waveforms for the FAN50FC3.

Figure 10. Start-up Waveforms

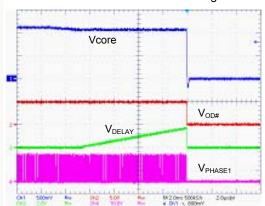

## Current-Limit, Short-Circuit, and Latch-Off Protections

The FAN50FC3 compares a programmable current-limit set point to the voltage from the output of the current sense amplifier. The current-limit level is set with the resistor from the ILIMIT pin to ground. During operation, the voltage on ILIMIT is 1.7V. The current through the external resistor is internally scaled to give a current limit threshold of  $10\text{mV}/\mu\text{A}$ . If the voltage between CSREF and CSCOMP rises above the current-limit threshold, the internal current-limit amplifier controls the internal COMP voltage to maintain the average output current at the limit.

After TD5 has completed, an over-current (OC) event starts a latch-off delay timer. The delay timer uses the DELAY pin timing capacitor. During current limit, the DELAY pin current is reduced to 3.75µA. When the voltage on the delay pin reaches 1.7V, the controller shuts down and latches off. The current limit latch-off delay time is therefore set by the current of 3.75µA charging the delay capacitor 1.7V. This delay is four times longer than the delay time during the start-up sequence. If there is a current limit during start-up, the FAN50FC3 goes through TD1 to TD5 in current limit, then starts the latch-off timer. Because the controller continues to operate during the latch-off delay time, if the OC is removed before the 1.7V threshold is reached, the controller returns to normal operation and the DELAY capacitor is reset to GND.

The latch-off function can be reset by cycling the supply voltage to the FAN50FC3 or by toggling the EN pin LOW for a short time. To disable the short-circuit latch-off function, an external resistor can be placed in parallel with  $C_{\text{DLY}}$  to prevent the DELAY capacitor from charging up to the 1.7V threshold. The addition of this resistor causes a slight increase in the delay times.

During start-up, when the output voltage is below 200mV, a secondary current limit is active. This secondary current limit clamps the internal COMP voltage at the PWM comparators to 1.5V. Typical overcurrent latch-off waveforms are shown in Figure 11.

Figure 11. Over-Current Latch-off Waveforms

#### FastvCore™ Operation

FastvCore™ improves the transient response for a load step-up change. Normally a controller has to wait till the next clock cycle if a load step-up happens during between PWM signals. With FastvCore™, the controller is able to immediately respond to the load step change, so that the inductor current increases to the new load current in a shorter period of time.

FastvCore<sup>™</sup> is adjusted by connecting a resistor (R<sub>SETOS</sub>) between pin 16 (VOSADJ) and AGND to set the threshold where FastvCore<sup>™</sup> is initiated.

$$R_{SETOS} = (V_{OS} + LLTOB) \cdot R_T \cdot 10$$

EQ. 1

where:

$R_T$  = the frequency set resistor

V<sub>OS</sub> = the target FastvCore™ detection threshold that is the voltage difference between the output voltage starting point and the voltage when the FastvCore™ starts to respond to a load stepup change

LLTOB= the socket load line tolerance band

FastvCore™ design example:

lf:

$R_T = 267 \text{kohm}$   $V_{OS} = 35 \text{mV}$ LLTOB = +/-19 \text{mV}

Then:

$R_{SETOS}$  =  $(V_{OS}+LLTOB) \cdot R_{T} \cdot 10$ =  $(35mV+19mV) \cdot 267kohm \cdot 10$ = 144.2kohm

#### **Dynamic VID**

The FAN50FC3 has the ability to dynamically change the VID inputs while the controller is running. This allows the output voltage to change while the supply is running and supplying current to the load. This is commonly referred to as VID on-the-fly (OTF). A VID OTF can occur under light or heavy load conditions. The processor signals the controller by changing the VID inputs in multiple steps from the start code to the finish code. This change can be positive or negative.

When a VID input changes state, the FAN50FC3 detects the change and ignores the DAC inputs for a minimum of 200ns. This time prevents a false code due to logic skew while the eight VID inputs are changing. Additionally, the first VID change initiates the PWRGD and CROWBAR blanking functions for a minimum of 100µs to prevent a false PWRGD or CROWBAR event. Each VID change resets the internal timer.

#### **Power Good Monitoring**

The power good comparator monitors the output voltage via the CSREF pin. The PWRGD pin is an open-drain output whose high level (when connected to a pull-up resistor) indicates that the output voltage is within the nominal limits specified based on the VID voltage setting. PWRGD goes low if the output voltage is outside of this specified range, if the VID DAC inputs are in no CPU mode, or whenever the EN pin is pulled low. PWRGD is blanked during a VID OTF event for a period of ~200µs to prevent false signals during the time the output is changing.

The PWRGD circuitry also incorporates an initial turn-on delay time (TD5) based on the DELAY timer. Prior to the SS voltage reaching the programmed VID DAC voltage, 100mV, the PWRGD pin is held low. Once the SS pin is within 100mV of the programmed DAC voltage, the capacitor on the DELAY pin begins to charge up. A comparator monitors the DELAY voltage and enables PWRGD when the voltage reaches 1.7V. The PWRGD delay time is therefore set by a current of 15µA charging a capacitor from 0V to 1.7V.

#### **Output Crowbar**

As part of the protection for the load and output components of the supply, the PWM outputs are driven low (turning on the low-side MOSFETs) when the output voltage exceeds the upper crowbar threshold. This crowbar action stops once the output voltage falls below the release threshold of approximately 300mV.

Turning on the low-side MOSFETs pulls down the output as the reverse current builds up in the inductors. If the

output over-voltage is due to a short in the high-side MOSFET, this action current-limits the input supply, protecting the microprocessor.