## **ON Semiconductor**

## Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# FSA8039A Audio Jack Interface Solution with Moisture Sensing

#### **Features**

- Detection:

- Accessory Plug-In

- Send / End Key Press

- Prevents False Detection due to Moisture

- V<sub>DD</sub>: 2.5 V to 4.5 V

- V<sub>IO</sub>: 1.6 V to V<sub>DD</sub>

- THD (MIC): 0.01% Typical

- 15 kV Air Gap ESD

- MIC Switch Removes Audio Jack "Pop" and "Click" Caused by MIC Bias

## **Applications**

- Any Device with 3.5 mm and 2.5 mm Audio Jack

- Cellular Phones, Smart Phones, and Tablets

- MP3, GPS, and PMP

## **Description**

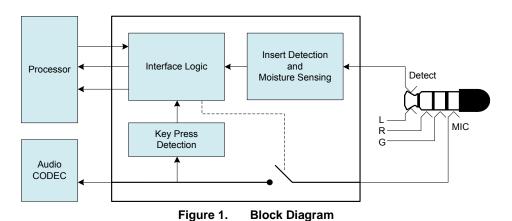

The FSA8039A is a detection switch for an audio jack that employs a normally open detect pin. The FSA8039A works with 3-pole and 4-pole accessories. The FSA8039A features moisture sensing that prevents false detection of accessories in the audio jack. The integrated MIC switch allows a processor to configure attached accessories. The architecture is designed to allow common third-party headphones to be used for listening to music from mobile handsets, personal media players, and portable peripheral devices.

#### **Related Resources**

FSA8039A Evaluation Board

**Ordering Information**

| Part Number  | Operating<br>Temperature Range | Top Mark | Package                                         | Packing<br>Method |

|--------------|--------------------------------|----------|-------------------------------------------------|-------------------|

| FSA8039AUMSX | -40°C to 85°C                  | NF       | 10-Lead, UMLP, 1.4 mm x 1.8 mm,<br>0.4 mm Pitch | Tape & Reel       |

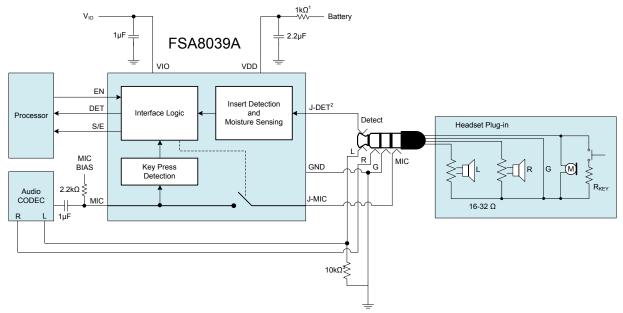

## **Typical Application Diagram**

Figure 2. Typical Application

#### Notes:

- A 1 kΩ resistor with a 2.2 µF capacitor is recommended for direct battery connection. This filter helps stabilize

power rail events not associated with the FSA8039A. If power is supplied from a stable source, such as from a

PMIC or LDO, a single 1 µF capacitor is recommended.

- 2. The J-DET is shorted to the left (L) audio channel when the headset or accessory plug is inserted into most audio jacks. Any external circuitry attached to the J-DET pin could affect audio performance in the 20-20 kHz range on the left channel.

- 3. The optional 10  $k\Omega$  resistor on the left channel is used to assist in detection of high-impedance accessories. This resistor has negligible impact on audio fidelity.

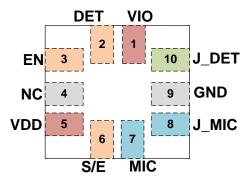

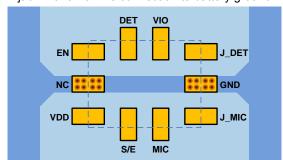

# **Pin Configuration**

Figure 3. Pin Assignment (Through View)

## **Pin Definitions**

| Name  | Pin#       | Туре   | Description                                                            |                                           |                                            |               |  |  |

|-------|------------|--------|------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|---------------|--|--|

| VIO   | 1          | Power  | Baseband or processor I/O supply voltage                               |                                           |                                            |               |  |  |

| DET   | 2          | Output | Indicates if audio accessory is plugged in                             | DET=Vol                                   | DET=V <sub>OL</sub> , Accessory plugged in |               |  |  |

| DET   | 2          | Output | (debounced output)                                                     | DET=V <sub>OH</sub> , Accessory unplugged |                                            |               |  |  |

|       |            |        |                                                                        |                                           | No Plug                                    | Plug inserted |  |  |

| EN    | EN 3 Input | Input  | Microphone switch control                                              | EN=V <sub>IL</sub>                        | MIC switch open                            | Music<br>Mode |  |  |

|       |            |        |                                                                        | MIC switch open                           | MIC switch closed                          |               |  |  |

| NC    | 4          | NC     | No connect; connect to GND for improved solder stability               |                                           |                                            |               |  |  |

| VDD   | 5          | Power  | Supply voltage                                                         |                                           |                                            |               |  |  |

| S/E   | 6          | Output | Indicates when an accessory key has been                               | S/E=V <sub>OL</sub> , No Key Press        |                                            |               |  |  |

| 3/E   | Ö          | Output | pressed (debounced output)                                             | S/E=V <sub>OH</sub> , Key Press           |                                            |               |  |  |

| MIC   | 7          | I/O    | Connection to the microphone pre-amplifier                             | EN=V <sub>IL</sub> , Switch Open          |                                            |               |  |  |

| J_MIC | 8          | I/O    | Connection from the audio jack mechanical plug microphone pin          |                                           |                                            |               |  |  |

| GND   | 9          | Ground | Ground for both the audio jack and PCB                                 |                                           |                                            |               |  |  |

| J_DET | 10         | Input  | Input from the audio jack mechanical plug insert/removal detection pin |                                           |                                            |               |  |  |

### **Application Information**

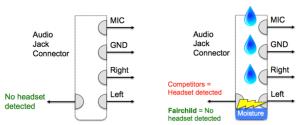

#### **Moisture Detection**

Moisture in the audio jack can cause the phone to incorrectly route audio signals to the audio jack rather than the phone speaker or microphone. Users perceive this as a dropped call or muted phone. The FSA8039A protects against this type of false plug-insert notification.

Figure 4. Moisture Impedance Detection

#### **Music Mode**

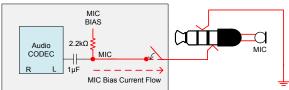

When a 4-pole headset is inserted into the audio jack and a music/listening application is used, the MIC bias is normally enabled for headset button press detection (i.e. mute, volume change, etc.). This consumes power due to a constant path from the MIC bias resistor and microphone in the headset to GND. Fairchild has developed a Music Mode to enable the MIC switch

periodically to monitor for a pressed button. This results in a power savings for battery-sensitive devices, such as cell phones or MP3 players. The FSA8039A enters Music Mode when EN=LOW and a 4-pole headset is inserted. Music Mode reduces MIC bias current by approximately 90%.

Figure 5. MIC Bias Leakage Path

#### **Headset Key-Press Operation**

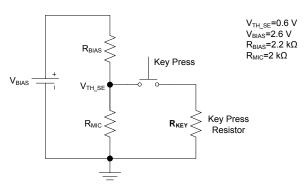

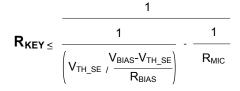

The headset key-press comparator threshold is a function of the MIC bias voltage, MIC bias resistor, and the MIC impedance. All of these variables must be considered when calculating the key-press resistor value. Figure 6 is an example of how to calculate the key-press resistor value.

R<sub>KEY ≤ 980 Ω</sub>

Figure 6. Example Key-Press Resistor Calculations and Values

### **Design / Layout Best Practices**

System-level Electrostatic Discharge (ESD) events often occur in the audio path of a mobile device, typically when inserting or removing an accessory from the audio jack. The audio path from the audio jack to the audio codec or microphone pre-amplifier is typically designed for relatively low frequencies (<100 kHz). An ESD event is a high-frequency event with fast edge rates (<100 ns/V). For this reason, the audio paths represent a high-frequency transmission line to the ESD signal.

Use the following PCB design and layout best practices when designing a system audio path.

#### **Audio Path Layout Guidelines for ESD**

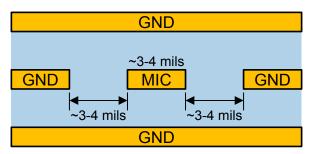

For the MIC and ground signals between the audio jack and FSA8039A, decrease the spacing between these traces to increase the inductive coupling of the signals. In effect, this creates a low-frequency band pass filter that shunts ESD energy to ground before it reaches internal components. Where feasible, lay the MIC trace as a shielded stripline, as shown in Figure 7.

Figure 7. MIC PCB Trace as Shielded Stripline

#### **Ground Layout Guidelines**

Ground layout for audio path devices should consider high-frequency effects. During an ESD event, parasitic inductance and resistance in the ground path reduces its ability to shunt the fast transient energy. Use the following techniques to improve grounding effectiveness:

- Use "star" ground connections (not daisy-chain).

- Use ground vias to minimize ground path impedance and ground loops.

- Stitch ground traces to the ground plane at the device, where possible (see Figure 8).

- Flood ground, where possible (see Figure 8).

- Avoid ground "islands" or "peninsulas" if possible.

- If using a modular audio jack assembly that is not soldered to the main PCB, use a ground pad on the jack with an ohmic connection to battery ground.

Figure 8. PCB Layout/Grounding

In addition to ESD robustness, these techniques can improve audio signal performance by reducing audio crosstalk and echo due to resistive voltage drops in the audio ground path.

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                            | Parameter                                  |                                                       |      | Max.                 | Unit |

|-----------------------------------|--------------------------------------------|-------------------------------------------------------|------|----------------------|------|

| V <sub>DD</sub> , V <sub>IO</sub> | Supply Voltage from Battery                |                                                       | -0.5 | 6.0                  | V    |

| V <sub>SW</sub>                   | Switch I/O Voltage (MIC, J_MIC)            |                                                       | -0.5 | V <sub>DD</sub> +0.5 | V    |

| $V_{JD}$                          | Input Voltage for J_DET Input              |                                                       | -1.5 | V <sub>DD</sub> +0.5 | V    |

| I <sub>IK</sub>                   | Input Clamp Diode Current                  |                                                       | -50  |                      | mA   |

| I <sub>SW</sub>                   | Switch I/O Current                         |                                                       |      | 50                   | mA   |

| T <sub>STG</sub>                  | Storage Temperature Range                  |                                                       |      | +150                 | °C   |

| TJ                                | Maximum Junction Temperature               |                                                       |      | +150                 | °C   |

| TL                                | Lead Temperature (Soldering, 10 Seconds)   |                                                       |      | +260                 | °C   |

|                                   | IEC 61000-4-2 System ESD  Air Gap  Contact |                                                       | 15   |                      |      |

|                                   |                                            |                                                       | 8    |                      |      |

| ESD                               | Human Body Model,                          | J_DET, J_MIC, V <sub>DD</sub> , V <sub>IO</sub> , GND | 8    |                      | kV   |

| 200                               | ANSI/ESDA/JEDEC JS-001-2012                | All Other Pins                                        | 2    |                      |      |

|                                   | Charged Device Model,<br>JEDEC JESD22-C101 | All Pins                                              | 2    |                      |      |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                  | Parameter                                                                                     |     | Max.     | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------|-----|----------|------|

| $V_{DD}$                | Battery Supply Voltage                                                                        | 2.5 | 4.5      | V    |

| V <sub>IO</sub>         | Parallel I/O Supply Voltage                                                                   |     | $V_{DD}$ | V    |

| T <sub>A</sub>          | Operating Temperature                                                                         |     | +85      | °C   |

| J_DET <sub>Audiof</sub> | Audio Frequency on J_DET Pin; V <sub>DD</sub> =2.4 to 4.5 V; DET= V <sub>OL</sub>             |     | 20000    | Hz   |

| $V_{SW}$                | MIC Switch Input Voltage Range                                                                |     | $V_{DD}$ | V    |

| J_DET <sub>AudioV</sub> | Audio Voltage on J_DET Pin                                                                    | -1  | 1        | V    |

| J_DET <sub>RL</sub>     | Maximum Resistance on Accessory Left Channel for Valid Attach / Audio Accessory Plug Inserted |     | 10       | kΩ   |

## **DC Electrical Characteristics**

All typical values are at T<sub>A</sub>=25°C, C<sub>IN\_VDD</sub>=1.0  $\mu$ F, and C<sub>IN\_VIO</sub>=0.1  $\mu$ F unless otherwise specified.

| Symbol                | Parameter                                                                           | V <sub>DD</sub> (V) | Conditions                                                  | $T_A = -40 \text{ to } +85^{\circ}\text{C}$ |      |                       | 11   |

|-----------------------|-------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------|---------------------------------------------|------|-----------------------|------|

|                       |                                                                                     |                     |                                                             | Min.                                        | Тур. | Max.                  | Unit |

| MIC Switch            |                                                                                     | •                   |                                                             | •                                           |      | •                     | •    |

| Ron                   | MIC Switch On Resistance                                                            | 3.8                 | I <sub>OUT</sub> =30 mA,<br>V <sub>IN</sub> =2.2 V          |                                             | 0.4  | 2.0                   | Ω    |

| R <sub>FLAT(ON)</sub> | On Resistance Flatness                                                              | 3.8                 | I <sub>OUT</sub> =30 mA,<br>V <sub>IN</sub> =1.6 V to 2.8 V |                                             | 0.30 | 1.50                  |      |

| I <sub>OFF</sub>      | Power-Off Leakage Current on MIC Pin                                                | 0                   | MIC=4.3 V                                                   |                                             |      | 1                     | μA   |

| Key Press             |                                                                                     |                     |                                                             |                                             |      |                       | •    |

| V <sub>TH_SE</sub>    | Key Detection Threshold                                                             | 2.5 to 4.5          | Detection<br>Threshold                                      | 0.60                                        |      |                       | V    |

| Parallel I/O (        | KP, INTB)                                                                           |                     |                                                             |                                             |      |                       |      |

| V <sub>OH</sub>       | Output High Voltage                                                                 |                     | Ι <sub>ΟΗ</sub> =-100 μΑ                                    | 0.8 × V <sub>IO</sub>                       |      |                       | V    |

| V <sub>OL</sub>       | Output Low Voltage                                                                  |                     | I <sub>OL</sub> =+100 μA                                    |                                             |      | 0.2 × V <sub>IO</sub> | ]    |

| I <sub>IN</sub>       | EN Input Leakage Current                                                            |                     |                                                             |                                             |      | 1                     | μΑ   |

| V <sub>IL</sub>       | Low-Level Input Voltage                                                             |                     |                                                             |                                             |      | 0.3 × V <sub>IO</sub> | V    |

| V <sub>IH</sub>       | High-Level Input Voltage                                                            |                     |                                                             | 0.7 × V <sub>IO</sub>                       |      |                       | V    |

| Current               |                                                                                     |                     |                                                             |                                             |      |                       |      |

| I <sub>DD-SLNA</sub>  | Battery Supply Sleep Mode<br>Current with No Accessory<br>Attached and LDO Disabled | 2.5 to 4.5          | Static Current<br>during Sleep<br>Mode                      |                                             | 1.5  | 3.0                   | μA   |

| I <sub>DD-SLWA</sub>  | Battery Supply Sleep Mode<br>Current with Accessory Attached                        | 2.5 to 4.5          | Active Current                                              |                                             | 20   | 30                    | μΑ   |

#### Note:

4. Refer to Figure 6 and  $R_{\text{KEY}}$  calculation.

#### **AC Electrical Characteristics**

All typical values are for  $T_A$ =25°C,  $C_{IN\ VDD}$ =1.0  $\mu F$ , and  $C_{IN\ VIO}$ =0.1  $\mu F$  unless otherwise specified.

| Symbol               | Parameter                                                                             | V <sub>DD</sub> (V) | Conditions                                                                  | Typical | Unit |  |  |

|----------------------|---------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------|---------|------|--|--|

| MIC Switch           | MIC Switch                                                                            |                     |                                                                             |         |      |  |  |

| THD+N                | Total Harmonic Distortion + Noise (Char)                                              | 3.8                 | $R_T$ =600 Ω, f=20 Hz to 20 kHz, $V_{MIC}$ =2.0 $V_{DC}$ +0.5 $V_{pp}$ Sine | 0.01    | %    |  |  |

| OIRR                 | Off Isolation                                                                         | 3.8                 | f=20 Hz to 20 kHz, Rs=RT=32 $\Omega$ , CL=0 pF                              | -85     | dB   |  |  |

| Timing Cha           | racteristics                                                                          |                     |                                                                             |         |      |  |  |

| t <sub>POLL</sub>    | ON Time of MIC Switch for<br>Sensing SEND / END Key Press<br>Oscillator Stable Time   | 2.5 to 4.5          | DET=V <sub>OL</sub> , EN=V <sub>IL</sub>                                    | 1       | ms   |  |  |

| t <sub>WAIT</sub>    | Period of MIC Switching for<br>Sensing SEND / END Key Press                           | 2.5 to 4.5          | DET=V <sub>OL</sub> , EN=V <sub>IL</sub>                                    | 10      | ms   |  |  |

| t <sub>DET_IN</sub>  | Debounce Time after J_DET Changes State from HIGH to LOW                              | 2.5 to 4.5          |                                                                             | 70      | ms   |  |  |

| t <sub>KBK</sub>     | Debounce Time for Sensing<br>SEND / END Key Press / Release                           | 2.5 to 4.5          |                                                                             | 30      | ms   |  |  |

| t <sub>DET_REM</sub> | Debounce Time from Changing<br>J_DET State from LOW to HIGH<br>to Detect Jack Removal | 2.5 to 4.5          |                                                                             | 30      | μS   |  |  |

| Power                | Power                                                                                 |                     |                                                                             |         |      |  |  |

| PSRR                 | Power Supply Rejection Ratio                                                          | 3.8                 | Power Supply Noise 300 mV <sub>PP</sub> , f=217 Hz                          | -90     | dB   |  |  |

## 10-Lead, Quad Ultrathin MLP (UMLP) Nominal Values

| JEDEC Symbol     | Description      | Nominal Values (mm) |

|------------------|------------------|---------------------|

| А                | Overall Height   | 0.5                 |

| A1               | Package Standoff | 0.026               |

| A3               | Lead Thickness   | 0.152               |

| b                | Lead Width       | 0.2                 |

| L                | Lead Length      | 0.4                 |

| е                | Lead Pitch       | 0.4                 |

| D                | Body Length (Y)  | 1.8                 |

| E Body Width (X) |                  | 1.4                 |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and h

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative