# **LP8765**

# **High Performance Power Management Unit for Handset Applications**

# **General Description**

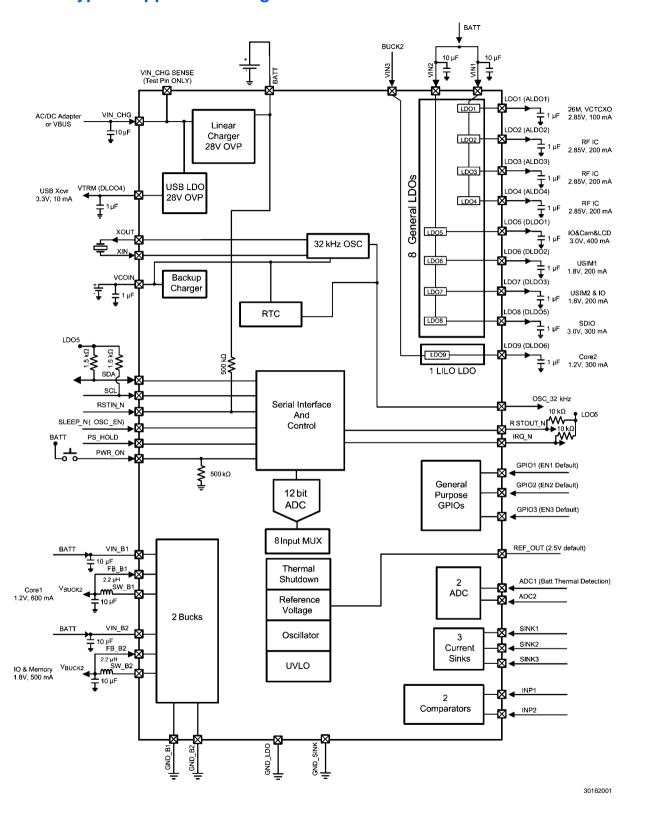

The LP8765 is a complete Power Management Unit (PMU) designed for handset applications. The LP8765 PMU contains a 28V Over-Voltage Protection (OVP) single-input linear Li-lon battery charger, backup battery charger, 10 low-dropout voltage regulators including 4 A-type LDOs, 4 D-type LDOs, one LILO LDO and one 28V OVP LDO, 2 high-efficiency buck regulators, 2 comparators, 3 current sinks, 12-bit ADC, real-time clock, 32 KHz OSC and one 2.5V reference output voltage. Programming is handled via a high-speed serial interface to program on/off conditions and output voltages of individual regulators, and to read status information of the PMU.

The LP8765 can safely charge and maintain a single cell Lilon battery operating from an AC adapter or USB power source

The Li-lon charger requires few external components and integrates the power FET. Charging is thermally regulated to obtain the most efficient charging rate for a given ambient temperature.

A built-in OVP circuit at the charger inputs protects the PMU from input voltages up to +28V, eliminating the need for any external protection circuitry.

Buck regulators have an automatic switch to PFM mode at low-load conditions providing very good efficiency at low-out-put currents.

A-type LDO regulators provide excellent PSRR and very low noise, 10  $\mu V$  typ., ideally suited for supplying voltage to RF section.

The real-time clock/calendar provides time interval information as well as two programmable alarms.

The current sink provides 4-bit current resolution with 6-bit PWM dimming, up to 120 mA maximum load current.

Two general-purpose comparators can be used for detecting external accessories like ear plugs, etc.

## **Features**

- Linear Li-Ion Battery Charger with Single Input 50 mA to 1200 mA Charging Current 4.05V to 4.75V Termination Voltage 28V OVP on the VIN\_CHG Input Charging from either AC Adaptor or USB

- Two Synchronous Magnetic Buck Regulators

I<sub>OUT</sub> 600 mA and 500 mA

High-efficiency PFM mode @ low I<sub>OUT</sub>

Auto-Mode PFM/PWM Switch

Programmable Peak Switching Current Limit

Low-Inductance 2.2 µH @2 MHz Switching Frequency

3% Accurate Buck Regulators up to 90% Efficiency

- LDOs

- 4 x A-type LDOs (3 x 200 mA, 1 x 100 mA) 4 x D-type LDOs (2 x 200 mA, 1 x 300 mA, 1 x 400 mA) 1 x LILO LDO (1 x 300 mA) 1 x 28V OVP LDO for USB Transceiver (1 x 10 mA) 10 μV noise on A-type LDOs 2% typ. Output Voltage Accuracy on LDOs

- 12-bit A/D Converter

- Three Controllable Current Sinks

- Two Comparators

- Interrupt Request to Reduce S/W Polling

- 32.786 KHz OSC

- Real-Time Clock with Two Programmable Alarms

- Thermal Shutdown with Early Warning Alarm

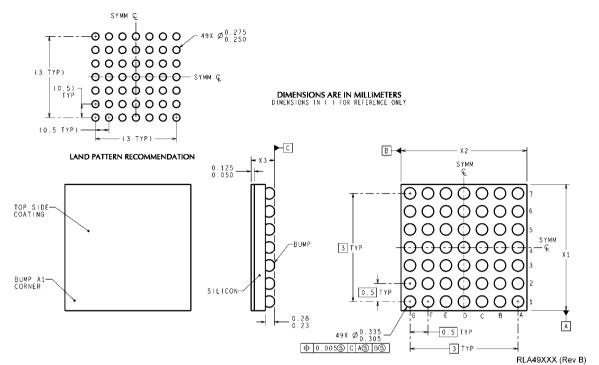

- 49-bump micro SMD package 3.7 x 3.7 mm, 0.5 mm pitch

# **Applications**

■ GSM, GPRS, EDGE, CDMA & 3G Handsets

# **Table of Contents**

| General Description                              |    |

|--------------------------------------------------|----|

| Features                                         | 1  |

| Applications                                     |    |

| General Typical Application Diagram              | 3  |

| Device Pin Diagram                               | 4  |

| Package Marking Information                      | 4  |

| Ordering Information                             |    |

| LP8765 Pin Descriptions                          | 5  |

| Device Operation Description                     | 6  |

| OPERATION MODES                                  | 6  |

| POWER-ON AND POWER-OFF SEQUENCES                 | 8  |

| Support Functions                                | 10 |

| REFERENCE                                        | 10 |

| OSCILLATOR                                       |    |

| REFERENCE VOLTAGE (2.5V)                         | 10 |

| OPERATING VOLTAGE MONITOR                        | 10 |

| THERMAL SHUTDOWN                                 |    |

| Absolute Maximum Ratings                         |    |

| Operating Ratings (Note 1, Note 2)               | 11 |

| Operating natings (Note 1, Note 2)               | 11 |

| Thermal Properties                               | 11 |

| General Electrical Characteristics               | 11 |

| Linear Li-lon Battery Charger with Single Input  |    |

| CHARGER FUNCTION                                 | 13 |

| END-OF-CHARGE (EOC) FUNCTION                     | 13 |

| EOC & BATTERY DEFAULT SETTING                    | 13 |

| HIGH-CURRENT MODE                                |    |

| Buck Converters                                  |    |

| CIRCUIT OPERATION                                |    |

| PWM OPERATION                                    |    |

| PFM OPERATION                                    | 15 |

| INTERNAL SYNCHRONOUS RECTIFICATION               |    |

| CURRENT LIMITING                                 |    |

| SOFT-START                                       | 16 |

| LOW-DROPOUT OPERATION                            | 16 |

| LDO's                                            |    |

| A/D Converter                                    | 21 |

| A/D CONVERTER DATA AND CONTROL REGISTERS         | 21 |

| MEASUREMENT RESULT CALCULATION                   | 21 |

| WORKING RANGE AND ACCURACY                       |    |

| S&H                                              | 21 |

| Real-Time Clock                                  | 22 |

| RTC UNLOCK FUNCTION                              | 22 |

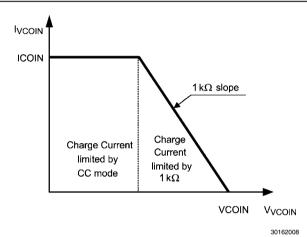

| Backup Battery Charger                           |    |

| 32.768 kHz Crystal Oscillator                    | 23 |

| Comparators                                      |    |

| 3 Current Sinks                                  | 25 |

| SINK DRIVERS                                     | 25 |

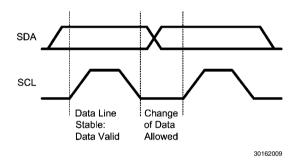

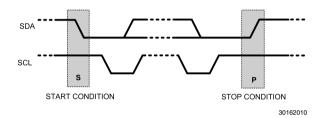

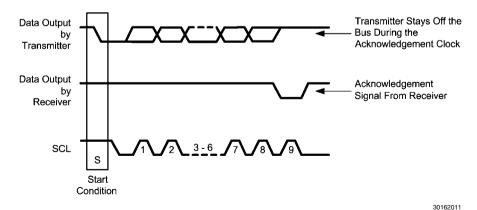

| I <sup>2</sup> C-Compatible Serial Bus Interface |    |

| INTERFACE BUS OVERVIEW                           |    |

| DATA TRANSACTIONS                                | _  |

| START AND STOP                                   |    |

| ACKNOWLEDGE CYCLE                                |    |

| Physical Dimensions                              |    |

# **General Typical Application Diagram**

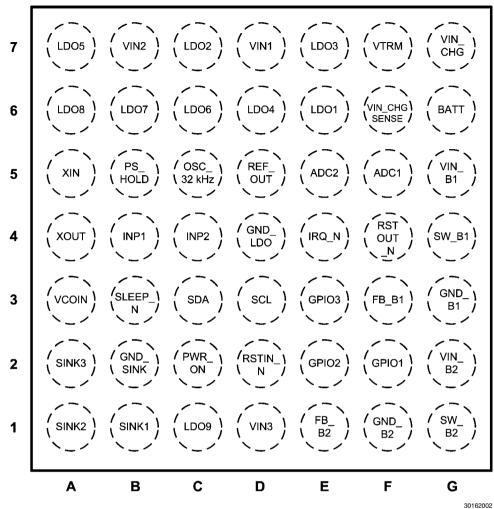

# **Device Pin Diagram**

TOP VIEW 49-Bump (0.5 mm pitch) micro SMDxt Package

# **Package Marking Information**

XY = 2 Digit Date Code TT = 2 Digit Die Run Trace Code 8765 = Product Identification

30162003

# **Ordering Information**

| Order Number | Package Type      | Product ID | Supplied As              |

|--------------|-------------------|------------|--------------------------|

| LP8765RLE    | micro SMD xT      | 9765       | 250 Units on Tape & Reel |

| LP8765RLX    | ILLICIO PINID X I | 8765       | 1000 Units onTape & Reel |

# **LP8765 Pin Descriptions**

| Pin# | Name          | Туре | Description                                                                         |

|------|---------------|------|-------------------------------------------------------------------------------------|

| F5   | ADC1          | Α    | ADC input for Battery thermal NTC thermal monitor, also used for battery detection. |

| E5   | ADC2          | Α    | Reserved Pin for external ADC usage                                                 |

| G6   | BATT          | Р    | Main Battery connection                                                             |

| F3   | FB_B1         | Α    | Buck1 feedback                                                                      |

| E1   | FB_B2         | Α    | Buck2 feedback                                                                      |

| G3   | GND_B1        | G    | Buck1 GND                                                                           |

| F1   | GND_B2        | G    | Buck1 GND                                                                           |

| D4   | GND_LDO       | G    | LDOs GND                                                                            |

| B2   | GND_SINK      | G    | SINKs GND                                                                           |

| F2   | GPIO1         | DI   | Used for Enable1                                                                    |

| E2   | GPIO2         | DI   | Used for Enable2                                                                    |

| E3   | GPIO3         | DI   | Used for Enable3                                                                    |

| B4   | INP1          | DI   | Comparator Input1                                                                   |

| C4   | INP2          | DI   | Comparator Input1                                                                   |

| E4   | IRQ_N         | DO   | Interrupt output, active low (Open Drain)                                           |

| E6   | LDO1          | Α    | LDO1 output                                                                         |

| C7   | LDO2          | Α    | LDO2 output                                                                         |

| E7   | LDO3          | Α    | LDO3 output                                                                         |

| D6   | LDO4          | Α    | LDO4 output                                                                         |

| A7   | LDO5          | Α    | LDO5 output                                                                         |

| C6   | LDO6          | Α    | LDO6 output                                                                         |

| В6   | LDO7          | Α    | LDO7 output                                                                         |

| A6   | LDO8          | Α    | LDO8 output                                                                         |

| C1   | LDO9          | Α    | LDO9 output                                                                         |

| C5   | OSC_32KHz     | Α    | 32 KHz clock buffer output to BB                                                    |

| B5   | PS_HOLD       | DI   | Control input from BB                                                               |

| C2   | PWR_ON        | DI   | Power switch on input                                                               |

| D5   | REF_OUT       | Α    | 2.5V reference output for ADC (load current should be less than 1mA)                |

| D2   | RSTIN_N       | DI   | Reset input, active low                                                             |

| F4   | RSTOUT_N      | DO   | Reset output, active low (Open Drain)                                               |

| D3   | SCL           | DI   | Serial interface clock input, external pull up 1.5K to LDO5                         |

| C3   | SDA           | DI/O | Serial interface bi-directional data, external pull up 1.5K to LDO5                 |

| B1   | SINK1         | Α    | Current Sink1 Input                                                                 |

| A1   | SINK2         | Α    | Current Sink2 Input                                                                 |

| A2   | SINK3         | Α    | Current Sink3 Input                                                                 |

| В3   | SLEEP_N       | DI   | Sleep Mode input, active low                                                        |

| G4   | SW_B1         | Α    | Buck1 switch note                                                                   |

| G1   | SW_B2         | Α    | Buck2 switch note                                                                   |

| A3   | VCOIN         | Α    | Backup battery connection                                                           |

| G5   | VIN_B1        | Α    | Buck1 input                                                                         |

| G2   | VIN_B2        | Α    | Buck2 input                                                                         |

| G7   | VIN_CHG       | Р    | DC power input to charger block (AC adaptor or USB)                                 |

| F6   | VIN_CHG SENSE | DO   | VIN_CHG pin testing point (test purpose only) and leave this pin floating.          |

| D7   | VIN1          | Α    | LDOs Input1                                                                         |

| B7   | VIN2          | Α    | LDOs Input2                                                                         |

| D1   | VIN3          | Α    | LILO LDO input                                                                      |

| F7   | VTRM          | Α    | 3.3V LDO output for USB transceiver                                                 |

| Pin # | Name | Туре | Description                     |

|-------|------|------|---------------------------------|

| A5    | XIN  | Α    | External crystal oscillator IN  |

| A4    | XOUT | Α    | External crystal oscillator OUT |

A: Analog Pin D: Digital Pin I: Input Pin DI/O: Digital Input/Output Pin O: Output Pin P: Power Pin

G: Ground

# **Device Operation Description**

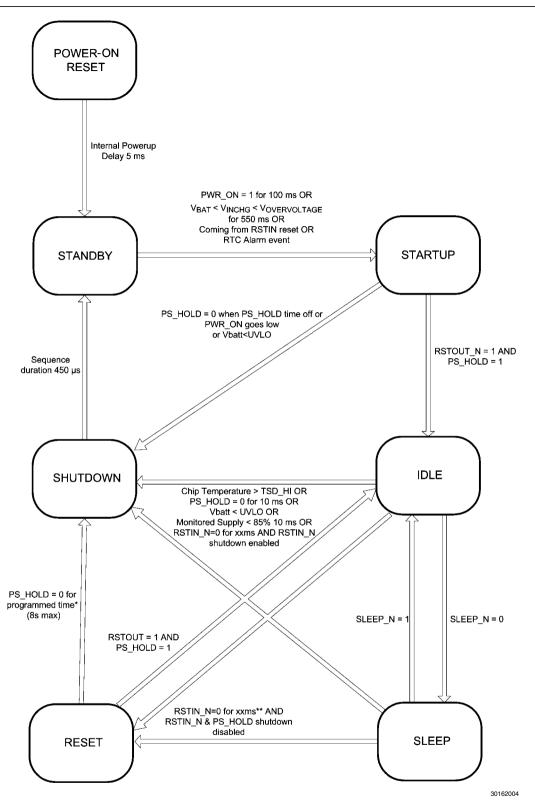

## **OPERATION MODES**

POWER-ON-RESET: In POWER-ON RESET mode all internal registers are reset to the default values.

STANDBY: In STANDBY mode all PMU functions are disabled except BB charger, 32 KHz OSC & RTC.

START UP: Startup sequence is triggered by setting Power-on-Switch (PWR ON) high for 100 ms or connecting a

suitable voltage to charger input (VIN\_CHG). For RTC ALARM events the startup sequence begins after 2ms delay from the RTC events. During the startup sequence, the 2.5V reference voltage will be powered by either charger block or battery first in order to detect battery existing. If there is a battery and the battery voltage is over OPVM, then the default on regulators (Buck1, Buck2 & LDO5) will be enabled according to a pre-programmed timing pattern. If the regulators are enabled, RSTOUT\_N is released, allowing the processor to start up. PS\_HOLD must be set high within a programmed timer\* (8s max) from the start of STARTUP state; this is true for all startup events except PWR\_ON. For PWR\_ON startup, PMU stays in POWER ON state when PWR\_ON is held high, and the PS\_HOLD must be set high before the PWR\_ON

goes low or Power-on-Switch is released. Otherwise, PMU will go to SHUTDOWN state.

If there is no main battery detected (voltage at ADC1 pin is about 2.4V), PMU will not start the startup sequence. In other modes, the PMU will not enable the charger. If the main battery is removed when PMU is running, then Charger will be disabled immediately to force UVLO shutdown.

If two-pin battery is used then ADC1 pin should be connect to GND through a resistor or floating in order to start up the PMU normally. However, there will be no battery exiting detection.

IDLE: PMU will enter into IDLE mode (normal operating mode) after PS\_HOLD signal is asserted by the host

processor. IDLE mode will enable all PMU functions that can be controlled by the Serial Interface or direct control inputs. PS\_HOLD going low for 10 ms, VDD voltage below UVLO, Chip temperature over TSDH,

or a flag failure in a monitored regulator (LDO5) for 10 ms will initiate a SHUTDOWN Sequence.

SLEEP: When BB pulls SLEEP\_N pin LOW, the PMU will not do anything except setting BUCKs and LDOs to low-

power mode in order to minimize quiescent current if LDOs\_LOW\_PWR\_IN\_SLEEP and BUCKs\_LOW\_PWR\_IN\_SLEEP bits are set to 1, otherwise both BUCKs and LDOs will stay in normally mode. However, in low-power mode, the summary of total load current of BUCKs or LDOs should stay below 5mA. Buck1 has two preset voltages (BUCK1 NORMAL & BUCK1 SLEEP); BUCK1 output equals BUCK1 SLEEP when SLEEP\_N pin is low, and goes back to BUCK1 NORMAL when SLEEP\_N is high. By default, BUCK1 SLEEP & NORMAL are same 1.2V. In this mode, only LDO1, LDO2, LDO3, LDO4 and LDO9 can be enabled/disabled through GPIO pins (EN1,2&3). If I²C communication is disabled during sleep, then for other power regulators, BB need to turn them off through I²C before SLEEP\_N goes to 0. Otherwise, these power regulators will stay on during BB sleep. The condition of going to SHUTDOWN

state is the same as in IDLE state. Please see Register Maps for detail.

SHUTDOWN: In this state, RSTOUT\_N is pulled low, and all regulators are disabled according to pre-programmed timing

pattern (opposite of STARTUP sequence). After this, all registers are reset to default values except address

xxxx, then PMU will go to STANDBY state.

SYSTEM RESET: PMU goes to SYSTEM RESET mode if RSTIN\_N input has been pulled low for xxms\*\*. There are two different reset methods:

6

1. Cold reset (EN\_RSTIN\_SHUTDOWN = high); PMU will go to SHUTDOWN state first and then initiate STARTUP event automatically. PS\_HOLD must be high within programmed PS\_HOLD timer, otherwise

- PMU will go to SHUTDOWN state.

a. Enable shutdown and enter EPROM READ + PREPARE mode, active the pulldown (Total time = 33 ms);

- b. Disable the pulldown and enter STARTUP mode:

- c. Wait 100 ms; and

- d. Enter Normal working mode.

- 2. Hot reset (EN\_RSTIN\_SHUTDOWN = low); PMU will pull low RSTOUT\_N and disable all the power regulators except BUCK1, BUCK2, LDO5(DLDO1), REF\_OUT. A STARTUP event then initiates automatically, and PS\_HOLD must be high within programmed PS\_HOLD timer, otherwise PMU will go to SHUTDOWN state.

- \* Note 1: PS\_HOLD timer is programmable 1.5s, 2s, 4s, and 8s.

- $^{\star\star}$  Note 2: RSTIN\_N timer is programmable 0.5 ms, 1.0 ms, 2.0 ms 33 ms.

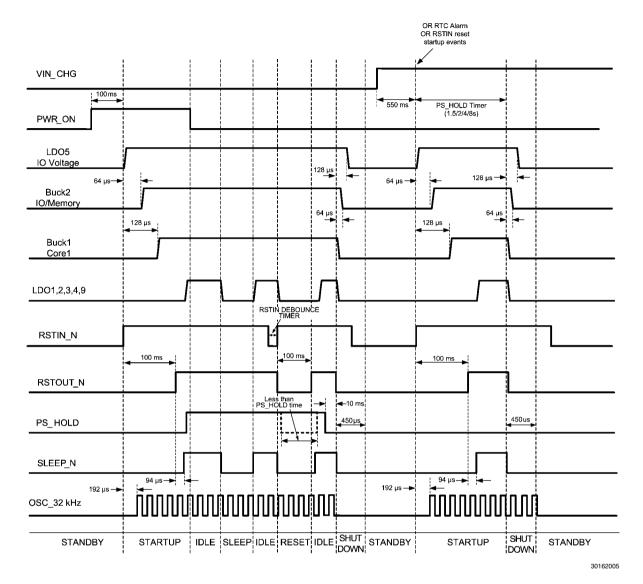

## **POWER-ON AND POWER-OFF SEQUENCES**

Default on power rail startup sequence: 2.5V reference voltage→LDO5 → Buck2 → Buck1.

Power-Off sequence is in reverse order of startup sequences.

## LP8765 POWER REGULATOR SPEC TABLE

| Outputs      | Loads              | Voltage<br>Range (V) | Default<br>Voltage<br>(V) | Current<br>Rating<br>[mA] | Default<br>ON (Y/N) | Turn-on<br>Sequence                                | Voltage<br>Steps<br>(mV) | ON/OFF<br>Control      |  |

|--------------|--------------------|----------------------|---------------------------|---------------------------|---------------------|----------------------------------------------------|--------------------------|------------------------|--|

| BUCK1        | Core1              | 0.8 - 1.45           | 1.2                       | 600                       | Υ                   | T0+128µs                                           | 50                       | S/I(always on)         |  |

| BUCK2        | IO&Memory          | 0.8 - 2.1            | 1.8                       | 500                       | Υ                   | T0+64µs                                            | 50                       | S/I(always on)         |  |

| LDO1 (ALDO1) | 26M, VCTCXO        | 1.5 - 3.0            | 2.85                      | 100                       | N                   | -                                                  | 50                       | S/I AND GPIO1<br>(EN1) |  |

| LDO2 (ALDO2) | RF IC              | 1.5 - 3.0            | 2.85                      | 200                       | N                   | -                                                  | 50                       | S/I AND GPIO1<br>(EN1) |  |

| LDO3 (ALDO3) | RF IC              | 1.5 - 3.0            | 2.85                      | 200                       | N                   | -                                                  | 50                       | S/I OR GPIO1<br>(EN1)  |  |

| LDO4 (ALDO4) | RF IC              | 1.85 - 3.4           | 2.85                      | 200                       | N                   | -                                                  | 50                       | S/I AND GPIO2<br>(EN2) |  |

| LDO5 (DLDO1) | IO&Cam&LCD         | 1.5 - 3.3            | 3                         | 400                       | Υ                   | T0                                                 | 100                      | S/I(always on)         |  |

| LDO6 (DLDO2) | USIM1              | 1.8 or 3.0           | 1.8                       | 200                       | N                   | -                                                  | -                        | S/I                    |  |

| LDO7 (DLDO3) | USIM2&IO           | 1.5 - 3.3            | 1.8                       | 200                       | N                   | -                                                  | 100                      | S/I                    |  |

| VTRM (DLDO4) | USB Xcvr           | 3.3 fixed            | 3.3                       | 10                        | Y                   | Always as<br>long as the<br>USB/Adaptor<br>plugged | -                        | S/I                    |  |

| LDO8 (DLDO5) | SDIO               | 1.5 - 3.3            | 3                         | 300                       | N                   | -                                                  | 100                      | S/I                    |  |

| LDO9 (DLDO6) | Core2              | 0.8 - 1.5            | 1.2                       | 300                       | -                   | -                                                  | 50                       | S/I AND GPIO3<br>(EN3) |  |

| REF_OUT      | ADC<br>Ref_Voltage | 2.5                  | 2.5                       | 1                         | Y                   | Always                                             | -                        | S/I(always on)         |  |

# **Support Functions**

#### REFERENCE

LP8765 has an internal reference block creating all necessary references and biasing for all blocks.

#### **OSCILLATOR**

There is an internal oscillator giving clock to the bucks and to logic control (2MHz typ.).

## **REFERENCE VOLTAGE (2.5V)**

| Parameter | Тур. | Min.       | Max.   | Load<br>(typ.) |

|-----------|------|------------|--------|----------------|

| REF_OUT   | 2.5V | 2.425<br>V | 2.575V | 100 μΑ         |

#### **OPERATING VOLTAGE MONITOR**

There is Operating Voltage Monitor (OPVM) that checks VDD-pin voltage before starting Power-On sequence. OPVM is also checked during Power-On sequence. If the VDD voltage is less than OPVM threshold LP8765 will not power on. After LP8765 successfully passed Power-On sequence OPVM is not monitored.

| Parameter      | Тур. | Min. | Max. | Unit |

|----------------|------|------|------|------|

| OPVM threshold | 3.1  | 3.0  | 3.25 | V    |

#### THERMAL SHUTDOWN

The Thermal Shutdown (TSD) function monitors the chip temperature to protect the chip from temperature damage caused, e.g. by excessive power dissipation. The temperature monitoring function has two threshold values that result in protective actions. When a lower threshold of +125°C is exceeded, the TSDL bit in the Register 0x08 will be set and an "early warning" interrupt, unless masked, is generated to the processor. A read operation on the TSDL bit will reset it if the temperature has decreased to lower than 10°C below the threshold. If the temperature exceeds a higher threshold value of +160°C, the TSDH bit in the Register 0x08 is set, and the chip will automatically go to the Power-Off sequence. A read operation on the TSDH bit will reset it. Power On can be activated only if the junction temperature is less than the early warning lower threshold +115°C.

| Parameter                  | Тур. | Unit |

|----------------------------|------|------|

| Higher Threshold*)         | 160  |      |

| Early Warning*)            | 125  | °C   |

| Early Warning Hysteresis*) | 10   |      |

<sup>\*)</sup> Guaranteed by design.

# **Absolute Maximum Ratings** (Note 1, Note

**2**)

ESD (Note 4)

VIN\_CHG, BATT, GND,

ADC1&2, PWR\_ON, RSTIN\_N

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| VIN_CHG, VIN_CHG SENSE                                  | -0.3V to $+28V$                       |

|---------------------------------------------------------|---------------------------------------|

| V <sub>BATT</sub> , VIN1, VIN2, VIN_B1,<br>VIN_B2       | -0.3V to +6V                          |

| VIN3                                                    | -0.3 to +4.5V                         |

| VCOIN                                                   | -0.3V to $+4V$                        |

| SINK1&2                                                 | $-0.3V$ to $V_{BATT}+0.5V$ and $< 6V$ |

| SINK3                                                   | -0.3V to 10V                          |

| All other input-only pins                               | $-0.3V$ to $V_{BATT}+0.3V$ , max $6V$ |

| Junction Temperature $(T_{J-MAX})$                      | 150°C                                 |

| Storage Temperature                                     | -40 to 150°C                          |

| Maximum Continuous Power Dissipation P <sub>D-MAX</sub> | ( <i>Note 3</i> )                     |

# **Operating Ratings** (Note 1, Note 2)

| VIN_CHG (Note 10)                            | 4.5V to 6.8V       |

|----------------------------------------------|--------------------|

| BATT                                         | 3.0V to 5.5V       |

| VCOIN                                        | 2.0V to 3.6V       |

| VIN1, VIN2, VIN_B1, VIN_B2                   | 2.5V to $V_{BATT}$ |

| VIN3                                         | 0.7V to 4.5V       |

| All input-output pins                        | 0V to $V_{BATT}$   |

| Junction Temperature (T <sub>J</sub> ) Range | -40°C to +125°C    |

| Ambient Temperature (T <sub>A</sub> )        | -40°C to +85°C     |

| Maximum Power Dissipation ( <i>Note 5</i> )  | 1.4W               |

# **Thermal Properties**

(Note 9)

Junction-to-Ambient Thermal

Resistance ( $\theta_{1\Delta}$ ) 38.6°C/W

(Jedec Standard Thermal PCB)

# **General Electrical Characteristics**

## **CURRENT CONSUMPTION**

8 kV HBM

2 kV HBM

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN3}$ = $V_{VIN_B1}$ = $V_{VIN_B2}$ ) =3.7V, GND (=GND\_B1=GND\_B2=GND\_LDO=GND\_SINK) =0V,  $C_{VIN_CHG}$ = $C_{VIN_B}$ 1= $C_{VIN_B2}$ = $C_{BUCK}$ 1= $C_{BUCK2}$ = $C_{VIN_1}$ = $C_{VIN_2}$ =10  $\mu$ F,  $C_{LDO_x}$ = $C_{VTRM}$ = $C_{COIN}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$ =25°C. Limits appearing in  $T_J$ =0°C to +125°C. (*Note 6*)

| Symbol                  | Parameter                     | Conditions                  | Tvn | Limit |     | Units  |

|-------------------------|-------------------------------|-----------------------------|-----|-------|-----|--------|

| Symbol                  |                               | Conditions                  | Тур | Min   | Max | Ullits |

|                         | Battery Standby Current       | COIN on, no load            | 35  |       |     |        |

| <sup>I</sup> Q(STANDBY) | Battery Standby Current       | COIN off, no load           | 4   |       |     | uА     |

|                         | Battery Current in SLEEP Mode | SLEEP_EN=LOW (Buck1, Buck2, | 165 |       |     | μΛ     |

| <sup>I</sup> Q(SLEEP)   | @ 0 load                      | LDO5, COIN & REF_OUT on)    | 100 |       |     |        |

#### **LOGIC AND CONTROL**

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN3}$ = $V_{VIN_B}$ = $V_{VIN$

| Symbol                   | Parameter Conditions | Conditions | Тур | Limit |      | Units |  |  |

|--------------------------|----------------------|------------|-----|-------|------|-------|--|--|

|                          |                      | Conditions |     | Min   | Max  | Units |  |  |

| Logic and Control Inputs |                      |            |     |       |      |       |  |  |

| V <sub>IL</sub>          | Input Low Level      | PWR ON     |     |       | 0.9  | V     |  |  |

| V <sub>IH</sub>          | Input High Level     | TEVA_ON    |     | 1.5   |      | V     |  |  |

| V <sub>IL</sub>          | Input Low Level      | GPIO1-3    |     |       | 0.4  | V     |  |  |

| V <sub>IH</sub>          | Input High Level     | GFIO1-3    |     | 1.3   |      | V     |  |  |

| V <sub>IL</sub>          | Input Low Level      | CDA COI    |     |       | 0.35 | V     |  |  |

| V <sub>IH</sub>          | Input High Level     | SDA,SCL    |     | 1.3   |      | V     |  |  |

11

| 0                 | Dawa wa atau       | O and distance                                                                 | T   | Lin            | Limit          |       |  |

|-------------------|--------------------|--------------------------------------------------------------------------------|-----|----------------|----------------|-------|--|

| Symbol            | Parameter          | Conditions                                                                     | Тур | Min            | Max            | Units |  |

| V <sub>IL</sub>   | Input Low Level    | CLEED N. DC. HOLD, DCTIN N.                                                    |     |                | 0.2*<br>VLDO5  | V     |  |

| V <sub>IH</sub>   | Input High Level   | SLEEP_N, PS_HOLD, RSTIN_N                                                      |     | 0.7* VLD<br>O5 |                | V     |  |

| I <sub>LEAK</sub> | Input Current      | SDA, SCL, SLEEP_N, PS_HOLD,<br>GPIO1-3 0V <v<sub>IN<v<sub>BATT</v<sub></v<sub> |     | -5             | +5             | μΑ    |  |

| R <sub>IN</sub>   | Input Resistance   | RSTIN_N, PWR_ON                                                                | 500 |                |                | kΩ    |  |

| Logic and Co      | ontrol Outputs     |                                                                                |     |                |                |       |  |

| V <sub>OL</sub>   | Output Low Level   | SDA, IRQ_N, RESTOUT_N, I <sub>OL</sub> = 2mA ( <i>Note 7</i> )                 |     |                | 0.15*<br>VLDO5 | V     |  |

| V <sub>OH</sub>   | Output High Level  | SDA I <sub>OH</sub> = 2mA ( <i>Note 7</i> )                                    |     | 0.75*<br>VLDO5 |                | V     |  |

| I <sub>OH</sub>   | Open Drain Leakage | IRQ_N, RSTOUT_N, V <sub>OH</sub> =V <sub>LDO5</sub> = 3V                       |     |                | 1              | μΑ    |  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: Internal thermal shutdown circuitry protects the device from permanent damage. .

Note 4: The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin. MIL-STD-883 3015.7

Note 5: Care must be exercised where high power dissipation is likely. The maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP})$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction to ambient thermal resistance of the package in the application  $(\theta_{JA})$ . This relationship is given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 6: All limits are guaranteed. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 7: Guaranteed by design.

Note 8: Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

Note 9: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design

Note 10: Full charging current is guaranteed for CHG\_IN = 4.5 to 6.8V, but particularly at higher input voltages. Increased power dissipation may cause the thermal regulation to limit the current to a safe level, resulting in longer charging time.

Note 11: Buck output voltage accuracy depends on the accuracy of the external feedback resistors. Resistor values should be chosen for the divider network to ensure that at the desired output voltage the FB pin is at the specified value of VOUT. See Buck Converter Application Information.

# Linear Li-Ion Battery Charger with Single Input

LP8765 has a built-in Li-Ion/Li-Poly battery management system. Its main features are:

- Single input AC adapter or USB

- CC/CV linear charging

- Selectable battery regulation voltage

- · Flexible charging cycle control

- Wide array of charging current

- Safetv timer

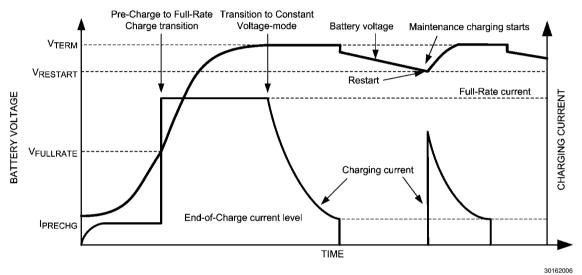

#### **CHARGER FUNCTION**

After detecting stable voltage on input (Put 10 µF 35V rated capacitor at input), charger enters pre-charge mode. In this mode battery is charged with pre-charge current until battery voltage reaches full-rate threshold. Now full charging current

is applied to the battery, until termination voltage is reached. After that, charger enters constant voltage mode, where constant battery voltage is maintained.

## **END-OF-CHARGE (EOC) FUNCTION**

This function ends the charging cycle if charger has reached constant voltage mode. It has automatic and manual control possibilities. Automatic EOC is enabled if AUTOMATIC START/STOP bit is set to 1, otherwise manual control is used.

Automatic EOC measures charging current and compares it to selected EOC current level. If charging current drops below EOC current threshold, then charging cycle is ended. It is also possible to set EOC time delay. This is the duration for which charging current must be below EOC level before charging ends. For manual EOC write '1' to STOP CHARGING in register 0x39 to stop charging, and write '1' to START CHARGING in register 0x39 to start charging again. These two bits are WRITE ONLY, and only one bit can be set to '1' at a time.

#### **EOC & BATTERY DEFAULT SETTING**

By default the EOC and Battery Detection Function will be disabled/masked off (2 EOC bits = 00) in order to support factory testing or software downloading without the main battery. in a normal customer usage, the BB processor should enable the EOC and Battery detection through the I<sup>2</sup>C after the system startup.

## **HIGH-CURRENT MODE**

The high-current mode should be used only during factory test, and there are few limitations since it is an add-on feature after the LP8765 was defined.

Once the high-current mode is enabled by programming the 2 MSB of ICHARGE to 11, three charger functions will be disabled:

- 1. Charger current limit

- 2. Battery voltage OVP (4.9V)

- 3. Charger Thermal regulation (115°C)

This high-current mode is not guaranteed to operate normally if the load is too high or with fast dynamic changes due to the following limitations:

- There is only one bump assigned for VBATT, so the maximum DC load is 1.5A.

- 2. The charger output will vary when load step is applied since there is no main battery connected.

## **CHARGER ELECTRICAL CHARACTERISTICS**

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN2}$ = $V_{VIN_B1}$ = $V_{VIN_B2}$ )=3.7V, GND (=GND\_B1=GND\_B2=GND\_LDO=GND\_SINK) =0V,  $C_{VIN\_CHG}$ = $C_{VIN_B1}$ = $C_{VIN_B2}$ = $C_{BUCK2}$ = $C_{VIN1}$ = $C_{VIN2}$ =10  $\mu$ F,  $C_{LDOx}$ = $C_{VTRM}$ = $C_{COIN}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for T<sub>J</sub>=25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, T<sub>J</sub>= -40°C to +125°C. (*Note 6, Note 9*)

| Cumbal                 | Parameter Conditions                               | Turn                                                                                                             | Lit  | mit   | Units |       |

|------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|

| Symbol                 |                                                    | Conditions                                                                                                       | Тур  | Min   | Max   | Units |

| V <sub>CHG_IN</sub>    | AC wall adapter input voltage operating range      |                                                                                                                  |      | 4.5   | 6.7   | V     |

| V <sub>OK_CHG</sub>    | CHG_IN OK Trip Point                               | V <sub>CHG_IN</sub>                                                                                              | 150  |       |       | mV    |

|                        | <u> </u>                                           | V <sub>CHG_IN</sub>                                                                                              | 40   |       |       |       |

|                        | Battan, abaraina tarminatian                       | V <sub>TERM</sub> = 4.2V, I <sub>CHG</sub> = 50 mA                                                               |      | -0.35 | +0.35 |       |

| V <sub>TERM</sub>      | Battery charging termination Voltage               | $\rm V_{\rm TERM}$ is measured at 10% of the programmed $\rm I_{\rm CHG}$ current                                |      | -1    | +1    | %     |

| I <sub>CHG</sub>       | CHG_IN programmable full-<br>rate charging current | $6.8V \ge V_{CHG} \ge 4.5V$ $V_{BATT} < V_{CHG-IN} - V_{OK\_CHG}$ $V_{FULLRATE} < V_{BATT} < V_{TERM} (Note 10)$ |      | 50    | 1200  | mA    |

|                        | Full-rate charging current tolerance               | I <sub>CHG</sub> = 400 mA                                                                                        |      | -10   | +10   | %     |

| I <sub>PREEQUAL</sub>  | Pre-charging current                               | 2.2V < V <sub>BATT</sub> < V <sub>FULL_RATE</sub>                                                                | 50   | 20    | 80    | mA    |

| V <sub>FULL_RATE</sub> | Full-rate qualification threshold                  | V <sub>BATT</sub> rising, transition from pre-charging to full-rate charging                                     | 2.8  | 2.7   | 2.9   | V     |

| I <sub>EOC</sub>       | End-of-charge current, % of full-rate current      | 0.1C option selected                                                                                             | 10   |       |       | %     |

| V <sub>RESTART</sub>   | Restart threshold voltage                          | From V <sub>TERM</sub> voltage (4.2V - 100 mV option selected)                                                   | -100 | -70   | -130  | mV    |

| C <sub>BATT</sub>      | Capacitance on BATT                                | (Note 7)                                                                                                         | ·    | 30    | 1000  | μF    |

| T <sub>REG</sub>       | Regulated junction temperature                     | (Note 7)                                                                                                         | 115  |       |       | °C    |

## **Buck Converters**

The LP8765 contains two high-efficiency step-down DC-DC switching buck converters, capable of delivering a constant voltage from a single Li-Ion battery. Using a voltage mode architecture with synchronous rectification, the LP8765 has the ability to deliver up to 600 mA (Buck1) and 500 mA (Buck2) depending on the input voltage, the output voltage, the ambient temperature, and the inductor chosen.

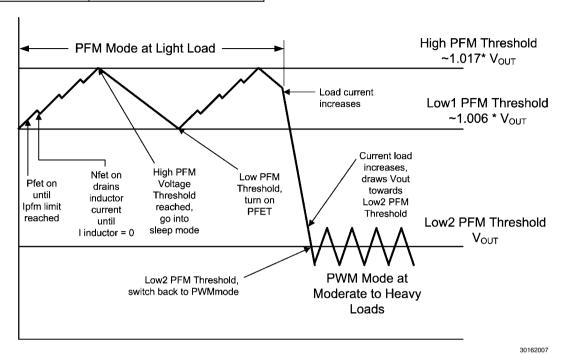

There are two modes of operation depending on the current required: PWM and PFM. PWM mode handles current loads of approximately 70 mA or higher, delivering voltage precision of  $\pm 3\%$  with up to 90% efficiency or better. Lighter output current loads cause the device to automatically switch into PFM for reduced current consumption (I $_{\rm Q}=16\,\mu{\rm A}$  typ.) and a longer battery life. User can force the buck converters to PWM mode by setting FORCE PWM BUCKx bit in Control Register.

Besides PFM power-saving feature, the buck regulators inside the LP8765 also have low-power operation mode, which has lower current consumption compare to PFM. The low-power mode can be enabled when SLEEP\_N pin goes low if control bit BUCKS LOW PWR IN SLEEP = 1. However, the total load capability of bucks will be limited to 5mA when they operate at low-power mode. The buck regulators inside the LP8765 can operate up to a 100% duty cycle (PFET switch always on) for low-dropout control of the output voltage. In this way the output voltage will be controlled down to the lowest possible input voltage.

#### **CIRCUIT OPERATION**

During the first portion of each switching cycle, the control block in the buck regulator turns on the internal PFET switch. This allows current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of  $(V_{\rm IN} - V_{\rm OUT})/L$  by storing energy in a magnetic field. During the second portion of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the NFET synchronous rectifier on. The inductor draws current from ground through the NFET to the output filter capacitor and load, which ramps the inductor current down with a slope of  $-V_{\rm OUT}/L$ . The output filter stores charge when the inductor current is high, and releases it when low, smoothing the voltage across the load.

Modulating the PFET switch-on time to control the average current sent to the load regulates the output voltage. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at the SW pin to a low-pass filter formed by the inductor and output filter capacitor. The output voltage is equal to the average voltage at the SW pin.

#### **PWM OPERATION**

During PWM operation the converter operates as a voltagemode controller with input voltage feed forward. This allows the converter to achieve good load and line regulation. The DC gain of the power stage is proportional to the input voltage. To eliminate this dependence, feed forward inversely proportional to the input voltage, is introduced.

While in PWM mode, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control power to the load. At the beginning of each clock cycle the PFET switch is turned on and the inductor current ramps up until the comparator trips and the control logic turns off the switch. The current limit comparator can also turn off the switch in case the current limit of the PFET is exceeded. In this case the NFET switch is turned on and the inductor current ramps down. The next cycle is initi-

ated by the clock turning off the NFET and turning on the PFET.

#### **PFM OPERATION**

At very light loads, the converter enters PFM mode and operates with reduced switching frequency and supply current to maintain high efficiency. The part will automatically transition into PFM mode when either of two conditions occurs for a duration of 32 or more clock cycles:

- 1. The inductor current becomes discontinuous; or

- The peak PFET switch current drops below the I<sub>MODE</sub> level.

Typically,

$$I_{MODE} < 30 \text{ mA} + \frac{V_{IN}}{42\Omega}$$

During PFM operation, the converter positions the output voltage slightly higher than the nominal output voltage during PWM operation, allowing additional headroom for voltage drop during a load transient from light to heavy load. The PFM comparators sense the output voltage via the feedback pin and control the switching of the output FETs such that the output voltage ramps between ~0.6% and ~1.7% above the nominal PWM output voltage. If the output voltage is below the 'high' PFM comparator threshold, the PFET switch is turned on. It remains on until the output voltage exceeds the 'high' PFM threshold or the peak current exceeds the  $\rm l_{PFM}$  level set for PFM mode.

The typical peak current in PFM mode is:

$$I_{PFM} = 112 \text{ mA} + \frac{V_{IN}}{270}$$

Once the PFET switch is turned off, the NFET switch is turned on until the inductor current ramps to zero. When the NFET zero-current condition is detected, the NFET switch is turned off. If the output voltage is below the 'high' PFM comparator threshold (see figure below), the PFET switch is again turned on, and the cycle is repeated until the output reaches the desired level. Once the output reaches the 'high' PFM threshold, the NFET switch is turned on briefly to ramp the inductor current to zero; then both output switches are turned off, and the part enters an extremely low-power mode which allows the part to achieve high efficiencies under extremely light load conditions. When the output drops below the 'low' PFM threshold, the cycle repeats to restore the output voltage (average voltage in PFM mode) to ~1.15% above the nominal PWM output voltage.

If the load current should increase during PFM mode (see below figure) causing the output voltage to fall below the 'low2' PFM threshold, the part will automatically transition into fixed-frequency PWM mode.

| V <sub>IN</sub> | PWM to PFM (Typ.) | PFM to PWM (Typ.) |

|-----------------|-------------------|-------------------|

| 3.6V            | 50 mA             | 100 mA            |

| 4.5             | 65 mA             | 115 mA            |

FORCE PWM BUCK1 and FORCE PWM BUCK2 bits in Serial Interface control registers determine whether the buck converter chooses PFM/PWM operating mode automatically or operates constantly in PWM mode.

| Forced PWM BUCKx | PFM/ PWM Mode     |

|------------------|-------------------|

| 0                | Auto mode PFM/PWM |

| 1                | Forced PWM mode   |

## **INTERNAL SYNCHRONOUS RECTIFICATION**

While in PWM mode, the converter uses an internal NFET as a synchronous rectifier to reduce rectifier forward voltage drop and associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relatively low compared to the voltage drop across an ordinary rectifier diode.

#### **CURRENT LIMITING**

A current limit feature allows the circuit to protect itself and external components during overload conditions PWM mode implements cycle-by-cycle current limiting using an internal comparator that trips at 1000 mA (typ.) for Buck1 and Buck2. If the output is shorted to ground the device enters a timed current limit mode where the NFET is turned on for a longer duration until the inductor current falls below a low threshold. This ensures the inductor current has more time to decay, thereby preventing runaway.

#### **SOFT-START**

The LP8765 buck regulators have a soft start circuit which limits in-rush current during startup.

## **LOW-DROPOUT OPERATION**

The buck converter can operate at 100% duty cycle (no switching, PFET switch completely on) for low-dropout support of the output voltage. In this way the output voltage will be controlled down to the lowest possible input voltage. The minimum input voltage needed to support the output voltage is:

- $V_{IN,MIN}$ : = $I_{LOAD}$  \*  $(R_{DSON(P)} + R_{INDUCTOR}) + V_{OUT}$

- I<sub>LOAD</sub>: I<sub>LOAD</sub> current

- R<sub>DSON(P)</sub>: PFET drain-source resistance in the triode region

- R<sub>INDUCTOR</sub>: Inductor resistance

#### **BUCK ELECTRICAL CHARACTERISTICS**

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN2}$ = $V_{VIN_B1}$ = $V_{VIN_B2}$ )=3.7V, GND (=GND\_B1=GND\_B2=GND\_LDO=GND\_SINK) =0V,  $C_{VIN\_CHG}$ = $C_{VIN_B}$ 1= $C_{VIN_B2}$ = $C_{BUCK}$ 1= $C_{BUCK}$ 2= $C_{VIN_1}$ = $C_{VIN_2}$ =10  $\mu$ F,  $C_{LDOx}$ = $C_{VTRM}$ = $C_{COIN}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$ =25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J$ =-40°C to +125°C. (*Note 6, Note 11*)

| Cumbal                | Parameter                                                                | Conditions                                                                        | Trees      | Limit |       | Units |

|-----------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------|-------|-------|-------|

| Symbol                | Parameter                                                                | Conditions                                                                        | Тур.       | Min   | Max   | Units |

| V <sub>FB 1</sub>     | Feedback Voltage (Buck1)                                                 | V <sub>OUT</sub> = 1.2V                                                           | 1.2        | 1.164 | 1.236 | - V   |

| V <sub>FB 2</sub>     | Feedback Voltage (Buck1)                                                 | V <sub>OUT</sub> = 1.8V                                                           | 1.8        | 1.746 | 1.854 | ]     |

| V <sub>OUT,PFM</sub>  | Output voltage regulation in PFM mode relative to regulation in PWM mode | (Note 7)                                                                          | 1.5        |       |       | %     |

| V <sub>OUT</sub>      | Line regulation (Note 7)                                                 | $3.0V \le V_{IN} \le 5.5V$<br>$I_{OUT} = 10 \text{ mA}$                           | 0.14       |       |       | %/V   |

| V <sub>OUT</sub>      | Load regulation (Note 7)                                                 | 100 mA ≤ I <sub>OUT</sub> ≤ 300 mA                                                | 0.09       |       |       | %/mA  |

|                       | Switch pook current limit                                                | PWM mode @ 600 mA $3.0V \le V_{IN} \le 4.2V \text{ (Buck1)}$                      | 1025       | 710   | 1500  | - mA  |

| I <sub>LIM_PWM</sub>  | Switch peak current limit                                                | PWM mode @ 500 mA<br>3.0V $\leq$ V <sub>IN</sub> $\leq$ 4.2V (Buck2)              | 925        | 630   | 1400  | IIIA  |

| R <sub>DSON (P)</sub> | P channel FET on resistance                                              | V <sub>IN</sub> = 3.6V, I <sub>OUT</sub> = 100 mA                                 | 300        |       |       | 0     |

| R <sub>DSON (N)</sub> | N channel FET on resistance                                              | V <sub>IN</sub> = 3.6 <b>V</b> , I <sub>OUT</sub> = 100 IIIA                      | 150        |       |       | mΩ    |

| f <sub>osc</sub>      | Internal Oscillator Frequency                                            | PWM mode                                                                          | 2          | 1.9   | 2.1   | MHz   |

| _                     | Efficiency                                                               | I <sub>OUT</sub> = 5 mA, PFM mode<br>V <sub>OUT</sub> = 1.35V ( <i>Note 7</i> )   | 88         |       |       | - %   |

| η                     | Linciency                                                                | I <sub>OUT</sub> = 300 mA, PWM mode<br>V <sub>OUT</sub> = 1.35V ( <i>Note 7</i> ) | 90         |       |       | /6    |

| T <sub>STUP</sub>     | Startup time                                                             | $I_{OUT} = 0$ $V_{OUT\_BUCK1} = 1.2V$ $V_{OUT\_BUCK2} = 1.8V (Note 7)$            | 120<br>140 |       |       | μs    |

## **Output Voltage Programming**

| BUCK# | Function  | I (mA) | Output Voltage (V)    | Startup Default | Enable Control |

|-------|-----------|--------|-----------------------|-----------------|----------------|

| Buck1 | CORE1     | 600    | 0.8-1.45 (50 mV step) | ON              | S/I            |

| Buck2 | IO&Memory | 500    | 0.8-1.45 (50 mV step) | ON              | S/I            |

BUCK1 has two pre-programmed voltages BUCK1 NORMAL & BUCK1 SLEEP at 0x1C.

## **DVS FUNCTION FOR BUCK1**

| SLEEP_N |                                       |

|---------|---------------------------------------|

| High    | Buck1 V <sub>OUT</sub> = BUCK1 NORMAL |

| Low     | Buck1 V <sub>OUT</sub> = BUCK1 SLEEP  |

NOTE: If user does not want this DVS function, just program BUCK1 SLEEP = BUCK1 NORMAL = 1.2V.

## LDO's

There are all together 10 LDO's in LP8765 grouped as:

- A-type LDO's (LDO's 1-4)

- D-type LDO's (LDO's 5-8)

- LILO LDO (LDO 9)

- USB LDO (LDO 10)

The A-type LDO's are optimized for supplying of analog loads and have ultra-low noise (10  $\mu$ VRMS) and excellent PSRR (75 dB) performance.

The D-type LDO's are optimized for good dynamic performance to supply different fast changing (digital) loads with still reasonable noise (30  $\mu$ VRMS) and PSRR (60 dB) performance

The LILO LDO (LDO9) is powered by the output of BUCK2 in order to get better efficiency.

The USB LDO (VTRM) is a high-voltage LDO that uses VIN CHG as supply; it has 28V OVP capability.

All LDO's can be programmed through serial interface for different output voltage values.

#### A-TYPE LDO ELECTRICAL CHARACTERISTICS

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN2}$ = $V_{VIN_B1}$ = $V_{VIN_B2}$ ) =3.7V, GND (=GND\_B1=GND\_B2=GND\_LDO=GND\_SINK) =0V,  $C_{VIN\_CHG}$ = $C_{VIN_B}$ 1= $C_{VIN_B2}$ = $C_{BUCK2}$ = $C_{VIN1}$ = $C_{VIN2}$ =10  $\mu$ F,  $C_{LDOx}$ = $C_{VTRM}$ = $C_{COIN}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$ =25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J$ = -40°C to +125°C. (*Note 6*)

| Cumbal                 | Parameter                                            | Condition                                                                                    | 100#  | т    | Lin | Limits |               |

|------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------|-----|--------|---------------|

| Symbol                 |                                                      |                                                                                              | LDO#  | Тур. | Min | Max    | Units         |

| V                      | Output Voltage Accuracy                              | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> = default                                           | 1-4   |      | -2  | +2     | %             |

| V <sub>OUT</sub>       | Output Voltage Accuracy                              | lout - IIIA, V <sub>OUT</sub> - deladit                                                      | 1-4   |      | -3  | +3     | /0            |

| I <sub>SLEEP</sub>     | Max output current in sleep<br>mode<br>(TXCO_EN = 0) | $V_{OUT}$ +0.5V $\leq$ $V_{IN}$ $\leq$ 5.5V ( <i>Note 7</i> )                                | 2     |      |     | 1      | mA            |

| 1                      | Output ourrent limit                                 | V <sub>OUT</sub> = 0V                                                                        | 1     | 230  | 100 |        | mA            |

| I <sub>SC</sub>        | Output current limit                                 | V <sub>OUT</sub> = 0V                                                                        | 2,3,4 | 395  | 200 |        | IIIA          |

| $V_{DO}$               | Dropout Voltage                                      | $V_{OUT} = 2.85V$ , $I_{OUT} = I_{MAX}$ ( <i>Note 8</i> )                                    |       | 90   |     | 150    | mV            |

| ۸۱/                    | Line Regulation                                      | $V_{OUT} + 0.5V \le V_{IN} \le 5.5V, I_{OUT} = 1 \text{mA}$                                  | 1-4   | 25   |     |        | mV            |

| ΔV <sub>OUT</sub>      | Load Regulation                                      | 1 mA ≤ I <sub>OUT</sub> ≤ 450 mA                                                             |       | 0.3  |     |        | IIIV          |

| e <sub>N</sub>         | Output noise voltage                                 | 10 Hz $\leq$ f $\leq$ 100 kHz<br>C <sub>OUT</sub> = 1µF ( <i>Note 7</i> )                    | 1-4   | 10   |     |        | $\mu V_{RMS}$ |

| PSRR                   | Power Supply Ripple Rejection Ratio                  | $f=10 \text{ kHz}$ , $C_{OUT} = 1\mu\text{F}$<br>$I_{OUT} = 20 \text{ mA}$ ( <i>Note 7</i> ) | 1-4   | 75   |     |        | dB            |

| t <sub>STARTUP</sub>   | Startup Time from Shutdown                           | $C_{OUT} = 1\mu F$ , $I_{OUT} = I_{MAX}$ , GPIO to 0.95* $V_{OUT}$ ( <i>Note 7</i> )         | 1-4   | 35   |     |        | μs            |

| V <sub>TRANSIENT</sub> | Startup Transient Overshoot                          | $C_{OUT} = 1\mu F, I_{OUT} = I_{MAX}$                                                        | 1-4   |      |     | 30     | mV            |

| C <sub>OUT</sub>       | External output capacitance for stability            |                                                                                              | 1-4   | 1.0  | 0.5 | 20     | μF            |

## **D-TYPE LDO ELECTRICAL CHARACTERISTICS**

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN3}$ = $V_{VIN\_B1}$ = $V_{VIN\_B2}$ ) =3.7V, GND (=GND\_B1=GND\_B2=GND\_LDO=GND\_SINK) =0V,  $C_{VIN\_CHG}$ = $C_{VIN\_B}$ 1= $C_{VIN\_B2}$ = $C_{BUCK2}$ = $C_{VIN1}$ = $C_{VIN2}$ =10  $\mu$ F,  $C_{LDOx}$ = $C_{VTRM}$ = $C_{COIN}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$ =25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J$ = -40°C to +125°C. (*Note 6*)

| Symbol             | Parameter                                      | Condition                                                          | LDO# Tvp. |      | Limits |     | Units |

|--------------------|------------------------------------------------|--------------------------------------------------------------------|-----------|------|--------|-----|-------|

| Symbol             | Parameter                                      | Condition                                                          | LDO#      | Тур. | Min    | Max | Units |

| V                  | Output Valtage Assurage                        | L - 1mA V - default                                                | F 0       |      | -2     | +2  | %     |

| V <sub>OUT</sub>   | Output Voltage Accuracy                        | $I_{OUT} = 1 \text{mA}, V_{OUT} = \text{default}$                  | 5-8       |      | -3     | +3  | 70    |

| I <sub>SLEEP</sub> | Max output current in sleep mode (TXCO_EN = 0) | $V_{\text{OUT}} + 0.5 \text{V} \le V_{\text{IN}} \le 5.5 \text{V}$ | 5-6       |      |        | 1   | mA    |

|                    |                                                |                                                                    | 5         | 680  | 400    |     |       |

| I <sub>SC</sub>    | Output current limit                           | V <sub>OUT</sub> = 0V                                              | 6,7       | 380  | 200    |     | mA    |

|                    |                                                |                                                                    | 8         | 540  | 300    |     |       |

| 0                     | Down water                                | O a malitalia an                                                                      | 1.00# | <b>T</b> | Lin | nits | 11                |

|-----------------------|-------------------------------------------|---------------------------------------------------------------------------------------|-------|----------|-----|------|-------------------|

| Symbol                | Parameter                                 | Condition                                                                             | LDO#  | Тур.     | Min | Max  | Units             |

|                       |                                           |                                                                                       | 5     | 175      |     | 280  |                   |

| $V_{DO}$              | Dropout Voltage                           | $V_{OUT} = 3V$ , $I_{OUT} = I_{MAX}$ ( <i>Note 8</i> )                                | 6,7   | 90       |     | 150  | mV                |

|                       |                                           |                                                                                       | 8     | 135      |     | 225  |                   |

| ۸۱/                   | Line Regulation                           | $V_{OUT} + 0.5V \le V_{IN} \le 5.5V, I_{OUT} = 1 \text{ mA}$                          | 5-8   | 30       |     |      | mV                |

| $\Delta V_{OUT}$      | Load Regulation                           | 1 mA ≤ I <sub>OUT</sub> ≤ 450 mA                                                      | 3-0   | 2        |     |      | IIIV              |

| e <sub>N</sub>        | Output noise voltage                      | 10 Hz ≤ f ≤ 100 kHz                                                                   | 5-8   | 35       |     |      | μV <sub>RMS</sub> |

| о <sub>N</sub>        | Output Hoise voitage                      | $C_{OUT} = 1\mu F (Note 7)$                                                           | 3-0   |          |     |      | PVRMS             |

| PSRR                  | Power Supply Ripple Rejection             | f=10 kHz, C <sub>OUT</sub> = 1μF                                                      | 1-4   | 65       |     |      | dB                |

| 1 01111               | Ratio                                     | I <sub>OUT</sub> = 20 mA ( <i>Note 7</i> )                                            | 1-4   | 03       |     |      | ub.               |

| t <sub>STARTUP</sub>  | Startup Time from Shutdown                | $C_{OUT} = 1\mu F$ , $I_{OUT} = I_{MAX}$ , GPIO2 to 0.95* $V_{OUT}$ ( <i>Note 7</i> ) | 5-8   | 35       |     |      | μs                |

| V <sub>TRANSIEN</sub> | Startup Transient Overshoot               | $C_{OUT} = 1\mu F$ , $I_{OUT} = I_{MAX}$ ( <i>Note 7</i> )                            | 5-8   |          |     | 30   | mV                |

| C <sub>OUT</sub>      | External output capacitance for stability |                                                                                       | 5-8   | 1.0      | 0.5 | 20   | μF                |

## LDO9 (LILO) ELECTRICAL CHARACTERISTICS

Limits in standard typeface are for  $T_A = 25^{\circ}C$ . Limits in **boldface** type apply over the operating ambient temperature range  $-40^{\circ}C \le T_A \le +125^{\circ}C$ ). Unless otherwise noted, specifications apply to the closed loop typical application circuit with  $V_{IN3} = 3.7V$ ,  $I_{OUT} = 1$ mA,  $C_{OUT} = 1$ µF,  $V_{EN} = V_{BATT}$  (*Note 6*).

| Symbol                             | Parameter                                             | Conditions                                                                                              | Tvn  | Li  | Limit |       |

|------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| Syllibol                           | Farameter                                             |                                                                                                         | Тур  | Min | Max   | Units |

| / <sub>OUT</sub>                   | Output Voltage Tolerance                              | V <sub>OUT</sub> = 1.2V at V <sub>IN3</sub> = 1.8V                                                      |      | -2  | 2     | %     |

| 70 <sup>OUT</sup> /V <sup>IN</sup> | Line Regulation Error                                 | $V_{IN3} = V_{OUT(NOM)} + 0.3V \text{ to } 1.8V,$<br>$I_{OUT} = 300 \text{ mA}$                         | 0.1  |     | 1.5   | mV    |

| ΔV <sub>OUT</sub> /ΔmA             | Load Regulation Error                                 | V <sub>IN3</sub> = 1.8V, I <sub>OUT</sub> = 1mA to 300 mA                                               | 2    |     | 20    | mV    |

| SC                                 | Output Current (short circuit)                        | V <sub>OUT</sub> = 0V, V <sub>IN3</sub> = 1.8V, I <sub>OUT</sub> = 1 mA                                 | 595  | 300 |       | mA    |

| V <sub>DO</sub>                    | Output Voltage Dropout                                | V <sub>OUT</sub> = 1.2V, I <sub>OUT</sub> = 300 mA ( <i>Note</i> 8)                                     | 55   |     | 110   | mV    |

|                                    |                                                       | I <sub>OUT</sub> =150 mA ( <i>Note 8</i> )                                                              | 27.5 |     | 60    | mV    |

| ΞN                                 | Output Noise                                          | 10 Hz to 100 Hz ( <i>Note 7</i> )                                                                       | 100  |     |       | mVRMS |

|                                    |                                                       | Sine modulated V <sub>BATT</sub> ( <i>Note 7</i> )                                                      |      |     |       |       |

|                                    |                                                       | f = 10 Hz                                                                                               | 70   |     |       | dB    |

|                                    |                                                       | f = 100 Hz                                                                                              | 65   | İ   |       | l ab  |

|                                    |                                                       | f = 1kHz                                                                                                | 45   |     |       |       |

|                                    |                                                       | Sine modulated V <sub>BATT</sub> ( <i>Note 7</i> )                                                      |      |     |       |       |

| PSRR                               | Power Supply Rejection Ration                         | f = 10 Hz                                                                                               | 80   |     |       |       |

|                                    |                                                       | f = 100 Hz                                                                                              | 90   |     |       |       |

|                                    |                                                       | f = 1kHz                                                                                                | 95   |     |       | dB    |

|                                    |                                                       | f = 10kHz                                                                                               | 85   |     |       |       |

|                                    |                                                       | f = 100 kHz                                                                                             | 64   |     |       |       |

| Q                                  | Quiescent Current into V <sub>IN3</sub> (Normal mode) | I <sub>LOAD</sub> = 0 ( <i>Note 7</i> )                                                                 | 11   |     |       | μА    |

| Q(SHUTDOWN)                        | V <sub>IN3</sub> Shutdown Current                     | Output disabled (Note 7)                                                                                | 0.1  |     |       | μΑ    |

|                                    | Line Transient Response (Note 7)                      | $V_{IN3} = V_{OUT(NOM)} + 0.3V \text{ to } V_{OUT}$<br>$(NOM) + 0.9V; \text{ tr, tf} = 10  \mu\text{s}$ | ±1   |     |       | mV    |

| ∆V <sub>OUT</sub>                  | Load Transient Response (Note 7)                      | Pulsed load 0↔300 mA, di/dt = 300 mA/1µs                                                                | ±15  |     |       | mV    |

| T <sub>STARTUP</sub>               | Startup Time                                          | GPIO3 to 0.95*V <sub>OUT</sub> (Note 7)                                                                 | 70   |     | 150   | μs    |

## USB LDO (VTRM) ELECTRICAL CHARACTERISTICS

Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40$  to  $+125^{\circ}\text{C}$ . Unless otherwise specified, the following applies for  $V_{VIN\_CHG} = 5V$ . (*Note* 6)

| Cumbal                 | Parameter                                 | Conditions                                                                       | T   | Limit |     | l lada |

|------------------------|-------------------------------------------|----------------------------------------------------------------------------------|-----|-------|-----|--------|

| Symbol                 |                                           |                                                                                  | Тур | Min   | Max | Units  |

| V <sub>OUT</sub>       | Output Voltage Accuracy                   | I <sub>OUT</sub> = 1mA,                                                          | 3.3 | 3.15  | 3.5 | ٧      |

| I <sub>sc</sub>        | Output Current Limit                      | V <sub>OUT</sub> = 0V                                                            | 135 | 10    |     | mA     |

| ΔV <sub>OUT</sub>      | Line Regulation                           | $4.5V \le V_{IN\_CHG} \le 6.5V$<br>$I_{OUT} = 10 \text{ mA}$                     | 10  |       |     | mV     |

| ΔV <sub>OUT</sub>      | Load Regulation                           | 1mA ≤ I <sub>OUT</sub> ≤ 10mA                                                    | 60  |       |     |        |

| PSRR                   | Power Supply Ripple Rejection Ratio       | f = 10 kHz, C <sub>OUT</sub> = 1mF<br>I <sub>OUT</sub> = 20 mA ( <i>Note 7</i> ) | 45  |       |     | dB     |

| t <sub>START-UP</sub>  | Startup Time from Shutdown                | C <sub>OUT</sub> = 1mF, I <sub>OUT</sub> = 10 mA<br>( <i>Note 7</i> )            | 15  |       |     | μs     |

| V <sub>TRANSIENT</sub> | Startup Transient Overshoot               | C <sub>OUT</sub> = 1mF, I <sub>OUT</sub> = 10 mA<br>( <i>Note 7</i> )            | 250 |       |     | mV     |

| C <sub>OUT</sub>       | External output capacitance for stability |                                                                                  | 1   | 0.6   | 20  | μF     |

## A/D Converter

LP8765 is equipped with a 12-bit successive approximation analog-to-digital converter to enable the conversion of analog inputs:

- Battery voltage

- Charge voltage or current

- IC temperature

- Battery Temperature (external input)

The battery voltage input and the charge current are scaled linearly to adapt the voltage/current range of the source to the input voltage range of the A/D core. The ADC is clocked by the internal 1MHz system clock. The conversion result is available in the registers 0x11 & 0x12 80 µs after the setting

of the CONV START bit in the ADC Control Register. The ADC will automatically enter power save mode if conversions are not performed.

#### A/D CONVERTER DATA AND CONTROL REGISTERS

The Read/Write Control register ADC CTRL allows starting the conversion, source selection and output format selection. Setting the CONV START bit in the control register starts a new A/D conversion. Setting ADC FORMAT register to '1' allows throwing out the MSB and shifting the result 1 bit left. This can be used if result's MSB is known, to get more data with one register read. User should wait at least 80 us between two readings, or check the register bit CONVERSION DONE=1 at 0x13 bit0 before read ADC data

#### **ADC INPUT SELECTION (REGISTER 0x10)**

| ADC INPUT SEL |      | ADC Input | Max_Value in        | Ассиноси |                                |

|---------------|------|-----------|---------------------|----------|--------------------------------|

| bit3          | bit2 | bit1      | ADC Input           | Formula  | Accuracy                       |

| 0             | 0    | 0         | V <sub>BATT</sub>   | 5.5V     | ±2% in operating range         |

| 0             | 0    | 1         | V <sub>IN_CHG</sub> | 6.0V     | ±3% in operating range         |

| 0             | 1    | 0         | I <sub>IN_CHG</sub> | 2.5A     | TBD                            |

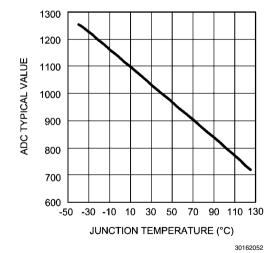

| 0             | 1    | 1         | T <sub>J</sub>      | 125°C    | See Figure 1                   |

| 1             | 0    | 0         | V <sub>BATT</sub>   | 6.0V     | ±3% in operating range         |

| 1             | 0    | 1         | V <sub>BATT</sub>   | 5.0V     | ±2% in operating range         |

| 1             | 1    | 0         | V <sub>ADC1</sub>   | 2.5V     | ±(2%+30 mV) in operating range |

| 1             | 1    | 1         | V <sub>ADC2</sub>   | 2.5V     | ±(2%+30 mV) in operating range |

#### MEASUREMENT RESULT CALCULATION

The transfer functions for conversions can be given as: VAL-UE =  $MAX_VALUE^*(i+0.5)/4095$  where i = 0...4095.

If only 8 most significant bits are read, then: VALUE =  $MAX_VALUE^*(i+0.5)/255$  where i = 0...255.

If ADC\_FORMAT is set to 1 and 8 bits are read, then: VALUE  $= MAX_VALUE^*(i+0.5)/511$  where i = 0...255.

If MSB is assumed 1, then MAX\_VALUE/2 must be added to this Value.

## **WORKING RANGE AND ACCURACY**

ADC reading is accurate for VBATT voltages over 2.7V. ADC uses internal bandgap reference. Total absolute accuracy for voltage measurement is better than 3% over all working conditions.

For current measurement the absolute accuracy is better than 5% or 10 mA whatever is bigger.

Sample in time is 1µs. As result ADC may sample in possible spikes that may occur during phone operation. To filter spikes out ADC code readings averaging can be used.

FIGURE 1. ADC Typical Value vs. Junction Temperature

#### **ADC ELECTRICAL CHARACTERISTICS**

Unless otherwise noted,  $V_{BATT}$  (= $V_{VIN1}$ = $V_{VIN2}$ = $V_{VIN3}$ = $V_{VIN_B1}$ = $V_{VIN_B2}$ ) =3.7V, GND (=GND\_B1=GND\_B2=GND\_LDO=GND\_SINK) =0V,  $C_{VIN_CHG}$ = $C_{VIN_B}$ 1= $C_{VIN_B2}$ = $C_{BUCK}$ 1= $C_{BUCK2}$ = $C_{VIN1}$ = $C_{VIN2}$ =10  $\mu$ F,  $C_{LDOx}$ = $C_{VTRM}$ = $C_{COIN}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$ =25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J$  = -40°C to +125°C. (*Note 6*)

| Symbol   | Parameter                 | Conditions               | Тур | Limit |     | Units |

|----------|---------------------------|--------------------------|-----|-------|-----|-------|

| Syllibol | Parameter                 |                          |     | Min   | Max | Units |

|          | Resolution                |                          | 12  |       |     | bits  |

| INL      | Integral Nonlinearity     | (Note 7)                 |     | -4    | 4   | LCD   |

| DNL      | Differential Nonlinearity | No missing code (Note 7) |     | -2    | 2   | LSB   |

|          | Conversion Time           | (Note 7)                 |     |       | 80  | μs    |

# **Real-Time Clock**

Real-time clock (RTC) block is used for time tracking in any chip condition. It uses 32 kHz crystal oscillator for accurate time predictions and is supplied either from system supply in normal condition or from coin battery when the chip is in shutdown mode.

This RTC has the following features: