## Highly Integrated, 4-Channel Sequencer and Supervisor

#### MAX16165/MAX16166

#### **General Description**

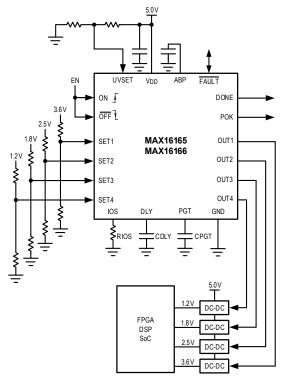

The MAX16165/MAX16166 monitor up to five voltages and sequence up to four voltages. These devices provide an adjustable delay as each supply is turned on as well as monitor each power-supply voltage, including the input voltage  $V_{DD}$ .

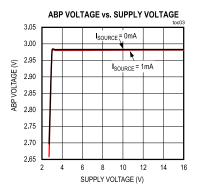

The MAX16165/MAX16166 operate from a supply range of 2.7V to 16V and have an internal regulator output (ABP), power internal circuits, and supply more than 1mA additional current to any external circuitry.

The sequencing is enabled by two inputs, ON and  $\overline{OFF}$ . A rising edge on the ON input initiates power-on sequencing of the channels whereas a falling edge on  $\overline{OFF}$  input initiates power-off sequencing. During the power-on sequencing, when all of the voltages reach their final values, a sequencing done output DONE asserts high followed by a Power-OK (POK) output after the reset delay timer has expired, allowing the microcontroller ( $\mu$ C) to operate. If any voltage falls below its threshold, the reset output asserts and all voltage supplies are turned off. When the sequencer initiates a power-off sequencing, the MAX16165/MAX16166 can reverse sequence the outputs.

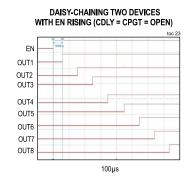

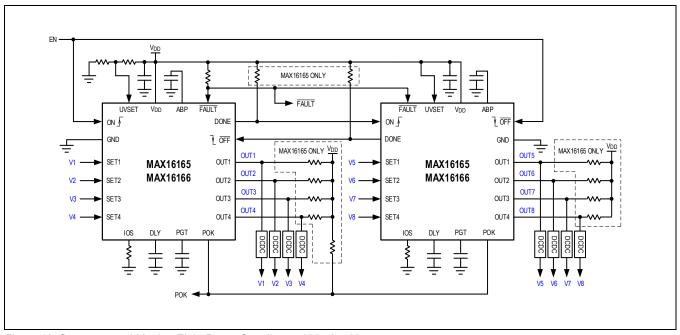

Output options available are open-drain (MAX16165) and push-pull (MAX16166). The MAX16165/MAX16166 can be daisy-chained unlimited amount to time to control any number of voltages in a system.

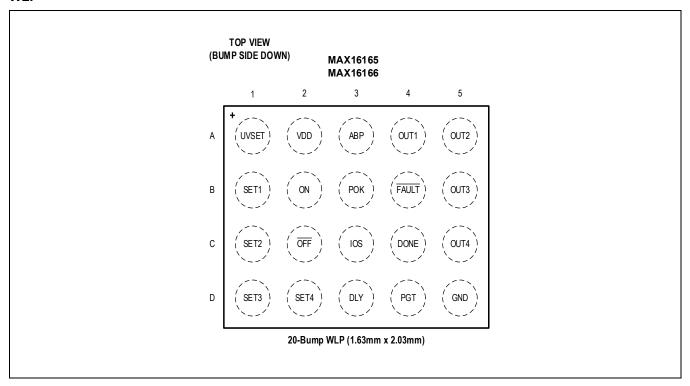

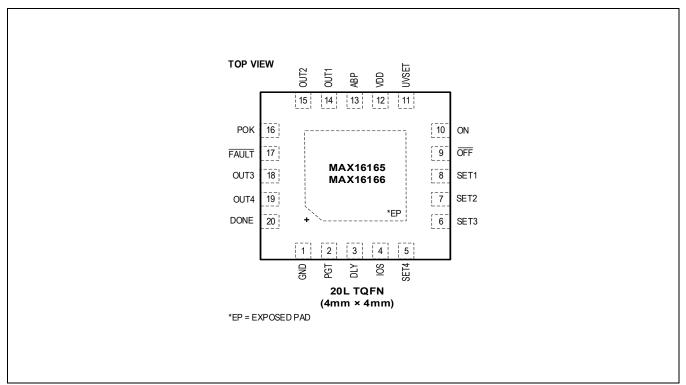

The MAX16165/MAX16166 feature a bidirectional active low FAULT input/output, which asserts low during any fault condition. FAULT stays low as long as an undervoltage event is present at UVSET Input and it is a one-shot output during all other FAULT conditions. An external signal pulling FAULT low disables all outputs immediately. The MAX16165/MAX16166 are available in a 1.63mm x 2.03mm, 20-bump Wafer-Level Package (WLP) and a 4mm x 4mm, 20L TQFN package. The device is fully specified over the -40°C to +125°C operating temperature range.

#### **Applications**

- Latch-Up Prevention and Inrush Current Protection in Multi-Supply Systems

- FPGA/ASIC Power Supply Sequencing

- Servers and Security Cameras

- Test Equipment

- Networking Equipment

- Industrial Sensors and Motor Controls

#### **Benefits and Features**

- 2.7V to 16.0V Wide Operating Voltage Range

- Monitor Up to Five Voltages

- Sequence Up to Four Voltages

- Power-Off in Reverse Order or Simultaneously

- Unlimited Daisy-Chain

- Capacitor-Adjustable Sequencing Delay

- Capacitor-Adjustable Power-Good Timeout

- Resistor-Configurable Power-Supply On and Off Thresholds

- Open-Drain (MAX16165)/Push-Pull (MAX16166) Outputs

- POK Output for System Microcontroller Reset

- Bidirectional FAULT Input/Output

- 4 x 5-Bump WLP and 20L TQFN Package

- -40°C to +125°C Operating Temperature Range

Ordering Information appears at end of data sheet.

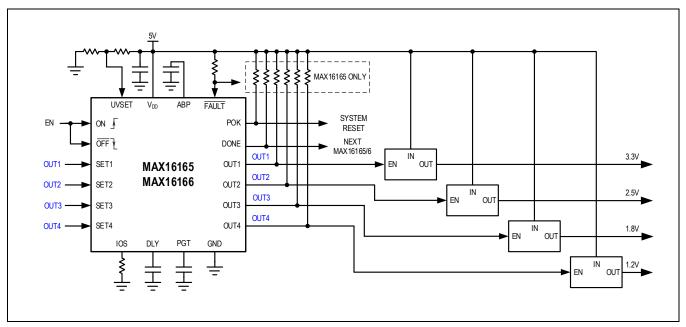

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                                 | 0.3V to +30V                       |

|--------------------------------------------------------|------------------------------------|

| OUT_ (Open-drain) to GND                               | 0.3V to +30V                       |

| OUT_ (Push-pull) to GND0.3 to                          | Min.(V <sub>ABP</sub> + 0.3V, +6V) |

| DONE, POK (Open-drain) to GND                          | 0.3V to +6V                        |

| DONE (Push-pull) to GND0.3 to                          | Min.(V <sub>ABP</sub> + 0.3V, +6V) |

| POK (Push-pull) to GND0.3 to                           | Min.(V <sub>ABP</sub> + 0.3V, +6V) |

| SET_, $\overline{FAULT}$ , ON, $\overline{OFF}$ to GND | 0.3V to +6V                        |

| UVSET, ABP, IOS, DLY, PGT to GNE                       | )0.3V to +6V                       |

| Input/Output Current                                   | 20mA                               |

| Continuous Power Dissipation, WLP, Multilayer (T <sub>A</sub> = +70°C, derate 18.02mW/°C above +70°C)144                                                           |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Continuous Power Dissipation, TQFN, Multilayer $(T_A = +70^{\circ}C, \text{ derate } 25.60 \text{mW}/^{\circ}C \text{ above } +70^{\circ}C) \dots 2050 \text{ me}$ |        |

| Operating Temperature Range40°C to                                                                                                                                 | +125°C |

| Junction Temperature                                                                                                                                               | +150°C |

| Storage Temperature Range (20 WLP)40°C to                                                                                                                          | +150°C |

| Storage Temperature Range (20 TQFN)55°C to                                                                                                                         | +150°C |

| Soldering Temperature (reflow)                                                                                                                                     | +260°C |

|                                                                                                                                                                    |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **WLP**

| Package Code                                           | W201C2+2                       |  |  |

|--------------------------------------------------------|--------------------------------|--|--|

| Outline Number                                         | <u>21-0779</u>                 |  |  |

| Land Pattern Number                                    | Refer to Application Note 1891 |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                   |                                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 55.49°C/W                      |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |  |  |

#### **TQFN**

| Package Code                                        | T2044+3C       |  |  |  |  |  |

|-----------------------------------------------------|----------------|--|--|--|--|--|

| Outline Number                                      | <u>21-0139</u> |  |  |  |  |  |

| Land Pattern Number                                 | <u>90-0037</u> |  |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                |                |  |  |  |  |  |

| Junction-to-Ambient ( $\theta_{JA}$ )               | 39°C/W         |  |  |  |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$ | 6°C/W          |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD}$  = 2.7V to 16.0V,  $V_{EN}$  =  $V_{ABP}$ ,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER SYMBOL                        |                       | CONDITIONS                                                           | MIN                        | TYP | MAX    | UNITS            |

|-----------------------------------------|-----------------------|----------------------------------------------------------------------|----------------------------|-----|--------|------------------|

| SUPPLY VOLTAGE                          |                       |                                                                      |                            |     |        |                  |

| Operating Voltage<br>Range              | $V_{DD}$              |                                                                      | 2.7                        |     | 16     | V                |

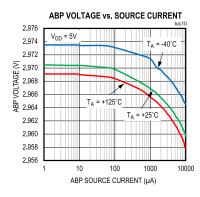

| Regulated Supply<br>Voltage             | $V_{ABP}$             | I <sub>ABP</sub> = +1mA (external sourcing current from ABP)         | 2.45                       |     | 3.20   | V                |

| Undervoltage Lockout                    | V <sub>UVLO</sub>     | Minimum voltage on ABP, ABP rising                                   |                            | 1.7 | 2.35   | V                |

| Undervoltage Lockout<br>Hysteresis      | V <sub>UVLO_HYS</sub> | ABP falling                                                          |                            | 100 |        | mV               |

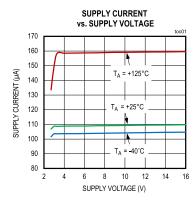

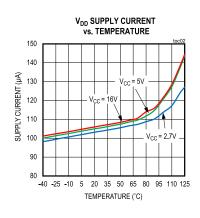

| Supply Current                          | $I_{DD}$              | V <sub>DD</sub> = 5V, all OUT_ = HIGH, No load                       |                            | 105 | 170    | μΑ               |

| ON, OFF INPUTS                          |                       |                                                                      |                            |     |        |                  |

| ON Input Threshold                      | V <sub>ON_TH</sub>    | ON rising                                                            | 0.496                      | 0.5 | 0.504  | V                |

| OFF Input Threshold                     | V <sub>OFF</sub> TH   | OFF falling                                                          | 0.496                      | 0.5 | 0.504  | V                |

| ON, OFF Threshold<br>Tempco             |                       | J.                                                                   |                            | 20  |        | ppm/°C           |

| ON, OFF Input Current                   | I <sub>ON_OFF</sub>   |                                                                      | -100                       |     | 100    | nA               |

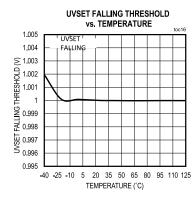

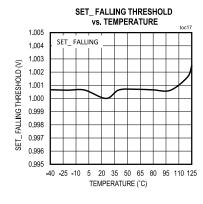

| MONITORED ANALOG I                      | NPUTS (UVSET          | , SET_)                                                              |                            |     |        |                  |

| UVSET, SET_<br>Threshold                | V <sub>TH</sub>       | UVSET, SET_falling                                                   | 0.496                      | 0.5 | 0.504  | V                |

| UVSET, SET_<br>Threshold Hysteresis     | V <sub>HYST</sub>     | UVSET, SET_ rising                                                   |                            | 1   |        | %V <sub>TH</sub> |

| UVSET, SET_<br>Threshold Tempco         |                       |                                                                      |                            | 20  |        | ppm/°C           |

| UVSET, SET_ Input<br>Current            |                       | V <sub>UVSET</sub> = V <sub>SET</sub> = 0.5V                         | -100                       |     | +100   | nA               |

| OFFSET CURRENT SET                      | TING INPUT (IO        | S)                                                                   |                            |     |        |                  |

| Offset Current Voltage Source           |                       |                                                                      | 0.4925                     | 0.5 | 0.5075 | V                |

| Offset Current Voltage<br>Source Tempco |                       |                                                                      |                            | 30  |        | ppm/°C           |

| Offset Current Range                    |                       | $R_{IOS}$ = 10k $\Omega$ to 1M $\Omega$                              | 0.5                        |     | 50     | μA               |

| Offset Current Error                    |                       | 0.5μA to 5μA                                                         | -25                        |     | +25    | %                |

| Oliset Gullent Liloi                    |                       | 5μA to 50μA                                                          | -5                         |     | +5     | 70               |

| DELAY TIMER INPUT (D                    | LY) AND POWE          | R-GOOD TIMER INPUT (PGT)                                             |                            |     |        |                  |

| 0 0 1                                   |                       | -40°C to +85°C                                                       | 3.8                        | 4   | 4.2    |                  |

| Source Current                          |                       | -40°C to +125°C                                                      | 3.8                        | 4   | 4.4    | μΑ               |

| Voltage Threshold                       |                       |                                                                      |                            | 0.5 |        | V                |

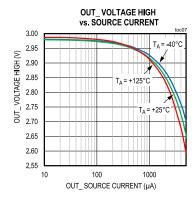

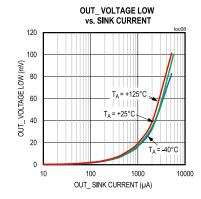

| SEQUENCER OUTPUTS                       | (OUT_)                |                                                                      | <u> </u>                   |     |        | 1                |

| OUT_ Output Voltage                     |                       | MAX16165, Open-drain Output, I <sub>SINK</sub> = 3.2mA               |                            |     | 0.3    |                  |

| Low                                     | V <sub>OUTL</sub>     | MAX16166, Push-pull Output,<br>I <sub>SINK</sub> = 3.2mA             |                            |     | 0.3    | V                |

| OUT_ Output Voltage<br>High             |                       |                                                                      | 0.85 x<br>V <sub>ABP</sub> |     |        | V                |

| OUT_ Leakage Current                    | lout_lkg              | MAX16165, Open-drain Output,<br>OUT_ = HIGH, V <sub>OUT</sub> _ = 5V |                            |     | 1      | μA               |

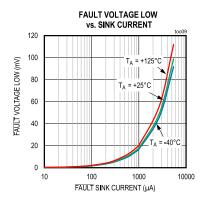

| FAULT INPUT/OUTPUT                      |                       |                                                                      |                            |     |        |                  |

$(V_{DD}$  = 2.7V to 16.0V,  $V_{EN}$  =  $V_{ABP}$ ,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                          | SYMBOL                 | CONDITIONS                                                                                                    | MIN                        | TYP | MAX | UNITS |  |

|--------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------|-----|-----|-------|--|

| FAULT Output Voltage<br>Low                                        | V <sub>FAULTL</sub>    | I <sub>SINK</sub> = 3.2mA 0.3                                                                                 |                            | 0.3 | V   |       |  |

| FAULT Leakage Current                                              | IFAULT_LKG             | FAULT = HIGH, V <sub>FAULT</sub> = 5V                                                                         |                            |     | 1   | μΑ    |  |

| FAULT Input Threshold                                              | V <sub>FAULT_TH</sub>  | FAULT falling                                                                                                 |                            | 0.5 |     | V     |  |

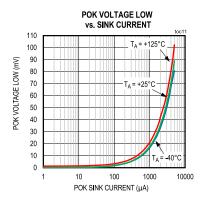

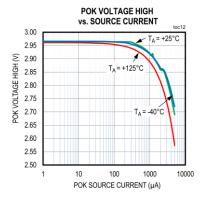

| POWER-OK OUTPUT (PO                                                | OK)                    |                                                                                                               |                            |     |     |       |  |

| POK Output Voltage<br>Low                                          | V <sub>POKL</sub>      | MAX16165, Open-drain Output, I <sub>SINK</sub> = 3.2mA  MAX16166, Push-pull Output, I <sub>SINK</sub> = 3.2mA |                            |     | 0.3 | V     |  |

| POK Output Voltage<br>High                                         | V <sub>РОКН</sub>      | MAX16166, Push-pull Output,<br>ISOURCE = 1mA                                                                  | 0.85 x<br>V <sub>ABP</sub> |     |     | V     |  |

| POK Leakage Current                                                | I <sub>POK_LKG</sub>   | MAX16165, Open-drain Output,<br>POK = HIGH, V <sub>POK</sub> = 5V                                             |                            |     | 1   | μA    |  |

| DONE OUTPUT (DONE)                                                 |                        |                                                                                                               |                            |     |     |       |  |

| DONE Output Voltage                                                | V <sub>DONEL</sub>     | MAX16165, Open-drain Output, I <sub>SINK</sub> = 3.2mA                                                        |                            |     | 0.3 |       |  |

| Low                                                                | DONEL                  | MAX16166, Push-pull Output, I <sub>SINK</sub> = 3.2mA                                                         |                            |     | 0.3 | V     |  |

| DONE Output Voltage<br>High                                        | $V_{DONEH}$            | MAX16166, Push-pull Output, I <sub>SOURCE</sub> = 1mA                                                         | 0.85 x<br>V <sub>ABP</sub> |     |     | V     |  |

| DONE Leakage Current                                               | I <sub>DONE_LKG</sub>  | MAX16165, Open-drain Output,<br>DONE = HIGH, V <sub>DONE</sub> = 5V                                           |                            |     | 1   | μA    |  |

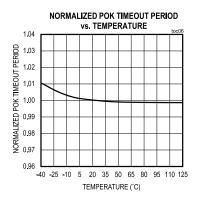

| TIMING                                                             |                        |                                                                                                               |                            |     |     |       |  |

| POK Reset Timeout<br>Accuracy                                      | t <sub>POK_ACC</sub>   |                                                                                                               | -15                        |     | +15 | %     |  |

| ON Input Pulse Width                                               | t <sub>ON_PW</sub>     | ON rising                                                                                                     | 6                          |     |     | μs    |  |

| OFF Input Pulse Width                                              | t <sub>OFF_PW</sub>    | OFF falling                                                                                                   | 6                          |     |     | μs    |  |

| External FAULT Input Pulse Width                                   | t <sub>FAULT_PW</sub>  | FAULT falling                                                                                                 | 6                          |     |     | μs    |  |

| ON Input, OFF Input,<br>External FAULT Input<br>Transient Immunity |                        |                                                                                                               |                            |     | 1   | μs    |  |

| FAULT Output Hold<br>Timeout                                       |                        |                                                                                                               | 68                         | 80  | 92  | μs    |  |

| SET_ to FAULT, OUT_<br>Low Delay Time                              | t <sub>SET_FAULT</sub> | SET_ falling below V <sub>TH</sub>                                                                            |                            | 1   |     | μs    |  |

| External FAULT to OUT_ Low Delay Time                              | t <sub>FAULT_OUT</sub> | FAULT falling below V <sub>TH</sub>                                                                           |                            | 3   |     | μs    |  |

| ON to FAULT, OUT_<br>low Delay Time                                |                        | ON rising above V <sub>TH</sub>                                                                               |                            | 3   |     | μs    |  |

| OFF to FAULT, OUT_<br>Low Delay Time                               |                        | OFF falling below V <sub>TH</sub>                                                                             |                            | 3   |     | μs    |  |

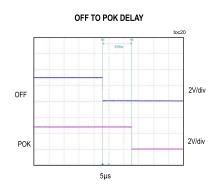

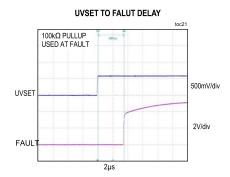

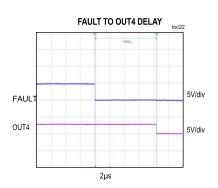

## **Typical Operating Characteristics**

$V_{DD}$  = 5.0V,  $V_{EN}$  =  $V_{ABP}$ ,  $T_A$  = 25°C, unless otherwise noted.

$V_{DD}$  = 5.0V,  $V_{EN}$  =  $V_{ABP}$ ,  $T_A$  = 25°C, unless otherwise noted.

$V_{DD}$  = 5.0V,  $V_{EN}$  =  $V_{ABP}$ ,  $T_A$  = 25°C, unless otherwise noted.

## **Pin Configurations**

#### WLP

#### **TQFN**

## **Pin Descriptions**

| PIN         |    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 20 WLP TQFN |    | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| A1          | 11 | UVSET | Set Monitored Threshold Input. Monitor a voltage by setting the threshold with an external resistive divider. The threshold is 0.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| A2          | 12 | VDD   | Device Power-Supply Input. Connect to 2.7V to 16V. Bypass V <sub>DD</sub> to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| A3          | 13 | ABP   | Internal Supply Bypass Input. Connect a 1µF capacitor from ABP to GND. ABP is an internally generated voltage that powers internal circuits, and can supply more than 1m/ additional current to any external circuitry. Do not leave ABP unconnected or short to Gl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| A4          | 14 | OUT1  | MAX16165: Open-Drain Output 1. Upon power-on sequencing (ON input rises from low to above 0.5V), OUT1 changes from low to high impedance after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at the SET2 pin falls below 0.5V, OUT1 goes from high impedance to low after sequence delay t <sub>DLY</sub> . OUT1 requires an external pullup resistor.  MAX16166: Push-Pull Output 1. Upon power-on sequencing (ON input rises from low to above 0.5V), OUT1 changes from low to high after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at the SET2 pin falls below 0.5V, OUT1 goes from high to low after sequence delay t <sub>DLY</sub> .                                                 |  |  |  |

| <b>A</b> 5  | 15 | OUT2  | MAX16165: Open-Drain Output 2. During power-on sequencing, when the voltage at SET1 rises above threshold voltage (Rising), OUT2 goes from low to high impedance after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at the SET3 pin falls below 0.5V, OUT2 goes from high impedance to low after sequence delay t <sub>DLY</sub> . OUT2 requires an external pullup resistor.  MAX16166: Push-Pull Output 2. During a power-on sequencing, when the voltage at SET1 rises above threshold voltage (Rising), OUT2 goes from low to high after sequence delay t <sub>DLY</sub> . During a power-off sequencing, when the voltage at SET3 pin falls below 0.5V, OUT2 goes from high to low after sequence delay t <sub>DLY</sub> . |  |  |  |

| B1          | 8  | SET1  | Set Monitored Threshold 1 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET1 threshold is 0.5V. To disable Channel 1, connect SET1 to ABP. Do not leave SET1 unconnected or short to GND. Connect OUT1 directly to SET1 for sequencing without monitoring Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| B2          | 10 | ON    | Noninverting Comparator Input. A rising voltage above 0.5V on this pin initiates power-on sequencing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| В3          | 16 | РОК   | MAX16165: Open-Drain Power-OK Output. During power-on sequencing, when SET4 voltage rises above 0.5V, this output changes from low to high impedance after the reset timeout period. This output is driven low if the voltage on any SET_ or UVSET input drops below 0.5V or when FAULT is pulled low by an an external signal. POK requires an external pullup resistor.  MAX16166: Push-Pull Power-OK Output. During power-on sequencing, when SET4 voltage rises above 0.5V, this output changes from low to high after the reset timeout period. This output is driven low if the voltage on any SET_ or UVSET input drops below                                                                                                                               |  |  |  |

| B4          | 17 | FAULT | 0.5V or when FAULT is pulled low by an external signal.  Bidirectional Input and Active Low Open-Drain Output. When an internal fault is detected, this pin is asserted low. An external signal pulling this pin low disables all outputs and sets the MAX16165/66 to initialization state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| B5          | 18 | OUT3  | MAX16165: Open-Drain Output 3. During power-on sequencing, when the voltage at SET2 rises above threshold voltage (Rising), OUT3 goes from low to high impedance after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at SET4 pin falls below 0.5V, OUT3 goes from high impedance to low after sequence delay t <sub>DLY</sub> . OUT3 requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

# Highly Integrated, 4-Channel Sequencer and Supervisor

|    | ı  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |      | MAX16166: Push-Pull Output 3. During power-on sequencing, when the voltage at SET2 rises above threshold voltage (Rising), OUT3 goes from low to high after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at the SET4 pin falls below 0.5V, OUT3 goes from high to low after sequence delay t <sub>DLY</sub> .                                                                                                                                                                                                                                                                                                                                                                                           |

| C1 | 7  | SET2 | Set Monitored Threshold 2 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET2 threshold is 0.5V. To disable Channel 2, connect SET2 to ABP. Do not leave SET2 unconnected or short to GND. Connect OUT2 directly to SET2 for sequencing without monitoring Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C2 | 9  | OFF  | Noninverting Comparator Input. A falling voltage below 0.5V on this pin initiates power-off sequencing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C3 | 4  | IOS  | Offset Current Setting Input. Connect a resistor $(10k\Omega \text{ to } 1M\Omega)$ to GND to set the offset current during power-off sequencing. Do not leave it unconnected or short to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C4 | 20 | DONE | MAX16165: Open-Drain Sequencing Done Output. When power-on sequencing is complete, DONE changes from low to high impedance. During power-off sequencing, the pin remains high impedance until SET1 voltage drops below its threshold. When a fault occurs, this pin is asserted low.  MAX16166: Push-Pull Sequencing Done Output. When power-on sequencing is complete, DONE changes from low to high. During power-off sequencing, the pin remains high until SET1 voltage drops below its threshold. When a fault occurs, this pin is asserted low.                                                                                                                                                                                      |

| C5 | 19 | OUT4 | MAX16165: Open-Drain Output 4. During power-on sequencing, when the voltage at SET3 rises above threshold Voltage (Rising), OUT4 goes from low to high impedance after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at the OFF pin falls below 0.5V, OUT4 goes from high impedance to low after sequence delay t <sub>DLY</sub> . OUT4 requires an external pullup resistor.  MAX16166: Push-Pull Output 4. During power-on sequencing, when the voltage at SET3 rises above 0.5V, OUT4 goes from low to high after sequence delay t <sub>DLY</sub> . During power-off sequencing, when the voltage at the OFF pin falls below 0.5V, OUT4 goes from high to low after sequence delay t <sub>DLY</sub> . |

| D1 | 6  | SET3 | Set Monitored Threshold 3 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET3 threshold is 0.5V. To disable Channel 3, connect SET3 to ABP. Do not leave SET3 unconnected or short to GND. Connect OUT3 directly to SET3 for sequencing without monitoring Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D2 | 5  | SET4 | Set Monitored Threshold 4 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET4 threshold is 0.5V. To disable channel 4, connect SET4 to ABP. Do not leave SET4 unconnected or short to GND. Connect OUT4 directly to SET4 for sequencing without monitoring the Channel 4.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D3 | 3  | DLY  | Adjustable Sequence Delay Timing Input. Connect a capacitor from DLY to GND to set the sequence delay between each OUT Leave DLY unconnected for a 40µs (typ) delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D4 | 2  | PGT  | Monitored Power-Supply Power-Good Timer Setting Input. The capacitor connected to this input to GND sets the time allowed between OUT_ being enabled and SET_ voltage goes above its threshold voltage (Rising). If SET_ does not rises above its threshold voltage (Rising) before the timer expires, the MAX16165/MAX16166 generates a fault condition and enters initialization state. Leave PGT unconnected for a 5µs (typ) delay.                                                                                                                                                                                                                                                                                                     |

| D5 | 1  | GND  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -  | -  | EP   | Exposed Pad. EP is internally connected to GND. Connect EP to the GND plane for improved heat dissipation. Do not use EP as the only ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

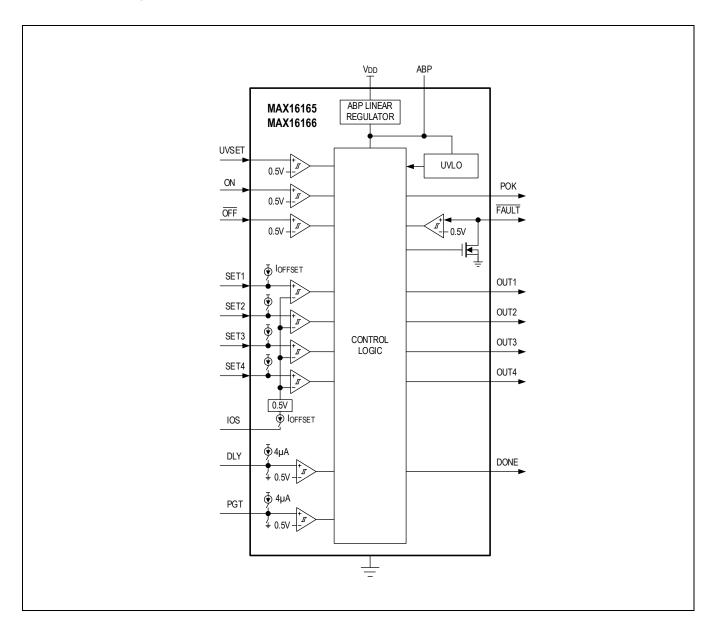

## **Functional Diagrams**

#### **Detailed Description**

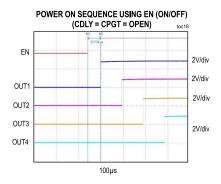

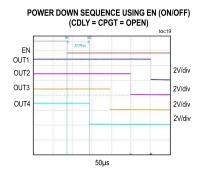

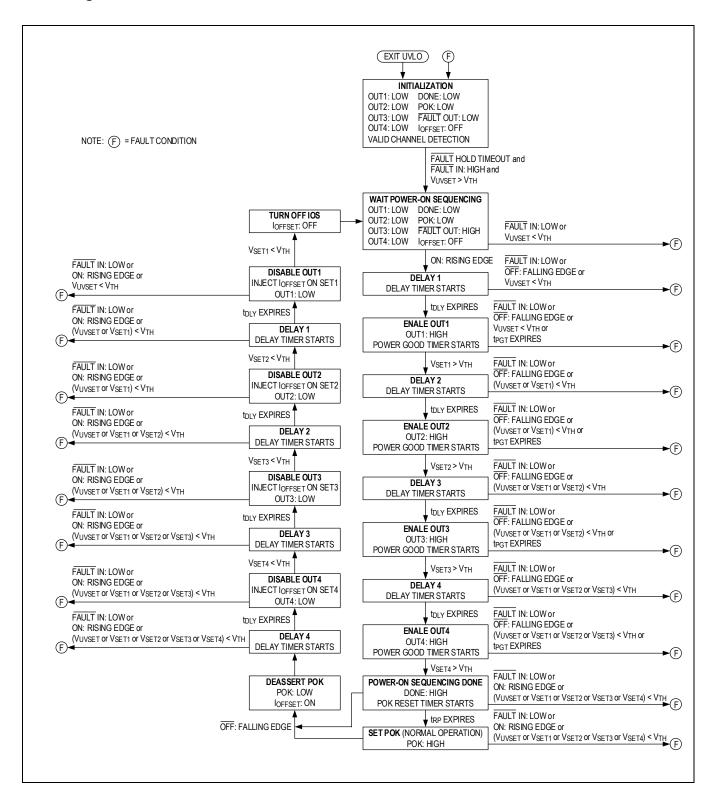

The MAX16165/MAX16166 enable four power supplies when the sequencer turns on and disable the four power supplies in reverse order when the sequencer turns off. The MAX16165/MAX16166 monitor each power supply once they are turned on. The device also includes an undervoltage (UV) sensing input (UVSET) that monitors VDD or any other power supply.

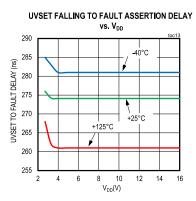

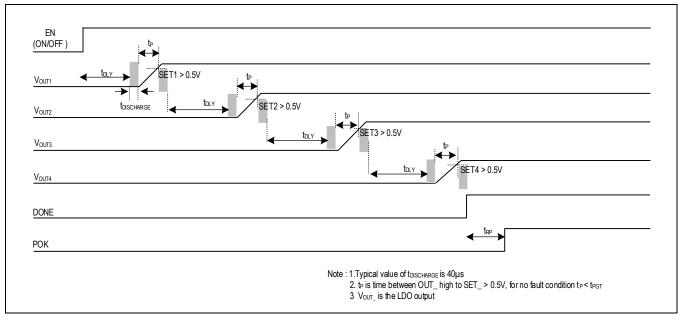

When the sequencer initiates power-on sequencing, the MAX16165/MAX16166 provide a capacitor-adjustable delay time  $(t_{DLY})$  before the first output is enabled. After the first output is enabled, the MAX16165/MAX16166 monitor the enabled power supply voltage by feeding it back to the voltage sensing input SET1. If the voltage at SET1 reaches its threshold  $(V_{TH} + V_{HYST})$  within a capacitor-adjustable power-good timeout period  $(t_{PGT})$ , the sequencer waits for the delay time  $t_{DLY}$  and enables the second output. The power-on sequencing repeats until the fourth output is enabled and the voltage at SET4 reaches its threshold. At that time, a sequencing done output DONE asserts high and a POK output asserts high after the reset timeout period  $(t_{RP})$ , allowing a system microcontroller  $(\mu C)$  to reset and start to operate. The MAX16165/MAX16166 monitor each sequenced voltage fed back on SET\_ after the respective channel is enabled. The MAX16165/MAX16166 also monitor UVSET input for undervoltage condition after power up. If any voltage falls below its threshold, the POK and DONE outputs deassert and all outputs are disabled simultaneously to turn off all sequenced power supplies. During any fault condition except UVSET undervoltage detection, a one-shot pulse of pulse width  $80\mu S$  (typ) is asserted on the FAULT pin. The device enters into the fault condition and initializes the state machine, waiting for a power-on sequencing command again. If an undervoltage condition is present at UVSET, FAULT stays low as long as the undervoltage condition persists.

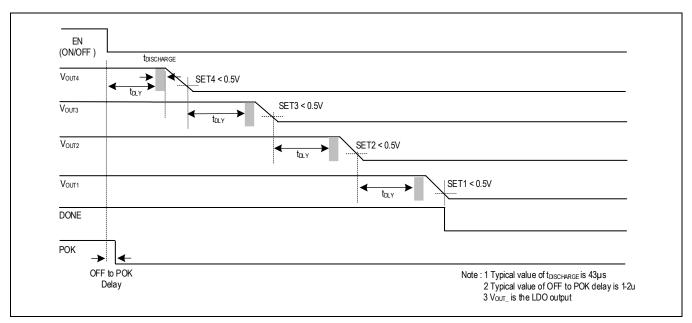

When the sequencer initiates a power-off sequencing, the MAX16165/MAX16166 provide the delay time  $t_{DLY}$  before the fourth output is disabled. At the time the fourth output is disabled, the device injects a resistor-programmable offset current ( $l_{OFFSET}$ ) to SET4 input and monitors the voltage at SET4. When SET4 voltage drops below its threshold, the MAX16165/MAX16166 wait for another delay time  $t_{DLY}$ , and then disable the third output. The power-off sequencing repeats until the first output is disabled. When the power-off sequencing is completed, DONE output asserts low. The MAX16165/MAX16166 can be cascaded to control a higher number of power supplies in a system.

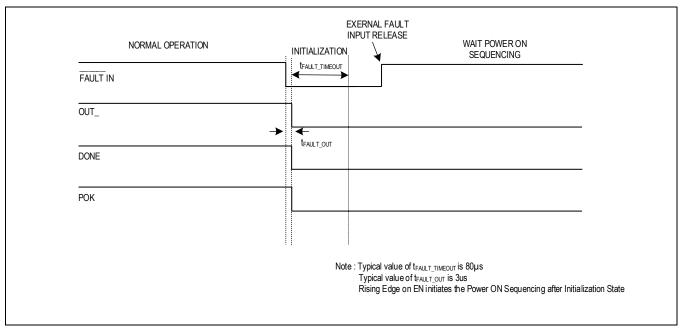

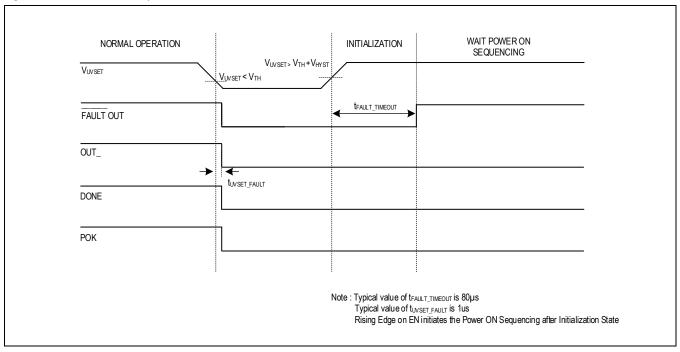

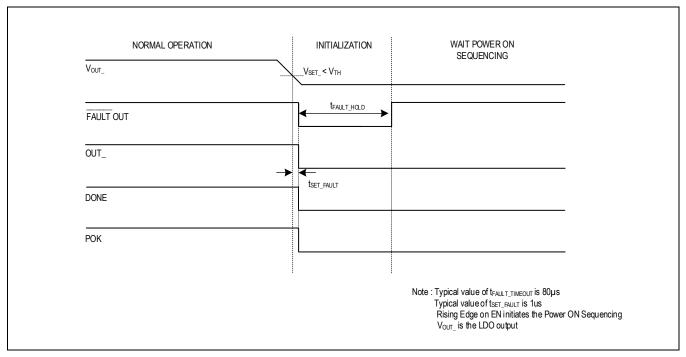

#### **FAULT** Input/Output

FAULT is bidirectional. It is an active low input and active low open-drain output. When an internal fault is detected, this pin is asserted low. An external signal pulling this pin low disables all outputs and sets the MAX16165/MAX16166 to a fault condition. See the <u>State Diagram</u> for all the conditions that assert a FAULT. During any fault condition except UVSET undervoltage detection, a one-shot pulse of pulse width 80µs (typ) is asserted. See the <u>Applications Information</u> section to understand how the FAULT output can be modified to achieve extended assert duration in applications where DC-DC converters having slow powerup are used.

For multichip solutions, all of the FAULT input/outputs can be connected together. In case of a fault condition, all outputs on every device are turned off simultaneously.

Figure 1. External Fault Response

Figure 2. UVSET Fault Response

Figure 3. SET Fault Response

#### Skip or Disable Channels

If fewer than four channels are required, skip a channel by connecting the SET\_pin to ABP pin. The sequencing is similar with four-channel sequencing, just treat the MAX16165/MAX16166 like fewer channels. For example, if SET2 is connected to ABP, all logic for Channel 2 is removed from the state machine so there is not a delay, timer, UV detection, or fault triggered from this channel. If all channels are skipped, the device asserts DONE and POK immediately after initialization.

Channel skipping decision is decided during the initialization phase after every fault condition. The MAX16165/MAX16166 checks for the respective SET\_ voltage during the initialization phase. If the voltage at SET\_ is above 0.5V, the corresponding channel gets skipped. Therefore, it is important to ensure the voltage at SET\_ is below 0.5V after each fault condition. If the power supplies are not properly loaded, it can take a long time to discharge the channel SET\_ voltage. This situation is more crucial when Voff voltage levels are low or the load current of the power supply is less. See the <u>Applications Information</u> section for more information on how to avoid the false skipping of channels in this situation.

#### ON and OFF Inputs

The ON and  $\overline{\text{OFF}}$  inputs are edge triggered inputs with a threshold of 500mV, which are used to initiate power sequencing. If no FAULT condition persists, a rising edge on the ON input initiates power-on sequencing while a falling edge on  $\overline{\text{OFF}}$  initiates a power-down sequencing in the reverse order. A falling edge on ON input and a rising edge on  $\overline{\text{OFF}}$  input are ignored. Normally ON and  $\overline{\text{OFF}}$  inputs are tied together and used separately in special cases such as daisy-chaining.

It is important to ensure a voltage above 0.5V at ON input until the sequencing gets completed. If the ON input voltage falls below 0.5V or another rising edge happens at ON input, a FAULT is asserted resulting in stopping the sequencing and simultaneous power-off of all the outputs. See the <u>Daisy-Chaining the MAX16165/MAX16166</u> and <u>Typical Application</u> <u>Circuits</u> sections for more information.

#### **State Diagram**

#### **Applications Information**

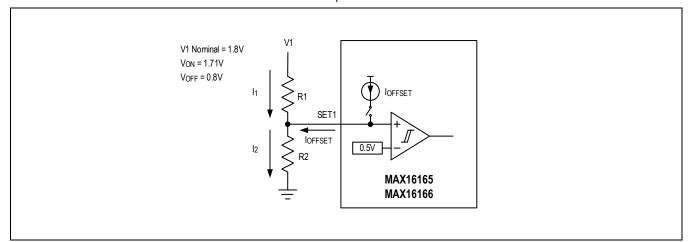

#### Selecting SET\_Feedback Resistors and Offset Current

For each sequenced power supply, choose a voltage when the power supply is considered to be ON during power-on sequencing (V<sub>ON</sub>) and a voltage when the power supply is considered to be OFF during power-off sequencing (V<sub>OFF</sub>). During power-off sequencing, an offset current I<sub>OFFSET</sub> is injected to the SET\_ pin so that V<sub>OFF</sub> is lower than V<sub>ON</sub> (see *Figure 4*). Calculate resistor values according to the following equations:

$$R1 = \left(\frac{V_{ON} - V_{OFF}}{I_{OFFSET}}\right)$$

$$R2 = R1 \times \left(\frac{0.5V}{V_{ON} - 0.5V}\right)$$

Use the formula shown below to calculate the RIOS for an offset current IOFFSET:

$$R_{IOS} = \left(\frac{0.5V}{I_{OFFSET}}\right)$$

For example, if power supply V1 nominal voltage is 1.8V, choose  $V_{ON}$  = 1.71V and  $V_{OFF}$  = 0.8V, offset current  $I_{OFFSET}$  = 5 $\mu$ A, R1 = 182k $\Omega$ , R2 = 75.21k $\Omega$ .

R1 =

$$\left(\frac{1.71V - 0.8V}{5\mu A}\right)$$

= 182 $k\Omega$

R2 = 182 $k\Omega \times \left(\frac{0.5V}{1.71V - 0.5V}\right)$  = 75.21 $k\Omega$

$R_{IOS} = \left(\frac{0.5V}{5\mu A}\right)$  = 100 $k\Omega$

Figure 4. Design of SET\_ Feedback Resistors and Offset Current

Connect a resistor with 1% tolerance from  $10k\Omega$  to  $1M\Omega$  at the IOS pin to achieve an offset current from  $0.5\mu$ A to  $50\mu$ A. To ensure correct power-down sequencing, adhere to the calculations provided in this section and calculate the SET\_ divider resistors in accordance with the  $l_{OFFSET}$  chosen. The resistor connected at IOS decides the  $l_{OFFSET}$  of all the channels.

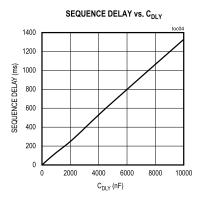

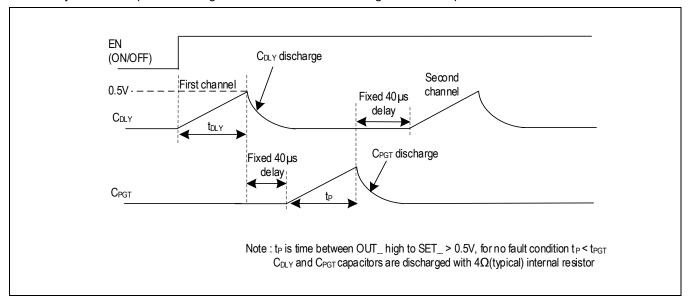

#### **Sequence Delay Time Input**

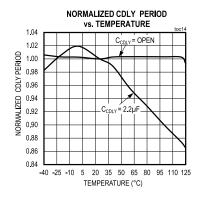

When the power-on sequence starts, the sequence delay time input (DLY) has an internal switch in series with an internal current source of  $4\mu A$ , which is connected to the  $C_{DLY}$  present at the DLY pin. This current charges the  $C_{DLY}$  linearly until the voltage reaches the threshold of 0.5V and signal to continue enabling the subsequent channel. Connect a capacitor ( $C_{DLY}$ ) between DLY and GND to adjust the sequencing delay period ( $t_{DLY}$ ) that occurs between sequenced channels. Use the following formula to estimate the delay:

$$t_{DLY} = 125K\Omega X C_{DLY}$$

where  $t_{DLY}$  is in seconds and  $C_{DLY}$  is in Farads. Leave DLY unconnected for the minimum 40µs (typ) delay. After each  $t_{DLY}$  the DLY capacitor discharges (internal  $4\Omega$ ) with typical  $40\mu$ s ( $t_{DISCHARGE}$ ) shown in <u>Figure 5</u>. The accuracy of the  $t_{DLY}$  is affected by the  $C_{DLY}$  capacitor leakage and tolerance. A low leakage ceramic capacitor is recommended.

Figure 5. Charging and Discharging of DLY and PGT Capacitor

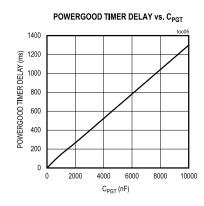

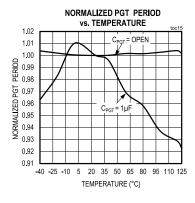

#### Power-Good Timer (PGT) and Power-Good Time Input

The Power Good Timer is used to check the capability of a power supply to reach a set voltage within a capacitor adjustable delay ( $t_{PGT}$ ). The FAULT output is asserted when any enabled voltage cannot reach its threshold on the SET\_pin within tPGT. The internal state machine should stop the PGT if SET\_voltage reaches 0.5V before the PGT expires. The MAX16165/MAX16166 do not have to wait for  $t_{PGT}$  to expire before moving to the next step. The PGT is only for power-on sequencing and not used during power-off sequencing. Like the DLY timer, the PGT circuit is also enabled by a  $4\mu$ A current source to charge the  $C_{PGT}$  capacitor.

Connect a capacitor ( $C_{PGT}$ ) between PGT and GND to adjust the sequencing delay period ( $t_{PGT}$ ). Use the following formula to estimate the delay:

$$t_{PGT} = 5\mu s + 125K\Omega X C_{PGT}$$

where  $t_{PGT}$  is in seconds and  $C_{PGT}$  is in Farads. Leave PGT unconnected for a minimum  $5\mu s$  (typ) delay. The accuracy of the delay is affected by the  $C_{PGT}$  capacitor leakage and tolerance. A low-leakage ceramic capacitor is recommended.

#### **Pullup Resistor Values**

The exact value of the pullup resistors for the open-drain outputs is not critical, but some consideration should be made to ensure the proper logic levels when the device is sinking current. For example, if  $V_{DD}$  = 3.3V and the pullup voltage is 5V, keep the sink current less than 3.2mA as shown in the <u>Electrical Characteristics</u> table. As a result, the pullup resistor should be greater than 1.6k $\Omega$ . For a 12V pullup, the resistor should be larger than 3.74k $\Omega$ .

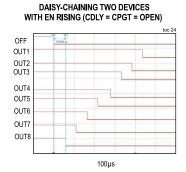

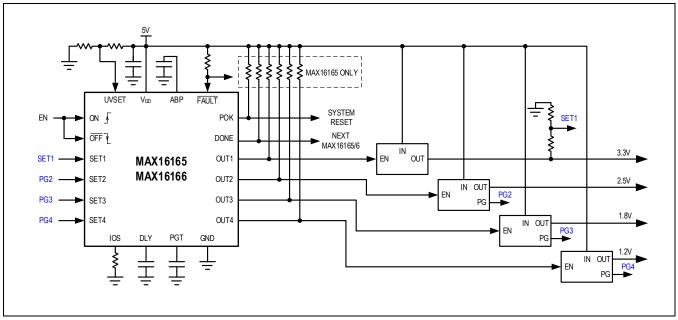

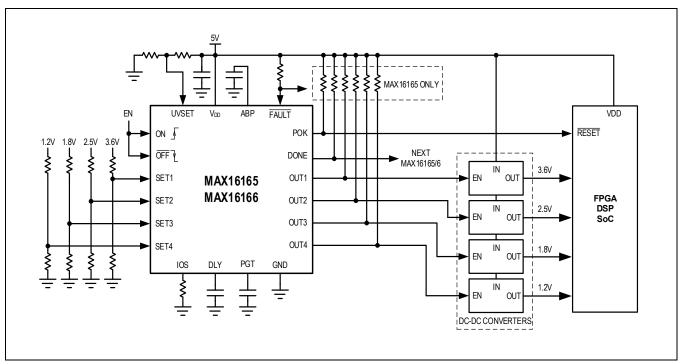

#### Daisy-Chaining the MAX16165/MAX16166

Multiple MAX16165/MAX16166 devices can be daisy-chained to sequence and monitor a large number of voltages. When a fault occurs on any of the monitored inputs, FAULT goes low which signals a fast power-down. Connect all FAULT pins of the MAX16165/MAX16166 together to ensure that all power supplies are turned off during a fault. Figure 13 shows an example of two daisy-chained devices.

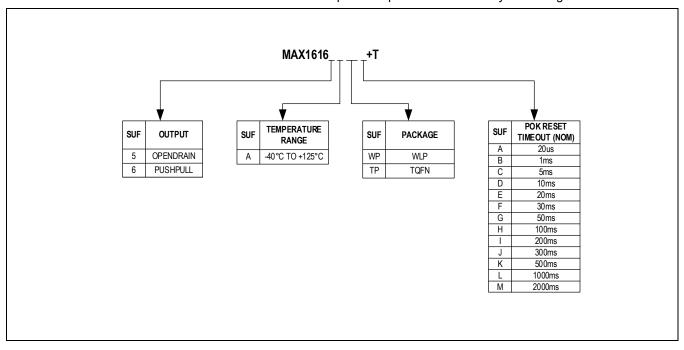

#### **Selection Guide Options**

The MAX16165/MAX16166 include different variants or device options; however, not all options are released for sale. Released variants are called standard models and are listed in the <u>Ordering Information</u>. For the most up to date list of standard models, refer to the product page's Sample & Buy section. Contact an Analog Devices sales representative for information on nonstandard models and be aware that samples and production units may have long lead times.

#### Layout and Bypassing

For better noise immunity, bypass VDD to GND with a  $0.1\mu\text{F}$  capacitor installed as close to the device as possible. Bypass ABP to GND with a  $1\mu\text{F}$  capacitor installed as close to the device as possible. Minimize stray capacitance on the SET\_inputs. The layout of the divider resistors should be as close to the MAX16165/MAX16166 as possible. Connect the exposed pad (EP) to the ground plane for improved heat dissipation. Do not use EP as the only ground connection for the device.

## **Typical Application Circuits**

#### Sequence Four Power Supplies, Monitor VDD, and Power-Good/Power-OK Outputs

Figure 6. Sequence Four Power Supplies, Monitor  $V_{DD}$ , V1 = 3.3V, and Power-Good Signals of the Other Three Power Supplies.

#### Monitor $V_{DD}$ and Sequence Four Power Supplies, without Monitoring

Figure 7. Sequence Four Power Supplies, without Monitoring. Only Monitor VDD.

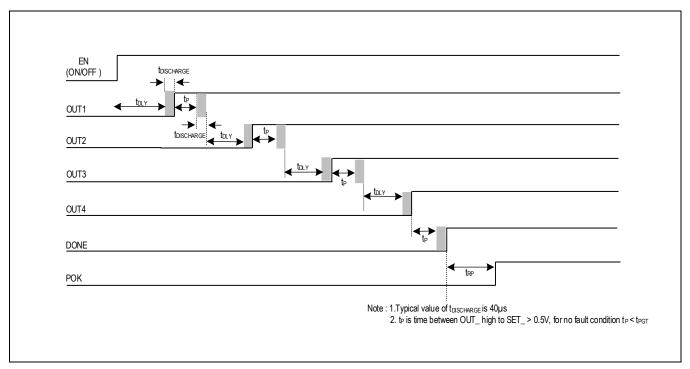

Figure 8. Power-Up Sequencing Timing Diagram. See the Typical Application Circuit (Figure 3).

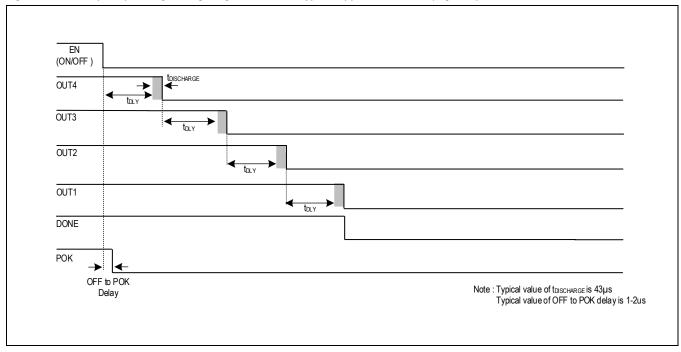

Figure 9. Power-Down Sequencing Timing Diagram. See the Typical Application Circuit (Figure 3).

#### Sequence and Monitor Four Power Supplies and Monitor VDD

Figure 10. Sequence Four Power Supplies and Monitor V<sub>DD</sub> and the Four Power Supplies.

Figure 11. Power-Up Monitoring Timing Diagram. See the Typical Application Circuit (Figure 6).

Figure 12. Power-Down Monitoring Timing Diagram. See the Typical Application Circuit (Figure 6).

#### Daisy-Chaining Using MAX16165/MAX16166

Figure 13. Sequence and Monitor Eight Power Supplies and Monitor VDD.

## **Ordering Information**

| PART NUMBER    | TEMP. RANGE     | PIN-PACKAGE | OUTPUTS    | POK RESET TIMEOUT |

|----------------|-----------------|-------------|------------|-------------------|

| MAX16166AWPH+T | -40°C to +125°C | 20 WLP      | Push-pull  | 100ms             |

| MAX16165ATPH+T | -40°C to +125°C | 20 TQFN     | Open-drain | 100ms             |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

Contact an Analog Devices sales representative for information on nonstandard models and be aware that samples and production units may have long lead times.

If ordering nonstandard models, complete the ordering code shown in Selection Guide Options.

T = Tape and reel.

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE                                                        | DESCRIPTION                                                                                                                                                                       | PAGES<br>CHANGED |

|--------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 11/21                                                                | Release for Market Intro                                                                                                                                                          | _                |

| 1                  | 1 4/22 Added MAX16165ATPH+T to the <i>Ordering Information</i> table |                                                                                                                                                                                   | 24               |

| 2                  | 6/24                                                                 | Corrected formula in the <i>Applications Information</i> section, changed header title from Selector Guide to Selection Guide Options, and updated the Ordering Information table | 17–19, 24        |

| 3                  | 1/25                                                                 | Added a Storage Temperature Range for 20 TQFN package in the <i>Absolute Maximum Ratings</i> section                                                                              | 3                |