#

## High-Speed, Wide-Input, Single-Phase MOSFET Driver

#### **General Description**

The MAX8552 highly integrated monolithic MOSFET driver is capable of driving a pair of power MOSFETs in single or multiphase synchronous buck-converter applications that provide up to 30A output current per phase. The MAX8552 simplifies PC board layout in multiphase systems, particularly three phases and higher. High input voltages up to 24V allow the MAX8552 to be used in desktop, notebook, and server applications. Each MOSFET driver is capable of driving 3000pF capacitive loads with only 12ns propagation delay and 11ns (typ) rise and fall times, making the MAX8552 ideal for high-frequency applications.

User-programmable break-before-make circuitry prevents shoot-through currents, maximizing converter efficiency. An enable input allows total driver shutdown (<1µA typ) for power-sensitive portable applications. The PWM control input is compatible with TTL and CMOS logic levels. The MAX8552, along with the MAX8524 or the MAX8525 multiphase controllers, provides flexible 2-, 3-, 4-, 6-, or 8-phase CPU core-voltage supplies.

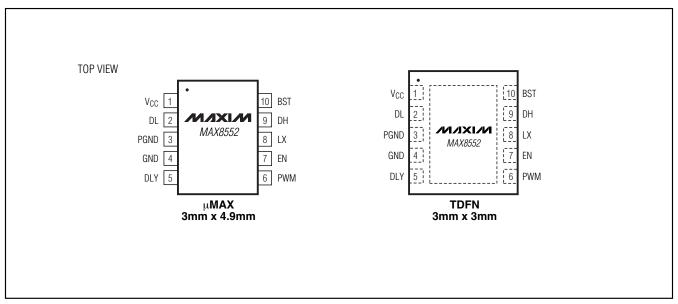

The MAX8552 is available in space-saving 10-pin TDFN and µMAX packages and is specified for -40°C to +85°C operation.

### **Applications**

Multiphase Buck Converters Voltage Regulator Modules (VRMs) Processor-Core Voltage Regulators Desktops, Notebooks, and Servers Switching Power Supplies

## **Features**

- **♦ Single-Phase Synchronous Drivers**

- ♦ Up to 24V (max) Input Voltage

- ♦ 0.1µA (typ) Quiescent Current in Shutdown Over **Temperature**

- ♦ 0.5Ω/1.0Ω/0.7Ω/1.3Ω ROUT Drivers

- ♦ 12ns (typ) Propagation Delay

- ♦ 11ns (typ) Rise/Fall Times with 3000pF Load

- **♦** Adaptive Dead Time and User-Programmable **Delay Mode**

- ♦ Up to 2MHz Operation with TDFN Package

- ♦ Up to 1.2MHz Operation with µMAX Package

- **♦ Enable Function**

- **♦ TTL- and CMOS-Compatible Logic Inputs**

- ♦ Available in a Space-Saving Thin DFN Package

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE          |

|------------|----------------|----------------------|

| MAX8552EUB | -40°C to +85°C | 10 μMAX              |

| MAX8552ETB | -40°C to +85°C | 10 TDFN<br>3mm x 3mm |

Pin Configurations appear at end of data sheet.

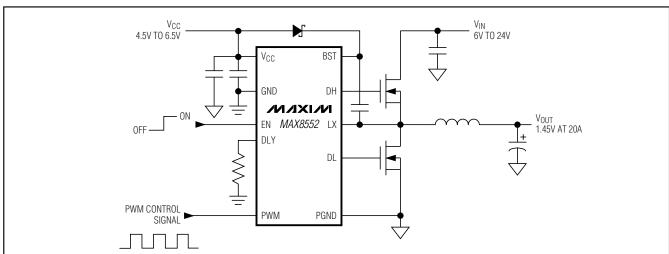

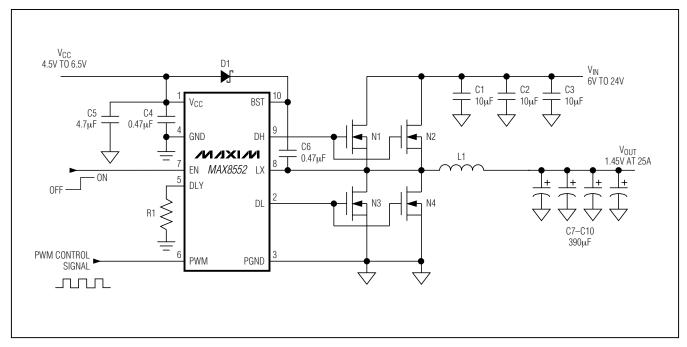

### Typical Operating Circuit

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC to GND                   | 0.3V to +7V                       | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|------------------------------|-----------------------------------|-------------------------------------------------------|

| PWM, EN, DL, DLY to GND      | 0.3V to (VCC + 0.3V)              | 10-Pin µMAX (derate 5.6mW/°C above +70°C)444.4mW      |

| BST to PGND                  | 0.3V to +35V                      | 10-Pin TDFN (derate 24.4mW/°C above +70°C)1951mW      |

| LX to PGND                   | 1V to +28V                        | Operating Temperature Range40°C to +85°C              |

| DH to PGND                   | 0.3V to (V <sub>BST</sub> + 0.3V) | Junction Temperature+150°C                            |

| DH, BST to LX                | 0.3V to +7V                       | Storage Temperature Range65°C to +150°C               |

| DH and DL Continuous Current | ±200mA                            | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{BST} = V_{DLY} = V_{EN} = 5V, V_{GND} = V_{PGND} = V_{LX} = 0V; T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 1)

| PARAMETER                            | CON                                           | IDITIONS                                              | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|-----------------------------------------------|-------------------------------------------------------|------|------|------|-------|

| UNDERVOLTAGE PROTECTION              | N                                             |                                                       |      |      |      | •     |

| V <sub>CC</sub> Supply Voltage Range |                                               |                                                       | 4.5  |      | 6.5  | V     |

| Lindowieltowa Lagicaut (LIVII O)     | O OFW by stores is                            | V <sub>CC</sub> rising                                | 3.25 |      | 3.80 | V     |

| Undervoltage Lockout (UVLO)          | 0.25V hysteresis                              | V <sub>CC</sub> falling                               | 3.0  |      | 3.5  | V     |

| Objects leaves Occurred to           | 07.77                                         | PWM = GND or $V_{CC}$ , $T_{A}$ = +25°C               |      | 0.04 | 1    | ^     |

| Shutdown Supply Current              | $V_{EN} = 0V$ , $V_{CC} = 6.5V$               | PWM = GND or $V_{CC}$ , $T_A = +85^{\circ}C$          |      | 0.1  |      | μA    |

| Idle Supply Current (ICC)            | No switching                                  | $V_{CC} = 6.5V$ , $PWM = GND$ , $R_{DLY} = 47k\Omega$ |      | 330  | 500  | μA    |

|                                      | NIitlei                                       | PWM = GND                                             |      | 25   | 50   | μΑ    |

| Control Cumply Current (lave)        | No switching                                  | PWM = V <sub>CC</sub>                                 |      | 2    | 3    | mA    |

| Control Supply Current (IGND)        | Switching                                     | f <sub>PWM</sub> = 250kHz,<br>50% duty cycle          |      | 1.8  | 3    | mA    |

|                                      | No quitalaina I                               | PWM = GND                                             |      | 0.1  | 10   | μΑ    |

|                                      | No switching, I <sub>CC</sub>                 | PWM = V <sub>C</sub> C                                |      | 1.2  | 2    | mA    |

| Driver Supply Current (IPGND)        | No awitahing Inca                             | PWM = GND                                             |      | 0.1  | 10   | μΑ    |

|                                      | No switching, I <sub>BST</sub>                | $PWM = V_{CC}$                                        |      | 1.2  | 2    | mA    |

|                                      | Switching, I <sub>BST</sub> + I <sub>CC</sub> | 250kHz                                                |      | 2    | 4    | IIIA  |

| <b>DRIVER SPECIFICATIONS</b> (See    | the Timing Diagram)                           |                                                       |      |      |      |       |

|                                      | PWM = GND,                                    | $V_{BST} = 4.5V$                                      |      | 1.3  | 2.4  |       |

| DH Driver Resistance                 | sourcing current                              | V <sub>BST</sub> = 5V                                 |      | 1.2  |      | Ω     |

| DITIONNEL MESISTATICE                | $PWM = V_{CC}$                                | $V_{BST} = 4.5V$                                      |      | 0.7  | 1.1  | 52    |

|                                      | sinking current                               | V <sub>BST</sub> = 5V                                 |      | 0.6  |      |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{BST} = V_{DLY} = V_{EN} = 5V, V_{GND} = V_{PGND} = V_{LX} = 0V; T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 1)

| PARAMETER                            | CC                                                                                               | ONDITIONS                               | MIN  | TYP  | MAX   | UNITS |

|--------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------|------|------|-------|-------|

|                                      | PWM = GND,                                                                                       | $V_{CC} = 4.5V$                         |      | 1.0  | 1.6   |       |

| DL Driver Resistance                 | sourcing current                                                                                 | $V_{CC} = 5V$                           |      | 0.9  |       |       |

| DL Driver Resistance                 | $PWM = V_{CC}$                                                                                   | V <sub>CC</sub> = 4.5V                  |      | 0.5  | 0.8   | Ω     |

|                                      | sinking current                                                                                  | $V_{CC} = 5V$                           |      | 0.45 |       |       |

| DH Rise Time (t <sub>rDH</sub> )     | $PWM = V_{CC}$                                                                                   | V <sub>BST</sub> = 5V, 3000pF load      |      | 14   |       | ns    |

| DH Fall Time (t <sub>fDH</sub> )     | PWM = GND                                                                                        | V <sub>BST</sub> = 5V, 3000pF load      |      | 9    |       | ns    |

| DL Rise Time (t <sub>rDL</sub> )     | $PWM = V_{CC}$                                                                                   | V <sub>CC</sub> = 5V, 3000pF load       |      | 11   |       | ns    |

| DL Fall Time (tfDL)                  | PWM = GND                                                                                        | V <sub>CC</sub> = 5V, 3000pF load       |      | 8    |       | ns    |

|                                      | PWM falling (tpDHf)                                                                              | V <sub>BST</sub> = 5V                   |      | 12   |       |       |

| DH Propagation Delay                 | PWM = V <sub>CC</sub> ,<br>DL falling (t <sub>pDHr</sub> )                                       | V <sub>BST</sub> = 5V                   |      | 14   |       | ns    |

|                                      | PWM rising (tpDLf)                                                                               |                                         |      | 9    |       |       |

| DL Propagation Delay                 | PWM = GND,<br>LX falling (t <sub>pDLr</sub> )                                                    | V <sub>BST</sub> - V <sub>LX</sub> = 5V |      | 16   |       | ns    |

| EN                                   |                                                                                                  |                                         |      |      |       |       |

| Leakage Current                      | V <sub>PWM</sub> = 0V or 6.5V, V <sub>EN</sub><br>V <sub>CC</sub> = 6.5V, T <sub>A</sub> = +25°C | = 0V or 6.5V,                           |      | 0.01 | 1     |       |

| Leakage Current                      | V <sub>PWM</sub> = 0V or 6.5V, V <sub>EN</sub><br>V <sub>CC</sub> = 6.5V, T <sub>A</sub> = +85°C | = 0V or 6.5V,                           |      | 0.1  |       | μА    |

| Input-Voltage High Threshold         | Vcc = 6.5V                                                                                       |                                         |      |      | 2.5   | V     |

| Input-Voltage Low Threshold          | $V_{CC} = 4.5V$                                                                                  |                                         | 0.8  |      |       | V     |

| PWM                                  |                                                                                                  |                                         |      |      |       |       |

| Leakage Current                      | V <sub>PWM</sub> = 0V or 6.5V, V <sub>EN</sub><br>V <sub>CC</sub> = 6.5V, T <sub>A</sub> = +25°C | = 0V or 6.5V,                           |      | 0.01 | 1     | μА    |

| Leanage Current                      | V <sub>PWM</sub> = 0V or 6.5V, V <sub>EN</sub><br>V <sub>CC</sub> = 6.5V, T <sub>A</sub> = +85°C | = 0V or 6.5V,                           |      | 0.1  |       | μΑ    |

| Input-Voltage High Threshold         | $V_{CC} = 6.5V$                                                                                  |                                         |      |      | 3.5   | V     |

| Input-Voltage Low Threshold          | V <sub>CC</sub> = 4.5V                                                                           |                                         | 1.2  |      |       | V     |

| Input Threshold Hysteresis           |                                                                                                  |                                         |      | 0.5  |       | V     |

| DLY                                  |                                                                                                  |                                         |      |      |       |       |

| Delay Program Accuracy               | $R_{DLY} = 47k\Omega$ , DL fall to [                                                             | DH rise                                 | 67.5 | 90.0 | 112.5 | ns    |

| Delay Disable-Detection<br>Threshold |                                                                                                  |                                         | 4.0  |      | 4.7   | V     |

**Note 1:** Specifications are production tested at  $T_A = +25^{\circ}C$ . Maximum and minimum limits are guaranteed by design and characterization.

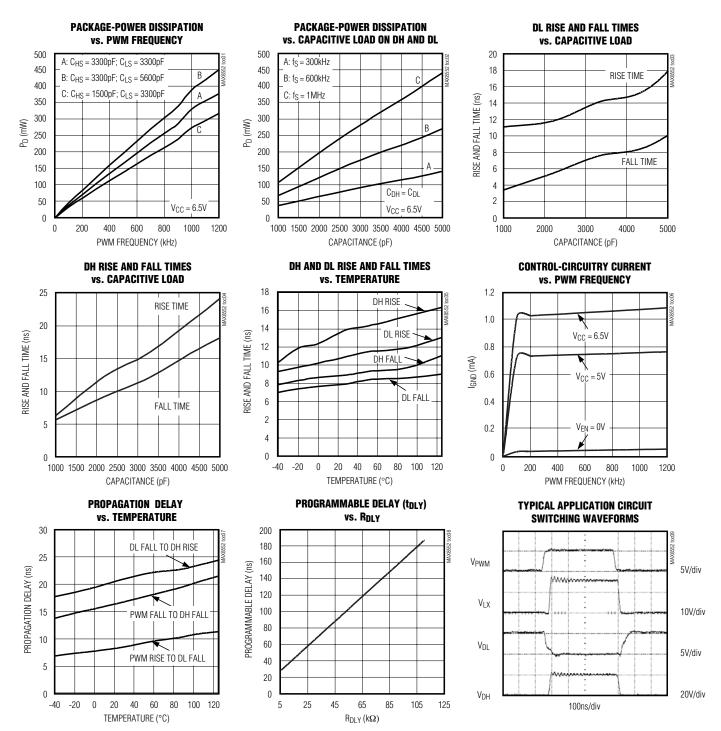

### Typical Operating Characteristics

$(V_{CC} = V_{DLY} = 5V, C_{HS\_LOAD} = C_{LS\_LOAD} = 3000pF, 50\%$  duty ratio.)

## Pin Description

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                                                 |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc                | Input Supply Voltage. Connect to a supply voltage in the 4.5V to 6.5V range. Bypass to PGND with a 2.2µF or larger capacitor, and bypass to GND with a 0.47µF or larger capacitor.                                                                                                       |

| 2   | DL                 | External Synchronous-Rectifier N-MOSFET Gate-Driver Output. Swings between V <sub>CC</sub> and PGND. Anticrowbar feature prevents DL from turning on until DH is off and (LX - PGND) < 2V. DL is pulled to GND in shutdown.                                                              |

| 3   | PGND               | Power Ground                                                                                                                                                                                                                                                                             |

| 4   | GND                | Analog Ground                                                                                                                                                                                                                                                                            |

| 5   | DLY                | Dead-Time Delay Programming Input. Connect a resistor from DLY to GND to set the dead-time delay between when DL falls and when DH rises. Connect DLY to V <sub>CC</sub> to disable the delay function. See the <i>Typical Operating Characteristics</i> for R <sub>DLY</sub> selection. |

| 6   | PWM                | PWM Input. DH is high when PWM is high; DL is high when PWM is low. Input frequency can be as high as 1.2MHz for the 10-pin µMAX package and as high as 2MHz for the 10-pin TDFN package.                                                                                                |

| 7   | EN                 | Enable Input. Drive high to enable output drivers. Drive low to disable output drivers and place the IC in low-power shutdown mode.                                                                                                                                                      |

| 8   | LX                 | Switching Node and Inductor Connection. Low power supply for the DH high-side gate driver. Connect to the source of the high-side N-MOSFET and the drain of the low-side N-MOSFET, as well as the switched side of the inductor.                                                         |

| 9   | DH                 | External High-Side N-MOSFET Gate-Driver Output. Swings between LX and BST. Anticrowbar feature delays DH from turning on until DL is off. An additional user-programmable delay can be added. DH is pulled to LX in shutdown.                                                            |

| 10  | BST                | Boost Flying-Capacitor Connection. Gate-drive power supply for DH high-side gate driver. Connect a 0.47µF or larger capacitor between BST and LX.                                                                                                                                        |

| _   | Exposed<br>Paddle* | Exposed Paddle. Connect to GND.                                                                                                                                                                                                                                                          |

<sup>\* 10-</sup>pin TDFN only.

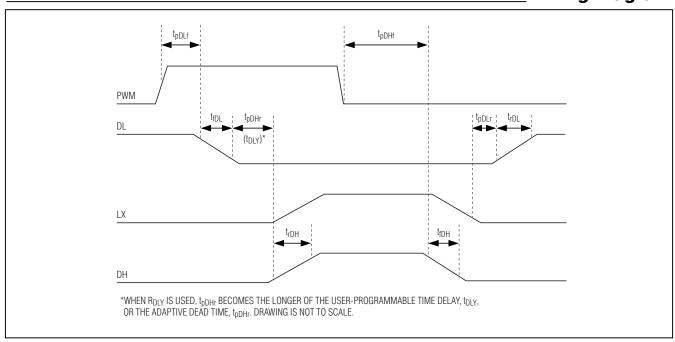

### **Timing Diagram**

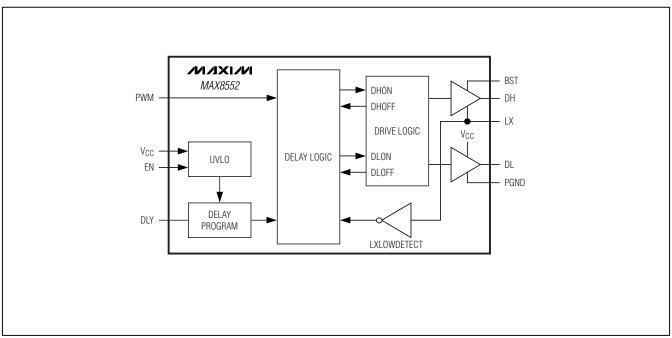

## Functional Diagram

6 \_\_\_\_\_\_\_\_\_\_\_\_/NI/XI/M

#### **Detailed Description**

The MAX8552 single-phase gate driver, along with the MAX8524/MAX8525 multiphase controllers, provide flexible one- to eight-phase CPU core-voltage supplies. The  $1.0\Omega/1.3\Omega$  driver resistance allows up to 30A output current per phase. Each MOSFET driver in the MAX8552 is capable of driving 3000pF capacitive loads with only 12ns propagation delay and 11ns (typ) rise and fall times, allowing operation up to 1.2MHz per phase. Adaptive dead time controls MOSFET turn-on, and user-programmable dead time provides additional flexibility for high-side MOSFET turn-on. This maximizes converter efficiency, while allowing operation with a varietv of MOSFETs and PWM-controller ICs. An undervoltage-lockout circuit allows proper power-on sequencing. The PWM signal input is both TTL and CMOS compatible. An enable input allows total driver shutdown (<0.1µA typ) for power-sensitive portable applications.

#### **MOSFET Gate Drivers (DH, DL)**

The high-side driver (DH) has a  $1.3\Omega$  (typ) sourcing resistance and  $0.7\Omega$  sinking resistance, resulting in 4A peak sourcing current and 7A peak sinking current with a 5V supply voltage. The low-side driver (DL) has a typical  $1.0\Omega$  sourcing resistance and  $0.5\Omega$  sinking resistance, yielding 5A peak sourcing current and 10A peak sinking current. This reduces switching losses, making the MAX8552 ideal for both high-frequency and high-output-current applications.

# Shoot-Through Protection and Programmable Delay (t<sub>DLY</sub>)

The MAX8552 incorporates adaptive shoot-through protection for the switching transition after the high-side MOSFET turns off and before the low-side MOSFET turns on and vice versa. The low-side driver turns on only when the LX voltage falls below 2.4V. Furthermore, the delay time between the low-side MOSFET turn-off and high-side MOSFET turn-on can be adjusted by selecting the value of R1 (see the *RpLy Selection* section).

#### **Undervoltage Lockout**

When  $V_{CC}$  is below the UVLO threshold (3.5V typ), DH and DL are held low. Once  $V_{CC}$  is above the UVLO threshold and while PWM is low, DL is driven high and DH is driven low. This prevents the output of the converter from rising before a valid PWM signal is applied.

#### EN

When EN is low, the MAX8552 is in shutdown mode and the total input current is reduced to less than  $1\mu A$  for power-sensitive applications. In shutdown mode, both DH and DL are held low. When EN goes high, the MAX8552 becomes active.

### **Applications Information**

#### **Decoupling of Vcc**

$V_{CC}$  provides the supply voltage for the internal logic circuits. Bypass  $V_{CC}$  with a 2.2 $\mu$ F or larger capacitor to PGND and a 0.47 $\mu$ F or larger capacitor to GND to limit noise to the internal circuitry. Connect these bypass capacitors as close to the IC as possible.

#### **Boost Flying-Capacitor Selection**

The MAX8552 uses a bootstrap circuit to generate the necessary drive voltage (V<sub>DH</sub>) to fully enhance the high-side N-MOSFET. The selected high-side MOSFET determines appropriate boost capacitance values (C6 in the Typical Application Circuit, Figure 1), according to the following equation:

#### CBST = QGATE / ΔVBST

where  $Q_{GATE}$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST}$  is the voltage variation allowed on the high-side MOSFET driver. Choose  $\Delta V_{BST}=0.1V$  to 0.2V when determining  $C_{BST}$ . The boost flying-capacitor should be a low-equivalent series resistance (ESR) ceramic capacitor.

#### **RDLY Selection**

Connect DLY to V<sub>CC</sub> to disable the programmable delay function and default to the adaptive delay time. To program a longer specific delay time between the low-side MOSFET driver turn-off and the high-side MOSFET turn-on, connect a delay resistor, R<sub>DLY</sub>, between DLY and GND (R1 in the Typical Application Circuit, Figure 1). See the *Typical Operating Characteristics* to select R<sub>DLY</sub>.

#### Avoiding dV/dt Turning on the Low-Side MOSFET

At high input voltages, fast turn-on of the high-side MOSFET can momentarily turn on the low-side MOSFET due to the high dV/dt appearing at the drain of the low-side MOSFET. The high dV/dt causes a current flow through the Miller capacitance (CRSS) and the input capacitance (CISS) of the low-side MOSFET. Improper selection of the low-side MOSFET that results in a high ratio of CRSS/CISS makes the problem more severe. To avoid this problem, minimize the ratio of CRSS/CISS when selecting the low-side MOSFET. Adding a  $1\Omega$  resistor between BST and CBST can slow the high-side MOSFET turn-on. Similarly, adding a small capacitor from the gate to the source of the high-side MOSFET has the same effect. However, both methods work at the expense of increased switching losses.

Figure 1. Typical Application Circuit

Table 1. Typical Component Values (500kHz Operation, 25A/Phase Output Current)

| DESIGNATION | DESCRIPTION                                                       | PART                            |

|-------------|-------------------------------------------------------------------|---------------------------------|

| C1, C2, C3  | 10μF, 25V ceramic capacitor                                       | Taiyo Yuden TMK432BJ106MM       |

| C4          | 4.7μF, 10V ceramic capacitor                                      | Taiyo Yuden LMK316 BJ475ML      |

| C5, C6      | 0.47µF, 10V ceramic capacitor                                     | Taiyo Yuden LMK107BJ474KA       |

| C7-C10      | 390μF/2V SP capacitor                                             | Panasonic EEFUE0D391XR          |

| D1          | 30V, 200mA, V <sub>F</sub> = 0.5V Schottky diode                  | Fairchild BAT54S                |

| L1          | $0.66\mu H/29A$ , $0.9m\Omega$ typical R <sub>DC</sub> resistance | Panasonic PCC-NX3               |

| N1, N2      | 30V, 14A N-MOSFET                                                 | International Rectifier IRF7821 |

| N3, N4      | 30V, 18A N-MOSFET                                                 | International Rectifier IRF7832 |

| R1          | $6k\Omega$ - 125kΩ = 1%, 1/8W resistor                            | Panasonic                       |

#### **Layout Guidelines**

The MAX8552 MOSFET driver sources and sinks large currents to drive MOSFETs at high switching speeds. The high di/dt can cause unacceptable ringing if the trace lengths and impedances are not well controlled. The following PC board layout guidelines are recommended when designing with the MAX8552:

- 1) Place all decoupling capacitors as close to their respective IC pins as possible.

- 2) Minimize the length of the high-current loop from the input capacitor, the upper switching MOSFET, and the low-side MOSFET back to the input-capacitor negative terminal.

- 3) Provide enough copper area at and around the switching MOSFETs and inductors to aid in thermal dissipation.

- Connect PGND of the MAX8552 as close as possible to the source of the low-side MOSFETs.

- 5) Keep LX away from sensitive analog components and nodes. Place the IC and the analog components on the opposite side of the board from the power-switching node if possible.

A sample layout is available in the MAX8552 evaluation kit.

### Chip Information

TRANSISTOR COUNT: 638

PROCESS: BICMOS

### Pin Configurations

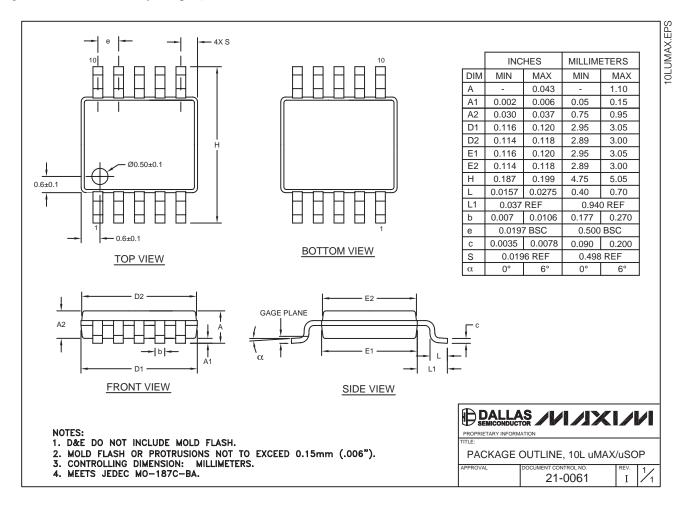

#### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

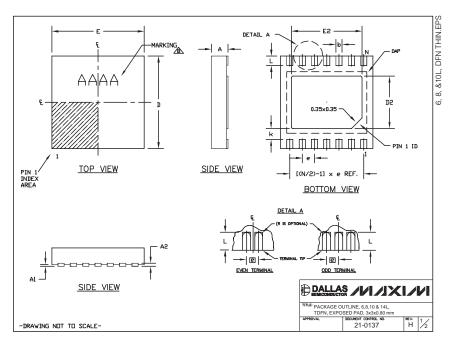

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| COMMON                                                                      | DIMEN                                                     | SIONS                                      |                                                                   | PACKAGE V                                                                                                        | ARIAT                       | TONS                                |            |          |                          |           |               |             |

|-----------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------|------------|----------|--------------------------|-----------|---------------|-------------|

| SYMBOL                                                                      | MIN.                                                      | MAX.                                       |                                                                   | PKG. CODE                                                                                                        | N                           | D2                                  | E2         | е        | JEDEC SPEC               | b         | [(N/2)-1] x e |             |

| Α                                                                           | 0.70                                                      | 0.80                                       |                                                                   | T633-1                                                                                                           | 6                           | 1.50±0.10                           | 2.30±0.10  | 0.95 BSC | MO229 / WEEA             | 0.40±0.05 | 1.90 REF      |             |

| D                                                                           | 2.90                                                      | 3.10                                       |                                                                   | T633-2                                                                                                           | 6                           | 1.50±0.10                           | 2.30±0.10  | 0.95 BSC | MO229 / WEEA             | 0.40±0.05 | 1.90 REF      |             |

| E                                                                           | 2.90                                                      | 3.10                                       |                                                                   | T833-1                                                                                                           | 8                           | 1.50±0.10                           | 2.30±0.10  | 0.65 BSC | MO229 / WEEC             | 0.30±0.05 | 1.95 REF      |             |

| A1                                                                          | 0.00                                                      | 0.05                                       |                                                                   | T833-2                                                                                                           | 8                           | 1.50±0.10                           | 2.30±0.10  | 0.65 BSC | MO229 / WEEC             | 0.30±0.05 | 1.95 REF      |             |

| L                                                                           | 0.20                                                      | 0.40                                       |                                                                   | T833-3                                                                                                           | 8                           | 1.50±0.10                           | 2.30±0.10  | 0.65 BSC | MO229 / WEEC             | 0.30±0.05 | 1.95 REF      |             |

| k                                                                           | 0.25                                                      | MIN.                                       |                                                                   | T1033-1                                                                                                          | 10                          | 1.50±0.10                           | 2.30±0.10  | 0.50 BSC | MO229 / WEED-3           | 0.25±0.05 | 2.00 REF      |             |

| A2                                                                          | 0.20                                                      | REF.                                       |                                                                   | T1033-2                                                                                                          | 10                          | 1.50±0.10                           | 2.30±0.10  | 0.50 BSC | MO229 / WEED-3           | 0.25±0.05 | 2.00 REF      |             |

|                                                                             |                                                           |                                            |                                                                   | T1433-1                                                                                                          | 14                          | 1.70±0.10                           | 2.30±0.10  | 0.40 BSC |                          | 0.20±0.05 | 2.40 REF      |             |

|                                                                             |                                                           |                                            |                                                                   | T1433-2                                                                                                          | 14                          | 1.70±0.10                           | 2.30±0.10  | 0.40 BSC |                          | 0.20±0.05 | 2.40 REF      |             |

| NOTES:                                                                      |                                                           |                                            |                                                                   |                                                                                                                  |                             |                                     |            |          |                          |           |               |             |

| 1. ALL [<br>2. COPL<br>3. WARP<br>4. PACK<br>5. DRAW<br>6. "N" 1<br>7. NUME | ANARITY<br>AGE SH<br>AGE LEI<br>ING CO<br>S THE<br>IER OF | SHALL IALL NO NGTH/PA NFORMS TOTAL N LEADS | NOT EXC<br>T EXCEED<br>ACKAGE V<br>TO JEDE<br>IUMBER O<br>SHOWN A | . ANGLES IN<br>SEED 0.08 m<br>0.10 mm.<br>VIDTH ARE CO<br>EC MO229, E<br>OF LEADS.<br>RE FOR REF<br>RIENTATION R | m.<br>ONSID<br>XCEP<br>EREN | ERED AS S<br>T DIMENSIO<br>CE ONLY. | NS "D2" AN |          | C(S).<br>ID T1433-1 & T  | 1433–2.   |               |             |

| 1. ALL [<br>2. COPL<br>3. WARP<br>4. PACK<br>5. DRAW<br>6. "N" 1<br>7. NUME | ANARITY<br>AGE SH<br>AGE LEI<br>ING CO<br>S THE<br>IER OF | SHALL IALL NO NGTH/PA NFORMS TOTAL N LEADS | NOT EXC<br>T EXCEED<br>ACKAGE V<br>TO JEDE<br>IUMBER O<br>SHOWN A | CEED 0.08 mm. 0 0.10 mm. WIDTH ARE CO EC MO229, E DF LEADS. WRE FOR REF                                          | m.<br>ONSID<br>XCEP<br>EREN | ERED AS S<br>T DIMENSIO<br>CE ONLY. | NS "D2" AN |          | DALL SEMICOND THE PACKAG | AS /L     | 3x3x0.80 mm   | <b>1</b> /1 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.