# **MCP8027**

# **3-Phase Brushless DC (BLDC) Motor Gate Driver** with Power Module, Sleep Mode

# Features

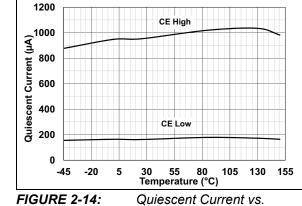

- Quiescent Current:

- Sleep mode: 5 µA typical

- Standby mode: < 200 μA

- Three Half-Bridge Drivers Configured to Drive External High-Side NMOS and Low-Side NMOS MOSFETs:

- Independent input control for high-side NMOS and low-side NMOS MOSFETs

- Peak output current: 0.5A at 12V

- Shoot-through protection

- Overcurrent and short-circuit protection

- Adjustable Output Buck Regulator (750 mW)

- Fixed Output Linear Regulators:

- 5V at 30 mA

- 12V at 30 mA

- Three Operational Amplifiers

- Overcurrent Comparator with DAC Reference

- Level Translators

- Input Voltage Range: 6V to 40V

- Operational Voltage Range:

- 6V to 28V

- Buck Regulator Undervoltage Lockout: 4V

- Undervoltage Lockout (UVLO): 5.5V (Except Buck)

- Overvoltage Lockout (OVLO): 32V

- High Temperature Range (T<sub>A</sub>): -40 to +150°C

- Thermal Shutdown

# Applications

- Industrial Fuel, Water, Ventilation Motors

- Home Appliances

- Permanent Magnet Synchronous Motor (PMSM) Control

- · Hobby Aircraft, Boats, Vehicles

# Description

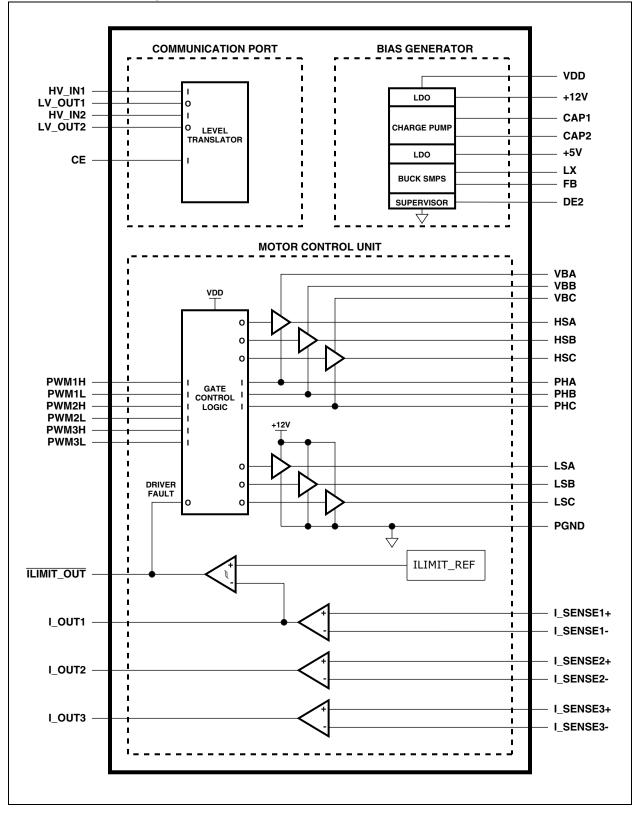

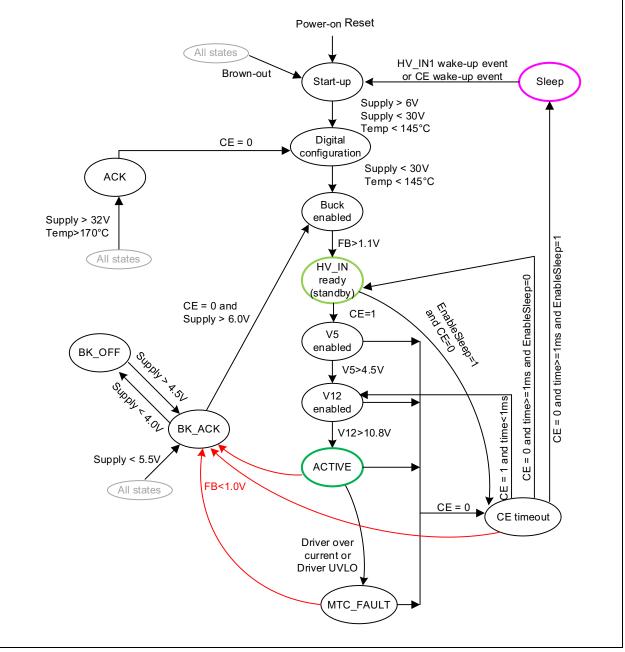

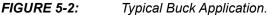

The MCP8027 device is a 3-phase Brushless DC (BLDC) power module, containing three integrated half-bridge drivers, capable of driving three external NMOS/NMOS transistor pairs. The three half-bridge drivers are capable of delivering a peak output current of 0.5A at 12V for driving high-side and low-side NMOS MOSFET transistors. The drivers have shoot-through, overcurrent and short-circuit protection. A Sleep mode has been added to achieve a typical "key-off" quiescent current of 5  $\mu$ A.

The MCP8027 device integrates a comparator, a buck voltage regulator, two LDO regulators, power monitoring comparators, an overtemperature sensor, with two level shifters, and three Op Amps. The buck converter is capable of delivering 750 mW of power for powering a companion microcontroller. The buck regulator may be disabled if not used. The on-board 5V and 12V Low-Dropout (LDO) voltage regulators are capable of delivering 30 mA of current.

The MCP8027 operation is specified over a temperature range of -40°C to +150°C.

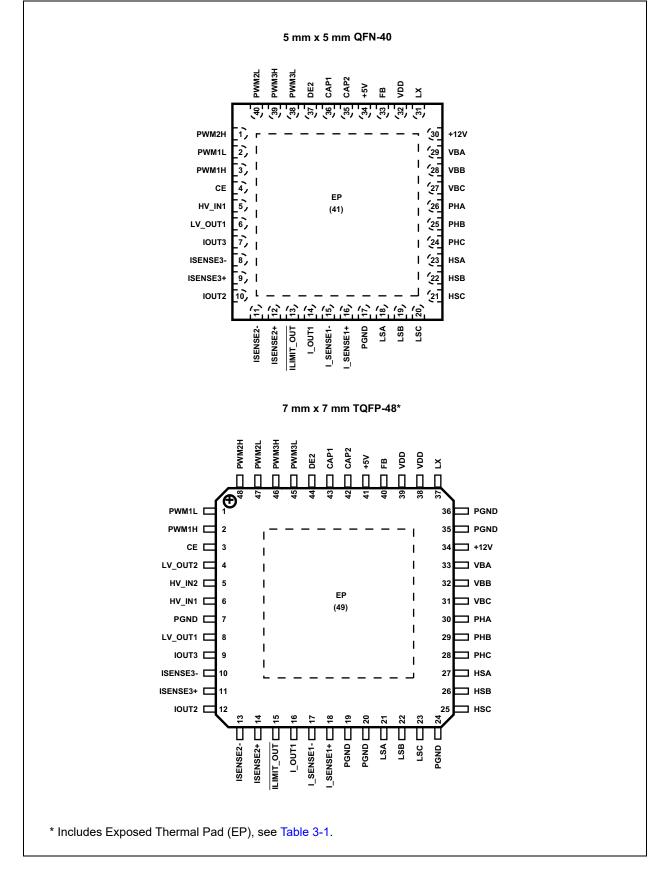

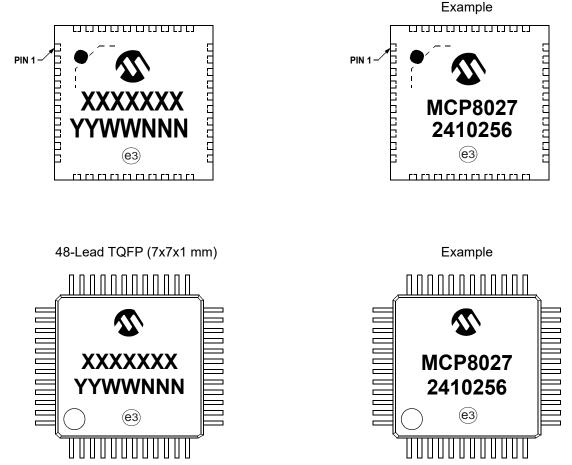

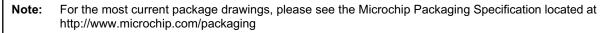

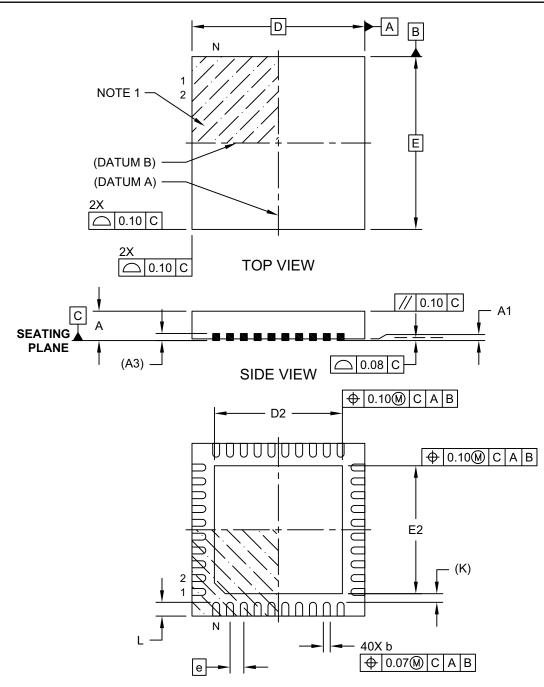

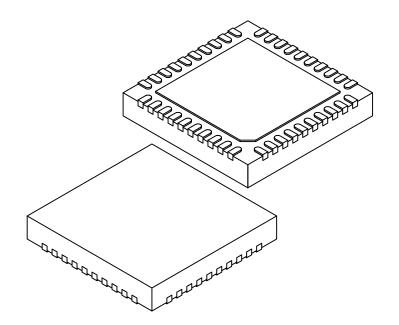

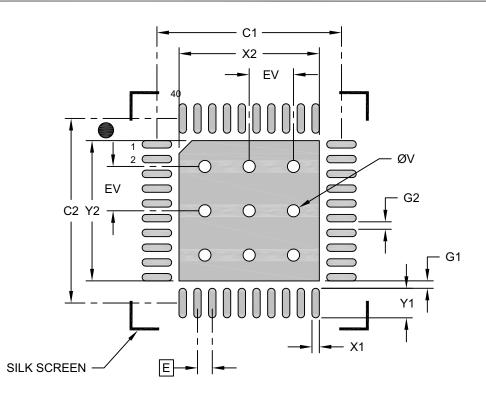

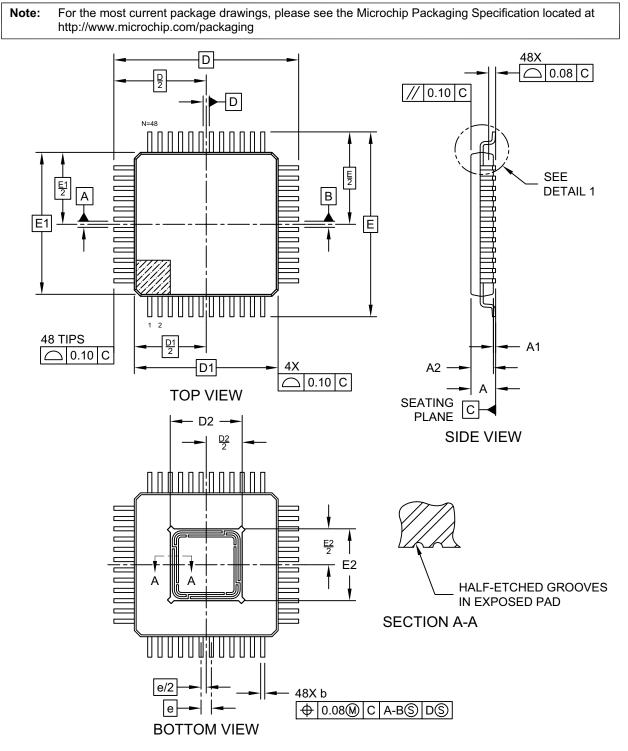

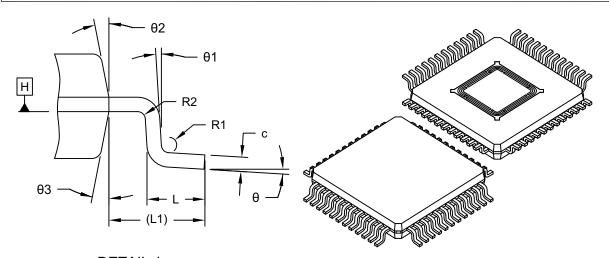

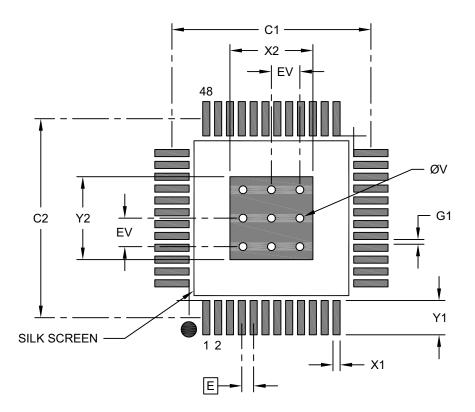

Package options include 40-Lead 5 x 5 mm QFN and 48-Lead 7 x 7 mm TQFP with Exposed Pad (EP).

# **Package Types**

# **Functional Block Diagram**

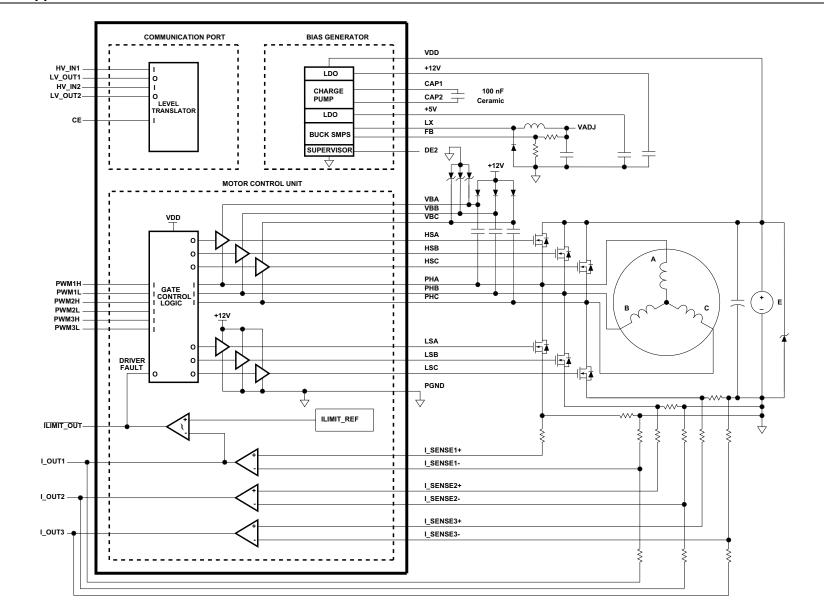

# **Typical Application Circuit**

**MCP8027**

# 1.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings<sup>†</sup>

| Input Voltage                           | +40V                                |

|-----------------------------------------|-------------------------------------|

| Internal Power Dissipation              | Internally-Limited                  |

| Operating Ambient Temperature Range     | 40°C to +150°C                      |

| Operating Junction Temperature (Note 1) | 40°C to +160°C                      |

| Transient Junction Temperature (Note 2) | +170°C                              |

| Storage Temperature (Note 1)            | 55°C to +150°C                      |

| Digital I/O                             | -0.3V to 5.5V                       |

| LV Analog I/O                           | 0.3V to 5.5V                        |

| VBx                                     | (GND – 0.3V) to +40V                |

| PHx, HSx                                | (GND – 5.5V) to +40V                |

| LSx                                     |                                     |

| ESD and Latch-up Protection:            |                                     |

| V <sub>DD</sub> , HV_IN1                | $\geq$ 8 kV HBM and $\geq$ 750V CDM |

| All other pins                          | $\geq$ 1 kV HBM and $\geq$ 750V CDM |

| Latch-up protection – all pins          | > 100 mA                            |

- **Note 1:** The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation may cause the device operating junction temperature to exceed the maximum +160°C rating. Sustained junction temperatures above +150°C can impact the device reliability and ROM data retention.

- 2: Transient junction temperatures should not exceed one second in duration. Sustained junction temperatures above +170°C may impact the device reliability.

- **† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| <b>Electrical Specifications:</b> Unless otherwise noted, $T_J = -40^{\circ}C$ to +150°C, typical values are for +25°C, $V_{DD} = 13V$ . |                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sym.                                                                                                                                     | Min.                                                                                           | Тур.                                                                                                                                                    | Max.                                                                                                                                                                                                                                                                                                                                       | Units                                                                                                                                                                                                                                                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                          |                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| V <sub>DD</sub>                                                                                                                          | 6                                                                                              | —                                                                                                                                                       | 28                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                | Operating range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                                                                                                                          | 6                                                                                              | —                                                                                                                                                       | 40                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                          | 4                                                                                              | _                                                                                                                                                       | 32                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Buck operating range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

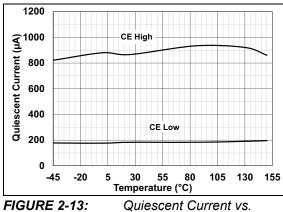

| I <sub>DD</sub>                                                                                                                          |                                                                                                | —                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                            | μA                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>DD</sub> > 13V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                          |                                                                                                | 5                                                                                                                                                       | 15                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Sleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                          | _                                                                                              | 120                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Standby, CE = 0V, T <sub>J</sub> = -45°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                          | _                                                                                              | 120                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Standby, CE = 0V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                          |                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                  | T <sub>J</sub> = +25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                                                                                          | —                                                                                              | 144                                                                                                                                                     | 300                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Standby, CE = 0V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                          |                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                  | T <sub>J</sub> = +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                                                                                                                          | _                                                                                              | 950                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Active, CE > V <sub>DIG_HI_TH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                          | _                                                                                              | 1090                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Active, $V_{DD}$ = 6V, $T_J$ = +25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| DIGITAL <sub>I/O</sub>                                                                                                                   | 0                                                                                              |                                                                                                                                                         | 5.5                                                                                                                                                                                                                                                                                                                                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| DIGITAL <sub>IOL</sub>                                                                                                                   |                                                                                                | 1                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                            | mA                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>DS</sub> < 50 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                                                                                                                          | Sym.<br>V <sub>DD</sub><br>I <sub>DD</sub><br>DIGITAL <sub>I/O</sub><br>DIGITAL <sub>I/O</sub> | Sym.         Min.           V <sub>DD</sub> 6           6         4           I <sub>DD</sub> DIGITAL <sub>I/O</sub> 0           DIGITAL <sub>IOL</sub> | Sym.         Min.         Typ. $V_{DD}$ 6            6          6           4          4 $I_{DD}$ 5            120             120             120             120             120             120             120             120             120             144            DIGITAL <sub>I/O</sub> 0            DIGITAL <sub>IOL</sub> 1 | Sym.         Min.         Typ.         Max. $V_{DD}$ 6         —         28           6         —         40           4         —         32 $I_{DD}$ —         — $I_{DD}$ —         — $$ 5         15 $$ 120         — $$ 120         — $$ 120         — $$ 144         300 $$ 950         — $$ 1090         —           DIGITAL <sub>I/O</sub> 0         —         5.5           DIGITAL <sub>IOL</sub> —         1         — | Sym.         Min.         Typ.         Max.         Units $V_{DD}$ 6         —         28         V           6         —         40         40         40           4         —         32         V $I_{DD}$ —         —         — $I_{DD}$ —         —         — $$ 5         15         — $$ 120         —         — $$ 120         —         — $$ 120         —         — $$ 120         —         — $$ 120         —         — $$ 120         —         — $$ 120         —         — $$ 1020         —         — $$ 1090         —         —           DIGITAL <sub>I/O</sub> 0         —         5.5         V |  |  |

# AC/DC CHARACTERISTICS

| Electrical Specifications: Unle           | ess otherwise note                                            | d, T <sub>J</sub> = -4 | 10°C to + | 150°C, tyj        | pical value | es are for +25°C, V <sub>DD</sub> = 13V.                                       |

|-------------------------------------------|---------------------------------------------------------------|------------------------|-----------|-------------------|-------------|--------------------------------------------------------------------------------|

| Parameters                                | Sym.                                                          | Min.                   | Тур.      | Max.              | Units       | Conditions                                                                     |

| Digital Input Rising Threshold            | V <sub>DIG_HI_TH</sub>                                        | 1.26                   |           | —                 | V           |                                                                                |

| Digital Input Falling Threshold           | V <sub>DIG_LO_TH</sub>                                        | _                      |           | 0.54              | V           |                                                                                |

| Digital Input Hysteresis                  | V <sub>DIG_HYS</sub>                                          | _                      | 500       | _                 | mV          |                                                                                |

| Digital Input Current                     | I <sub>DIG</sub>                                              | _                      | 30        | 100               | μA          | V <sub>DIG</sub> = 3V                                                          |

|                                           |                                                               | _                      | 0.2       | _                 |             | V <sub>DIG</sub> = 0V                                                          |

| Analog Low-Voltage Input                  | ANALOG <sub>VIN</sub>                                         | 0                      |           | 5.5               | V           | Excludes high-voltage pins                                                     |

| Analog Low-Voltage Output                 | ANALOG <sub>VOUT</sub>                                        | 0                      |           | V <sub>OUT5</sub> | V           | Excludes high-voltage pins                                                     |

| Bias Generator                            |                                                               |                        |           |                   |             |                                                                                |

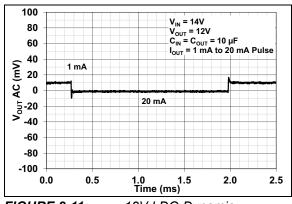

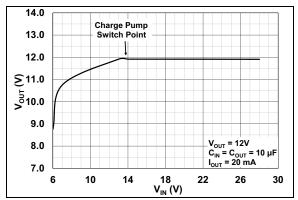

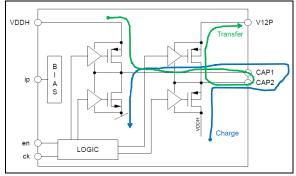

| +12V Regulated Charge Pum                 | p                                                             |                        |           |                   |             |                                                                                |

| Charge Pump Current                       | I <sub>CP</sub>                                               | 20                     |           | _                 | mA          | V <sub>DD</sub> = 9V                                                           |

| Charge Pump Start                         | CP <sub>START</sub>                                           | 11                     | 11.5      |                   | V           | V <sub>DD</sub> falling                                                        |

| Charge Pump Stop                          | CP <sub>STOP</sub>                                            |                        | 12        | 12.5              | V           | V <sub>DD</sub> rising                                                         |

| Charge Pump Frequency                     | CP <sub>FSW</sub>                                             | —                      | 76.8      | —                 | kHz         | V <sub>DD</sub> = 9V                                                           |

| (50% charging/<br>50% discharging)        |                                                               |                        | 0         | —                 |             | V <sub>DD</sub> = 13V (stopped)                                                |

| Charge Pump Switch<br>Resistance          | CP <sub>RDSON</sub>                                           | —                      | 14        | —                 | Ω           | RDS <sub>ON</sub> sum of high-side and<br>low-side                             |

| Output Voltage                            | V <sub>OUT12</sub>                                            | _                      | 12        | —                 | V           | V <sub>DD</sub> ≥ 7.5V, C <sub>PUMP</sub> = 100 nF<br>I <sub>OUT</sub> = 20 mA |

|                                           |                                                               | _                      | 9         | —                 |             | V <sub>DD</sub> = 5.1V, C <sub>PUMP</sub> = 260 nF<br>I <sub>OUT</sub> = 15 mA |

| Output Voltage Tolerance                  | TOLV <sub>OUT12</sub>                                         |                        |           | 4                 | %           | I <sub>OUT</sub> = 1 mA                                                        |

| Output Current                            | I <sub>OUT</sub>                                              | 30                     |           | —                 | mA          | Average current                                                                |

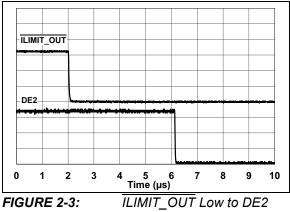

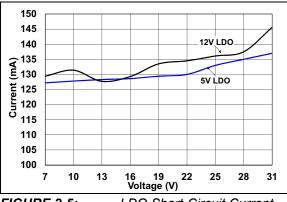

| Output Current Limit                      | I <sub>LIMIT</sub>                                            | 40                     | 50        | _                 | mA          | Average current                                                                |

| Output Voltage Temperature<br>Coefficient | TCV <sub>OUT12</sub>                                          |                        | 50        | —                 | ppm/°C      | Note 1                                                                         |

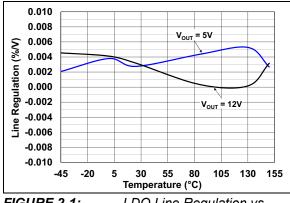

| Line Regulation                           | ΔV <sub>OUT</sub> /<br>(V <sub>OUT</sub> x ΔV <sub>DD</sub> ) |                        | 0.1       | 0.5               | %/V         | 13V < V <sub>DD</sub> < 19V,<br>I <sub>OUT</sub> = 20 mA                       |

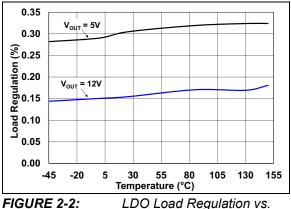

| Load Regulation                           | ΔV <sub>OUT</sub> /V <sub>OUT</sub>                           |                        | 0.2       | 0.5               | %           | I <sub>OUT</sub> = 0.1 mA to 15 mA                                             |

| Power Supply Rejection Ratio              | PSRR                                                          |                        | 60        | —                 | dB          | f = 1 kHz,<br>I <sub>OUT</sub> = 10 mA <b>(Note 1)</b>                         |

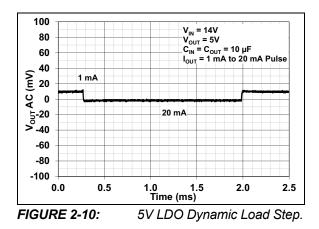

| +5V Linear Regulator                      |                                                               |                        |           | •                 | •           |                                                                                |

| Output Voltage                            | V <sub>OUT5</sub>                                             |                        | 5         | _                 | V           | V <sub>DD</sub> = V <sub>OUT5</sub> + 1V,<br>I <sub>OUT</sub> = 1 mA           |

| Output Voltage Tolerance                  | TOLV <sub>OUT5</sub>                                          | _                      |           | 4                 | %           |                                                                                |

| Output Current                            | I <sub>OUT</sub>                                              | 30                     |           | —                 | mA          | Average current                                                                |

| Output Current Limit                      | I <sub>LIMIT</sub>                                            | 40                     | 50        | —                 | mA          | Average current                                                                |

| Output Voltage Temperature<br>Coefficient | TCV <sub>OUT5</sub>                                           | —                      | 50        | —                 | ppm/°C      | Note 1                                                                         |

| Line Regulation                           | ΔV <sub>OUT</sub> /<br>(V <sub>OUT</sub> x ΔV <sub>DD</sub> ) |                        | 0.1       | 0.5               | %/V         | 6V < V <sub>DD</sub> < 28V,<br>I <sub>OUT</sub> = 20 mA                        |

| Load Regulation                           |                                                               |                        | 0.2       | 0.5               | %           | $I_{OUT} = 0.1 \text{ mA to } 15 \text{ mA}$                                   |

| Electrical Specifications: Unl                  | ess otherwise note                       | d, T <sub>J</sub> = -4 | 10°C to + | 150°C, ty | oical valu | es are for +25°C, V <sub>DD</sub> = 13V.                                                             |

|-------------------------------------------------|------------------------------------------|------------------------|-----------|-----------|------------|------------------------------------------------------------------------------------------------------|

| Parameters                                      | Sym.                                     | Min.                   | Тур.      | Max.      | Units      | Conditions                                                                                           |

| Dropout Voltage                                 | V <sub>DD</sub> – V <sub>OUT5</sub>      |                        | 180       | 350       | mV         | I <sub>OUT</sub> = 20 mA,<br>measurement taken when<br>output voltage drops 2% from<br>no load value |

| Power Supply Rejection Ratio                    | PSRR                                     | _                      | 60        | _         | dB         | f = 1 kHz,<br>I <sub>OUT</sub> = 10 mA <b>(Note 1)</b>                                               |

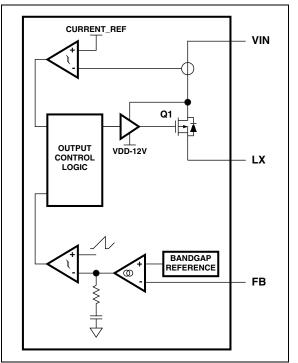

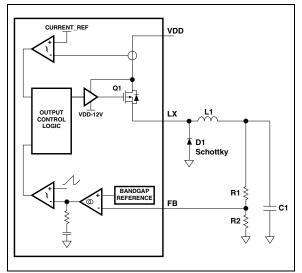

| Buck Regulator                                  |                                          |                        |           |           |            |                                                                                                      |

| Feedback Voltage                                | V <sub>FB</sub>                          | 1.19                   | 1.25      | 1.31      | V          |                                                                                                      |

| Feedback Voltage Tolerance                      | TOLV <sub>FB</sub>                       | _                      | _         | 5         | %          | I <sub>FB</sub> = 1 μA                                                                               |

| Feedback Voltage Line<br>Regulation             | $ (\Delta V_{FB}/V_{FB})/\Delta V_{DD} $ |                        | 0.1       | 0.5       | %/V        | $V_{DD}$ = 6V to 28V                                                                                 |

| Feedback Voltage Load<br>Regulation             | ∆V <sub>FB</sub> /V <sub>FB</sub>        |                        | 0.1       | 0.5       | %          | I <sub>OUT</sub> = 5 mA to 150 mA                                                                    |

| Feedback Input Bias Current                     | I <sub>FB</sub>                          | -100                   | —         | +100      | nA         | Sink/Source (Note 1)                                                                                 |

| Feedback Voltage<br>to Shut Down Buck Regulator | V <sub>BUCK_DIS</sub>                    | 2.5                    | —         | 5.5       | V          | V <sub>DD</sub> > 6V                                                                                 |

| Switching Frequency                             | f <sub>SW</sub>                          | _                      | 461       | _         | kHz        |                                                                                                      |

| Duty Cycle Range                                | DC <sub>MAX</sub>                        | 3                      | _         | 96        | %          | Note 1                                                                                               |

| PMOS Switch-On Resistance                       | R <sub>DSON</sub>                        | _                      | 0.6       | _         | Ω          | T <sub>J</sub> = 25°C                                                                                |

| PMOS Switch Current Limit                       | I <sub>P(MAX)</sub>                      | _                      | 2.5       |           | А          |                                                                                                      |

| Ground Current – PWM Mode                       | I <sub>GND</sub>                         | _                      | 1.5       | 2.5       | mA         | Switching (Note 1)                                                                                   |

| Quiescent Current –<br>PFM Mode                 | Ι <sub>Q</sub>                           |                        | 150       | 200       | μA         | I <sub>OUT</sub> = 0 mA (Note 1)                                                                     |

| Output Voltage Adjust Range                     | V <sub>OUT</sub>                         | 2                      | —         | 5         | V          | Note 1                                                                                               |

| Output Current                                  | I <sub>OUT</sub>                         | 150                    | —         | _         | mA         | 5V, V <sub>DD</sub> – V <sub>OUT</sub> > 0.5V                                                        |

|                                                 |                                          | 250                    | —         | _         |            | 3V, V <sub>DD</sub> – V <sub>OUT</sub> > 0.5V                                                        |

| Output Power                                    | P <sub>OUT</sub>                         |                        | 750       |           | mW         | P = I <sub>OUT</sub> x V <sub>OUT</sub><br>2.5A peak current <b>(Note 1)</b>                         |

| Voltage Supervisor                              |                                          |                        |           |           |            |                                                                                                      |

| Buck Input Undervoltage<br>Lockout – Start-up   | UVLO <sub>BK_STRT</sub>                  | _                      | 4.5       | 4.7       | V          | V <sub>DD</sub> rising                                                                               |

| Buck Input Undervoltage<br>Lockout – Shutdown   | UVLO <sub>BK_STOP</sub>                  | 3.8                    | 4         | _         | V          | V <sub>DD</sub> falling                                                                              |

| Buck Input Undervoltage<br>Lockout Hysteresis   | UVLO <sub>BK_HYS</sub>                   | _                      | 0.5       |           | V          | Note 1                                                                                               |

| 5V LDO Undervoltage Fault<br>Inactive           | UVLO <sub>5VLDO_IN-</sub><br>ACT         |                        | 4.5       |           | V          | V <sub>OUT5</sub> rising <b>(Note 1)</b>                                                             |

| 5V LDO Undervoltage Fault<br>Active             | UVLO <sub>5VLDO_ACT</sub>                | _                      | 4         |           | V          | V <sub>OUT5</sub> falling (Note 1)                                                                   |

| 5V LDO Undervoltage Fault<br>Hysteresis         | UVLO <sub>5VLDO_HYS</sub>                |                        | 0.5       |           | V          | Note 1                                                                                               |

| Input Undervoltage Lockout –<br>Start-up        | UVLO <sub>STRT</sub>                     |                        | 6         | 6.25      | V          | V <sub>DD</sub> rising                                                                               |

| Input Undervoltage Lockout –<br>Shutdown        | UVLO <sub>STOP</sub>                     | 5.1                    | 5.5       |           | V          | V <sub>DD</sub> falling                                                                              |

| <b>Electrical Specifications:</b> Unless otherwise noted, $T_J = -40^{\circ}C$ to +150°C, typical values are for +25°C, $V_{DD} = 13V$ . |                        |                             |      |                              |                  |                                                                      |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|------|------------------------------|------------------|----------------------------------------------------------------------|--|

| Parameters                                                                                                                               | Sym.                   | Min.                        | Тур. | Max.                         | Units            | Conditions                                                           |  |

| Input Undervoltage Lockout<br>Hysteresis                                                                                                 | UVLO <sub>HYS</sub>    | 0.2                         | 0.45 | 0.70                         | V                | Note 1                                                               |  |

| Input Overvoltage Lockout –<br>Driver Disabled                                                                                           | DOVLO <sub>STOP</sub>  | —                           | 28   | 28.5                         | V                | V <sub>DD</sub> rising                                               |  |

| Input Overvoltage Lockout –<br>Driver Enabled                                                                                            | DOVLO <sub>STRT</sub>  | 26.75                       | 27.5 | _                            | V                | V <sub>DD</sub> falling                                              |  |

| Input Overvoltage Lockout<br>Hysteresis                                                                                                  | DOVLO <sub>HYS</sub>   | 0.25                        | 0.5  | 0.75                         | V                | Note 1                                                               |  |

| Input Overvoltage Lockout<br>– All Functions Disabled                                                                                    | AOVLO <sub>STOP</sub>  | —                           | 32   | 33                           | V                | V <sub>DD</sub> rising                                               |  |

| Input Overvoltage Lockout<br>– All Functions Enabled                                                                                     | AOVLO <sub>STRT</sub>  | 29                          | 30   | —                            | V                | V <sub>DD</sub> falling                                              |  |

| Input Overvoltage Lockout<br>Hysteresis                                                                                                  | AOVLO <sub>HYS</sub>   | 1                           | 2    | 3                            | V                | Note 1                                                               |  |

| Temperature Supervisor                                                                                                                   |                        |                             |      | 1                            |                  |                                                                      |  |

| Thermal Warning Temperature                                                                                                              | T <sub>WARN</sub>      | _                           | 115  | _                            | %T <sub>SD</sub> | Rising temperature (Note 1)                                          |  |

| Thermal Warning Hysteresis                                                                                                               | $\Delta T_{WARN}$      | _                           | 15   | _                            | °C               | Falling temperature (Note 1)                                         |  |

| Thermal Shutdown<br>Temperature                                                                                                          | T <sub>SD</sub>        | 160                         | 170  | _                            | °C               | Rising temperature (Note 1)                                          |  |

| Thermal Shutdown Hysteresis                                                                                                              | $\Delta T_{SD}$        |                             | 25   |                              | °C               | Falling temperature (Note 1)                                         |  |

| Motor Control Unit                                                                                                                       | 00                     |                             | L    |                              |                  |                                                                      |  |

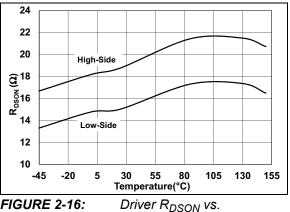

| Output Drivers                                                                                                                           |                        |                             |      |                              |                  |                                                                      |  |

| PWMH/L Input Pull-Down                                                                                                                   | R <sub>PULLDN</sub>    | _                           | 47   | _                            | kΩ               |                                                                      |  |

| Output Driver Source Current                                                                                                             | ISOURCE                | 0.3                         |      | — A                          |                  | V <sub>DD</sub> = 12V, HS[A:C], LS[A:C]                              |  |

| Output Driver Sink Current                                                                                                               | I <sub>SINK</sub>      | 0.3                         | _    | _                            | А                | V <sub>DD</sub> = 12V, HS[A:C], LS[A:C]                              |  |

| Output Driver Source<br>Resistance                                                                                                       | R <sub>DSON</sub>      | —                           | 17   | —                            | Ω                | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 12V,<br>HS[A:C], LS[A:C] |  |

| Output Driver Sink Resistance                                                                                                            | R <sub>DSON</sub>      |                             | 17   | _                            | Ω                | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 12V,<br>HS[A:C], LS[A:C] |  |

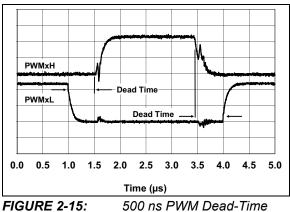

| Output Driver Blanking                                                                                                                   | t <sub>BLANK</sub>     | 500                         | _    | 4000                         | ns               | Configurable (Note 1)                                                |  |

| Output Driver UVLO Threshold                                                                                                             | D <sub>UVLO</sub>      | 6.5                         | 7.2  | 8                            | V                | Configuration Register 0<br>bit 3 = 0                                |  |

| Output Driver UVLO Minimum<br>Duration                                                                                                   | t <sub>DUVLO</sub>     | t <sub>BLANK</sub><br>+ 700 |      | t <sub>BLANK</sub> +<br>1400 | ns               | Fault latched after t <sub>DUVLO</sub> (Note 1)                      |  |

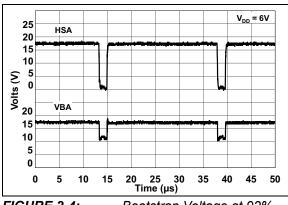

| Output Driver HS Drive                                                                                                                   | V <sub>HS</sub>        | 8                           | 12   | 13.5                         | V                | With respect to the phase pin                                        |  |

| Voltage                                                                                                                                  |                        | -5.5                        | _    | _                            |                  | With respect to ground                                               |  |

| Output Driver LS Drive Voltage                                                                                                           | V <sub>LS</sub>        | 8                           | 12   | 13.5                         | V                | With respect to ground                                               |  |

| Output Driver Bootstrap<br>Voltage                                                                                                       | V <sub>BOOTSTRAP</sub> | —                           | _    | -                            | V                | With respect to ground (Note 1)                                      |  |

|                                                                                                                                          |                        | —                           | _    | 40                           |                  | Continuous                                                           |  |

| Output Driver Phase Pin<br>Voltage                                                                                                       | V <sub>PHASE</sub>     | —                           | _    | -                            | V                | With respect to ground (Note 1)                                      |  |

|                                                                                                                                          |                        | -5.5                        | _    | 40                           |                  | Continuous                                                           |  |

|                                                                                                                                          |                        |                             |      |                              |                  |                                                                      |  |

| Electrical Specifications: Unle                                                                    | ss otherwise not                  | ed, I <sub>J</sub> = -4 | 40°C to + | 150°C, ty | pical valu | es are for +25°C, $V_{DD}$ = 13V.                                            |

|----------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------|-----------|-----------|------------|------------------------------------------------------------------------------|

| Parameters                                                                                         | Sym.                              | Min.                    | Тур.      | Max.      | Units      | Conditions                                                                   |

| Output Driver Short-Circuit                                                                        | D <sub>SC_THR</sub>               |                         | —         |           | V          | Set in CFG0 register (Note 1)                                                |

| Protection Threshold                                                                               |                                   |                         | 0.250     | _         |            | 00 (default)                                                                 |

| High Side (V <sub>DD</sub> – V <sub>PHx</sub> )<br>Low Side (V <sub>PHx</sub> – P <sub>GND</sub> ) |                                   |                         | 0.500     |           |            | 01                                                                           |

|                                                                                                    |                                   |                         | 0.750     |           |            | 10                                                                           |

|                                                                                                    |                                   |                         | 1.000     |           |            | 11                                                                           |

| Output Driver Short-Circuit<br>Detected Propagation Delay                                          | T <sub>SC_DLY</sub>               | _                       | —         |           | ns         | C <sub>LOAD</sub> = 1000 pF, V <sub>DD</sub> = 12V<br>(Note 1)               |

|                                                                                                    |                                   |                         | 430       | _         |            | Detection after blanking                                                     |

|                                                                                                    |                                   | _                       | 10        | —         |            | Detection during blanking,<br>value is delayed after<br>blanking             |

| Output Driver OVLO Turn-Off<br>Delay                                                               | T <sub>OVLO_DLY</sub>             | 3                       | 5         | _         | μs         | Detection synchronized with internal clock (Note 1)                          |

| Power-up or Sleep to Standby                                                                       | t <sub>POWER</sub>                | —                       | 5         |           | ms         | CE high-low-high<br>transition < 100 μs (Fault<br>clearing) <b>(Note 1)</b>  |

| Standby to Motor Operational                                                                       | t <sub>MOTOR</sub>                |                         | 35        | 50        | μs         | CE high-low-high<br>transition < 0.9 ms (Fault<br>clearing)                  |

|                                                                                                    |                                   | —                       | —         | 10        | ms         | Standby state to Operational state (Note 1)                                  |

| Fault to Driver Output Turn-Off                                                                    | T <sub>FAULT_OFF</sub>            | _                       | _         | —         | μs         | $C_{LOAD}$ = 1000 pF, $V_{DD}$ = 12V,<br>time after Fault occurs<br>(Note 1) |

|                                                                                                    |                                   | —                       | 1         |           |            | UVLO, OCP Faults                                                             |

|                                                                                                    |                                   | _                       | 10        |           |            | All other Faults                                                             |

| CE Low to Driver Output<br>Turn-Off                                                                | T <sub>DEL_OFF</sub>              | —                       | 100       | 250       | ns         | $C_{LOAD}$ = 1000 pF, $V_{DD}$ = 12V,<br>time after CE = low (Note 1)        |

| CE Low to Standby State                                                                            | t <sub>STANDBY</sub>              | —                       | 1         |           | ms         | Time after CE = low,<br>SLEEP bit = 0 (Note 1)                               |

| CE Low to Sleep State                                                                              | t <sub>SLEEP</sub>                | -                       | 1         | _         | ms         | Time after CE = low,<br>SLEEP bit = 1 (Note 1)                               |

| CE Fault Clearing Pulse                                                                            | <sup>t</sup> FAULT_CLR            | 4                       |           | 900       | μs         | CE high-low-high transition time (Note 1)                                    |

| Current Sense Amplifier                                                                            |                                   |                         |           |           |            |                                                                              |

| Input Offset Voltage                                                                               | V <sub>OS</sub>                   | -5                      |           | +5        | mV         | $V_{CM} = 0V,$<br>$T_A = -40^{\circ}C$ to +150°C                             |

| Input Offset Temperature Drift                                                                     | $\Delta V_{OS} / \Delta T_A$      |                         | ±2        |           | µV/°C      | V <sub>CM</sub> = 0V (Note 1)                                                |

| Input Bias Current                                                                                 | Ι <sub>Β</sub>                    | -1                      |           | +1        | μA         |                                                                              |

| Common-Mode Input Range                                                                            | V <sub>CMR</sub>                  | -0.3                    |           | 3.5       | V          |                                                                              |

| Common-Mode Rejection Ratio                                                                        | CMRR                              | _                       | 80        |           | dB         | Frequency = 1 kHz,<br>I <sub>OUT</sub> = 10 µA <b>(Note 1)</b>               |

| Maximum Output Voltage<br>Swing                                                                    | V <sub>OL</sub> , V <sub>OH</sub> | 0.05                    |           | 4.5       | V          | I <sub>OUT</sub> = 200 μA                                                    |

| Slew Rate                                                                                          | SR                                | _                       | ±7        |           | V/µs       | Symmetrical (Note 1)                                                         |

| Gain Bandwidth Product                                                                             | GBWP                              | _                       | 10        | _         | MHz        | Note 1                                                                       |

| Electrical Specifications: Unle                 | ess otherwise note                | ed, T <sub>J</sub> = -4 | 0°C to + | 150°C, ty | pical valu      | es are for +25°C, V <sub>DD</sub> = 13V.                                                       |

|-------------------------------------------------|-----------------------------------|-------------------------|----------|-----------|-----------------|------------------------------------------------------------------------------------------------|

| Parameters                                      | Sym.                              | Min.                    | Тур.     | Max.      | Units           | Conditions                                                                                     |

| Current Comparator Hysteresis                   | CC <sub>HYS</sub>                 | —                       | 10       | _         | mV              | Note 1                                                                                         |

| Current Comparator<br>Common-Mode Input Range   | V <sub>CC_CMR</sub>               | 1                       | —        | 4.5       | V               | Note 1                                                                                         |

| Current Limit DAC                               |                                   |                         | 1        |           | J               |                                                                                                |

| Resolution                                      |                                   | _                       | 8        | _         | bits            |                                                                                                |

| Output Voltage Range                            | V <sub>OL</sub> , V <sub>OH</sub> | 0.991                   | —        | 4.503     | V               | I <sub>OUT</sub> = 1 mA                                                                        |

| Output Voltage                                  | V <sub>DAC</sub>                  | _                       | —        |           | V               | CFG1 code x 13.77 mV/bit +<br>0.991V (Note 1)                                                  |

|                                                 |                                   | _                       | 0.991    | -         |                 | Code 00H                                                                                       |

|                                                 |                                   | _                       | 1.872    |           |                 | Code 40H                                                                                       |

|                                                 |                                   | _                       | 4.503    |           |                 | Code FFH                                                                                       |

| Input to Output Delay                           | T <sub>DELAY</sub>                | —                       | 50       | _         | μs              | (Note 1)                                                                                       |

| Integral Nonlinearity                           | INL                               | -0.5                    | —        | +0.5      | %FSR            | %Full Scale Range (Note 1)                                                                     |

| Differential Nonlinearity                       | DNL                               | -50                     | —        | +50       | %LSB            | %LSB (Note 1)                                                                                  |