# AM25S05

Rochester Electronics<sup>®</sup>

# Four-Bit by Two-Bit Two's Complement Multiplier

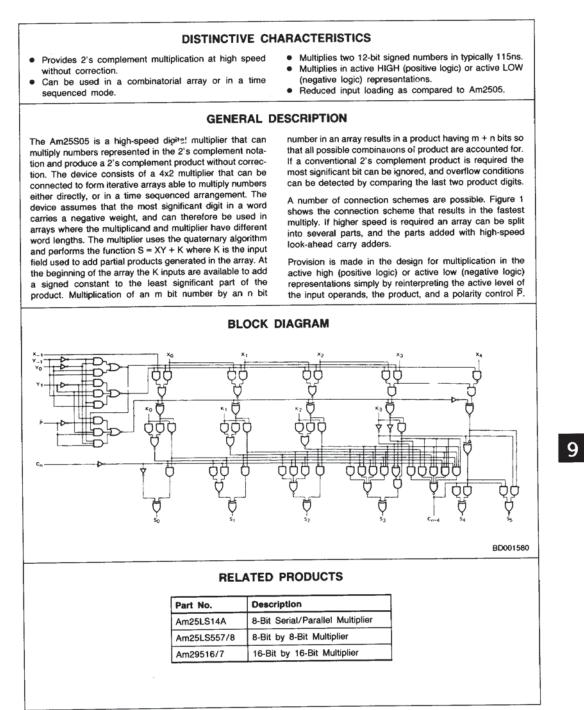

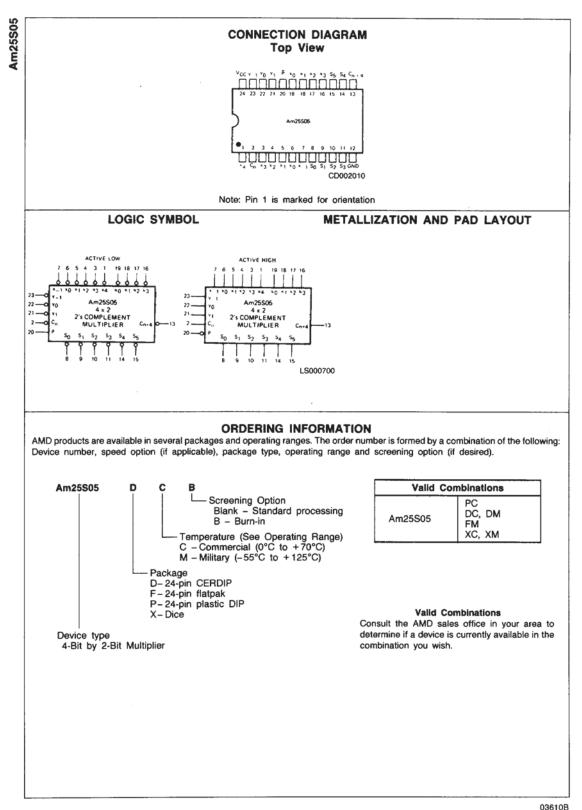

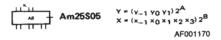

The AM25S05 is a high-speed digital multiplier that can multiply numbers represented in the 2's complement notation and produce a 2's complement product without correction. The device consists of a 4x2 multiplier that can be connected to form iterative arrays able to multiply numbers either directly, or in a time sequenced arrangement. The device assumes that the most significant digit in a word carries a negative weight, and can therefore be used in arrays where the multiplicand and multiplier have different word lengths. The multiplier uses the quaternary algorithm and performs the function S = XY + K where K is the input field used to add partial products generated in the array. At the beginning of the array the K inputs are available to add a signed constant to the least significant part of the product. Multiplication of an m bit number by an n bit number in an array results in a product having m + n bits so that all possible combinations of product are accounted for. If a conventional 2's complement product is required the most significant bit can be detected by comparing the last two product digits.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Am25S05

Four-Bit by Two-Bit Two's Complement Multiplier

9-1

03610B

Refer to Page 13-1 for Essential Information on Military Devices

9-2

U3610B Refer to Page 13-1 for Essential Information on Military Devices

#### SWITCHING TIME TEST TABLE

| Input          | Outputs                          | Inputs at 0V (remaining inputs at 4.5V)                                                    |

|----------------|----------------------------------|--------------------------------------------------------------------------------------------|

| Cn             | Cn + 4, S0123, S45               | P, Y-1, Y1, All X                                                                          |

| ko             | Cn + 4, S0123, S45               | P, Y-1, Y1, All X                                                                          |

| k1             | Cn + 4, S123, S45                | P, Y-1, Y1, All X                                                                          |

| k <sub>2</sub> | Cn + 4, S23, S45                 | P. Y.1, Y1, All X                                                                          |

| ka l           | S3                               | P. Y.1, Y1, All X                                                                          |

| ka             | S45                              | P, Y.1, Y1, All X, Cn                                                                      |

| K-1            | Cn + 4, S0123, S45               | P. Y1. All k                                                                               |

|                | Cn + 4, S0123, S45               | P. Y.1. Y1. All k                                                                          |

| ×0             | $C_{n+4}$ , $S_{123}$ , $S_{45}$ | P. Y.1. Y1. All k                                                                          |

| ×1             | $C_{n+4}, S_{123}, S_{45}$       | P. Y.1. Y1. All k                                                                          |

| ×2             | S3                               | P. Y.1. Y1. All k                                                                          |

| x3             | S45                              | P. Y.1, Y1, All k, Cn                                                                      |

| ×3             |                                  | P. Y1. All k. Cn                                                                           |

| X4             | S45                              |                                                                                            |

| y-1            | Cn + 4, S0123, S45               | P, X1, X2, X3, X4, All k                                                                   |

| Уо             | Cn + 4, S0123, S45               | P, X1, X2, X3, X4, All k                                                                   |

| У0<br>У1       | Cn + 4, So123, S45               | X <sub>0</sub> , X <sub>1</sub> , X <sub>2</sub> , X <sub>3</sub> , X <sub>4</sub> , All k |

### DEFINITION OF TERMS

#### SUBSCRIPT TERMS:

H HIGH, applying to a HIGH logic level or when used with V<sub>CC</sub> to indicate high V<sub>CC</sub> value.

I Input.

L LOW, applying to LOW logic level or when used with V<sub>CC</sub> to indicate low V<sub>CC</sub> value. O Output.

#### FUNCTIONAL TERMS:

Cn The carry input to the high-speed adder.

$C_{n+4}$  The carry output from the high-speed adder. KI The constant field used for accumulating partial products. i = 0, 1, 2, 3. At the beginning of the array the K field can be used to add a 2's complement number to the least significant half of the double length product. P The polarity control input. This input must be at a lowlogic level for numbers in the active high logic representation, and held high for numbers in the active low logic representation.

Si The product outputs. i = 0, 1, 2, 3, 4, 5.

x The multiplicand inputs. i = -1, 0, 1, 2, 3, 4. At the first column of the array x-1 must be held at logic '0',

#### MSI INTERFACING RULES

|                                            | Equiv<br>Input U | alent<br>hit Load |

|--------------------------------------------|------------------|-------------------|

| Interfacing<br>Digital Family              | HIGH             | LOW               |

| Advanced Micro Devices 54/7400<br>Series   | 1.25             | 1.25              |

| Advanced Micro Devices 9300/2500<br>Series | 1.25             | 1.25              |

| FSC Series 9300                            | 1.25             | 1.25              |

| TI Series 54/7400                          | 1.25             | 1.25              |

| Signetics Series 8200                      | 2.5              | 2.5               |

| National Series DM 75/85                   | 1.25             | 1.25              |

| DTL Series 930                             | 15               | 1.25              |

and at the last column of the array x4 is connected to X3

$Y_i$  The multiplier inputs. i = -1, 0, 1.

At the first row of the array Y-1 must be held at logic '0'.

#### **OPERATIONAL TERMS:**

IL Forward input load current.

IOH Output HIGH current, forced out of output in VOH test.

IoL Output LOW current, forced into the output in VOL test.

Icc The current drawn by the device from V<sub>CC</sub> power supply with input and output terminals open. IH Reverse input load current. Negative Current Current flowing out of the device. Positive Current Current flowing into the device. VIH Minimum logic HIGH input voltage. VIL Maximum logic LOW input voltage. VIN Input voltage applied in IIL, IIH tests. VOH Minimum logic HIGH output voltage with output HIGH current IOH flowing out of output.

VoL Maximum logic LOW output voltage with output LOW current IOL flowing into output.

#### **OPERATION TABLE**

|    | ν.             | ν.                          | Operation<br>X Multiplicand                                              |

|----|----------------|-----------------------------|--------------------------------------------------------------------------|

| -1 | Yo             | Y <sub>1</sub>              | A multiplicatio                                                          |

| 0  | 0              | 0                           | K + 0                                                                    |

| 1  | 0              | 0                           | K + X                                                                    |

| 0  | 1              | 0                           | K + X '                                                                  |

| 1  | 1              | 0                           | K + 2X                                                                   |

| 0  | 0              | 1                           | K – 2X                                                                   |

| 1  | 0              | 1                           | K – X                                                                    |

| 0  | 1              | 1                           | K – X                                                                    |

| 1  | 1              | 1                           | K – 0                                                                    |

|    | '1' =<br>Activ | = Low, '0' =<br>re High Inp | uts and Outputs<br>= High, P = High<br>uts and Outputs<br>= Low, P = Low |

03610B

9

Refer to Page 13-1 for Essential Information on Military Devices

#### Am25S05 LOADING RULES IN UNIT LOADS

Am25S05

|                    |             |               | out<br>Load  | Fan            | -out          |

|--------------------|-------------|---------------|--------------|----------------|---------------|

| Input/Output       | Pin<br>Nos. | Input<br>HIGH | Input<br>LOW | Output<br>HIGH | Output<br>LOW |

| X4                 | 1           | 0.2           | 0.2          | -              | -             |

| Cn                 | 2           | 0.2           | 0.2          | -              | -             |

| x3                 | 3           | 0.2           | 0.2          | -              | -             |

| x <sub>2</sub>     | 4           | 0.4           | 0.4          | ~              | -             |

| ×1                 | 5           | 0.4           | 0.4          | -              | -             |

| x <sub>0</sub>     | 6           | 0.4           | 0.4          | -              | -             |

| X-1                | 7           | 0.2           | 0.2          | -              | -             |

| S <sub>0</sub>     | 8           | -             | -            | 20             | 10            |

| S <sub>1</sub>     | 9           | -             | -            | 20             | 10            |

| S <sub>2</sub>     | 10          | -             | -            | 20             | 10            |

| S <sub>3</sub>     | 11          | -             | -            | 20             | 10            |

| GND                | 12          | -             | -            | -              | -             |

| C <sub>n + 4</sub> | 13          | -             | -            | 20             | 10            |

| S <sub>4</sub>     | 14          | -             | -            | 20             | 10            |

| S <sub>5</sub>     | 15          | -             | -            | 20             | 10            |

| k3                 | 16          | 2             | 2            | -              | -             |

| k2                 | 17          | 2             | 2            | -              | -             |

| k <sub>1</sub>     | 18          | 2             | 2            | -              | -             |

| k <sub>0</sub>     | 19          | 2             | 2            | -              | -             |

| P                  | 20          | 1             | 1            | -              | -             |

| У1                 | 21          | 0.6           | 0.6          | -              | -             |

| Уо                 | 22          | 0.6           | 0.6          | -              | -             |

| У-1                | 23          | 0.6           | 0.6          | -              | -             |

| Vcc                | 24          | -             | -            | -              | -             |

A Schottky TTL Unit Load is defined as  $50\mu$ A at 2.7V at the HIGH Logic Level and -2.0mA at 0.5V at the LOW Logic Level.

#### USER NOTES

- 1. Arithmetic in the multiplier is performed in the 2's complement notation, which requires a carry in at the first stage. This is accomplished by connecting the  $Y_i$  multiplier bit to the appropriate carry input terminal i = 1, 3, 5...

- The multiplier can perform multiplication in either the active high (positive logic) or active low (negative logic) representations by reinterpreting the active logic level and by grounding or leaving the polarity control pin P open circuit respectively.

- 3. Multiplication can be performed in number representations other than 2's complement by either correcting the 2's complement product or adding in a correction at the beginning of the multiplication at the K inputs. 2's complement numbers are represented as:  $X_2 = x - x_s 2^{n-1}$ .

| Number<br>Representation | Correction                                                                                                                                                                                                                                                                   |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2's complement           | None                                                                                                                                                                                                                                                                         |

| 1's complement           | Add $x_{s}Y_{2} + y_{s}X_{2} + x_{s}Y_{s}$ at K inputs                                                                                                                                                                                                                       |

| Unsigned                 | Extended multiplier and multiplicand one bit                                                                                                                                                                                                                                 |

| (Magnitude)              | at the least significant end. Form                                                                                                                                                                                                                                           |

| Sign magnitude           | $\begin{array}{l} x_{0}y_{0}+y_{0}x+x_{0}y \mbox{ with conditional adder and}\\ add to array shifted two places up at k in-puts. Force k_{s}, y_{s}, x_{s}=0.\\ x_{s}=0, \ y_{s}=0 \mbox{ None}\\ x_{s}=1, \ y_{s}=0 \mbox{ Form}\left[(XY)_{2}+2^{n-1}y\right] \end{array}$ |

|                          | $x_s = 0$ , $y_s = 1$ Form $[(XY)_2 + 2^{n-1}x]$<br>$x_s = 1$ , $y_s = 1$ Add $2^{n-1}(x + y) - 2^{2n-2}$                                                                                                                                                                    |

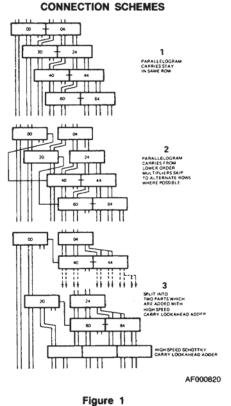

- 4. For the highest speed array with the multipliers arranged in a parallelogram structure carries between certain multipliers are exchanged with the y carry-ins needed for 2's complement subtract. The delays in the array are then equalized as best possible as shown in Figure 1.

- For higher speed multiplication the array can be split into several parts that can be added together with high-speed adders.

- 6. Rounding off to a single length product can be achieved by adding a '1' to the array at the most significant positive k input of the array, ignoring the most significant product digit, and using the remainder of the most significant part of the product.

- 7. Truncation of a product without round off enables some of the multipliers in the array to be removed.

03610B Refer to Page 13-1 for Essential Information on Military Devices

| Array        | Total                       | Pack    | age Count    |

|--------------|-----------------------------|---------|--------------|

| Size<br>Bits | Multiplication<br>Time (ns) | Am25S05 | Am54S/74S181 |

| 4 x 4        | 35                          | 2       |              |

| 8x8          | 75                          | 8       |              |

| 12 x 12      | 115                         | 18      |              |

| 12 x 12      | 82                          | 18      | 5            |

| 16 x 16      | 155                         | 32      |              |

| 16 x 16      | 111                         | 32      | 7            |

| 16 x 16      | 98                          | 32      | 16           |

| 20 x 20      | 195                         | 50      |              |

| 20 x 20      | 130                         | 50      | 9            |

| 24 x 24      | 235                         | 72      |              |

| 24 x 24      | 149                         | 72      | 11           |

| 24 x 24      | 125                         | 72      | 24           |

| 28 x 28      | 275                         | 98      |              |

| 28 x 28      | 168                         | 98      | 13           |

| 32 x 32      | 315                         | 128     |              |

| 32 x 32      | 187                         | 128     | 15           |

| 32 x 32      | 152                         | 128     | 32           |

9-5

Figure 2

•\_

Refer to Page 13-1 for Essential Information on Military Devices

9

### ABSOLUTE MAXIMUM RATINGS

### Storage Temperature ..... -65°C to +150°C Temperature(Ambient) Under Bias ......-55°C to +125°C Supply Voltage to Ground Potential

(Pin 24 to Pin 12) Continuous .....-0.5V to +7.0V DC Voltage Applied to Outputs For High Output State ......-0.5V to +V<sub>CC</sub> max

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### OPERATING RANGES

#### Commercial (C) Devices

Supply Voltage ...... + 4.75V to + 5.25V

Military (M) Devices Temperature .....-55°C to +125°C Supply Voltage ...... + 4.5V to + 5.5V

Operating ranges define those limits over which the functionality of the device is guaranteed.

#### DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters    | Description                     | Test Condition                                                                                         | Min | Typ<br>(Note 1) | Max | Units |       |

|---------------|---------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----------------|-----|-------|-------|

| <b>1</b> 1000 |                                 | V <sub>CC</sub> = MIN., I <sub>OH</sub> = -1.0mA                                                       | XM  | 2.5             | 3.3 |       |       |

| VOH           | Output HIGH Voltage             | VIN = VIH or VIL                                                                                       | XC  | 2.7             | 3.3 |       | Volts |

| VOL           | Output LOW Voltage              | V <sub>CC</sub> = MIN., I <sub>OL</sub> = 20mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |     |                 | 0.3 | 0.5   | Volts |

| VIH           | Input HIGH Level                | Guaranteed input logical HIGH voltage for all inputs                                                   |     | 2.0             |     |       | Volts |

| VIL           | Input LOW Level                 | Guaranteed input logical LOW voltage for all inputs                                                    |     |                 |     | 0.8   | Volts |

| IIL (Note 2)  | Unit Load<br>Input LOW Current  | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.5V                                                         |     |                 |     | -2.0  | mA    |

| IIH (Note 2)  | Unit Load<br>Input HIGH Current | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.7V                                                         |     |                 |     | 50    | μA    |

| 1)A (11010 L) | Input HIGH Current              | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 5.5V                                                         |     |                 |     | 1.0   | mA    |

| Isc           | Output Short Circuit Current    | V <sub>CC</sub> = MAX., V <sub>OUT</sub> = 0.0V                                                        |     | - 40            |     | -100  | mA    |

| lcc           | Power Supply Current            | V <sub>CC</sub> = MAX., Y <sub>1</sub> = .0V                                                           |     | -               | 120 | 175   | mA    |

Note 1. Typical Limits are at  $V_{CC}$  = 5.0V, 25°C ambient and maximum loading. Note 2. Actual input currents are obtained by multiplying unit load current by the input load factor (See loading rules).

9-6

| VITCHING<br>rameters | From (Input) | To (Output)          | Test Conditions | Min      | Тур          | Max      | Units |

|----------------------|--------------|----------------------|-----------------|----------|--------------|----------|-------|

| tplH<br>tpHL         | Cn           | Cn + 4               |                 | 4        | 8<br>9       | 12<br>14 | ns    |

| tPLH<br>tPHL         | Cn           | S <sub>0,1,2,3</sub> |                 | 6<br>5   | 12<br>10     | 18<br>15 | ns    |

| <sup>t</sup> PLH     | Cn           | S4,5                 |                 | 7<br>6   | 15<br>13     | 22<br>20 | ns    |

| tPHL<br>tPLH<br>tPHL | Any k        | C <sub>n + 4</sub>   |                 | 3<br>5   | 6.5<br>10    | 12<br>15 | ns    |

| tPLH<br>tPHL         | Any k        | S <sub>0,1,2,3</sub> |                 | 6<br>4   | 13.5<br>9.5  | 20<br>14 | ns    |

| tPLH<br>tPHL         | Any k        | S4,5                 | Constant Table  | 3        | 15.5<br>12.5 | 23<br>19 | ns    |

| tPLH<br>tPHL         | Any x        | Cn + 4               | See Test Table  | 8<br>9   | 17<br>18     | 26<br>27 | ns    |

| <sup>t</sup> PLH     | Any x        | S <sub>0,1,2,3</sub> |                 | 10<br>10 | 21<br>21     | 32<br>32 | ns    |

| tPHL<br>tPLH<br>tPHL | Any x        | S4,5                 | -               | 6<br>5   | 23.5<br>21.5 | 35<br>32 | ns    |

| tPLH                 | Any y        | Cn + 4               |                 | 11<br>10 | 23<br>20     | 34<br>30 | ns    |

| tphl<br>tplh<br>tphl | Any y        | S <sub>0,1,2,3</sub> |                 | 11       | 23<br>23     | 34<br>34 | ns    |

| трін<br>трін         | Any y        | S4,5                 |                 | 12<br>12 | 25<br>25     | 37<br>37 | ns    |

|                      |              |                      |                 |          |              |          |       |

|                      |              |                      |                 |          |              |          |       |