# IXF1002

ochester

### Dual Port Gigabit Ethernet Controller

The Intel IXF1002 Dual Port Gigabit Ethernet Media Access Controller (MAC), provides two independent 1000 Mb/s intelligent, high-performance MAC ports. It includes Gigabit Physical Coding Sublayer (GPCS) interface network management support and is optimized for switch applications.

The IXF1002 handles Simple Network Management Protocol (SNMP) and Remove Monitoring (RMON) management counter sets, accessible through a generic CPU 8/16-bit interface, which is also used for mode programming. Each MAC port includes a 4 Kbyte FIFO for packet receive, and a 2 Kbyte FIFO for packet transmit. All the packets are transferred onto a high-performance, common IX Bus interface.

| Rochester Electronics<br>Manufactured Components<br>Rochester branded components are<br>manufactured using either die/wafers<br>purchased from the original suppliers<br>or Rochester wafers recreated from the<br>original IP. All recreations are done with<br>the approval of the OCM. | <ul> <li>Quality Overview</li> <li>ISO-9001</li> <li>AS9120 certification</li> <li>Qualified Manufacturers List (QML) MIL-PRF-38535 <ul> <li>Class Q Military</li> <li>Class V Space Level</li> </ul> </li> <li>Qualified Suppliers List of Distributors (QSLD) <ul> <li>Rochester is a critical supplier to DLA and meets all industry and DLA standards.</li> </ul> </li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parts are tested using original factory<br>test programs or Rochester developed<br>test solutions to guarantee product<br>meets or exceeds the OCM data sheet.                                                                                                                            | Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.                                                                                                                                                                                                |

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Intel<sup>®</sup> IXF1002 Dual Port Gigabit Ethernet Controller

#### Datasheet

### **Product Features**

The Intel<sup>®</sup> IXF1002 Dual Port Gigabit Ethernet Media Access Controller (MAC), provides two independent 1000 Mb/s intelligent, high-performance Media Access Control (MAC) ports. It includes Gigabit Physical Coding Sublayer (GPCS) interface network management support and is optimized for switch applications.

- Integration

- Offers two independent Ethernet 1000 Mb/s MAC ports

- Includes GPCS functions for 1000BASE-X connections

- -Handles SNMP and RMON counters

- IX Bus

- Supports up to 5.12 Gbps memory bus bandwidth

- Variable bus speed of 33 MHz to 80 MHz

- 64-bit bus with three modes of operation:

- Full 64 bits for transmit or receive

- Split —32 low bits for receive, and 32 high bits for transmit

- Narrow —32 bits for transmit or receive — Independent 2 Kbyte transmit FIFO and 4 Kbyte reasons FIFO for each part

- Kbyte receive FIFO for each port

- Supports little or big endian byte ordering

- Supports receive packet fragmentation on byte boundaries (replay feature)

- Programmable transmit and receive bus thresholds

- Enables optional appending of packet status

#### Performance

- Packet transfers are completed prior to servicing CPU interrupt requests

- Enables early address filtering ability, with packet header preprocessing

- IEEE P802.1Q Virtual Bridged Local Area Network (VLAN) tag append, strip and replace function on chip, during packet transmission

- Offers ignore or stop transmission options following packet transmission errors

- Provides programmable automatic discard of badly received packets such as cyclic redundancy (CRC) errors and too long packets

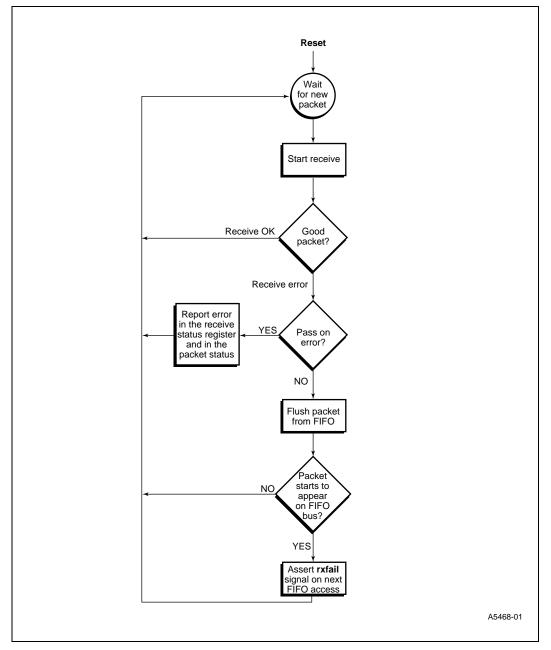

- Informs the system in case bad packets start to appear on the FIFO bus

- -Allows interpacket gap (IPG) programming

#### Serial

- Enables independent mode of operation in each port

- Supports IEEE 802.3x standard flow-control functionality

- Interfaces standard GPCS connections (10b interface)

- Interfaces standard GMII connections

- Supports 1000BASE-SX, 1000BASE-LX, 1000BASE-CX, and 1000BASE-T connections

- Provides programmable CRC generation and removal

- Supports Auto-Negotiation link protocol for 1000BASE-X

- Implements only full-duplex operation

- Complies with IEEE 802.3z standard

- -Supports large packets of up to 64 Kbytes

#### **CPU** Interface

- Supports fully programmable independent ports through a dedicated generic CPU port

- --- Supports interrupt programming

- -Provides an 8- or 16-bit bus for register access

#### Device

- CPU and FIFO interfaces are compatible with the IXF440 Multiport 10/100 Mbps Ethernet Controller and the IXP1200 Network Processor.

- Includes internal and external loopback capabilities

- -Provides software reset support

- -Supports JTAG boundary scan

- Implemented in a low-power 3.3 V and 5 V tolerant CMOS device

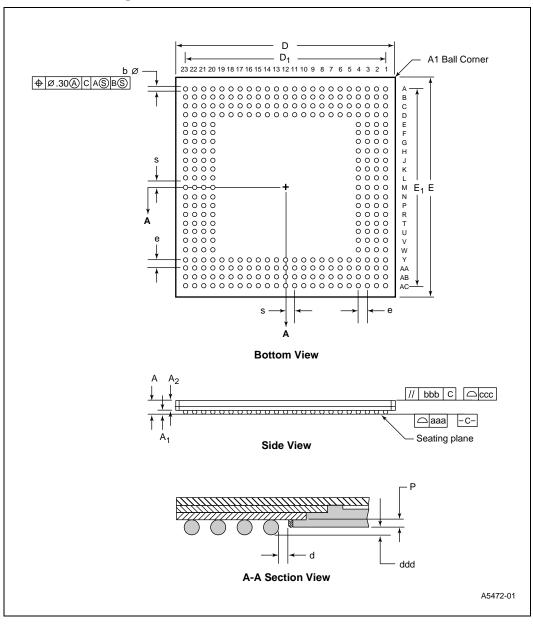

- 304-ESBGA package.

**Notice:** This document contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

Order Number: 278310-008 June, 2002

#### **Revision History**

| Date     | Revision | Description                                                                                  |

|----------|----------|----------------------------------------------------------------------------------------------|

| 8/31/99  | 001      | Initial release.                                                                             |

| 12/15/99 | 002      | Format revision, electrical specification updates.                                           |

| 5/26/00  | 003      | Updates for IXP1200 v1.0 release.                                                            |

| 9/26/00  | 004      | Changed to Intel branding with updates for IXP1200 v1.1 release.                             |

| 12/13/00 | 005      | Updates for IXP1200 v1.2 release.                                                            |

| 05/18/01 | 006      | Updates for the V1.3 SDK.                                                                    |

| 10/02/01 | 007      | Changes to Table 16, Table 18, Section 9.0, Figure 56.                                       |

| 5/23/02  | 008      | Change to Figure 31; removed extended temperature QDF references; added footnote to Table 5. |

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IXF1002 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2002

Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries

\*Other names and brands may be claimed as the property of others.

# intപ്രം Contents

| 1.0 | Introdu                  | ction                      |                                                                                                               | 9              |

|-----|--------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------|----------------|

|     | 1.1<br>1.2<br>1.3        | Block [                    | al Description<br>Diagram<br>are Overview                                                                     | 9              |

|     |                          |                            |                                                                                                               |                |

| 2.0 | Pinout                   |                            |                                                                                                               |                |

|     | 2.1<br>2.2<br>2.3<br>2.4 | Pin Co<br>Conne<br>Pin Lis | Description<br>unt<br>ction Rules<br>t.                                                                       | 17<br>17<br>18 |

| 3.0 | Registe                  | ers Desc                   | ription                                                                                                       | 21             |

|     | 3.1<br>3.2               | 3.1.1                      | er Conventions<br>Access Rules<br>egister                                                                     | 21             |

|     |                          | 3.2.1                      | Register Mapping                                                                                              |                |

|     |                          | 3.2.2                      | Base Registers                                                                                                |                |

|     |                          |                            | 3.2.2.1 Interrupt Status Register                                                                             |                |

|     |                          |                            | 3.2.2.2 Interrupt Enable Register                                                                             |                |

|     |                          |                            | 3.2.2.3 Port Control Register                                                                                 | 24             |

|     |                          |                            | 3.2.2.4 Identification and Revision Register                                                                  |                |

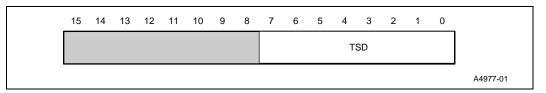

|     |                          |                            | 3.2.2.5 Transmit and Receive Status Register                                                                  |                |

|     |                          |                            | 3.2.2.6 Transmit Counter Overflow Status Register                                                             |                |

|     |                          |                            | 3.2.2.7 Receive Counter Overflow Status Register                                                              |                |

|     |                          | 3.2.3                      | Configuration Registers                                                                                       |                |

|     |                          |                            | 3.2.3.1 Transmit and Receive Error Mode Register                                                              |                |

|     |                          |                            | 3.2.3.2 FIFO Threshold Register                                                                               |                |

|     |                          |                            | <ul><li>3.2.3.3 Port Working Mode Register</li><li>3.2.3.4 Transmit and Receive Parameters Register</li></ul> | JZ             |

|     |                          |                            | 3.2.3.5 Transmit Threshold Register                                                                           |                |

|     |                          |                            | 3.2.3.6 Transmit Flow-Control Pause Time Register                                                             |                |

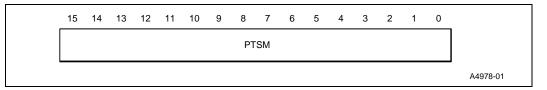

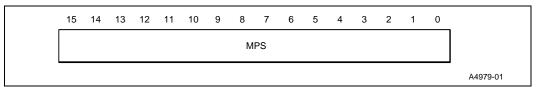

|     |                          |                            | 3.2.3.7 Maximum Packet Size Register                                                                          |                |

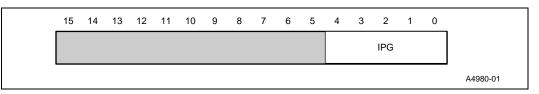

|     |                          |                            | 3.2.3.8 Inter Packet Gap Value Register                                                                       |                |

|     |                          |                            | 3.2.3.9 MAC Address Registers                                                                                 |                |

|     |                          |                            | 3.2.3.10VLAN Tag Length/Type Register                                                                         |                |

|     |                          |                            | 3.2.3.11Transmit Counter Overflow Mask Register                                                               | 39             |

|     |                          |                            | 3.2.3.12Receive Counter Overflow Mask Register                                                                |                |

|     |                          | 3.2.4                      | GMII Management Access Registers                                                                              | 42             |

|     |                          |                            | 3.2.4.1 GMII Management Access Register                                                                       |                |

|     |                          |                            | 3.2.4.2 GMII Management Data Register                                                                         |                |

|     |                          | 3.2.5                      | GMII Management Register Set                                                                                  |                |

|     |                          |                            | 3.2.5.1 GMII Control Register                                                                                 |                |

|     |                          |                            | 3.2.5.2 GMII Status Register                                                                                  |                |

|     |                          |                            | 3.2.5.3 AN Advertisement Register                                                                             |                |

|     |                          |                            | 3.2.5.4 AN Link Partner Ability Base Page Register                                                            |                |

|     |                          |                            | 3.2.5.5 AN Expansion Register                                                                                 |                |

|     |                          |                            | 3.2.5.6 AN Next Page Register<br>3.2.5.7 AN Link Partner Receive Next Page Register                           |                |

|     |                          |                            | 5.2.5.7 AN LINK Partner Receive Next Page Register                                                            | oZ             |

|     |        |           | 3.2.5.8 Extended Status Register<br>3.2.5.9 GPCS Status Register |    |

|-----|--------|-----------|------------------------------------------------------------------|----|

|     | 3.3    | Networ    | k Statistic Counter Mapping                                      |    |

|     |        | 3.3.1     | Register Mapping                                                 |    |

|     |        | 3.3.2     | Network Statistic Counters Access Rules                          |    |

|     | 3.4    | Access    | Sequences                                                        |    |

|     |        | 3.4.1     | Initialization Sequence                                          |    |

|     |        | 3.4.2     | Mode Change Sequence                                             |    |

|     |        | 3.4.3     | Interrupt Handling Sequence                                      |    |

| 4.0 | IX Bus | Interface | e Operation                                                      |    |

|     | 4.1    | IX Bus    | Interface                                                        | 59 |

|     |        | 4.1.1     | IX Bus Operating Modes                                           | 59 |

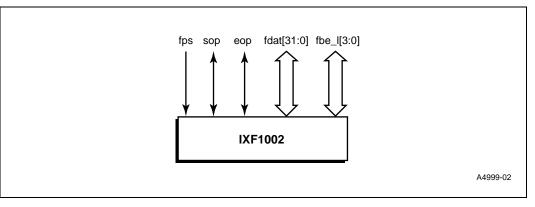

|     |        |           | 4.1.1.1 Signal Naming in Full-64 and Narrow Mode                 | 59 |

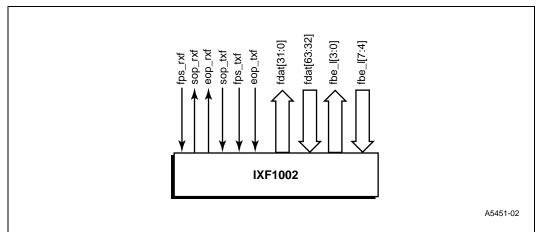

|     |        |           | 4.1.1.2 Signal Naming in Split Mode                              | 59 |

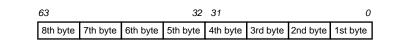

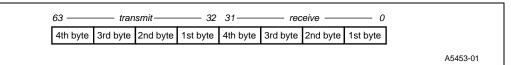

|     |        | 4.1.2     | Byte Ordering on IX Bus                                          | 60 |

|     |        | 4.1.3     | FIFO Status Signaling                                            | 62 |

|     | 4.2    | Packet    | Transmission                                                     | 62 |

|     |        | 4.2.1     | Packet Loading                                                   | 62 |

|     |        | 4.2.2     | VLAN Tagging                                                     |    |

|     |        |           | 4.2.2.1 VLAN Tag Functions in IXF1002                            | 64 |

|     |        |           | 4.2.2.2 VLAN Tag Append                                          |    |

|     |        |           | 4.2.2.3 VLAN Tag Strip                                           |    |

|     |        |           | 4.2.2.4 VLAN Tag Replace                                         |    |

|     |        | 4.2.3     | Network Transmission                                             |    |

|     |        | 4.2.4     | FIFO Underflow                                                   |    |

|     |        |           | 4.2.4.1 Stopping Mode on Transmission Underflow Error            |    |

|     |        | 4.2.5     | Transmit Flow Diagram                                            |    |

|     | 4.3    |           | Reception                                                        |    |

|     |        | 4.3.1     | Packet Storing                                                   |    |

|     |        |           | 4.3.1.1 Packet Status                                            |    |

|     |        | 4.3.2     | Header Preprocessing                                             |    |

|     |        | 4.3.3     | Packet Segmentation                                              |    |

|     |        | 4.3.4     | Packet Abortion                                                  |    |

|     |        | 4.3.5     | Network Reception                                                |    |

|     |        | 4.3.6     | Rejecting Mode on Reception Errors                               |    |

|     |        | 4.3.7     | Accepting Mode on Reception Errors                               |    |

|     |        | 4.3.8     | Receive Flow Diagram                                             | 72 |

| 5.0 | CPU In |           | Operation                                                        |    |

|     | 5.1    | CPU In    | terface                                                          | 73 |

|     | 5.2    | Networ    | k Management                                                     | 73 |

|     |        | 5.2.1     | SNMP MIB Support                                                 |    |

|     |        | 5.2.2     | RMON Statistic Group Support                                     |    |

|     |        | 5.2.3     | RMON Host Group Support                                          | 75 |

| 6.0 | Networ | k Interfa | ce Operation                                                     | 77 |

|     | 6.1    | Operati   | ng Modes                                                         | 77 |

|     | 6.2    |           | ort Interface                                                    |    |

|     | 6.3    |           | rame Format                                                      |    |

|     | 6.4    |           | ransmit Operation                                                |    |

7.0

|        | 6.4.1     | Transmit Initiation                          |    |

|--------|-----------|----------------------------------------------|----|

|        | 6.4.2     | Inter Packet Gap                             | 80 |

|        | 6.4.3     | Frame Encapsulation                          | 80 |

|        | 6.4.4     | Terminating Transmission                     | 80 |

|        | 6.4.5     | Flow Control                                 |    |

|        |           | 6.4.5.1 Additional Flow-Control Mode         | 81 |

| 6.5    | MAC R     | Receive Operation                            | 82 |

|        | 6.5.1     | Receive Initiation                           | 82 |

|        | 6.5.2     | Preamble Processing                          | 82 |

|        | 6.5.3     | Frame Decapsulation                          |    |

|        | 6.5.4     | Terminating Reception                        |    |

|        | 6.5.5     | Flow Control                                 |    |

| 6.6    | MAC L     | oopback Operations                           |    |

|        | 6.6.1     | Internal Loopback Mode                       |    |

|        | 6.6.2     | External Loopback Mode                       |    |

| 6.7    | GPCS      | Mode                                         |    |

|        | 6.7.1     | Synchronization                              |    |

|        |           | 6.7.1.1 Comma detect                         |    |

|        | 6.7.2     | Auto-Negotiation                             |    |

|        | -         |                                              |    |

| Timing | g Diagran | ns                                           | 87 |

| 7.1    | IX Bus    | Port Timing Diagrams                         | 87 |

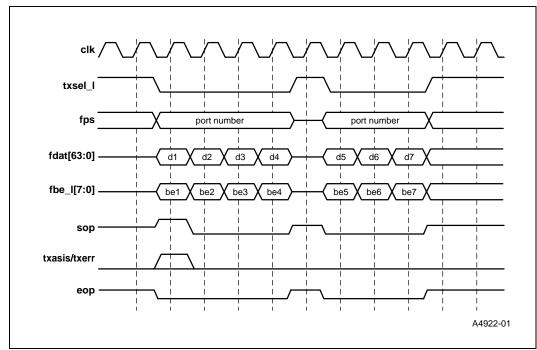

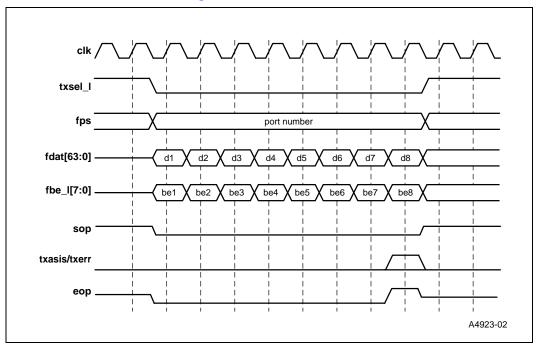

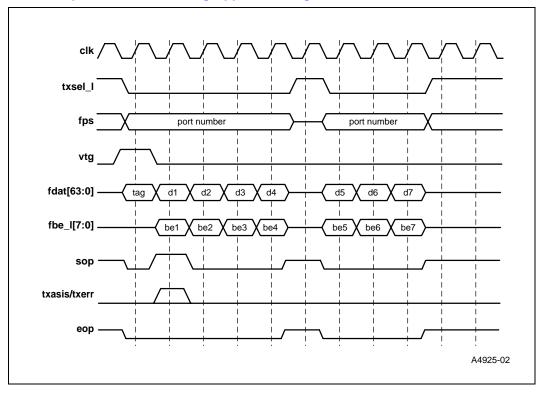

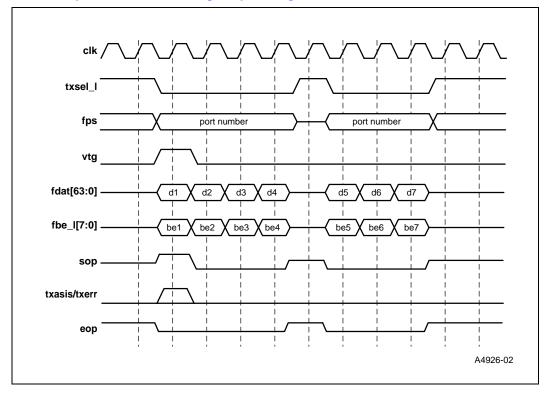

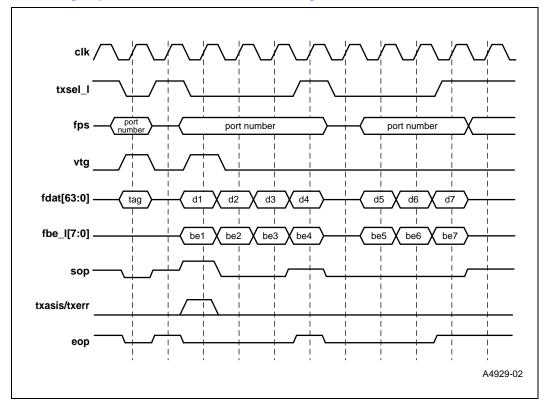

|        | 7.1.1     | Transmit Start-of-Packet Timing              | 87 |

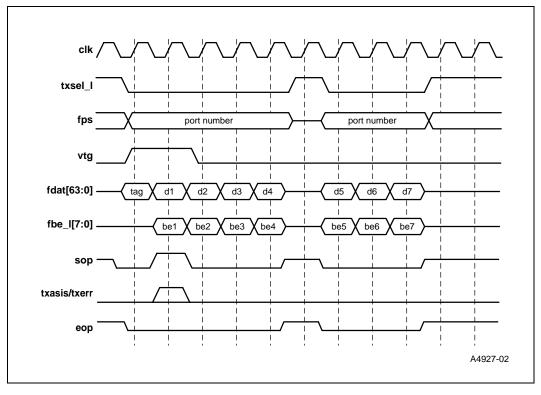

|        | 7.1.2     | Transmit End-of-Packet Timing                |    |

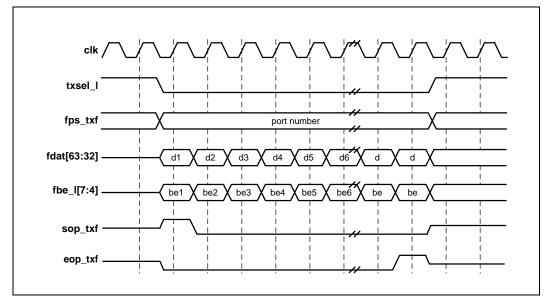

|        | 7.1.3     | Transmit Packet Timing in Split Mode         |    |

|        | 7.1.4     | Transmit Packet with VLAN Tag Append Timing  |    |

|        | 7.1.5     | VLAN Strip Mode Timing                       |    |

|        | 7.1.6     | Transmit Packet with VLAN Tag Replace Timing |    |

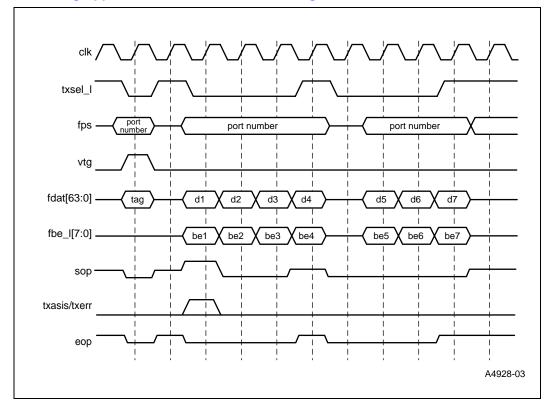

|        | 7.1.7     | VLAN Tag Append in Two txsel_I Bursts        |    |

|        | 7.1.8     | VLAN Tag Replace in Two txsel_I Bursts       |    |

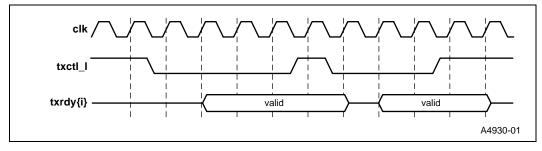

|        | 7.1.9     | Transmit FIFO Control Timing                 |    |

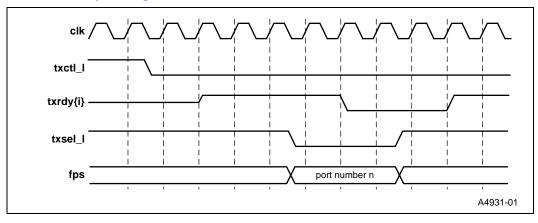

|        | 7.1.10    | Transmit txrdy Timing                        |    |

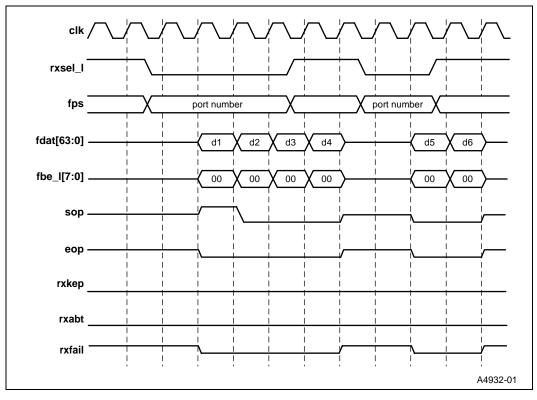

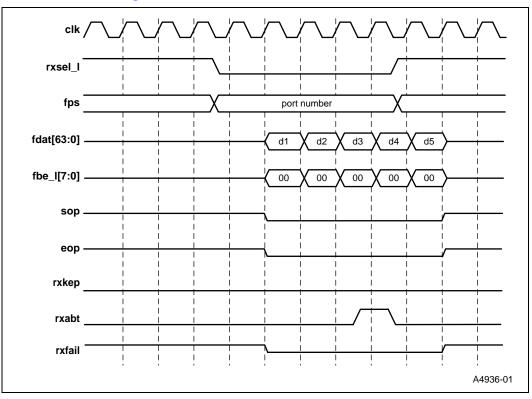

|        | 7.1.11    | Receive Start-of-Packet Timing               |    |

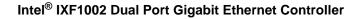

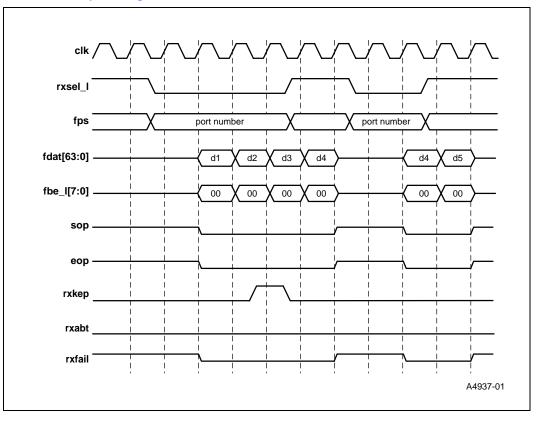

|        |           | Receive End-of-Packet Timing                 |    |

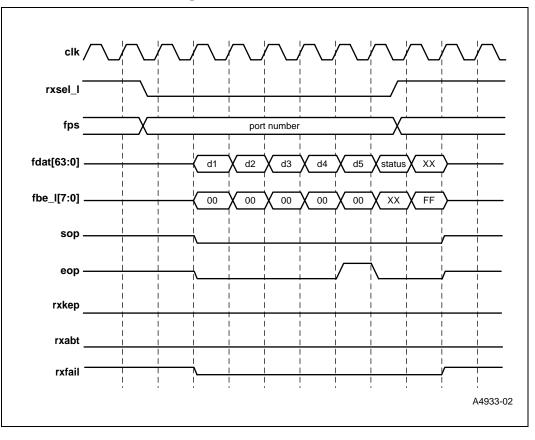

|        |           | Receive Packet Timing in Split Mode          |    |

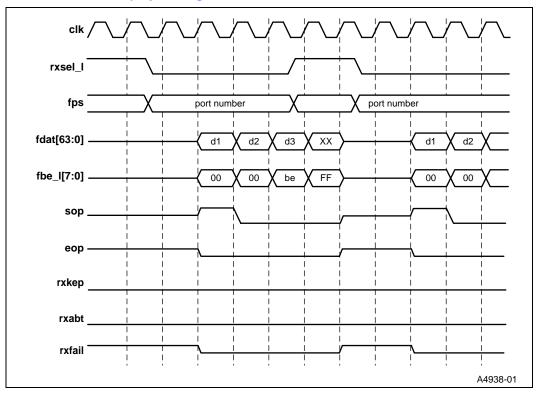

|        |           | Receive rxfail Timing                        |    |

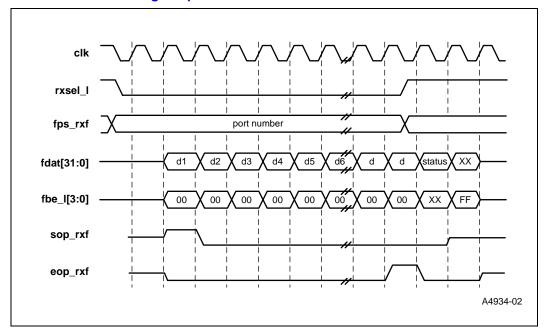

|        |           | Receive rxabt Timing                         |    |

|        | 7.1.16    | 5                                            |    |

|        | 7.1.17    | Receive Header Replay Timing                 |    |

|        | 7.1.18    | Receive FIFO Control Timing                  |    |

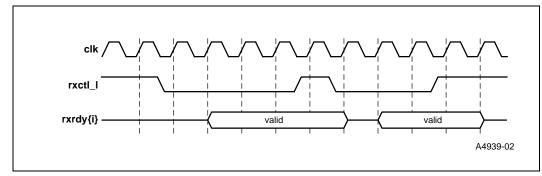

|        | 7.1.19    | Receive rxrdy Control Timing                 |    |

|        |           |                                              |    |

|        |           | 5                                            |    |

|        |           | 5                                            |    |

|        |           | Consecutive Receive-Transmit Timing          |    |

| 7.2    |           | GPCS Port Timing Diagrams                    |    |

| 1.2    |           |                                              |    |

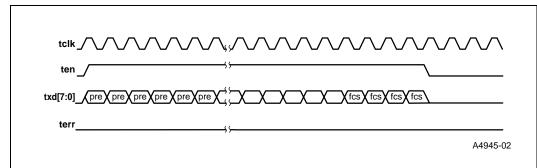

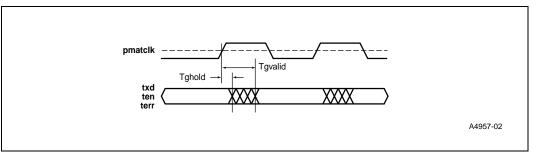

|        | 7.2.1     | Packet Transmission Timing                   |    |

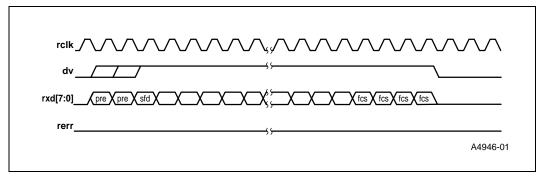

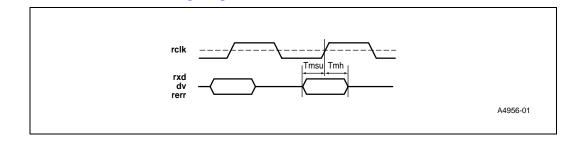

|        | 7.2.2     | Packet Reception Timing                      |    |

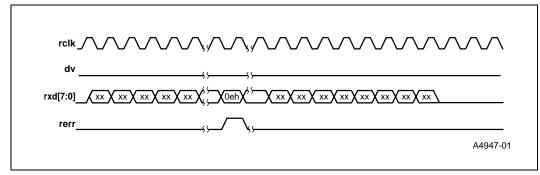

|        | 7.2.3     | False Carrier Timing                         |    |

| 8.0 | Electric | cal and E | Invironmental Specifications              | 105 |

|-----|----------|-----------|-------------------------------------------|-----|

|     | 8.1      | Functio   | onal Operating Range                      | 105 |

|     | 8.2      |           | te Maximum Rating                         |     |

|     | 8.3      | Supply    | Current and Power Dissipation             | 106 |

|     | 8.4      | Tempe     | rature Limit Ratings                      | 106 |

|     | 8.5      | Reset S   | Specification                             | 106 |

|     | 8.6      | FIFO P    | ort Specifications                        | 106 |

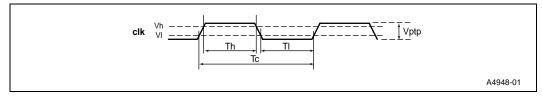

|     |          | 8.6.1     | Clock Specification                       | 106 |

|     |          | 8.6.2     | 3 Volt DC Specifications                  | 107 |

|     |          | 8.6.3     | 5 Volt DC Specifications                  | 108 |

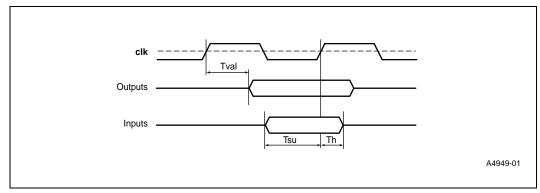

|     |          | 8.6.4     | IX Bus Signals Timing                     | 108 |

|     | 8.7      | CPU P     | ort Specifications                        |     |

|     |          | 8.7.1     | DC Specifications                         | 109 |

|     |          | 8.7.2     | Signals Timing                            | 109 |

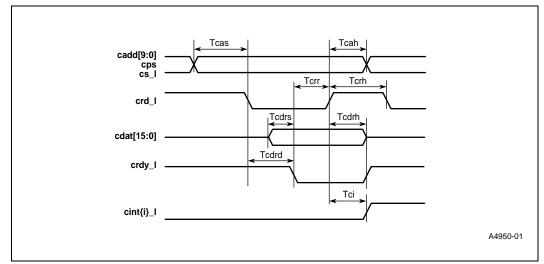

|     |          |           | 8.7.2.1 Read Timing                       | 109 |

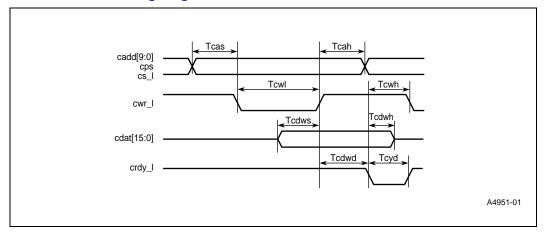

|     |          |           | 8.7.2.2 Write Timing                      |     |

|     |          |           | 8.7.2.3 Timing Parameters                 |     |

|     | 8.8      | GMII/G    | PCS Port Specifications                   |     |

|     |          | 8.8.1     | DC Specifications                         |     |

|     |          | 8.8.2     | Signals Timing                            | 111 |

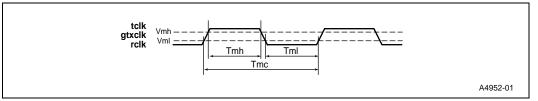

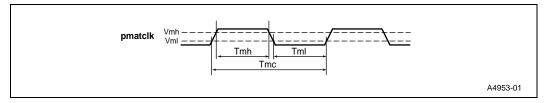

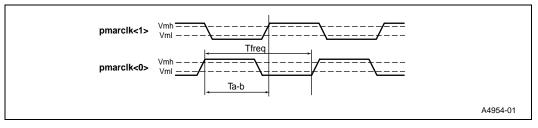

|     |          |           | 8.8.2.1 Clocks Specifications             |     |

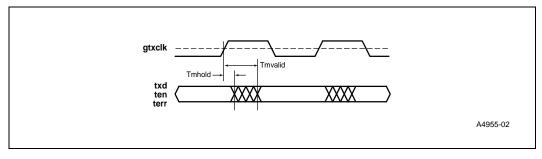

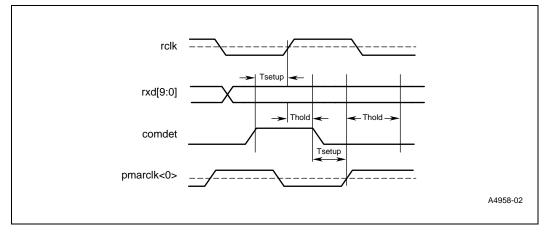

|     |          |           | 8.8.2.2 GMII Signals Timing Diagrams      |     |

|     |          |           | 8.8.2.3 GMII Signals Timing Parameters    |     |

|     |          |           | 8.8.2.4 GPCS Signals Timing Diagrams      |     |

|     | 0.0      |           | 8.8.2.5 GPCS Signals Timing Parameters    |     |

|     | 8.9      |           | Port Specifications                       |     |

|     |          | 8.9.1     | DC Specifications                         |     |

|     |          | 8.9.2     | Signals Timing                            |     |

| 9.0 | Mecha    | nical Sp  | ecifications                              | 117 |

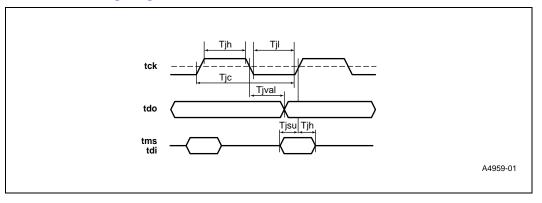

| A   | Joint T  | est Actic | n Group – Test Logic                      | 121 |

|     | A.1      | Genera    | al Description                            | 121 |

|     |          | A.1.1     | Test Access Port Controller               |     |

|     | A.2      | Registe   | ers                                       |     |

|     |          | A.2.1     | Instruction Register                      |     |

|     |          | A.2.2     | Bypass Register                           |     |

|     |          | A.2.3     | Boundary-Scan Register                    |     |

| В   | Glossa   | rv.       | , , , , , , , , , , , , , , , , , , ,     |     |

| D   | B.1      | •         | Abbreviations                             |     |

| •   |          |           |                                           |     |

| С   |          |           | ode                                       |     |

|     | C.1      |           | ew                                        |     |

|     | C.2      |           | ction - txrdy Assertion/Deassertion Rules |     |

|     | C.3      |           | acket Mode                                |     |

|     | C.4      | Port W    | orking Mode Register                      | 126 |

# Figures

| 1  | Block Diagram                                      | 9   |

|----|----------------------------------------------------|-----|

| 2  | Full-64 IX Bus Mode                                | 60  |

| 3  | Narrow IX Bus Mode                                 | 60  |

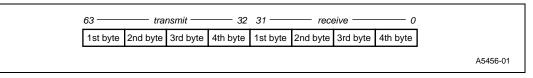

| 4  | Split IX Bus Mode                                  | 60  |

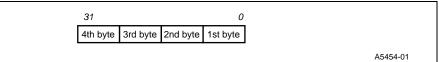

| 5  | Little Endian, Full-64 Bus Mode (BEND=0, FIFMD=01) |     |

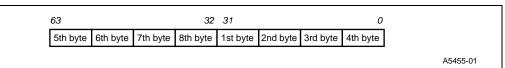

| 6  | Little Endian, Split Bus Mode (BEND=0, FIFMD=10)   | 61  |

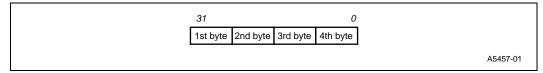

| 7  | Little Endian, Narrow Bus Mode (BEND=0, FIFMD=00)  | 61  |

| 8  | Big Endian, Full-64 Bus Mode (BEND=1, FIFMD=01)    |     |

| 9  | Big Endian, Split Bus Mode (BEND=0, FIFMD=10)      | 61  |

| 10 | Big Endian, Narrow Bus Mode (BEND=1, FIFMD=00)     | 61  |

| 11 | VLAN Tagged MAC Frame Format                       | 63  |

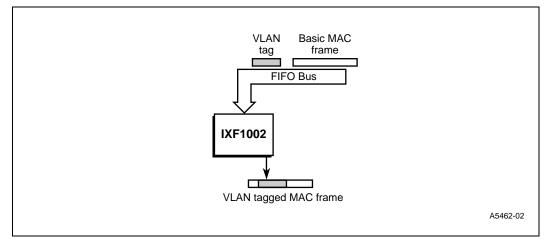

| 12 | VLAN Tag Append                                    | 65  |

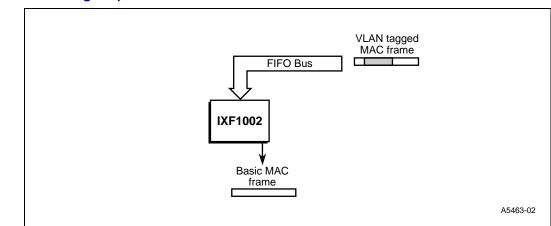

| 13 | VLAN Tag Strip                                     | 65  |

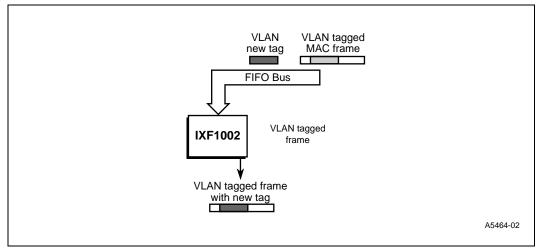

| 14 | VLAN Tag Replace                                   | 66  |

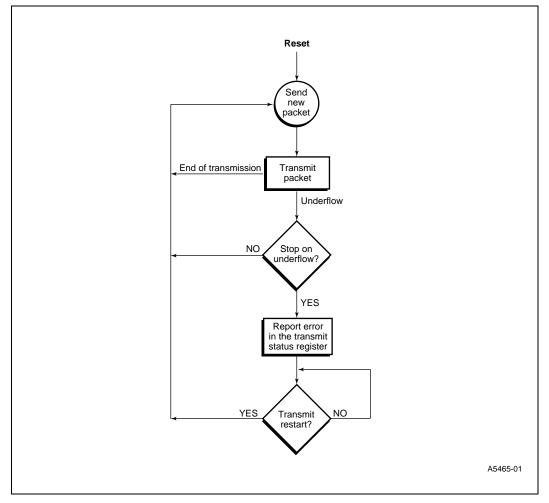

| 15 | Transmit Flow Diagram                              | 67  |

| 16 | Receive Flow Diagram                               |     |

| 17 | MAC Frame Format                                   | 79  |

| 18 | Transmit Start-of-Packet Timing                    |     |

| 19 | Transmit End-of-Packet Timing                      |     |

| 20 | Transmit Packet Timing in Split Mode               |     |

| 21 | Transmit packet with VLAN Tag Append Timing        |     |

| 22 | Transmit packet with VLAN Tag Strip Timing         |     |

| 23 | Transmit packet with VLAN Tag Replace Timing       |     |

| 24 | VLAN Tag Append in Two txsel_I Bursts Timing       |     |

| 25 | VLAN Tag Replace in Two txsel_I Bursts Timing      |     |

| 26 | Transmit FIFO Control Timing                       |     |

| 27 | Transmit txrdy Timing                              |     |

| 28 | Receive Start-of-Packet Timing                     |     |

| 29 | Receive End-of-Packet Timing                       |     |

| 30 | Receive Packet Timing in Split Mode                |     |

| 31 | Receive rxfail Timing                              |     |

| 32 | Receive rxabt Timing                               |     |

| 33 | Receive rxkep Timing                               |     |

| 34 | Receive Header Replay Timing                       |     |

| 35 | Receive FIFO Control Timing                        |     |

| 36 | Receive rxrdy Timing                               |     |

| 37 | Consecutive Transmit-Transmit Timing               |     |

| 38 | Consecutive Transmit-Receive Timing                |     |

| 39 | Consecutive Receive-Transmit Timing                |     |

| 40 | Consecutive Receive-Receive Timing                 |     |

| 41 | Packet Transmission Timing                         |     |

| 42 | Packet Reception Timing                            |     |

| 43 | False Carrier Timing                               |     |

| 44 | IX Bus Clock Timing Diagram                        |     |

| 45 | IX Bus Signals Timing Diagram                      |     |

| 46 | CPU Port Read Timing Diagram                       |     |

| 47 | CPU Port Write Timing Diagram                      |     |

| 48 | GMII Clock Timing Diagram                          |     |

| 49 | GPCS Transmit Clock Timing Diagram                 | 111 |

| 50 | GPCS Receive Clock Timing Diagram |  |

|----|-----------------------------------|--|

| 51 | GMII Port Transmit Timing Diagram |  |

| 52 | GMII Port Receive Timing Diagram  |  |

| 53 | GPCS Port Transmit Timing Diagram |  |

| 54 | GPCS Receive Timing Diagram       |  |

| 55 | JTAG Port Timing Diagram          |  |

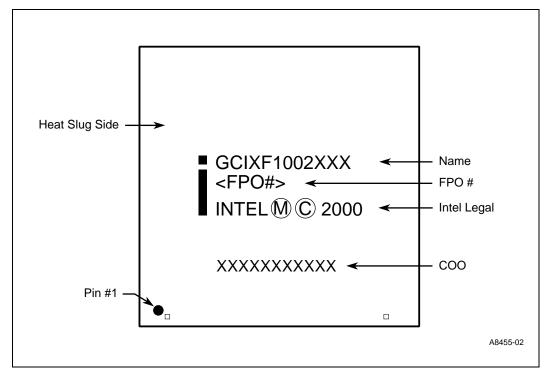

| 56 | Part Marking                      |  |

| 57 | 304-ESBGA Package                 |  |

# **Tables**

| 1  | Component Description                        | 10  |

|----|----------------------------------------------|-----|

| 2  | Signal Descriptions                          | 11  |

| 3  | IXF1002 Pin Count                            | 17  |

| 4  | Pin List                                     | 18  |

| 5  | CSR Register Mapping                         | 22  |

| 6  | Network Statistic Register Mapping           | 55  |

| 7  | IX Bus Receive Packet Status                 | 69  |

| 8  | SNMP MIB to IXF1002 Counters Mapping         | 74  |

| 9  | RMON Statistics to IXF1002 Counters Mapping  | 74  |

| 10 | RMON Host to IXF1002 Counters Mapping        | 75  |

| 11 | GMII Port Signals versus Standard Signals    | 78  |

| 12 | Ethernet Frame Description                   | 79  |

| 13 | Flow-Control Field Matching                  | 83  |

| 14 | GPCS Port Signal Description                 |     |

| 15 | Functional Operating Range                   |     |

| 16 | Absolute Maximum Rating                      |     |

| 17 | Supply Current and Power Dissipation         |     |

| 18 | Temperature Limit Ratings                    |     |

| 19 | IX Bus Clock Timing Specifications           |     |

| 20 | IX Bus 3.3 V Signaling Specifications        |     |

| 21 | IX Bus 5 V Signaling Specifications          |     |

| 22 | IX Bus Signals Timing Specifications         |     |

| 23 | CPU Port DC Specifications                   |     |

| 24 | Timing Parameters                            | 110 |

| 25 | GMII/GPCS Port DC Specifications             |     |

| 26 | GMII/GPCS Port Signals Timing Specifications | 112 |

| 27 | Signals Timing Parameters                    | 113 |

| 28 | GPCS Signals Timing Parameters               | 114 |

| 29 | JTAG Port DC specifications                  |     |

| 30 | JTAG Port Timing Specifications              |     |

| 31 | 304-ESBGA Dimensional Attributes             |     |

### 1.0 Introduction

### 1.1 General Description

The Intel<sup>®</sup> IXF1002 Dual-Port Gigabit Ethernet Controller includes two full-duplex independent 1000 Mb/s Ethernet controllers and interfaces directly to Gigabit Ethernet standard transceivers through its Gigabit Media Independent Interface (GMII) or GPCS interface. The IXF1002 handles Simple Network Management Protocol (SNMP) and Remote Monitoring (RMON) management counter sets, accessible through a generic CPU 8/16-bit interface, which is also used for mode programming. Each MAC port includes a 4 Kbyte FIFO for packet receive, and a 2 Kbyte FIFO for packet transmit. All the packets are transferred onto a high-performance, common IX Bus interface. The IXF1002 CPU and IX Bus interfaces are compatible to the Intel<sup>®</sup> 21440 Octal Fast Ethernet Controller device.

The IXF1002 is fully compatible with IEEE 802.3x and 802.3z standards, including Auto-Negotiation and flow-control support.

It is implemented in a low-power 3.3 V CMOS device within a 304-ESBGA package.

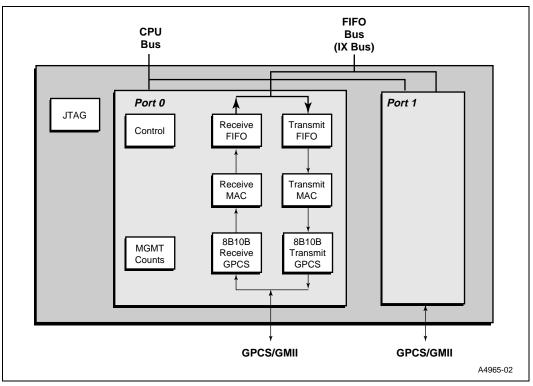

#### 1.2 Block Diagram

Figure 1 shows the IXF1002 block diagram.

#### Figure 1. Block Diagram

### **1.3 Hardware Overview**

Table 1 describes the IXF1002 components.

#### Table 1. Component Description

| Component     | Description                                                                                                                                                  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit FIFO | A 2 Kbyte buffer for temporary storage of transmitted packets. The transmit FIFO has direct interface to the IX Bus.                                         |

| Receive FIFO  | A 4 Kbyte buffer for temporary storage of received packets. Supports packet deletion in case of errors. The receive FIFO has direct interface to the IX Bus. |

| Transmit MAC  | Implements the IEEE 802.3 transmit full-duplex MAC functions while interfacing between the transmit FIFO and the GMII PHY or the GPCS function.              |

| Receive MAC   | Implements the IEEE 802.3 receive full-duplex MAC functions while interfacing between the receive FIFO and the GMII PHY or the GPCS function.                |

| GPCS          | Implementing the 1000BASE-X PCS layer that includes the Auto-Negotiation synchronization and encoding/decoding functions.                                    |

| SNMP and RMON | Handles network statistic counters for SNMP and RMON.                                                                                                        |

| Control       | Handles the chip registers accessible through the CPU bus.                                                                                                   |

| JTAG          | Includes the JTAG technologies IEEE 1149.1 (JTAG) boundary scan logic.                                                                                       |

# 2.0 Pinout

This chapter describes the IXF1002 pinouts.

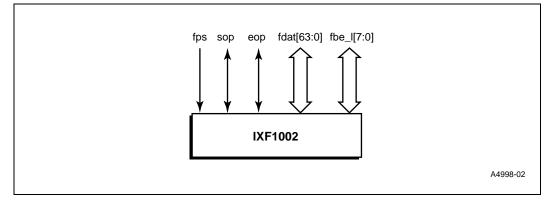

### 2.1 Signal Description

Table 2 describes the IXF1002 signals.

The following conventions are used in the signal names:

- \_I: Indicates that the pin is active low.

- {i}: The i subscript appended to pin names indicates that each port has its own pin (numbered from 0 to 1).

- <m:l>: Refers to a pin number within a bus (m is the most significant, I is the least significant).

The following abbreviations are used in Table 2:

- I = Input

- O = Output

- OD = Open Drain

- I/O = Input/Output

#### Table 2. Signal Descriptions (Sheet 1 of 6)

| Signal Name   | I/O           | Pin Description                                                                                                                                                  |  |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPU Interface | CPU Interface |                                                                                                                                                                  |  |  |  |

|               | 1             | Chip select.                                                                                                                                                     |  |  |  |

| cs_l          | <b> </b> '    | This pin must be asserted to enable CPU access to the chip registers.                                                                                            |  |  |  |

|               |               | CPU port select.                                                                                                                                                 |  |  |  |

| cps           | 1             | Selects one of the two internal ports for register accesses. When asserted, port number 1 is selected. when deasserted, port number 0 is selected.               |  |  |  |

|               |               | Read strobe.                                                                                                                                                     |  |  |  |

| crd_l         | 1             | Upon assertion, the address signals cadd<9:0>, cs_l, and cps are latched by the chip. Deassertion occurs after the read data is latched from the cdat<15:0> bus. |  |  |  |

|               |               | Write strobe.                                                                                                                                                    |  |  |  |

| cwr_l         | 1             | Upon assertion, the address signals cadd<9:0>, cs_l, and cps are latched by the chip. Deassertion must occur while the data is valid on the cdat<15:0> bus.      |  |  |  |

|               |               | Ready indication.                                                                                                                                                |  |  |  |

| crdy_l        | OD            | When asserted, indicates that either data is stable on the cdat<15:0> bus during read access or that data was latched by the chip during write access.           |  |  |  |

| cadd<9:0>     | 1             | Address bus.                                                                                                                                                     |  |  |  |

|               |               | Selects one of the internal registers to be accessed.                                                                                                            |  |  |  |

#### Table 2. Signal Descriptions (Sheet 2 of 6)

| Signal Name      | I/O | Pin Description                                                                                                                                                                                          |

|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |     | CPU data bus.                                                                                                                                                                                            |

|                  |     | In 8 bit mode (default):                                                                                                                                                                                 |

| cdat<15:0>       | I/O | <ul> <li>cdat&lt;7:0&gt; carries data to be written to or read from the registers.</li> </ul>                                                                                                            |

| cual<15.0>       | 1/0 | <ul> <li>cdat&lt;15:8&gt; should be connected to pull up resistors.</li> </ul>                                                                                                                           |

|                  |     | In 16 bit mode:                                                                                                                                                                                          |

|                  |     | <ul> <li>cdat&lt;15:0&gt; carries data to be written to or read from the registers.</li> </ul>                                                                                                           |

|                  |     | Interrupt lines.                                                                                                                                                                                         |

| cint{i}_l        | OD  | These signals are asserted following a variety of programmable conditions.<br>Deassertion occurs after reading the events that cause the interrupt, unless<br>another interrupt is registered meanwhile. |

|                  |     | General reset.                                                                                                                                                                                           |

| reset_l          | I   | Upon reset, all the registers are reset to their default values and the FIFOs are flushed.                                                                                                               |

|                  |     | reset_I assertion time should be at least 1 ms.                                                                                                                                                          |

| IX Bus Interface |     |                                                                                                                                                                                                          |

|                  |     | Vdd clamp.                                                                                                                                                                                               |

| clamp            | I   | Should be connected to the power of the highest signal level used on the IX Bus.                                                                                                                         |

| - 11             |     | System clock.                                                                                                                                                                                            |

| clk              | I   | All the FIFO data transfers are synchronized to this clock.                                                                                                                                              |

| tue el l         |     | Transmit select.                                                                                                                                                                                         |

| txsel_l          | I   | This pin must be asserted to enable transmit FIFO write access.                                                                                                                                          |

|                  |     | Receive select.                                                                                                                                                                                          |

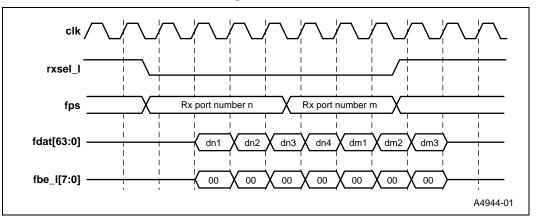

|                  |     | This pin must be asserted to enable receive FIFO read access. The following signals are driven by the IXF1002 upon assertion of rxsel_I:                                                                 |

| rxsel_l          | I   | <ul> <li>fdat&lt;63:0&gt;, fbe_l&lt;7:0&gt;, sop, eop and rxfail in full-64 IX Bus mode.</li> </ul>                                                                                                      |

|                  |     | <ul> <li>fdat&lt;31:0&gt;, fbe_l&lt;3:0&gt;, sop_rxf, eop_rxf and rxfail in split IX Bus mode.</li> </ul>                                                                                                |

|                  |     | <ul> <li>fdat&lt;31:0&gt;, fbe_l&lt;3:0&gt;, sop, eop and rxfail in narrow IX Bus mode.</li> </ul>                                                                                                       |

|                  |     | FIFO port select.                                                                                                                                                                                        |

|                  |     | In full-64 mode and in narrow mode (fps):                                                                                                                                                                |

|                  |     | • When asserted, selects port no. 1 for data transfer through the IX Bus.                                                                                                                                |

| fps/fps_rxf      | I   | • When deasserted, selects port no. 0 for data transfer through the IX Bus.                                                                                                                              |

|                  |     | In split mode(fps_rxf):                                                                                                                                                                                  |

|                  |     | <ul> <li>Selects one of the ports for reading data, through fdat&lt;31:0&gt;, from the<br/>receive FIFO of the selected port.</li> </ul>                                                                 |

|                  |     | FIFO port select.                                                                                                                                                                                        |

|                  |     | In full-64 mode and in narrow mode:                                                                                                                                                                      |

| fps_txf          | 1   | Not in use, should be connected to pull up resistors.                                                                                                                                                    |

| 162-171          | 1   | In split mode:                                                                                                                                                                                           |

|                  |     | <ul> <li>Selects one of the ports for writing data, through fdat&lt;63:32&gt;, to the transmit<br/>FIFO of the selected port.</li> </ul>                                                                 |

| Signal Name | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |     | FIFO data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |     | In full-64 mode:                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     | <ul> <li>fdat&lt;63:0&gt; (I/O) carries the data to be written to the transmit FIFO or read<br/>from the receive FIFO of the selected port.</li> </ul>                                                                                                                                                                                                                                                                                                    |

|             |     | In split mode:                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| fdat<63:0>  | I/O | <ul> <li>fdat&lt;31:0&gt; (output) carries the data to be read from the receive FIFO of the<br/>selected port.</li> </ul>                                                                                                                                                                                                                                                                                                                                 |

|             |     | <ul> <li>fdat&lt;63:32&gt; (input) carries the data to be written to the transmit FIFO of the<br/>selected port.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

|             |     | In narrow mode:                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |     | <ul> <li>fdat&lt;31:0&gt; (I/O) carries the data to be written to the transmit FIFO or to be<br/>read from the receive FIFO of the selected port.</li> </ul>                                                                                                                                                                                                                                                                                              |

|             |     | <ul> <li>fdat&lt;63:32&gt; should be connected to pull up resistors.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

|             |     | FIFO byte enable.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |     | In full-64 mode:                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     | <ul> <li>During transmit, fbe_I&lt;7:0&gt; indicates which of the bytes driven onto<br/>fdat&lt;63:0&gt; contain valid data (valid bytes need to be contiguous and at leas<br/>one byte must be valid). During receive, fbe_I&lt;7:0&gt; indicates which bytes<br/>are valid. Each fbe_I signal relates to a different fdat byte (for example,<br/>fbe_I&lt;0&gt; relates to fdat&lt;7:0&gt; and fbe_I&lt;5&gt; relates to fdat&lt;47:40&gt;).</li> </ul> |

| fbe I<7:0>  | I/O | In split mode:                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IDE_ICT.02  | 1/0 | <ul> <li>fbe_I&lt;3:0&gt; (output) relates to fdat&lt;31:0&gt; that is directed out of the port<br/>(receive FIFO).</li> </ul>                                                                                                                                                                                                                                                                                                                            |

|             |     | • fbe_I<7:4> (input) indicates valid data on fdat<63:32> that is directed into the port (transmit FIFO).                                                                                                                                                                                                                                                                                                                                                  |

|             |     | In narrow mode:                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |     | • fbe_I<3:0> (I/O) relates to fdat<31:0> that is directed in/out of the port.                                                                                                                                                                                                                                                                                                                                                                             |

|             |     | <ul> <li>fbe_l&lt;7:4&gt; should be connected to pull up resistors.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

|             |     | Receive keep.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| rxkep       | I   | When asserted, this signal causes the last read data to be kept in the receive FIFO. May be asserted only with rxsel_l assertion.                                                                                                                                                                                                                                                                                                                         |

|             |     | Start of packet.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     | In full-64 mode and in narrow mode (sop – I/O):                                                                                                                                                                                                                                                                                                                                                                                                           |

| sop/sop_rxf | I/O | <ul> <li>When asserted during transmit, indicates that the first data in the packet is<br/>transferred to the transmit FIFO. During receive, this signal is asserted whe<br/>the first data in the packet is transferred from the receive FIFO to the IX Bus</li> </ul>                                                                                                                                                                                   |

|             |     | In split mode (sop_rxf – output):                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |     | • During receive, this signal is asserted when the first data in the packet is transferred from the receive FIFO to the IX Bus.                                                                                                                                                                                                                                                                                                                           |

|             |     | Start of packet.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     | In full-64 mode and in narrow mode:                                                                                                                                                                                                                                                                                                                                                                                                                       |

| sop_txf     | 1   | This signal is not in use and should be connected to a pull up resistor.                                                                                                                                                                                                                                                                                                                                                                                  |

| 000_00      | l'  | In split mode:                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |     | • During transmit, indicates that the first data in the packet is written to the transmit FIFO.                                                                                                                                                                                                                                                                                                                                                           |

#### Table 2. Signal Descriptions (Sheet 3 of 6)

#### Table 2. Signal Descriptions (Sheet 4 of 6)

| Signal Name  | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |     | End of packet.                                                                                                                                                                                                                                                                                                                                                                                                               |

| eop/eop_rxf  |     | In full-64 mode and in narrow mode (eop – I/O):                                                                                                                                                                                                                                                                                                                                                                              |

|              | I/O | • When asserted during transmit, indicates that the final data in the packet is written to the transmit FIFO. During receive, eop is asserted when the final data of the packet is transferred from the receive FIFO to the IX Bus.                                                                                                                                                                                          |

|              |     | In split mode (eop_rxf – output):                                                                                                                                                                                                                                                                                                                                                                                            |

|              |     | • During receive, eop_rxf is asserted when the final data of the packet is transferred from the receive FIFO to the IX Bus. In the following FIFO access cycle, the packet status is driven onto the bus (see Section 4.3.1.1).                                                                                                                                                                                              |

|              |     | End of packet.                                                                                                                                                                                                                                                                                                                                                                                                               |

|              |     | In full-64 mode and in narrow mode:                                                                                                                                                                                                                                                                                                                                                                                          |

| eop_txf      | 1   | This signal is not in use and should be connected to a pull up resistor.                                                                                                                                                                                                                                                                                                                                                     |

| 000_00       |     | In split mode:                                                                                                                                                                                                                                                                                                                                                                                                               |

|              |     | • During transmit, indicates that the final data in the packet is written to the transmit FIFO.                                                                                                                                                                                                                                                                                                                              |

|              |     | VLAN tag.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| vtg          | I   | When asserted during transmit before sop assertion, VLAN tag will be appended to the transmitted packet. When asserted during transmit together with sop assertion, VLAN tag will be stripped from the transmitted packet. When asserted during transmit before and also together with sop assertion, VLAN tag will be replaced. See Section 4.2.2 for more details.                                                         |

|              |     | <b>NOTE:</b> In case of VLAN tag append, strip or replace, the frame check sequence (FCS) field will be calculated by the IXF1002 (see Section 4.2.2.1).                                                                                                                                                                                                                                                                     |

|              |     | Transmit as is/Transmit error.                                                                                                                                                                                                                                                                                                                                                                                               |

| txasis/txerr | I   | When asserted during transmit, upon transfer of the packet's first data (together with sop assertion), no padding and/or CRC is appended to the packet even if the port was programmed to do so. When asserted upon transfer of the packet's final data (together with eop assertion), the packet is transmitted with a CRC error (if the port is programmed to append CRC), and a GMII error or a symbol error (GPCS mode). |

|              |     | Receive packet failure.                                                                                                                                                                                                                                                                                                                                                                                                      |

| rxfail       | 0   | This signal is asserted if a packet was received with errors, had started to appear<br>on the IX Bus, and was discarded from the receive FIFO.                                                                                                                                                                                                                                                                               |

|              |     | Receive abort.                                                                                                                                                                                                                                                                                                                                                                                                               |

| rxabt        | I   | This signal forces a received packet, that is currently being transferred to the IX Bus, to be aborted and flushed from the receive FIFO. May be asserted only with rxsel_I assertion. Any following packets loaded onto the receive FIFO are not affected by rxabt assertion.                                                                                                                                               |

|              |     | Flow control.                                                                                                                                                                                                                                                                                                                                                                                                                |

| flct_{i}     | I   | When asserted, a flow-control packet with the programmed pause time is transmitted. Upon deassertion, a flow-control packet with time equal to 0 is sent if programmed accordingly. For correct latch of flct pin in the chip - signal flct_{i} should be valid until 1 cycle after flct_lat deassertion.                                                                                                                    |

|              |     | Flow control pin enable                                                                                                                                                                                                                                                                                                                                                                                                      |

| flct_lat     | I   | When asserted the flct_{i} pin will be sampled by the IXF1002. When deasserted, the IXF1002 will latch the value of the flct_{i} pin, ignoring subsequent changes to the flct_{i} pin.                                                                                                                                                                                                                                       |

|              |     | Transmit control enable.                                                                                                                                                                                                                                                                                                                                                                                                     |

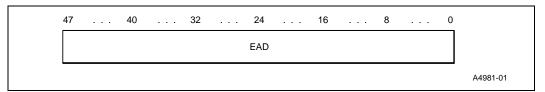

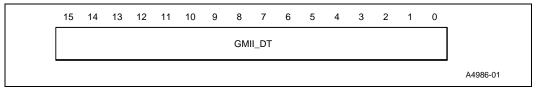

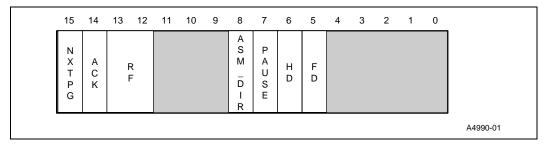

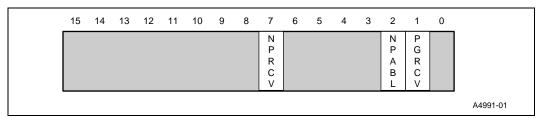

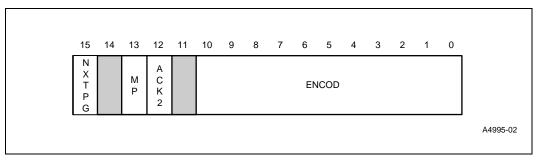

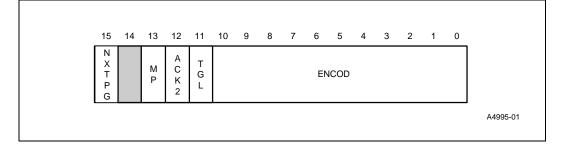

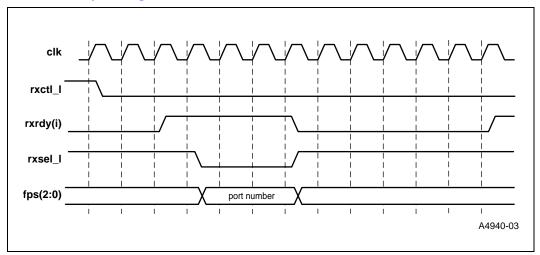

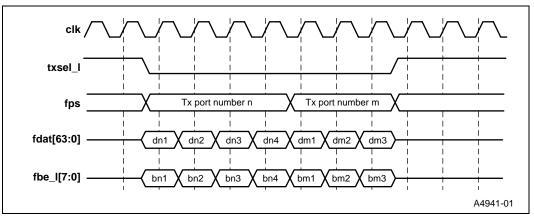

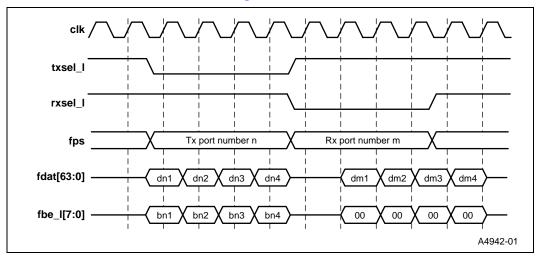

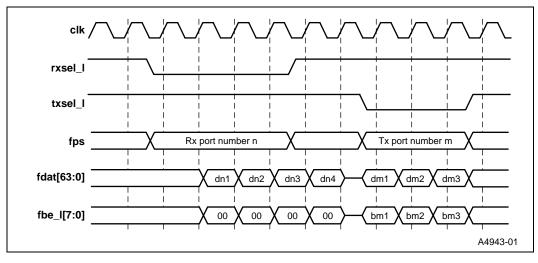

| txctl_l      | I   | When asserted, this pin enables the txrdy_{i} output drivers to report the transmit FIFO status.                                                                                                                                                                                                                                                                                                                             |