## Automotive PMIC with BUCK and precise voltage reference for MCU applications

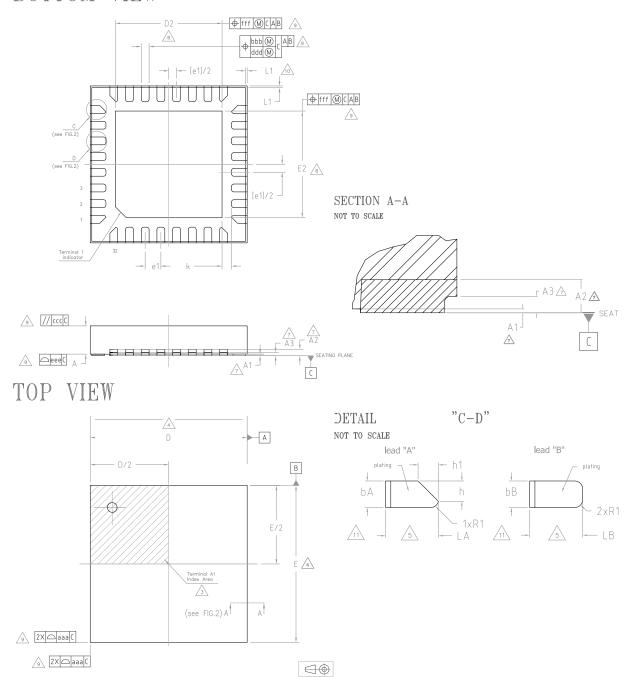

QFN32L Epad 5.0x5.0x1.0 mm

#### **Product status link**

SPSA068

| Product summary |         |  |  |  |  |

|-----------------|---------|--|--|--|--|

| Order code      | SPSA068 |  |  |  |  |

| Package         | QFN32L  |  |  |  |  |

| Packing         | -       |  |  |  |  |

| Option          | Blank   |  |  |  |  |

#### **Features**

- AEC-Q100 qualified

- Pre SMPS BUCK regulator, adjustable via NVM to 5.0 V, 3.3 V, 1.2 V at 0.5 A and 1.0 A load current, 0.4/2.4 MHz. Via external resistive divider, it can regulate a voltage between 5 V and 1.2 V.

- Precise voltage reference (1%), adjustable via NVM to 5.0 V, 3.3V, 1.2 V at 20 mA load current

- Standby mode Iq < 5 μA</li>

- Low quiescent current, 50 μA, in low power active mode

- SPI interface with CRC

- · Programmable soft start

- · Voltage supervisors

- Spread frequency spectrum

- Reset output

- Adjustable window watchdog supervisors

- V<sub>REF</sub>, tracking of V<sub>BUCK</sub> in power-up phase

- Short circuit protected outputs and Fault detection pin to microcontroller

- Low external components number

- Thermal warning and thermal shutdown

### **Description**

SPSA068 is a BUCK voltage regulator with a precise voltage reference for MCU applications. All the regulators have internal power switches.

The LPM allows the operation under light-load conditions reducing the quiescent current down to 50  $\mu$ A typ.

An internal programmable memory allows selecting the main device parameters like output voltages and switching frequencies.

An SPI interface can be used for diagnostics, programming, monitor and external window watchdog.

The device offers a set of features to support applications that need to fulfill functional safety requirements as defined by automotive Safety Integrity Level.

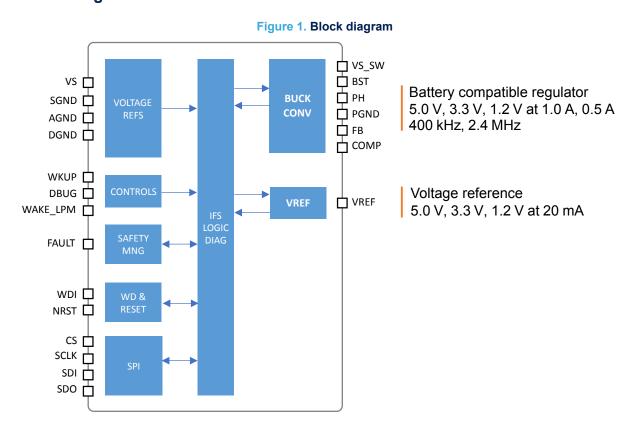

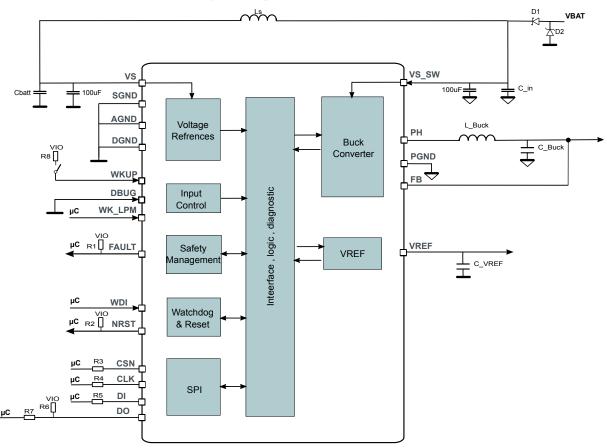

### 1 Overview

The SPSA068 is a PMIC composed by a synchronous current mode BUCK voltage regulator, with integrated LS and HS power-MOS, and a precise voltage reference. It offers flexibility and ease to use, together with a set of features that make it compliant to the commonly used microcontroller in car passenger applications that require functional safety. The product includes input and output monitors, independent band-gaps, ground loss monitors, digital and analog BIST, FAULT pin.

SPSA068 provides 2 different regulated voltages: there are a battery-compatible regulator with integrated MOS for loads up to 1 A and a 1% accurate reference voltage.

A window watchdog, a reset output and an SPI bus complete the product.

The output voltages can be selected via non-volatile memory cells that should be programmed before using the PMIC, since there is no default programming. The absence of external programming components guarantees precision and safety, since output voltages are not susceptible to variations due to the external environment. It also helps reduce the number of external components. Among programmable parameters there are the output voltages, the switching frequency, the spread spectrum disable, the protection intervention thresholds and the BUCK limiting current.

The device must be programmed at the customer's production line at first power-up.

The low power mode allows to supply components at a very optimized quiescent current, down to 50 µA. LPM can be activated by the SPI command and, if not required, it can be disabled by NVM configuration.

An SPI bus is used to program the PMIC and to communicate with the microcontroller. Through the SPI it is possible to provide a watchdog signal and communicate the status of the regulators in case of faults or warnings.

DS14755 - Rev 1 page 2/49

# Block diagram and pin description

## 2.1 Block diagram

DS14755 - Rev 1 page 3/49

# 2.2 Pin description

NC NC DBUG РΗ WDI PGND WAKE\_LPM NC **FAULT** FΒ NC NC **NRST** NC NC NC

Figure 2. Pinout (bottom view)

Table 1. Pin description

| #  | Name   | Туре | Description                                                           | Global / Local |

|----|--------|------|-----------------------------------------------------------------------|----------------|

| 1  | NO CON | NC   | Internally not connected                                              | -              |

| 2  | PH     | 0    | Switching node BUCK                                                   | Local          |

| 3  | PGND   | G    | BUCK power ground                                                     | Local          |

| 4  | NO CON | NC   | Internally not connected                                              | -              |

| 5  | FB     | ı    | BUCK regulated voltage output (feedback to internal voltage monitors) | Local          |

| 6  | NO CON | NC   | Internally not connected                                              | -              |

| 7  | NO CON | NC   | Internally not connected                                              | -              |

| 8  | NO CON | NC   | Internally not connected                                              | -              |

| 9  | NO CON | NC   | Internally not connected                                              | -              |

| 10 | CS     | I    | SPI: chip select input. Internal current pull-up                      | Local          |

| 11 | SDI    | ı    | SPI: serial data input. Internal current pull-down                    | Local          |

| 12 | SCLK   | I    | SPI: serial clock input. Internal current pull-down                   | Local          |

| 13 | SGND   | G    | Signal ground for low noise circuitry                                 | Local          |

| 14 | SDO    | OD   | SPI: serial data output                                               | Local          |

| 15 | DGND   | G    | Digital ground                                                        | Local          |

| 16 | NO CON | NC   | Internally not connected                                              | -              |

| 17 | NO CON | NC   | Internally not connected                                              | -              |

| 18 | NRST   | OD   | Reset, negate                                                         | Local          |

| 19 | NO CON | NC   | Internally not connected                                              | -              |

DS14755 - Rev 1 page 4/49

| #  | Name     | Туре | Description                                                                   | Global / Local |

|----|----------|------|-------------------------------------------------------------------------------|----------------|

| 20 | FAULT    | OD   | Fault pin detection to MCU                                                    | Local          |

| 21 | WAKE_LPM | ı    | LPM Wake pin                                                                  | Local          |

| 22 | WDI      | I    | Watchdog input. WDI is trigger input from the MCU. Internal current pull-down | Local          |

| 23 | DBUG     | I    | Device debug. Connect to ground when not used                                 | Local          |

| 24 | NO CON   | NC   | Internally not connected                                                      | -              |

| 25 | NO CON   | NC   | Internally not connected                                                      | -              |

| 26 | AGND     | G    | Analog GND                                                                    | Local          |

| 27 | WKUP     | I    | Wake up input. Internal 200 kΩ pull-down                                      | Global         |

| 28 | NO CON   | NC   | Internally not connected                                                      | -              |

| 29 | VREF     | 0    | Accurate reference voltage output                                             | Local          |

| 30 | NO CON   | NC   | Internally not connected                                                      | -              |

| 31 | VS       | S    | Input voltage, battery voltage                                                | Global         |

| 32 | VS_SW    | S    | Input voltage for switching regulator (BUCK)                                  | Global         |

DS14755 - Rev 1 page 5/49

# 3 Electrical specifications

## 3.1 Absolute maximum ratings and operating voltage

Table 2. Absolute maximum ratings and operating voltage

| Dia mana | Ab   | 0                 | age  |      |                   |      |

|----------|------|-------------------|------|------|-------------------|------|

| Pin name | Min  | Max               | Unit | Min  | Max               | Unit |

| VS       | -0.3 | 42                | V    | -0.3 | 19 <sup>(1)</sup> | V    |

| VS_SW    | -0.3 | 42                | V    | -0.3 | 19 <sup>(1)</sup> | V    |

| VREF     | -0.3 | 20(2)             | V    | -0.3 | 5.5               | V    |

| DGND     | -0.3 | 0.3               | V    | 0    | 0                 | V    |

| DEBUG    | -0.3 | 20                | V    | -0.3 | 5.5               | V    |

| SGND     | -0.3 | 0.3               | V    | 0    | 0                 | V    |

| AGND     | -0.3 | 0.3               | V    | 0    | 0                 | V    |

| WKUP     | -0.3 | 42                | V    | -0.3 | 19                | V    |

| FB       | -0.3 | 20 <sup>(2)</sup> | V    | -0.3 | 5.5               | V    |

| PGND     | -0.3 | 0.3               | V    | -0.3 | 0.3               | V    |

| PH       | -1   | 42                | V    | -1   | 19                | V    |

| WDI      | -0.3 | 20                | V    | -0.3 | 5.5               | V    |

| CS       | -0.3 | 20                | V    | -0.3 | 5.5               | V    |

| SDI      | -0.3 | 20                | V    | -0.3 | 5.5               | V    |

| SCLK     | -0.3 | 20                | V    | -0.3 | 5.5               | V    |

| SDO      | -0.3 | 20(3)             | V    | -0.3 | 5.5               | V    |

| NRST     | -0.3 | 20(3)             | V    | -0.3 | 5.5               | V    |

| FAULT    | -0.3 | 20(3)             | V    | -0.3 | 5.5               | V    |

| WAKE_LPM | -0.3 | 20                | V    | -0.3 | 5.5               | V    |

<sup>1.</sup> In load dump, the PMIC remains active till 32 V.

### 3.2 Thermal data

### 3.2.1 Thermal resistance

Table 3. Thermal data

| Symbol              | Parameter                                                                         | Value | Unit |

|---------------------|-----------------------------------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | nal resistance with device soldered on a 2s2p PCB + vias (according to JEDEC)     |       | °C/W |

| R <sub>th j-c</sub> | Thermal resistance with device soldered on a 252p PCB + vias (according to JEDEC) | 2     | °C/W |

| P <sub>diss</sub>   | Target power dissipation at 1 A, 2.4 MHz                                          | 1.5   | W    |

DS14755 - Rev 1 page 6/49

<sup>2.</sup> Direct short to 20 V is not allowed when the device is in rec mode and fast discharge is enabled, max voltage allowed ≤ 8 V.

<sup>3.</sup> Direct short to 20 V not allowed when pin is asserted, max voltage allowed ≤ 8 V.

## 3.2.2 Thermal warning and protection

Table 4. Temperature thresholds

| Symbol                 | Parameter                | Test condition | Min | Тур | Max | Unit |

|------------------------|--------------------------|----------------|-----|-----|-----|------|

| T <sub>SD_TH</sub>     | Thermal shutdown         |                | 160 | 175 | 190 | °C   |

| T <sub>SD_hys</sub>    | Thermal hysteresis       |                | 0.5 | 4   | 8   | °C   |

| T <sub>OT_TH</sub>     | Over temperature warning |                | 140 | 155 | 170 | °C   |

| T <sub>OT_hys</sub>    | OT hysteresis            |                | 3   | 7   | 11  | °C   |

| T <sub>SD_filter</sub> | Thermal filter time      |                | 400 | 500 | 600 | μs   |

| TJ                     | Junction temperature     |                | -40 | -   | 150 | °C   |

| T <sub>stg</sub>       | Storage temperature      |                | -   | -   | 150 | °C   |

### 3.3 Electrical characteristics

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: Supply voltage according to the operating range of the Table 2;  $T_J$  according to operating range of the Table 4.

Table 5. Electrical characteristics

| Symbol                 | Parameter                                                                | Test condition                                                                                                                                   | Min  | Тур | Max  | Unit |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|--|--|--|--|--|

|                        | General characteristics                                                  |                                                                                                                                                  |      |     |      |      |  |  |  |  |  |

|                        |                                                                          | BUCK = 3.3 V                                                                                                                                     |      |     |      |      |  |  |  |  |  |

| VS                     | Operating range                                                          | In case of BUCK = 5 V, the device still operates with VS < 5 V, down to 4 V, but regulated voltage will be equal to BUCK = VS - I_load x RonHS   | 4.2  | 14  | 19   | V    |  |  |  |  |  |

|                        |                                                                          | BUCK = 3.3 V                                                                                                                                     |      |     |      |      |  |  |  |  |  |

| VS                     | Operating range LPM                                                      | In case of BUCK = 5 V, the device still operates with VS < 5 V, down to 4.5 V, but regulated voltage will be equal to BUCK = VS - I_load x RonHS | 4.5  | 14  | 19   | V    |  |  |  |  |  |

| I <sub>q-sm</sub>      | Quiescent current in standby mode on VS pin                              | All regulators off VS = 14 V, WKUP = GND                                                                                                         | -    | -   | 5    | μA   |  |  |  |  |  |

| I <sub>q-lpmns</sub>   | Quiescent current in low<br>power mode, BUCK not<br>switching, on VS pin | Buck not switching VS = 14 V, WKUP = High                                                                                                        | -    | 25  | 40   | μA   |  |  |  |  |  |

| I <sub>q-lpm</sub>     | Quiescent current in low power mode on VS pin                            | I <sub>BUCK</sub> = 3.3 V at 80 μA<br>VS = 14 V, WKUP = High                                                                                     | -    | 50  | 75   | μA   |  |  |  |  |  |

| I <sub>active</sub>    | Quiescent current in active power mode on VS pin                         | All regulators on<br>VS = 14 V, WKUP = High                                                                                                      | -    | -   | 12   | mA   |  |  |  |  |  |

|                        |                                                                          | Supply monitors                                                                                                                                  |      |     |      |      |  |  |  |  |  |

| V <sub>UV</sub>        | Undervoltage threshold for VS                                            | Supply decreasing                                                                                                                                | 3.8  | -   | 4.2  | V    |  |  |  |  |  |

| V <sub>UV_HYS</sub>    | Undervoltage hysteresis                                                  |                                                                                                                                                  | 0.05 | -   | 0.2  | V    |  |  |  |  |  |

| t <sub>UV_filter</sub> | Undervoltage filter time                                                 |                                                                                                                                                  | -    | 40  | -    | μs   |  |  |  |  |  |

| V <sub>NRST_LOW</sub>  | NRST pin asserted voltage                                                | I <sub>RESET</sub> = 1 mA (source current)                                                                                                       | 0    | 0.1 | 0.25 | V    |  |  |  |  |  |

| T <sub>NRST</sub>      | NRST time assertion                                                      |                                                                                                                                                  | -    | 500 | -    | μs   |  |  |  |  |  |

DS14755 - Rev 1 page 7/49

| Symbol                            | Parameter                                                                                    | Test condition                                                                                                                                     | Min         | Тур | Max         | Unit |

|-----------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-------------|------|

| V <sub>FAULT</sub>                | FAULT pin asserted voltage                                                                   | I <sub>FAULT</sub> = 1 mA                                                                                                                          | -           | 0.1 | 0.25        | V    |

| T <sub>FAULT</sub>                | FAULT time toggling after LPM exit                                                           |                                                                                                                                                    | -           | 500 | -           | μs   |

|                                   |                                                                                              | Power on reset                                                                                                                                     |             |     |             |      |

| V <sub>POR_R</sub>                | VS threshold                                                                                 | VS rising                                                                                                                                          | 3.1         | -   | 3.8         | V    |

| V <sub>POR_F</sub>                | VS threshold                                                                                 | VS falling                                                                                                                                         | 2.9         | -   | 3.6         | V    |

|                                   |                                                                                              | Oscillator                                                                                                                                         |             |     |             |      |

| f <sub>osc_main</sub>             | Main oscillator frequency                                                                    |                                                                                                                                                    | 2.4 -<br>5% | 2.4 | 2.4 +<br>5% | MHz  |

| f <sub>osc_aux</sub>              | Aux oscillator frequency                                                                     |                                                                                                                                                    | 0.4 -<br>5% | 0.4 | 0.4 +<br>5% | MHz  |

|                                   |                                                                                              | BUCK                                                                                                                                               |             |     |             |      |

| Vout_buck5v                       | Output voltage  Output value depends on the input voltage (V <sub>i</sub> > V <sub>o</sub> ) | BUCK_VOUT_SEL<1:0> = 00<br>V <sub>in</sub> = 6 to 16 V<br>Load = 0.1 A to 1 A                                                                      | -2%         | 5.0 | +2%         | V    |

| Vout_buck3v3                      | Output voltage  Output value depends on the input voltage (V <sub>i</sub> > V <sub>o</sub> ) | BUCK_VOUT_SEL<1:0> = 01<br>V <sub>in</sub> = 6 to 16 V<br>Load = 0.1 A to 1 A                                                                      | -2%         | 3.3 | +2%         | V    |

| Vout_buck1v2                      | Output voltage<br>Output value depends on the input voltage ( $V_i > V_0$ )                  | BUCK_VOUT_SEL<1:0> = 10<br>$V_{in}$ = 6 to 16 V<br>Load = 0.1 A to 1 A<br>Frequency 2.4 MHz                                                        | -2%         | 1.2 | +2%         | V    |

| Vout_buck1v2                      | Output voltage Output value depends on the input voltage (V <sub>i</sub> > V <sub>o</sub> )  | BUCK_VOUT_SEL<1:0> = 11<br>$V_{in}$ = 6 to 16 V<br>Load = 0.1 A to 1 A<br>Frequency 400 kHz                                                        | -4%         | 1.2 | +4%         | V    |

| t <sub>on_min</sub>               | Min Ton internal FET Fast SR                                                                 | Guaranteed by design  BUCK_SLEW_RATE<0> = 1 fast                                                                                                   | -           | 60  | -           | ns   |

| t <sub>on_min</sub>               | Min Ton internal FET Slow SR                                                                 | Guaranteed by design  BUCK_SLEW_RATE<0> = 0 slow                                                                                                   | -           | 75  | -           | ns   |

| F <sub>SW</sub>                   | Free running frequency                                                                       | BUCK_FREQ<5> = 0<br>BUCK_FREQ<5> = 1                                                                                                               | -           | 0.4 | -           | MHz  |

| ΔV <sub>LINE-TRANSIENT</sub>      | Line transient regulation                                                                    | VS from 6 V to 18 V at 1 V/µs (and vice versa) I_load = 1 A  All regulation voltages at 2.4 MHz, 3.3 V and 5 V at 400 kHz  C <sub>load</sub> 40 µF | -6          |     | +6          | %    |

| ΔV <sub>LINE</sub> -TRANSIENT     | Line transient regulation                                                                    | VS from 6 V to 18 V at 1 V/µs (and vice versa) I_load = 1 A 1.2 V at 400 kHz C <sub>load</sub> 40 µF                                               | -15         | -   | +15         | %    |

| $\Delta V_{LOAD	ext{-}TRANSIENT}$ | Load transient regulation                                                                    | I_load from 50 mA to 1 A (and vice versa) at 300 mA/µs                                                                                             | -10         | -   | +10         | %    |

DS14755 - Rev 1 page 8/49

| Symbol                           | Parameter                                | Test condition                                         | Min | Тур  | Max                  | Unit |

|----------------------------------|------------------------------------------|--------------------------------------------------------|-----|------|----------------------|------|

| -                                |                                          | VS = 14 V                                              |     |      |                      |      |

|                                  |                                          | 3.3 V and 5 V at 400 kHz and 2.4 MHz                   |     |      |                      |      |

|                                  |                                          | C <sub>load</sub> 40 μF                                |     |      |                      |      |

|                                  |                                          | I_load from 50 mA to 1 A (and vice versa) at 300 mA/µs |     |      |                      |      |

| ΔV <sub>LOAD-TRANSIENT</sub>     | Load transient regulation                | VS = 14 V                                              | -15 | _    | +15                  | %    |

| 20/15 110 11012111               |                                          | 1.2 V at 2.4 MHz                                       |     |      |                      |      |

|                                  |                                          | C <sub>load</sub> 40 μF                                |     |      |                      |      |

|                                  | Peak switching current                   | BUCK_CURR_LIM<6> = 0                                   | 4.0 |      | 0.4                  |      |

| IL <sub>IMIT_L</sub>             | limitation                               | Iload = 1 A                                            | 1.6 | -    | 3.4                  | Α    |

| VDEE                             | VDEE leekens                             | VS connected                                           |     |      |                      |      |

| VREF <sub>leakage</sub>          | VREF leakage                             | Device in standby or sleep                             | -2  | -    | +2                   | μA   |

| II                               | Peak switching current                   | BUCK_CURR_LIM<6> = 1                                   | 1   |      | 2.3                  | _    |

| IL <sub>IMIT_L</sub>             | limitation                               | Iload = 0.5 A                                          | '   | -    | 2.3                  | Α    |

| Ron <sub>HS</sub>                | High side switch on resistance           |                                                        | _   | 395  | -                    | mΩ   |

| Ron <sub>LS</sub>                | Low side switch on resistance            |                                                        | -   | 200  | -                    | mΩ   |

|                                  |                                          | Fsw = 2.4 MHz, V <sub>o</sub> = 3.3 V                  |     |      |                      |      |

|                                  | Efficiency                               | Fsw = 2.4 MHz, V <sub>o</sub> = 5 V                    |     |      |                      |      |

|                                  |                                          | Fsw = 0.4 MHz, V <sub>o</sub> = 3.3 V                  | 68  | 73   | 73<br>80<br>90<br>92 |      |

| η                                |                                          | Fsw = 0.4 MHz, V <sub>0</sub> = 5 V                    | 75  |      |                      | %    |

|                                  |                                          | lload = 1 A; DCR ≤ 10 mΩ                               | 85  |      |                      |      |

|                                  |                                          | DC ESR ≤ 10 mΩ; V <sub>in</sub> = 14 V                 | 87  | 92   |                      |      |

|                                  |                                          | Slow rise and fall time are configured                 |     |      |                      |      |

|                                  | Soft start time when                     | BUCK_SS_CLK_SEL<2> = 1                                 |     | 0.45 |                      |      |

| tsoftstart_buck                  | start-up                                 | BUCK_SS_CLK_SEL<2> = 0                                 | -   | 1.1  | -                    | ms   |

|                                  |                                          | Fsw = 400 kHz                                          |     |      |                      |      |

| F <sub>spread</sub> _BUCK2       | Spread spectrum range                    | Fsw = 2.4 MHz                                          | -3  | -    | +3                   | %    |

| F <sub>spread_mod_2.4</sub>      | Spread spectrum modulation frequency     | Fsw = 2.4 MHz                                          | -   | 9.3  | -                    | kHz  |

| F <sub>spread_mod_rand_2.4</sub> | Spread spectrum random modulation spread | Fsw = 2.4 MHz                                          | -30 | -    | 20                   | %    |

| F <sub>spread_mod_400</sub>      | Spread spectrum modulation frequency     | Fsw = 400 kHz                                          | -   | 6.25 | -                    | kHz  |

| F <sub>spread_mod_rand_400</sub> | Spread spectrum random modulation spread | Fsw = 400 kHz                                          | -28 | -    | +28                  | %    |

|                                  | Output stage rise time                   | BUCK_SLEW_RATE<0> = 0 slow                             |     |      |                      |      |

| t <sub>RT_PH</sub>               | fsw = 400 kHz and                        | I_load = 500 mA                                        | -   | 12   | -                    | ns   |

|                                  | 2.4 MHz                                  | Guaranteed by design                                   |     |      |                      |      |

|                                  | Output stage fall time                   | BUCK_SLEW_RATE<0> = 0 slow                             |     |      |                      |      |

| t <sub>FT_PH</sub>               | fsw = 400 kHz and                        | I_load = 500 mA                                        | -   | 13   | -                    | ns   |

|                                  | 0.4 MU                                   | Guaranteed by design                                   |     |      |                      |      |

| t <sub>RT_PH</sub>               | Output stage rise time                   | BUCK_SLEW_RATE<0> = 1 fast                             | -   | 7.5  | -                    | ns   |

DS14755 - Rev 1 page 9/49

| Symbol                   | Parameter                                                                       | Test condition                                                                                                                                                                           | Min   | Тур  | Max        | Unit |

|--------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------------|------|

|                          | fsw = 400 kHz and                                                               | I_load = 500 mA                                                                                                                                                                          |       |      |            |      |

|                          | 2.4 MHz                                                                         | Guaranteed by design                                                                                                                                                                     |       |      |            |      |

|                          | Output stage fall time                                                          | BUCK_SLEW_RATE<0> = 1 fast                                                                                                                                                               |       |      |            |      |

| t <sub>FT_PH</sub>       | fsw = 400 kHz and                                                               | I_load = 500 mA                                                                                                                                                                          | -     | 9    | -          | ns   |

|                          | 2.4 MHz                                                                         | Guaranteed by design                                                                                                                                                                     |       |      |            |      |

| Fast disc                | Fast-discharge current of                                                       | Enabled in REC MODE                                                                                                                                                                      | _     | 12   | _          | mA   |

| . us_uss                 | BUCK and VREF                                                                   | FB = 5 V                                                                                                                                                                                 |       |      |            |      |

|                          |                                                                                 | V <sub>REF</sub>                                                                                                                                                                         |       |      |            |      |

| $V_{out\_REF5v}$         | Output voltage (it depends on input voltage $(V_i > V_0)$ )                     | VREF_OUT<10:9> = 00                                                                                                                                                                      | -1%   | 5.0  | +1%        | V    |

| V <sub>out_REF3v3</sub>  | Output voltage (it depends on input voltage (V <sub>i</sub> > V <sub>o</sub> )) | VREF_OUT<10:9> = 01                                                                                                                                                                      | -1%   | 3.3  | +1%        | V    |

| V <sub>out_REF1v2</sub>  | Output voltage (it depends on input voltage (V <sub>i</sub> > V <sub>o</sub> )) | VREF_OUT<10:9> = 10                                                                                                                                                                      | -1.5% | 1.2  | +1.5%      | V    |

| I <sub>load</sub>        | Load current range                                                              |                                                                                                                                                                                          | 0     | -    | 20         | mA   |

| I <sub>REF_TOT</sub>     | Reference voltage current limit                                                 | Ron = 10 Ω                                                                                                                                                                               | 25    | 50   | 70         | mA   |

| tsoftstart_vref          | Soft start time when                                                            | BUCK_SS_CLK_SEL<2> = 1                                                                                                                                                                   | _     | 0.45 | _          | ms   |

| SOFISIARI_VREF           | start-up                                                                        | BUCK_SS_CLK_SEL<2> = 0                                                                                                                                                                   | _     | 1.1  | _          | 1113 |

|                          |                                                                                 | BUCK_SS_CLK_SEL<2> = 1                                                                                                                                                                   |       |      |            |      |

|                          | VREF load capacitor                                                             | BUCK_SS_CLK_SEL<2> = 0                                                                                                                                                                   | 0.00  |      |            |      |

| C <sub>VREF</sub>        |                                                                                 | In case of Cvref > 1.4 µF (BUCK<br>SOFTSART = 0) or Cvref > 3.5 µF (BUCK<br>SOFTART = 1), the VREF_UV flag may be<br>set at power-up. Flag can be cleared by<br>reading the SPI register | 0.22  | -    | 1.4<br>3.5 | μF   |

| _                        | VREF load capacitor                                                             | C <sub>LOAD</sub> = 220 nF                                                                                                                                                               |       |      |            |      |

| R <sub>ESR_CVREF</sub>   | ESR                                                                             | 100 kHz < f < 1 MHz                                                                                                                                                                      | -     | -    | 100        | mΩ   |

| T <sub>oc_filter</sub>   | Filter for over current flag of VREF                                            |                                                                                                                                                                                          | -     | 4    | -          | ms   |

|                          |                                                                                 | WKUP                                                                                                                                                                                     |       |      |            |      |

| V <sub>WAKE_ON</sub>     | Wake pin high threshold                                                         | Compatible with 3.3 V                                                                                                                                                                    | 1.25  | -    | 2          | V    |

| V <sub>WAKE OFF</sub>    | Wake pin Low threshold                                                          | Compatible with 3.3 V                                                                                                                                                                    | 0.8   | -    | 1.75       | V    |

| <br> <br> LEAK_WKUP      | Leakage current                                                                 | Active mode,WAKE < 20 V                                                                                                                                                                  | _     | -    | 2          | uA   |

| t <sub>WAKE_filter</sub> | Wake pin filter time                                                            |                                                                                                                                                                                          | 10    | 25   | 40         | μs   |

| T <sub>wk_rec1</sub>     | Wake up high duration in rec                                                    | WAKE_RETRY_TIMER<2:1> = 00                                                                                                                                                               | -     | 10   | -          | ms   |

| T <sub>wk_rec2</sub>     | Wake up high duration in rec                                                    | WAKE_RETRY_TIMER<2:1> = 01                                                                                                                                                               | -     | 20   | -          | ms   |

| T <sub>wk_rec3</sub>     | Wake up high duration in rec                                                    | WAKE_RETRY_TIMER<2:1> = 10                                                                                                                                                               | -     | 30   | -          | ms   |

| T <sub>wk_rec4</sub>     | Wake up high duration in rec                                                    | WAKE_RETRY_TIMER<2:1> = 11                                                                                                                                                               | -     | 40   | -          | ms   |

DS14755 - Rev 1 page 10/49

| Symbol                       | Parameter                                                                                                            | Test condition                                                                                        | Min | Тур | Max | Unit |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                              | <u>'</u>                                                                                                             | GND loss comparator                                                                                   |     |     |     |      |

| $V_{GL\_TH}$                 | GND loss threshold                                                                                                   |                                                                                                       | 0.3 | -   | 0.8 | V    |

| t <sub>GL_filter</sub>       | GND loss filter                                                                                                      | Filter time before to enable BUCK                                                                     | -   | 100 | -   | μs   |

| $V_{PGL\_TH}$                | PGND loss threshold                                                                                                  |                                                                                                       | 0.1 | -   | 0.4 | V    |

|                              | P                                                                                                                    | Power output UV/OV monitor                                                                            |     |     |     |      |

| V <sub>виски</sub> у_н_о     | Under voltage threshold<br>at falling edge of output<br>(as % of output).<br>Referred to the BUCK<br>relative value  | BUCK_UV_L<3> = 1                                                                                      | 88  | -   | 96  | %    |

| V <sub>вискиv_н_1</sub>      | Under voltage threshold<br>at falling edge of output<br>(as % of output).<br>Referred to the BUCK<br>relative value  | BUCK_UV_L<3> = 0 (default)                                                                            | 84  | -   | 91  | %    |

| V <sub>BUCKUV_HYS</sub>      | Hysteresis of BUCK UV                                                                                                |                                                                                                       | 70  | -   | -   | mV   |

| V <sub>BUCKUV_L</sub>        | Deep under voltage<br>threshold at falling edge<br>of output (as % of<br>output). Referred to<br>BUCK relative value |                                                                                                       | -   | -   | 65  | %    |

| V <sub>BUCKOV_0</sub>        | Over voltage threshold at rising edge of output (as % of output). Referred to the BUCK relative value                | BUCK_OV_L<4> = 0 (default)                                                                            | 104 | -   | 114 | %    |

| V <sub>BUCKOV_1</sub>        | Over voltage threshold at rising edge of output (as % of output). Referred to the BUCK relative value                | BUCK_OV_L<4> = 1                                                                                      | 109 | -   | 120 | %    |

| tuvH_filter_BUCK             | Under voltage threshold filter time                                                                                  |                                                                                                       | -   | 40  | -   | μs   |

| tov_filter_BUCK              | Over voltage threshold filter time                                                                                   | Overvoltage filter time for SPI flag detection  Overvoltage reacts in the loop forcing pulse-skipping | -   | 500 | -   | μs   |

| t <sub>UV_filter_</sub> VREF | Under voltage threshold filter time                                                                                  |                                                                                                       | -   | 20  | -   | μs   |

| t <sub>OV_filter_VREF</sub>  | Over voltage threshold filter time                                                                                   |                                                                                                       | -   | 20  | -   | μs   |

| tov_filter_BUCK_fast         | Over voltage filter time used for open load diagnosis                                                                | BUCK_OL_EN<8> = 1 (open load diagnosis enabled), applicable only during the BUCK start-up phase       | -   | 3   | -   | μs   |

| t <sub>UVL_filter_BUCK</sub> | Buck deep under voltage filter time                                                                                  |                                                                                                       | -   | 3   | -   | μs   |

| V <sub>REFUV_0</sub>         | Under voltage threshold<br>at falling edge of output<br>(as % of output).<br>Referred to the VREF<br>relative value  | VREF_UV_L<11> = 0 (default)                                                                           | 87  | -   | 96  | %    |

| V <sub>VREFUV_1</sub>        | Under voltage threshold<br>at falling edge of output<br>(as % of output).<br>Referred to the VREF<br>relative value  | VREF_UV_L<11> = 1                                                                                     | 82  | -   | 91  | %    |

DS14755 - Rev 1 page 11/49

| Symbol                        | Parameter                                                                                             | Test condition                                                                            | Min   | Тур | Max   | Unit |

|-------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-----|-------|------|

| V <sub>REFUV_HYS</sub>        | Hysteresis of VREF UV                                                                                 |                                                                                           | 100   | -   | _     | mV   |

| V <sub>VREFOV_0</sub>         | Over voltage threshold at rising edge of output (as % of output). Referred to the VREF relative value | VREF_OV_L<12> = 0 (default)                                                               | 104   | -   | 116   | %    |

| V <sub>REFOV_1</sub>          | Over voltage threshold at rising edge of output (as % of output). Referred to the VREF relative value | VREF_OV_L<12> = 1                                                                         | 109   | -   | 120   | %    |

| T <sub>POWER_ON_TIMEOUT</sub> | Power on timeout for BUCK and VREF                                                                    |                                                                                           | -     | 3   | -     | ms   |

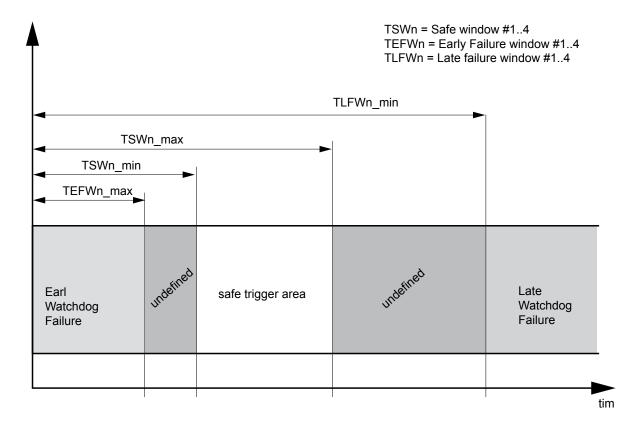

|                               |                                                                                                       | Watchdog trigger                                                                          |       |     |       |      |

| VH <sub>WDI</sub>             | WDI pin threshold high                                                                                |                                                                                           | 2.3   | -   | -     | V    |

| VL <sub>WDI</sub>             | WDI pin threshold low                                                                                 |                                                                                           | -     | -   | 1     | V    |

| T <sub>LW</sub>               | Long open window                                                                                      |                                                                                           | 160   | 200 | 240   | ms   |

| R <sub>WDI_PD</sub>           | WDI PD resistance                                                                                     | Active mode                                                                               | 120   | 200 | 350   | kΩ   |

| T <sub>EFW1</sub>             | Early failure window 1                                                                                | WDG_TIME_WINDOW<4:3> = 00                                                                 | -     | -   | 6.4   | ms   |

| T <sub>LFW1</sub>             | Late failure window 1                                                                                 | WDG_TIME_WINDOW<4:3> = 00                                                                 | 15.6  | -   | -     | ms   |

| T <sub>SW1</sub>              | Safe window 1                                                                                         | WDG_TIME_WINDOW<4:3> = 00                                                                 | 7.8   | -   | 12.7  | ms   |

| T <sub>EFW2</sub>             | Early failure window 2                                                                                | WDG_TIME_WINDOW<4:3> = 01                                                                 | -     | -   | 12.7  | ms   |

| T <sub>LFW2</sub>             | Late failure window 2                                                                                 | WDG_TIME_WINDOW<4:3> = 01                                                                 | 31.1  | -   | -     | ms   |

| T <sub>SW2</sub>              | Safe window 2                                                                                         | WDG_TIME_WINDOW<4:3> = 01                                                                 | 15.6  | -   | 25.5  | ms   |

| T <sub>EFW3</sub>             | Early failure window 3                                                                                | WDG_TIME_WINDOW<4:3> = 10                                                                 | -     | -   | 25.5  | ms   |

| T <sub>LFW3</sub>             | Late failure window 3                                                                                 | WDG_TIME_WINDOW<4:3> = 10                                                                 | 62.2  | -   | -     | ms   |

| T <sub>SW3</sub>              | Safe window 3                                                                                         | WDG_TIME_WINDOW<4:3> = 10                                                                 | 31.1  | -   | 50.9  | ms   |

| T <sub>EFW4</sub>             | Early failure window 4                                                                                | WDG_TIME_WINDOW<4:3> = 11                                                                 | -     | -   | 50.9  | ms   |

| T <sub>LFW4</sub>             | Late failure window 4                                                                                 | WDG_TIME_WINDOW<4:3> = 11                                                                 | 124.4 | -   | -     | ms   |

| T <sub>SW4</sub>              | Safe window 4                                                                                         | WDG_TIME_WINDOW<4:3> = 11                                                                 | 62.2  | -   | 101.8 | ms   |

| T <sub>DWR</sub>              | Delay between WD trigger fault and reset low                                                          |                                                                                           | -     | -   | 4     | μs   |

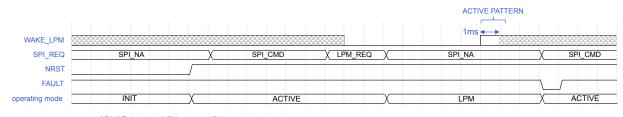

|                               |                                                                                                       | LPM parameters                                                                            |       |     |       |      |

| T <sub>LPM_EN</sub>           | Low power mode enters filter time                                                                     | Digital filter time                                                                       | -     | 5   | -     | ms   |

| T <sub>WAKE_LPM_</sub> FILT   | Filter time on<br>WAKE_LPM to exit from<br>LPM                                                        | Digital filter time                                                                       | -     | 1   | -     | ms   |

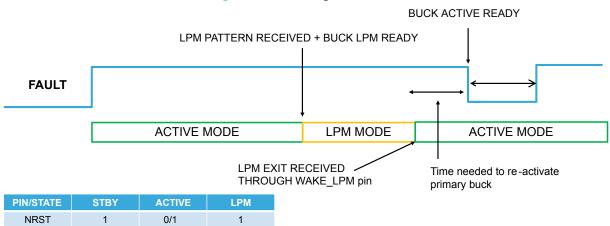

| T <sub>LPM_DIS</sub>          | Low power mode exit delay time                                                                        | Analog delay + digital wait time from filtered WAKE_LPM = 1 to ACTIVE MODE (FAULT toggle) | -     | 8   | -     | ms   |

| T <sub>PHOLD</sub>            | PHOLD timer                                                                                           | Timer starting from WKUP_FILT = 0 before to switch off the device                         | -     | 5   | -     | ms   |

| V <sub>WAKELPM_ON</sub>       | Wake pin high threshold                                                                               | Compatible with 3.3 V                                                                     | 1.25  | -   | 2     | V    |

| V <sub>WAKELPM_OFF</sub>      | Wake pin low threshold                                                                                | Compatible with 3.3 V                                                                     | 0.8   | -   | 1.75  | V    |

| ILEAK_WAKELPM                 | Leakage current                                                                                       | Active mode,WAKE_LPM < 20 V                                                               | -     | -   | 2     | μA   |

DS14755 - Rev 1 page 12/49

| Symbol               | Parameter                      | Test condition | Min | Тур | Max | Unit |

|----------------------|--------------------------------|----------------|-----|-----|-----|------|

| I <sub>LPM_24</sub>  | Load current in LPM 2.4<br>MHz | Fsw = 2.4 MHz  | 0   | -   | 5   | mA   |

| I <sub>LPM_400</sub> | Load current in LPM 400 kHz    | Fsw = 400 kHz  | 0   | -   | 50  | mA   |

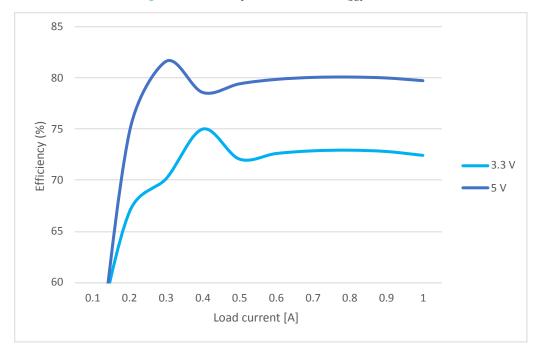

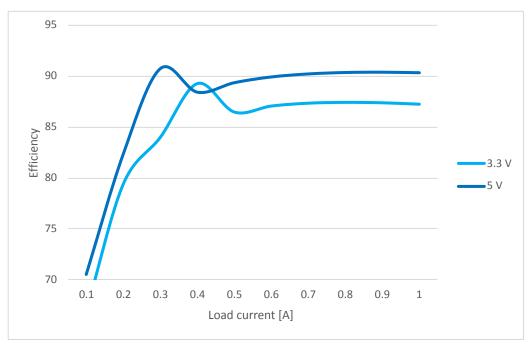

## 3.4 Typical characteristics

Figure 3. Efficiency at 2.4 MHz with V<sub>bat</sub> at 14 V

DS14755 - Rev 1 page 13/49

## 4 Functional description

### 4.1 Programming by NVM

The device has an internal nonvolatile memory used to program the operating parameters.

Programmable values are:

- BUCK VOUT SEL, output values: if '00' is 5 V, if '01' is 3.3 V, if '10' is 1.2 V (2 bits)

- BUCK FREQ, free running frequency: if '0' is 0.4 MHz, if '1' is 2.4 MHz (1 bit)

- BUCK CURR LIM, output current limitation: if '0' is 1.0 A, if '1' is 0.5 A (1 bit)

- BUCK\_PGND\_EN, ground loss detection: if '0' is disabled, if '1' is enabled (1 bit)

- BUCK\_OL\_EN, open load diagnosis: if '0' is disabled, if '1' is enabled (1 bit)

- BUCK\_SS\_CLK\_SEL, soft start duration: if '0' is 0.45 ms, if '1' is 1.1 ms (1 bit)

- BUCK\_UV\_L, UV threshold: if'1' is V<sub>BUCKUV\_H\_0</sub>, if '0' is V<sub>BUCKUV\_H\_1</sub> (1 bit). In case of 1.2 V configuration, it is mandatory to keep NVM configuration to default (V<sub>BUCKUV H 1</sub>)

- BUCK\_OV\_L, OV threshold: if '0' is  $V_{BUCKOV_0}$ , if '1' is  $V_{BUCKOV_1}$  (1 bit)

- VREF OUT, VREF output voltage: if '00' is 5 V, if '01' is 3.3 V, if '10' is 1.2 V (2 bits)

- VREF\_UV\_L, UV threshold: if '0' is V<sub>REFUV\_0</sub> if '1' is V<sub>REFUV\_1</sub> (1 bit)

- VREF\_OV\_L, OV threshold: if '0' is  $V_{REFOV_0}$  if '1' is  $V_{REFOV_1}$  (1 bit)

- Watchdog selection by WDI pin or through SPI (2 bits):

- If NVM "WDG SEL" bits are '00' or '01': no watchdog

- If NVM "WDG SEL" bits are '10': watchdog by PIN

- If NVM "WDG SEL" bits are '11': watchdog by SPI

- Effect of WD failure on FSM. If WDG\_REC\_EN = 0, in SPI register, and WD\_REC\_EN = 0, in NVM register, a WD failure asserts NRST but not REC state: the device keeps an active state with all regulators running. If one of these bits is '1', NRST is asserted and FSM goes to REC state.

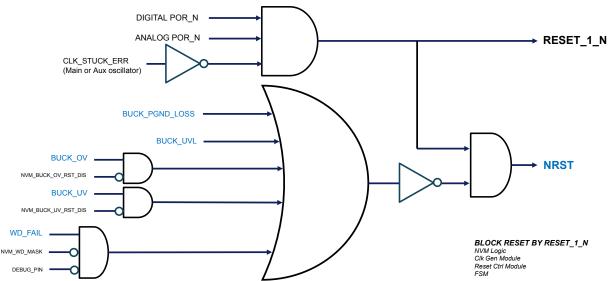

- Effect of BUCK UV/OV failure on FSM. If BUCK\_UV\_REC\_DIS = 1, a BUCK UV fail asserts NRST but not REC state: the device keeps an active state. If BUCK\_UV\_REC\_DIS = 0, a BUCK UV fail asserts NRST and the device goes to REC state. If BUCK\_OV\_REC\_DIS = 1, a BUCK OV fail asserts NRST but not REC state: the device keeps an active state. If BUCK\_OV\_REC\_DIS = 0, a BUCK UV fail asserts NRST and the device goes to REC state.

- Effect of BUCK UV/OV failure on NRST. If BUCK\_UV\_RST\_DIS = 1, a BUCK UV fail does not assert NRST and the device goes to REC state. If BUCK\_UV\_RST\_DIS = 0, a BUCK UV fail asserts NRST and the device goes to REC state. If BUCK\_OV\_RST\_DIS = 1, a BUCK OV fail does not assert NRST and the device goes to REC state. If BUCK\_OV\_RST\_DIS = 0, a BUCK OV fail asserts NRST and the device goes to REC state.

- VREF POWERUP DIS chooses if VREF can be disabled or enabled through the SPI

- VREF\_DELAY sets the turn on delay after BUCK > BUCK UV th: 0 ms, 2.5 ms, 5 ms or 10 ms (2 bits)

- NRST\_RELEASE configures the release of NRST after the BUCK crosses its UV threshold or VREF

crosses its UV threshold (1 bit) at power-up, with the possibility to add a delay, NRST\_DELAY, from 0 ms

(no delay) to 2.5 ms, 5 ms or 10 ms (2 bits)

- LPM MODE DIS: if '0' the LPM mode is active, if '1' the WAKE LPM pin is ignored

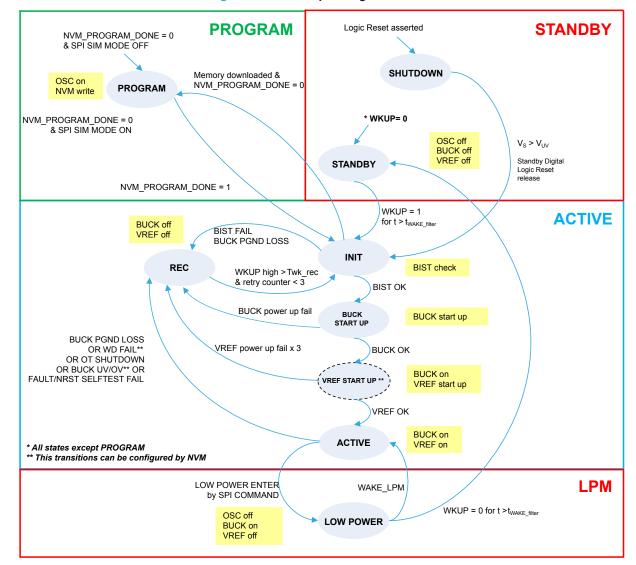

If the PMIC has never been configured, the device automatically moves to NVM program mode to allow to program the desired configuration for the target application.

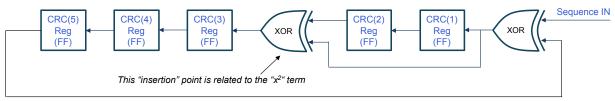

Write procedure is protected by CRC and shall be done by SPI interface. NVM PROGRAM operation can be performed only once.

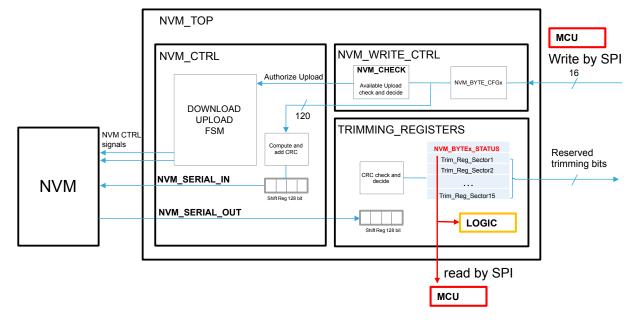

The device embeds a 2 Kbits nonvolatile memory (NVM) where trimming bits are stored to calibrate the device and to configure it. The NVM area can read and written using the control register of SPI. The NVM is internally divided in 16 sectors, each of 128 bit (120 data bit and 8 CRC bit). Two different groups can be distinguished:

- 2 sectors: reserved trimming bits used to calibrate internal voltage and current (ST reserved)

- 1 sector: programmable by the user to configure the device

DS14755 - Rev 1 page 14/49

The MCU can read the configuration bits in NVM\_CONF\_STATUSx. The MCU can write the user trimming bits using the control register (WRITE\_TO\_NVM). The data stored in the SPI data register (NVM\_CONF\_CTRLx) is written inside the trimming registers of the main logic. Then, the user can decide to test the configuration by SPI command (register WRITE\_TO\_NVM with the command ENTER\_SIM\_MODE) or to upload the configuration directly inside the NVM (register WRITE\_TO\_NVM with the command NVM PROGRAM). When the operation is completed, a read operation starts automatically. The whole operation requires about 15 ms.

To simulate the user trimming bits, the procedure at start up is the following:

- 1. The MCU writes the configuration in NVM\_CONF\_CTRLx registers (N bits N SPI registers);

- 2. The MCU writes 0xAAAA (ENTER\_SIM\_MODE) to enter simulation mode by WRITE\_TO\_NVM register;

- 3. The MCU checks the programmed configuration at the end of power-up;

- 4. The MCU writes 0x5555 (EXIT\_SIM\_MODE) to exit from simulation mode by WRITE\_TO\_NVM register and it comes back to PROGRAM MODE.

Then, the user can configure again the trimming bits to test another configuration or can perform the NVM WRITE operation. After physical NVM WRITE operation, soft-trimming procedure will not be available.

To perform the NVM write operation, the procedure is the following:

- 1. The MCU writes the configuration in NVM\_CONF\_CTRLx registers (N bits N SPI registers);

- 2. The MCU sends the 0xF0F0 NVM WRITE CTRL (WRITE TO NVM) command;

- 3. The FSM validates write operation through CRC check of SPI command and NVM CODE. If the check fails, upload operation is discarded, otherwise upload is authorized;

- 4. Then the CRC (8 bits) is computed on the whole sector and data is transferred inside.

Then, the NVM\_PROGRAM\_DONE bit is set to '1'.

Figure 5. NVM block diagram and write procedure

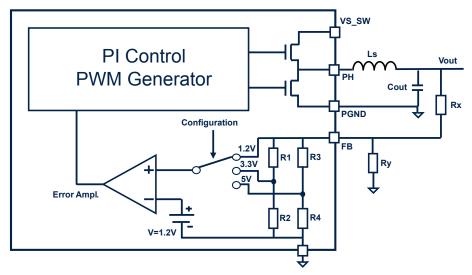

### 4.2 BUCK

The BUCK regulator operates in constant frequency peak current mode control to reduce the switching noise when the LPM is deactivated. The BUCK is enabled by the WKUP pin signal. The input voltage (VS) is compatible to the car passenger battery level. The switching frequency is set via NVM to 0.4 or 2.4 MHz with the possibility to have a spread spectrum (enabled by default and disabled via SPI). The output current can be programed via NVM to support 1.0 A and 500 mA loads.

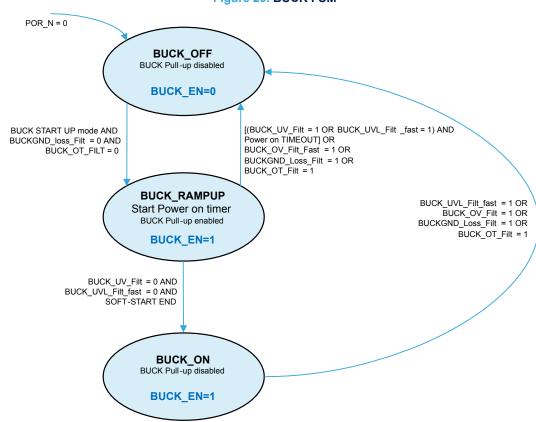

The output voltage is programmed with internal memory cells to 3 possible values. 5 V, 3.3 V and 1.2 V. It is suggested to select the 1.2 V when the BUCK is supplied by a preregulated voltage. When configured to regulate 1.2 V, it is possible, with an external resistor divider, to select the desired regulated voltage between 1.2 V and 5 V. The user shall select a proper resistor divider value following the guidelines indicated in the Section 9: Application information. The over current protection is always active. The soft start time can be set via NVM.

The BUCK regulator provides the following diagnostics:

DS14755 - Rev 1 page 15/49

- Monitor of the output voltage by an independent circuit for UV/OV detection with thresholds set via NVM

- Overtemperature detection by a thermal sensor

- Overcurrent detection and limitation on integrated HS and LS MOSFET

- · PGND loss detection

- Open load diagnosis during BUCK startup phase and ACTIVE MODE

#### **BUCK** fault management:

- If a UV or OV fault occurs, the FAULT pin is asserted low and the corresponding fault bit is set inside the SPI register, where it can be read and cleared. NRST is asserted only if enabled by NVM, otherwise no reset occurs. If configured by NVM, UV or OV faults move the device to the REC state.

- If OT occurs, the power stage is switched OFF when thermal ADC conversion is ready (max 500 μs). The device goes in REC state and restarts when the device is cooled down. The corresponding SPI register bit is set and the FAULT pin is asserted.

- The load overcurrent limitation is a cycle by cycle protection: if the peak current reaches the overcurrent limit, the switcher starts a cycle-by-cycle operation to limit the current until the normal operation is reached. The corresponding fault bit (BUCK\_OC\_STAT) is set inside the SPI register. When the current is limited, the voltage is lower than the expected value, but the regulator is able to operate normally, also with the fault bit stored. The LS MOS overcurrent detection protects the BUCK against a short to battery fault on PH pin, when BUCK LS OC is detected the BUCK regulator goes in high impedance.

- PGND loss detection is able to detect, at power-up, before BUCK startup phase, a ground loss fault on PGND. The corresponding fault bit (PGND\_LOSS) is provided by SPI after t<sub>GL\_filter</sub> filter time. If configured by NVM, when the fault is detected at power-up the BUCK regulator is not enabled and the device moves to REC state (safe state). If PGND\_LOSS occurs during operation, PGND\_LOSS reacts immediately in the loop by forcing the minimum duty cycle, the BUCK continues to operate until the BUCK voltage goes below deep under the voltage threshold: when it happens, the BUCK is disabled and the device moves in a REC state

- The open load detection is able to detect open FB pin fault, to protect the load (for example MCU) against over voltage events. The open load diagnosis works in a different way depending on the state of the device. During BUCK startup phase, a small pull-up current is provided to the FB pin; if the pin is open, FB goes above the BUCK\_OV\_L threshold, the digital FSM detects an OV and moves to REC state. During active mode, the pull-up current is disabled to avoid useless current consumption and impact the regulated voltage accuracy; if the FB pin is open, it goes below the BUCK deep under voltage threshold and, thanks to the integrated resistor divider, the digital FSM detects BUCK UV and moves to REC state. Open load diagnosis can be enabled or disabled by NVM bit.

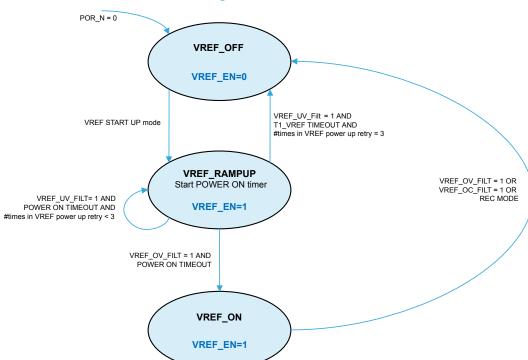

### 4.3 VREF

SPSA068 includes a 1% precise voltage reference output to supply a system ADC. The output voltage can be selected via NVM cells. This regulator is disabled in LPM.

VREF provides the following diagnostics:

- Monitor of the output voltage by an independent circuit for UV/OV detection

- Overcurrent detection and limitation in case of overload or short to ground

#### VREF fault management:

- In case of OV, the regulator is turned off, the fault SPI register bit is set and the FAULT pin is asserted low. The power stage is turned on again only after a read and clear cycle.

- In case of UV, the fault SPI bit is set and the FAULT pin is asserted. The rail is not turned off.

- In case of OC, after 4 ms, the SPI register fault bit is set and VREF turns off. The FAULT pin is asserted. VREF turns on again when OC is removed.

### 4.4 Wake up pin (WKUP)

The maximum voltage this WKUP pin can sustain is limited to 40 V.

A higher voltage compliance level in the application can be achieved by applying an external series resistor between the WKUP pin and the external wake-up signal.

When the device is in STANDBY mode, it can be activated by a voltage above  $V_{WAKE\_ON}$  threshold, with a minimum duration of  $t_{WAKE\_FILTER}$ .

The device can be moved to STANDBY mode applying a voltage below  $V_{WAKE\_OFF}$  threshold, with a minimum pulse width of  $t_{WAKE\_FILTER}$  and waiting  $T_{PHOLD}$  timer. PHOLD timer starts after the detection of  $t_{WAKE\_FILTER}$ .

DS14755 - Rev 1 page 16/49

### 4.5 Reset and fault

In ACTIVE mode, a reset signal is generated by SPSA068 at NRST pin in case of:

- BUCK UV (can be disabled by NVM)

- BUCK OV (can be disabled by NVM)

- PGND loss on BUCK regulator by PGND comparator or BUCKUV L threshold

- Watchdog failure (can be disabled by NVM)

- CLOCK stuck fault

The minimum pulse of NRST assertion lasts  $T_{NRST}$ .

Figure 6. Signal contribution to the reset

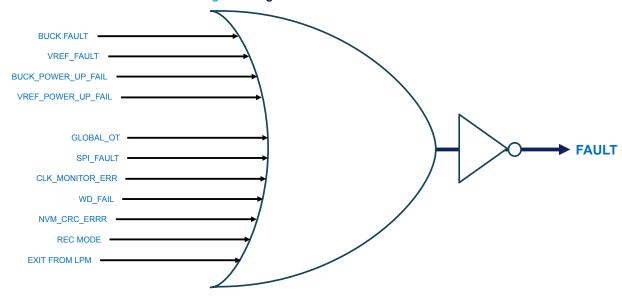

A FAULT signal, active low, is generated when one of the following events occurs:

- BUCK regulator fault

- V<sub>REF</sub> fault

- OT warning and shutdown

- SPI communication error (CRC)

- Powerup fault. It is an error generated during the power-up phase in case the regulators cannot complete

their own power-up phase within T<sub>POWER\_ON\_TIMEOUT</sub>

- Digital bist error

- WD fail

- Clock monitor error

- Device is in REC mode

Furthermore, a FAULT signal is also generated after the LPM exit procedure is completed (toggling of T<sub>FAULT</sub>).

DS14755 - Rev 1 page 17/49

Figure 7. Signal contribution to the fault

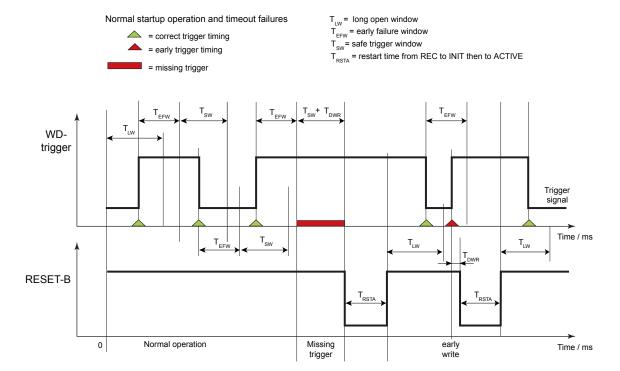

### 4.6 Configurable watchdog and reset

During normal operation, the watchdog monitors the microcontroller within a programmable trigger cycle. When the device is in ACTIVE mode, which means the power-up phase has been correctly performed and NRST signal has been released, the watchdog is started with a timeout (long open window TLW) to allow the microcontroller to run its own setup and then to start the window watchdog by setting an inner signal TRIG = 1. Subsequently, the microcontroller has to serve the watchdog by providing the watchdog trigger bit TRIG within the safe trigger area TSW. The trigger time is configurable by SPI. A correct watchdog trigger signal immediately starts the next cycle. A wrong watchdog trigger causes a watchdog failure.

WDI signal can be ignored, by setting a NVM bit, and SPI can be used as watchdog: in this case, a specific SPI register must be accessed and toggled by SPI within the watchdog window. If the register is not refreshed at the right time, a watchdog failure happens.

A 0 is written to the watchdog register at startup or when the device is reset. Via SPI it is necessary to continue to toggle the bit in the register within the watchdog window.

In case of a watchdog failure, a NRST is always asserted, and the device goes to REC mode or keeps in ACTIVE mode depending on WD\_REC\_en NVM configuration.

If NVM\_WD\_REC\_en = 1 the device goes to REC mode in case of WD failure, and the WD is not more sensed until the ACTIVE mode is reached again.

If NVM\_WD\_REC\_en = 0, the device keeps the ACTIVE mode in case of WD failure. It remains active in Long open window, but NRST asserts a small pulse (typ 8  $\mu$ s). If SPI\_WD\_REC\_en = 1, the device behavior is the same as NVM\_WD\_REC\_en = 1, but it expects to receive the WD signal from the SPI.

Configuration with NVM\_WD\_REC\_en = 0 is useful if voltages should be immediately active to initialize the system, regardless of the WD signal.

The following picture illustrates the watchdog behavior. The WD works in ACTIVE mode and if enabled at register level.

DS14755 - Rev 1 page 18/49

Figure 8. Watchdog behavior

WD working

Long open window

WD stop

Trig = 1

Window mode

Proper trigger in window mode

The watchdog trigger time is configured through the SPI. The change of this time is not limited to the long open window. It can be changed also in "Window mode" state. However, it is suggested to write these bits only during the long window, to avoid watchdog failures. Besides, the first trigger time should be < TLW (160 ms), after that, next trigger should happen between (previous \_Trigger\_ time + TSW\_min) and (previous \_Trigger\_ time + TSW\_max).

Figure 9. Watchdog timing if WD\_REC\_en = 1

DS14755 - Rev 1 page 19/49

Normal startup operation and timeout failures  $T_{LW}$  = long open window T<sub>EFW</sub> = early failure window = correct trigger timing T<sub>sw</sub>= safe trigger window = early trigger timing  $T_{RSTT}$  = restart time longer than 1.5  $\mu$ s = missing trigger T<sub>EFW</sub> WDtrigger Trigger signal Time / ms  $\mathsf{T}_{\mathsf{sw}}$ T<sub>LW</sub> T<sub>LW</sub> **RESET-B** T<sub>RSTT</sub> 0 Normal operation Missing early write Time / ms trigger

Figure 10. Watchdog timing if WD\_REC\_en = 0

The WD can be temporarily disabled by keeping the DBUG pin high. This allows software debugging in the development environment.

DS14755 - Rev 1 page 20/49

### 4.7 Spread spectrum

SPSA068 features a triangular-modulation spread spectrum for 2.4 MHz at the modulation frequency of  $F_{spread\_mod\_2.4}$ , while for 400 kHz at  $F_{spread\_mod\_400}$ . The modulation frequency can be fixed or variable according to the SPI configuration: BUCK\_SS\_MAIN\_FIXED\_FMODE and BUCK\_SS\_AUX\_FIXED\_FMODE. In case of BUCK\_SS\_MAIN\_FIXED\_FMODE = '0', the  $F_{spread\_mod\_2.4}$  is randomically changed in a range of  $F_{spread\_mod\_rand\_2.4}$ , while in case of BUCK\_SS\_AUX\_FIXED\_FMODE = '0' the  $F_{spread\_mod\_400}$  is changed in a range of  $F_{spread\_mod\_rand\_400}$ , to avoid emissions in the audio band, and it is superposed to a higher frequency modulation of lower amplitude to ensure effectiveness in the whole frequency spectrum. Both spread spectrum's can be independently disabled by SPI.

### 4.8 Undervoltage and overvoltage (power-good)

Output voltages are monitored: undervoltage and overvoltage information is provided through SPI.

One SPI bit allows to select between two threshold options for each regulator.

The power on timeout for every regulator is a signal that is set to '1' if BUCK or VREF are not switched on after 3 ms. If the timeout expires, the relative power on the timeout is set and the device moves to REC state.

### 4.9 Temperature control

The PMIC has a thermal sensor with ADC, positioned at the center of the chip to continuously monitor the temperature of the die.

In case the temperature reaches the thermal shutdown threshold, the outputs are shut down and the device moves in REC state.

A temperature warning is signaled by the FAULT pin, written in a register and read out by SPI.

Temperature information is updated every 500 µs and it is coded in the digital domain in unsigned 8 bit word provided into a SPI register.

Temperature is calculated with the following formula:

Temperature

$$[^{\circ}C] = 1.3706 \times CHIP\_TEMP < 15:8 > -77.402$$

(1)

DS14755 - Rev 1 page 21/49

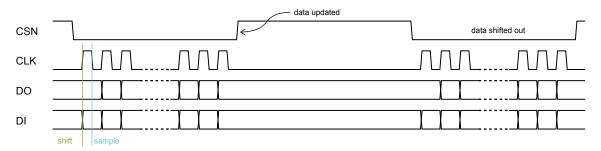

## SPI format and register mapping

A 32-bit SPI bus is used for bidirectional communication with the microcontroller and for functional and test purpose.

A write operation leads to a modification of the addressed data by the payload if a write access is allowed (for example control register, valid data). A read operation (based on previous communication request) shifts out the data present in the addressed register (out of frame data exchange protocol).

A read and clear operation will lead to a clear of addressed status bits. The bits to be cleared are defined first by payload bits set to 0.

20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 Bit 31 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 22 21 NVM DΙ RW **ADDRESS DATA WRITE** CRC CODE SPI DO **IERR** ADDRESS FDBACK DATA READ CRC

Table 6, SPI DI and SPI DO frames

Logic content is reset only by POR activation, once VBAT1 falls below the POR threshold. WD\_TWIN is not reset by a reset command (or a WD fail) regardless of 'WD\_REC\_en' value.

**FRR**

- Bit 31: R/W flag. To select read (0) or write (1) operation

- Bit 30-23: SPI register address

- Bit 22-21: NVM CODE:

- 00 NVM NOP (NVM code/address error: in case the address field is relative to NVM operation, SPI ERR is set)

- 01 NVM SOFT TRIM (NVM code/address error: in case the address field is not relative to NVM operation, SPI ERR is set)

- 10 NVM WRITE (NVM code/address error: in case the address field is not relative to NVM operation, SPI ERR is set)

- 11 NVM NOP (NVM code/address error: in case the address field is relative to NVM operation, SPI ERR is set)

- Bit 20-5: Data to be written at a selected address

- Bit 4-0: CRC code

#### DO stream:

- Bit 31: Previous SPI communication error (frame length error, CRC error, MOSI stuck error, address error, NVM code/address error)

- Bit 30:NRST

- Bit 29: FAULT

- Bit 28:21: SPI register address (related to the previous transmission)

- Bit 20-5: Data read at selected address (related to previous transmission)

- Bit 4-0: CRC code

Note:

Bit 29 and bit 30 reflect the current status of NRST pin and FAULT pin. Every time the relevant SPI register is accessed, an internal register will sample the current status of RSTB and FAULT pins, store them, then shift them out on SPI DO frame at the next SPI access.

DS14755 - Rev 1 page 22/49

500

25

ns

ns

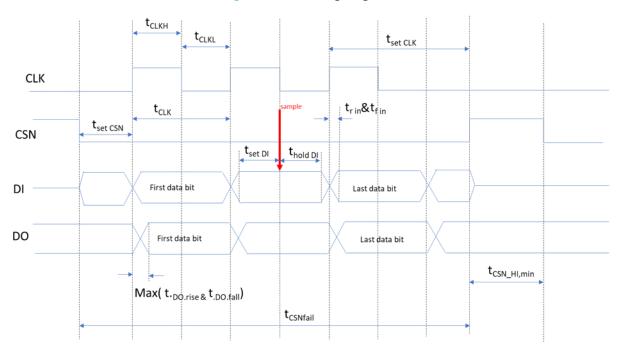

DO is sampled by the microcontroller on CLK falling edge. DI is sampled by device on CLK falling edge. In case of writing operation selected, internal register is updated at CSN rising edge.

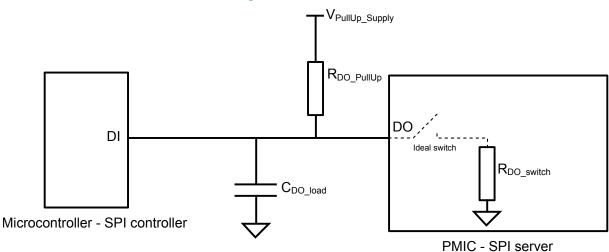

DO is reliable only when the BUCK is active (only in ACTIVE state), otherwise the internal pull-up is not supplied.

CSN Write register X, data Y Register X shifted out (data Y)

DDO

DI

RW = 1

RW = 0

RW = 0