# Low Skew, Low Additive Jitter 8 Output HCSL/LVDS/ LVPECL Fanout Buffer with Per Enable Control

#### **Features**

- 3 to 1 Input Multiplexer: Two Inputs Accept Any Differential (LVPECL, HCSL, LVDS, SSTL, CML, LVCMOS) or a Single-Ended Signal and the Third Input Accepts a Crystal or a Single-Ended Signal

- · Eight Differential HCSL/LVDS/LVPECL Outputs

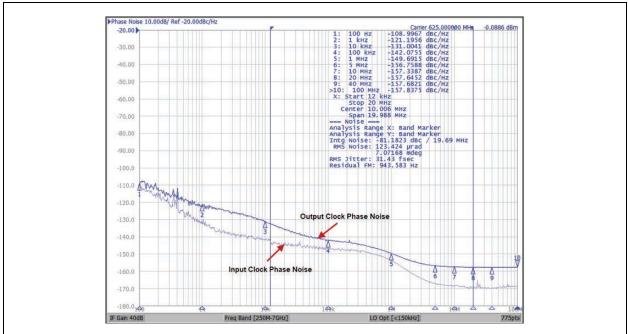

- Ultra-Low Additive Jitter: 24 fs (Integration Band: 12 kHz to 20 MHz at 625 MHz Clock Frequency)

- Supports Clock Frequencies from 0 to 1.5 GHz

- Supports 2.5V or 3.3V Power Supplies on HCSL/ LVDS/LVPECL Outputs

- Embedded Low Drop Out (LDO) Voltage Regulator Provides Superior Power Supply Noise Rejection

- · Maximum Output to Output Skew of 50 ps

- Device Controlled Via I<sup>2</sup>C or Hardware Control Pins

- · Factory Configurable Default Settings via OTP

- · Transparent for Spread Spectrum Clock

#### **Applications**

- PCIe Gen1/2/3/4/5 Clock Distribution

- Wired Communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC

- · General Purpose Clock Distribution

- · Low-Jitter Clock Trees

- Logic Translation

- · Clock and Data Signal Restoration

- · Wireless Communications

- High Performance Microprocessor Clock Distribution

- · Test Equipment

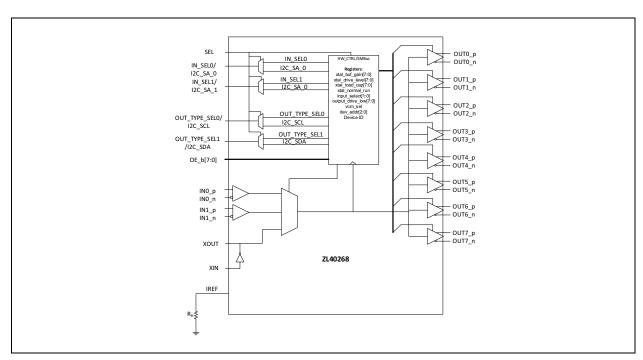

FIGURE 0-1: Functional Block Diagram.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **TABLE OF CONTENTS**

| 1.0 "Pin Description And Configuration"        | 6  |

|------------------------------------------------|----|

| 2.0 "Functional Description"                   | 11 |

| 2.1 "Clock Inputs"                             |    |

| 2.2 "Clock Outputs"                            |    |

| 2.3 "Crystal Oscillator Input"                 |    |

| 2.4 "Termination of Unused Inputs and Outputs" |    |

| 2.5 "Power Consumption"                        | 15 |

| 2.6 "Power Supply Filtering"                   | 16 |

| 2.7 "Power Supplies and Power-up Sequence"     |    |

| 2.8 "Host Interface"                           | 16 |

| 2.8.1 "Hardware Control Mode"                  |    |

| 2.8.2 "I2C Bus Control Mode"                   | 18 |

| 2.9 "I2C Bus Byte Read/Write"                  | 19 |

| 2.10 "I2C Bus Burst Read/Write"                | 19 |

| 2.11 "Typical Phase Noise Characteristics"     | 21 |

| 3.0 "Register Map"                             | 23 |

| 4.0 "Electrical Characteristics"               | 29 |

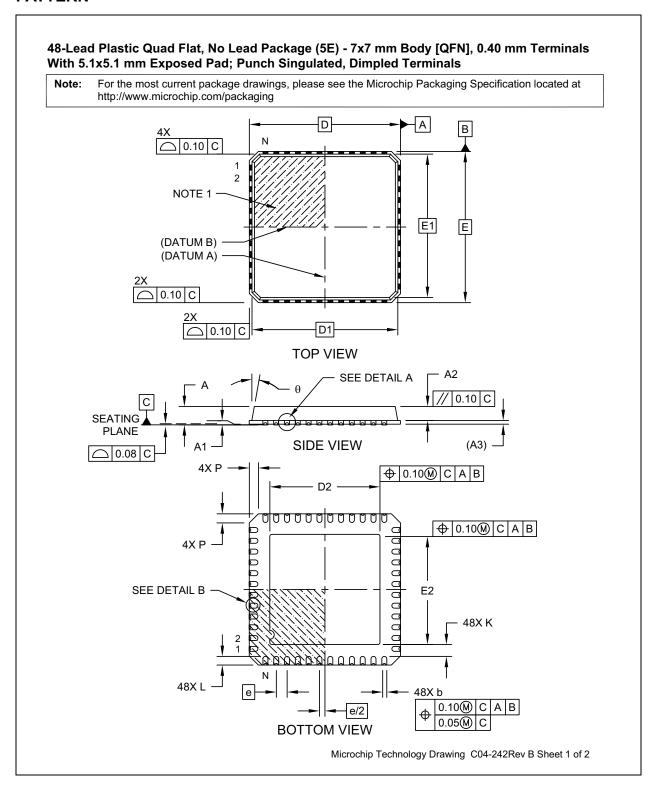

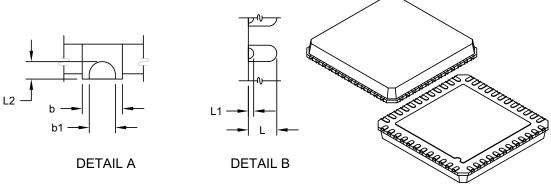

| 5.0 "Package Outline"                          | 47 |

| 5.1 "Package Marking Information"              |    |

| Appendix A: "Data Sheet Revision History"      |    |

| "Product Identification System"                | 53 |

# **List of Figures**

| FIGURE 0-1: "Functional Block Diagram."                                                           | 1  |

|---------------------------------------------------------------------------------------------------|----|

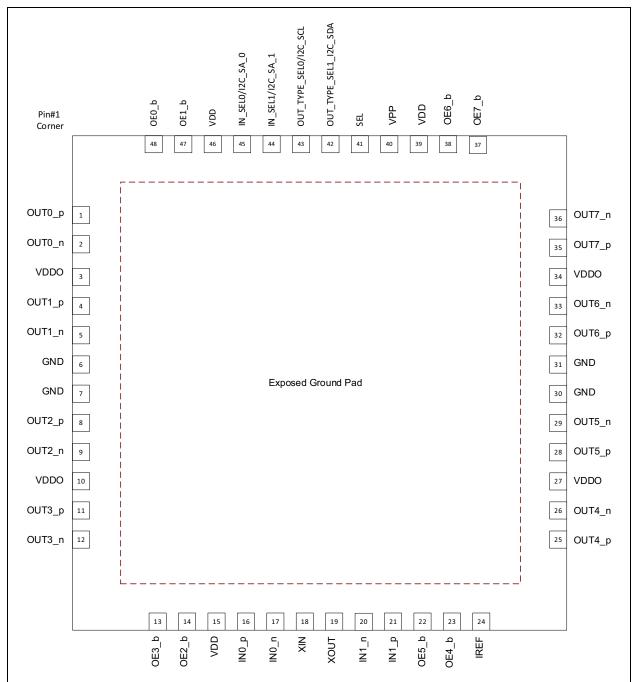

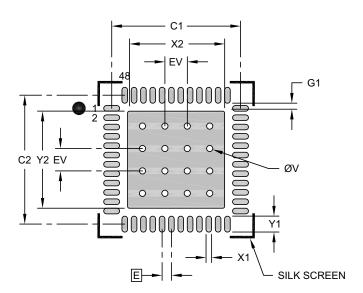

| FIGURE 1-1: "48-Lead 7 mm x 7 mm QFN."                                                            | 6  |

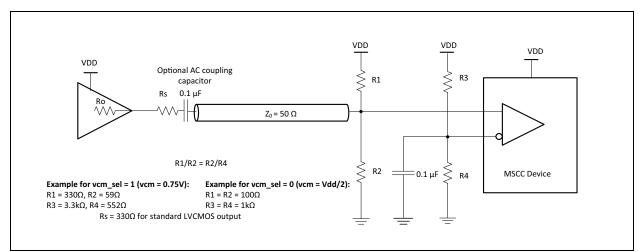

| FIGURE 2-1: "Input Driven by a Single-Ended Output for vcm_sel = 0 and 1."                        | 11 |

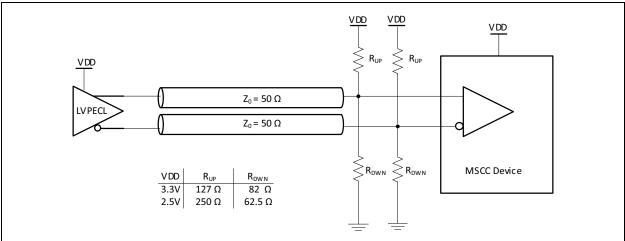

| FIGURE 2-2: "Input Driven by DC-Coupled LVPECL Output for vcm_sel = 0."                           | 12 |

| FIGURE 2-3: "Input Driven by DC-Coupled LVPECL Output for vcm_sel = 0 (Alternative Termination)." | 12 |

| FIGURE 2-4: "Input Driven by AC-Coupled LVPECL Output for vcm_sel = 0 and 1."                     |    |

| FIGURE 2-5: "Input Driven by HCSL Output for vcm_sel = 1."                                        | 13 |

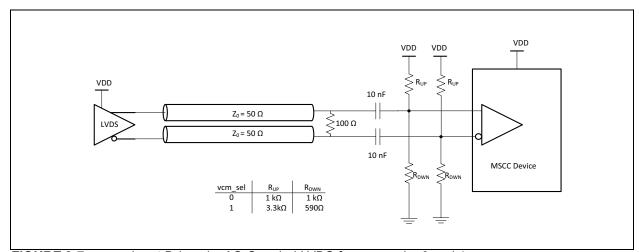

| FIGURE 2-6: "Input Driven by LVDS Output for vcm_sel = 0."                                        | 13 |

| FIGURE 2-7: "Input Driven by AC-Coupled LVDS for vcm_sel = 0 and 1."                              | 13 |

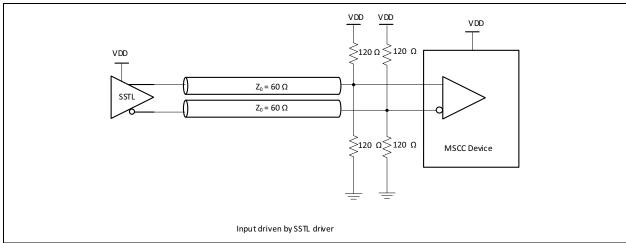

| FIGURE 2-8: "Input Driven by an SSTL Output for vcm_sel = 1."                                     |    |

| FIGURE 2-9: "Driving A Load Via Transformer."                                                     |    |

| FIGURE 2-10: "Crystal Oscillator Circuit in Hardware Controlled Mode."                            | 15 |

| FIGURE 2-11: "Power Supply Filtering."                                                            |    |

| FIGURE 2-12: "Output Disable."                                                                    | 17 |

| FIGURE 2-13: "Output Enable."                                                                     | 18 |

| FIGURE 2-14: "I2C Bus Client Interface."                                                          | 18 |

| FIGURE 2-15: "I2C Bus Byte Read."                                                                 | 19 |

| FIGURE 2-16: "I2C Bus Byte Write."                                                                | 19 |

| FIGURE 2-17: "I2C Bus Burst Read."                                                                | 20 |

| FIGURE 2-18: "I2C Bus Burst Write."                                                               | 20 |

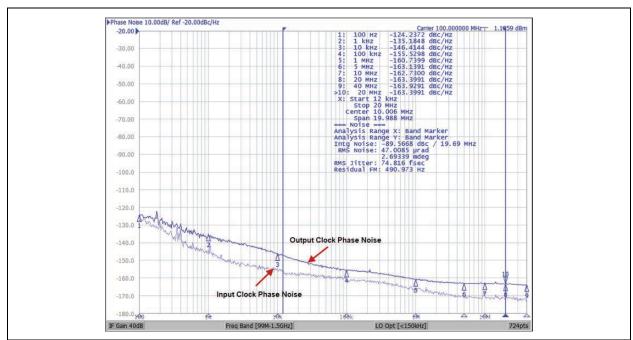

| FIGURE 2-19: "100 MHz HCSL Output Phase Noise."                                                   | 21 |

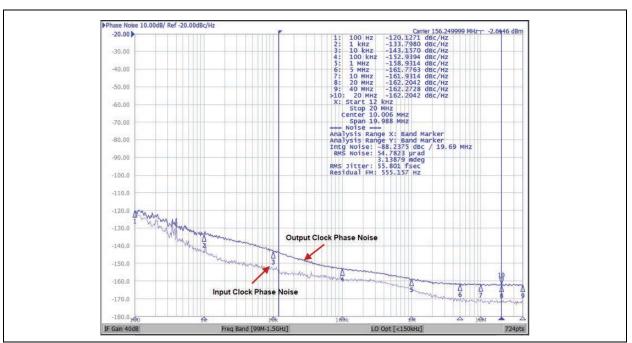

| FIGURE 2-20: "156.25MHz LVDS Output Phase Noise."                                                 | 21 |

| FIGURE 2-21: "625 MHz LVPECL Output Phase Noise."                                                 | 22 |

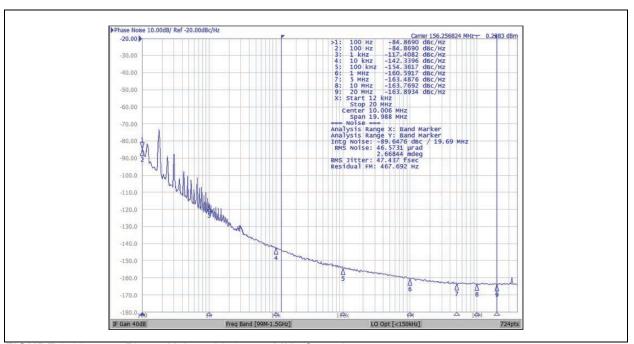

| FIGURE 2-22: "Phase Noise with 156.25MHz Crystal."                                                |    |

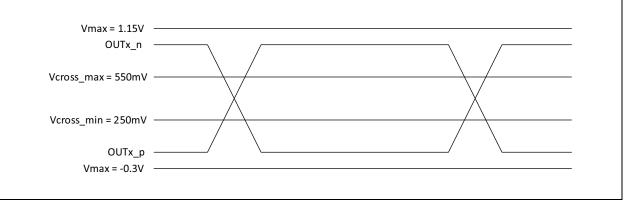

| FIGURE 4-1: "Single-Ended Measurement Points for Absolute Cross Point and Swing."                 | 39 |

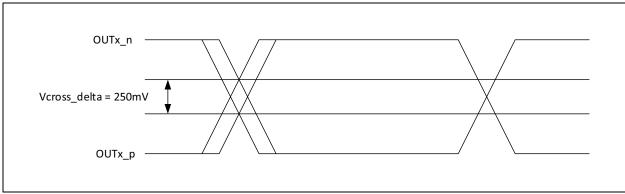

| FIGURE 4-2: "Single-Ended Measurement Points for Delta Cross Point."                              |    |

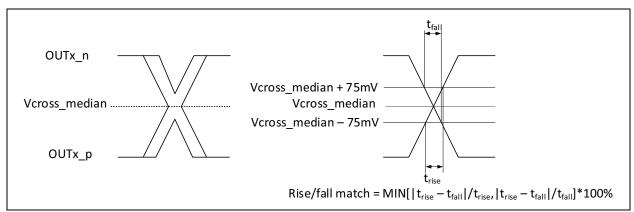

| FIGURE 4-3: "Single-Ended Measurement Points for Rise and Fall Time Matching."                    | 39 |

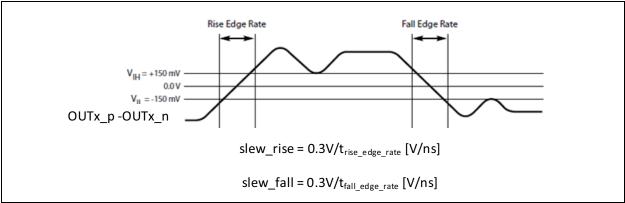

| FIGURE 4-4: "Differential Measurement Points for Rise and Fall Time."                             | 40 |

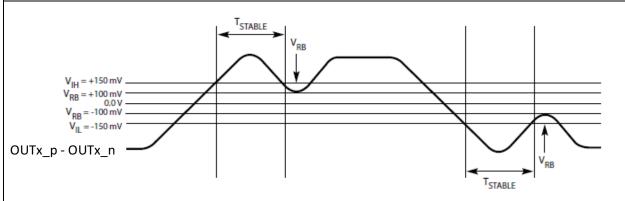

| FIGURE 4-5: "Differential Measurement Points for Ringback."                                       | 40 |

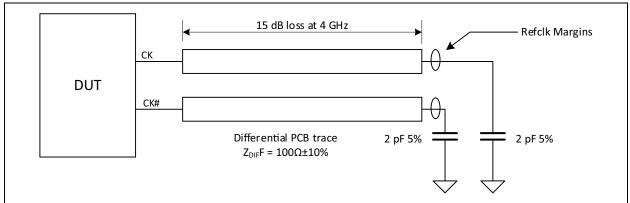

| FIGURE 4-6: "PCIe Test Circuit."                                                                  | 40 |

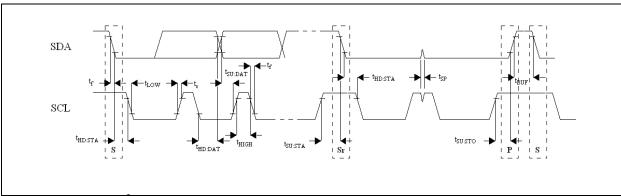

| FIGURE 4-7: "I2C Bus Timing"                                                                      | 45 |

## **List of Tables**

| TABLE 1-1: "Pin Description"                                                          | 7  |

|---------------------------------------------------------------------------------------|----|

| TABLE 2-1: "Input Clock Selection"                                                    | 17 |

| TABLE 2-2: "Output Type Selection"                                                    | 17 |

| TABLE 2-3: "I2C Bus Address Table"                                                    | 18 |

| TABLE 3-1: "Register Map"                                                             | 23 |

| TABLE 3-2: "0x00 XTALBG-XTAL Buffer Gain"                                             |    |

| TABLE 3-3: "0x01 XTALDL - XTAL Drive Level"                                           | 24 |

| TABLE 3-4: "0x02 XTALLC - XTAL Load Capacitance"                                      | 24 |

| TABLE 3-5: "0X03 XTALNR - XTAL Normal Run"                                            | 25 |

| TABLE 3-6: "0X04 OUTLOWALL - Output Low All"                                          |    |

| TABLE 3-7: "0X05 INSEL - Input Select Register"                                       | 25 |

| TABLE 3-8: "0X07 DRVTYPE0 - (Output Type Select 0 to 3)"                              | 26 |

| TABLE 3-9: "0X08 DRVTYPE1 - Output Type Select (Outputs 4 to 7)"                      | 26 |

| TABLE 3-10: "0X09 DRVTYPE2 - Output Type Select (Outputs 8 to 11)"                    | 26 |

| TABLE 3-11: "0X0A OUTLOW0 - Output Drive Low (Outputs 0 to 7)"                        | 26 |

| TABLE 3-12: "0X0B OUTLOW1 - Output Drive Low (Outputs 8 TO 11)"                       | 27 |

| TABLE 3-13: "0X0C COMMODSEL - Common Mode Select"                                     | 27 |

| TABLE 3-14: "0X0E DEVADDR - I2C Bus Client Device Address"                            | 28 |

| TABLE 3-15: "0X11 DEVID - Device Modification"                                        | 28 |

| TABLE 4-1: "Absolute Maximum Ratings"                                                 | 29 |

| TABLE 4-2: "Operating Ratings"                                                        | 29 |

| TABLE 4-3: "Current Consumption"                                                      | 29 |

| TABLE 4-4: "Input Characteristics"                                                    |    |

| TABLE 4-5: "Crystal Oscillator Characteristics"                                       | 31 |

| TABLE 4-6: "Power Supply Rejection Ratio for VDD = VDDO = 3.3V"                       |    |

| TABLE 4-7: "Power Supply Rejection Ratio for VDD = VDDO = 2.5V"                       | 32 |

| TABLE 4-8: "LVPECL Output Characteristics for VDDO = 3.3V"                            | 32 |

| TABLE 4-9: "LVPECL Output Characteristics for VDDO = 2.5V"                            | 33 |

| TABLE 4-10: "LVDS Output Characteristics for VDDO = 3.3V"                             | 34 |

| TABLE 4-11: "LVDS Output Characteristics for VDDO = 2.5V"                             |    |

| TABLE 4-12: "HCSL Outputs (PCIe Electrical Characteristics) for VDDO = 3.3V and 2.5V" | 36 |

| TABLE 4-13: "HCSL (PCIe) Jitter Performance for VDDO = 3.3V"                          | 37 |

| TABLE 4-14: "HCSL (PCIe) Jitter Performance for VDDO = 2.5V"                          | 38 |

| TABLE 4-15: "LVPECL Output Phase Noise with 25 MHz XTAL"                              |    |

| TABLE 4-16: "LVDS Output Phase Noise with 25 MHz XTAL"                                | 41 |

| TABLE 4-17: "HCSL Output Phase Noise with 25 MHz XTAL"                                | 42 |

| TABLE 4-18: "LVDS Output Phase Noise with 125 MHz XTAL"                               | 42 |

| TABLE 4-19: "HCSL Output Phase Noise with 125 MHz XTAL"                               | 43 |

| TABLE 4-20: "LVPECL Output Phase Noise with 156.25 MHz XTAL"                          |    |

| TABLE 4-21: "LVDS Output Phase Noise with 156.25 MHz XTAL"                            | 44 |

| TABLE 4-22: "HCSL Output Phase Noise with 156.25 MHz XTAL"                            | 44 |

|                                                                                       | ΔF |

### 1.0 PIN DESCRIPTION AND CONFIGURATION

**FIGURE 1-1:** 48-Lead 7 mm x 7 mm QFN.

TABLE 1-1: PIN DESCRIPTION

| Pin<br>Number   | Pin Name                          | Type<br>(Note 1-1)   |                                                                                                                                                                                                                                                                                                                                               | Descri             | ption                                         |

|-----------------|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------|

| Input Reference |                                   |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 16              | IN0_p                             | I <sub>APD</sub>     | Differential/Single                                                                                                                                                                                                                                                                                                                           | Ended Reference    | es 0 and 1                                    |

| 17              | IN0_n                             | I <sub>APU/APD</sub> | Input froguency                                                                                                                                                                                                                                                                                                                               | ao 0 Uz to 4 E OU  | _                                             |

| 21              | IN1_p                             | I <sub>APD</sub>     | Input frequency ran                                                                                                                                                                                                                                                                                                                           | ge u Hz to 1.5 GH. | Ζ.                                            |

| 20              | IN1_n                             | I <sub>APU/APD</sub> | Non-inverting inputs (_p) are pulled down with internal 30 k $\Omega$ pull-down resistors. Inverting inputs (_n) are pulled up and pulled down with 60 k $\Omega$ internal resistors (30 k $\Omega$ equivalent) to keep inverting input voltages at VDD/2 when inverting inputs are left floating (device fed with a single ended reference). |                    |                                               |

| Output Cl       | ocks                              |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 1               | OUT0_p                            |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 2               | OUT0_n                            |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 4               | OUT1_p                            |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 5               | OUT1_n                            |                      | Ultra-Low Additive                                                                                                                                                                                                                                                                                                                            | Jitter Differentia | I LVPECL/HCSL/LVDS Outputs                    |

| 8               | OUT2_p                            |                      | 0 to 7                                                                                                                                                                                                                                                                                                                                        |                    | •                                             |

| 9               | OUT2_n                            |                      | Outrout from success of the                                                                                                                                                                                                                                                                                                                   |                    |                                               |

| 11              | OUT3_p                            |                      | Output frequency ra                                                                                                                                                                                                                                                                                                                           | inge 0 to 1.5 GHZ  |                                               |

| 12              | OUT3_n                            | 0                    | In I <sup>2</sup> C bus controlled mode (SEL pin pulled high on the power up) type (LVPECL/HCSL/LVDS/High-Z) of each output is programmable via I <sup>2</sup> C                                                                                                                                                                              |                    | oulled high on the power up) type             |

| 25              | OUT4_p                            | ] 0                  |                                                                                                                                                                                                                                                                                                                                               |                    | n output is programmable via I <sup>2</sup> C |

| 26              | OUT4_n                            |                      | Bus                                                                                                                                                                                                                                                                                                                                           |                    |                                               |

| 28              | OUT5_p                            |                      | In Hardware control                                                                                                                                                                                                                                                                                                                           | mode (SEL pin pu   | ılled low on the power up) type               |

| 29              | OUT5_n                            |                      | (LVPECL/HCSL/LVI                                                                                                                                                                                                                                                                                                                              | DS/High-Z) of each | n output is controlled via                    |

| 32              | OUT6_p                            |                      | OUT_TYPE_SEL0/                                                                                                                                                                                                                                                                                                                                | 1 pins.            |                                               |

| 33              | OUT6_n                            |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 35              | OUT7_p                            |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

| 36              | OUT7_n                            |                      |                                                                                                                                                                                                                                                                                                                                               |                    |                                               |

|                 | IN SEL0                           |                      | Input Select 0 or I <sup>2</sup> C Address When SEL pin is low this pin is Input Select 0 hardware control input. When SEL pin is high this pin together with pin 44 provides address for I2C Bus. This pin is pulled down with $300~k\Omega$ resistor.                                                                                       |                    |                                               |

| 45              | /I <sup>2</sup> C_SA_0            | I <sub>PD</sub>      | IN_SEL1                                                                                                                                                                                                                                                                                                                                       | IN_SEL0            | OUTN                                          |

|                 | _ <b>_</b>                        |                      | 0                                                                                                                                                                                                                                                                                                                                             | 0                  | Input 0 (IN0)                                 |

|                 |                                   |                      | 0                                                                                                                                                                                                                                                                                                                                             | 1                  | Input 1(IN1)                                  |

|                 |                                   |                      | 1 0 Crystal Oscillator or overdr                                                                                                                                                                                                                                                                                                              |                    | Crystal Oscillator or overdrive               |

|                 |                                   |                      | 1                                                                                                                                                                                                                                                                                                                                             | 1                  | Crystal Bypass                                |

| 44              | IN_SEL1<br>/I <sup>2</sup> C_SA_1 | I <sub>PD</sub>      | Input Select 1 or Serial Interface Input When SEL pin is low this pin is Input Select 1 hardware control pin. When SEL pin is high this pin together with pin 45 provides address for I <sup>2</sup> C Bus. This pin is pull-down with 300 k $\Omega$ resistor.                                                                               |                    |                                               |

TABLE 1-1: PIN DESCRIPTION (CONTINUED)

| Pin<br>Number | Pin Name                                                            | Type<br>(Note 1-1) | (CONTINUED)  Description                                                                                                                                                                                                                                                             |                                                                                          |                              |  |

|---------------|---------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------|--|

|               |                                                                     |                    | Output Signal Type or I2C Bus Clock When SEL pin is low this pin and pin 42 selects output type.                                                                                                                                                                                     |                                                                                          |                              |  |

|               |                                                                     |                    | OUT_TYPE_SEL1                                                                                                                                                                                                                                                                        | OUT_TYPE_SEL0                                                                            | Output [7:0]                 |  |

|               | OUT_TYPE                                                            |                    | 0                                                                                                                                                                                                                                                                                    | 0                                                                                        | HCSL                         |  |

| 43            | SEL0/I <sup>2</sup> C_SCL                                           | I/O                | 0 1 LVDS                                                                                                                                                                                                                                                                             |                                                                                          |                              |  |

|               |                                                                     |                    | 1                                                                                                                                                                                                                                                                                    | 0                                                                                        | LVPECL                       |  |

|               |                                                                     |                    | 1 High-Z (Disabled)                                                                                                                                                                                                                                                                  |                                                                                          |                              |  |

|               |                                                                     |                    |                                                                                                                                                                                                                                                                                      | h this pin is I <sup>2</sup> C Bus (                                                     |                              |  |

| 42            | OUT_TYPE<br>SEL1/I <sup>2</sup> C_SDA                               | I/O                | When SEL pin is lov                                                                                                                                                                                                                                                                  | e or I <sup>2</sup> C Bus I/O Data<br>this pin and pin 43 s<br>th this pin is an I/O pin |                              |  |

| 48            | OE0_b                                                               |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 47            | OE1_b                                                               |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 14            | OE2_b                                                               |                    | Output Enable Cor                                                                                                                                                                                                                                                                    | itrol                                                                                    |                              |  |

| 13            | OE3_b                                                               |                    |                                                                                                                                                                                                                                                                                      | the output n where n                                                                     | = {0,,7} is active.          |  |

| 23            | OE4_b                                                               | I <sub>PD</sub>    | When OEn_b is high the output is disabled (High-Z) OEn_b pins are pulled-down with 300 k $\Omega$ resistor.                                                                                                                                                                          |                                                                                          |                              |  |

| 22            | OE5_b                                                               |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 38            | OE6_b                                                               |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 37            | OE7_b                                                               |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| Crystal O     | scillator                                                           |                    | 1                                                                                                                                                                                                                                                                                    |                                                                                          |                              |  |

| 18            | XIN                                                                 | I                  | Crystal Oscillator Input or crystal bypass mode or crystal overdrive mode  If crystal circuit is not used pull-down this pin or connect it to the ground.                                                                                                                            |                                                                                          |                              |  |

| 19            | XOUT                                                                | 0                  | Crystal Oscillator Output                                                                                                                                                                                                                                                            |                                                                                          |                              |  |

| Hardware      | /l <sup>2</sup> C Bus Control                                       | Selection          | -                                                                                                                                                                                                                                                                                    | •                                                                                        |                              |  |

| 41            | SEL                                                                 | I                  | Select control.  When this pin is low, the device is controlled via hardware pins, IN_SEL0/1 and OE.  When this pin is high, the device is controlled via I <sup>2</sup> C Bus port.  Any change of SEL pin value requires power cycle. Hence, SEL pin cannot be changed on the fly. |                                                                                          |                              |  |

| 24            | IREF                                                                | 0                  | Output current select. Connect this pin to the ground via resistor R: HCSL/LVDS/LVPECL for $100\Omega$ differential transmission line: R = $536\Omega$ HCSL for $85\Omega$ differential transmission line: R = $422\Omega$                                                           |                                                                                          |                              |  |

| Power an      | Power and Ground                                                    |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 15            |                                                                     |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 39            | VDD                                                                 | Р                  | Positive Supply Voltage Connect to 3.3V or 2.5V supply                                                                                                                                                                                                                               |                                                                                          |                              |  |

| 46            | ]                                                                   |                    |                                                                                                                                                                                                                                                                                      | -                                                                                        | , . <del>.</del>             |  |

| 3             |                                                                     |                    |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 10            | 10 Positive Supply Voltage for Differential Outputs Connect to 3.3\ |                    | utputs Connect to 3.3V or 2.5V                                                                                                                                                                                                                                                       |                                                                                          |                              |  |

|               | VDDO                                                                | Р                  |                                                                                                                                                                                                                                                                                      |                                                                                          |                              |  |

| 27            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                               | •                  | power supply. These                                                                                                                                                                                                                                                                  | e pins power up differ                                                                   | ential outputs OUT[11:0]_p/n |  |

TABLE 1-1: PIN DESCRIPTION (CONTINUED)

| Pin<br>Number | Pin Name | Type<br>(Note 1-1) | Description                                                                                                                                              |

|---------------|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40            | VPP      | Р                  | Positive Supply Voltage for programming OTP memory This pin is used for generating custom configurations on ATE. Connect to ground for normal operation. |

| ePad          | GND      | Р                  | Ground Connect to the ground                                                                                                                             |

**Note 1-1** All device inputs and outputs are LVPECL unless described otherwise. The Type column uses the following symbols:

I - Input,

$I_{PU}$  – Input with 300 k $\Omega$  internal pull-up resistor,

$I_{PD}$  – Input with 300 k $\Omega$  internal pull-down resistor,

$I_{\mbox{\footnotesize APU}}$  - Input with 31 k $\Omega$  internal pull-up resistor,

$I_{\mbox{\footnotesize{APD}}}$  - Input with 30 k $\Omega$  internal pull-down resistor,

$I_{APU/APD}$  – input biased to VDD/2 with 60 k $\Omega$  internal pull-up and pull-down resistors

(30 kΩ equivalent),

O – Output,

I/O<sub>OD</sub> - Input/Open Drain Output pin,

NC - No connect,

P - Power supply pin

| 7 | I 4 | A | 7 | C | 0 |

|---|-----|---|---|---|---|

|   | ᆫ华  | U | Z | O | 0 |

NOTES:

#### 2.0 FUNCTIONAL DESCRIPTION

The ZL40268 is a I<sup>2</sup>C Bus programmable or hardware pin controlled low additive jitter, low power 3 x 8 HCSL/LVDS/LVPECL fanout buffer.

Two inputs can accept signal in differential (LVPECL, SSTL, LVDS, HSTL, CML) or single ended (LVPECL or LVCMOS) format and the third input can accept a single ended signal or it can be used to build a crystal oscillator by connecting an external crystal resonator between its XIN and XOUT pins. All the other components for building crystal oscillator are built in device such as load capacitance, series and shunt resistors.

The ZL40268 has eight HCSL/LVDS/LVPECL outputs which can be powered from 3.3V or 2.5V supply. Each output can be independently enabled/disabled via OEn\_b pins or via I<sup>2</sup>C Bus. The type of each output driver can be programmed to be LVPECL, HCSL or LVDS. Hence, the device can be configured to support different signaling formats depending on the application.

The device operates from 2.5V±5% or 3.3V±5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.

### 2.1 Clock Inputs

The following blocks diagram shows how to terminate different signals fed to the ZL40268 inputs.

The device has programmable common mode input voltage. The common mode voltage can be programmed in COMMODSEL register at address 0x0C:

COMMODSEL.vcm\_sel = 1 (default) for inputs with common mode between 0 and 1V such as HCSL.

COMMODSEL.vcm sel = 0 for inputs with common mode voltage between 1V and 2V such as LVPECL and LVDS.

For devices intended to be used in hardware pin controlled mode the default common mode voltage can be changed in factory by programming OTP.

Figure 2-1 shows how to terminate a single ended output such as LVCMOS. Resistors R1 and R2 should present  $50\Omega$  equivalent resistance to the line and  $R_O$  +  $R_S$  should be  $50\Omega$  so that the transmission line is terminated at both ends with characteristic impedance. If the driving strength of the output driver is not sufficient to drive low impedance (standard LVCMOS output for example), the value of series resistor  $R_S$  should be increased. This will reduce the voltage swing at the input but this should be fine as long as the input voltage swing requirement is not violated (Table 4-4). The source resistors of Rs =  $330\Omega$  could be used for standard LVCMOS driver. This will provide 471 mV of voltage swing for 3.3V LVCMOS driver with the peak load current of  $(3.3V^*\ 0.85)^*(1/(330\Omega + 50\Omega)) = 7.3$  mA for common mode voltage biased at 0.5V. For common mode voltage of Vdd/2, the peak current will be lower.

For optimum performance both differential input pins (\_p and \_n) need to be DC biased to the same voltage. Hence, the ratio R1/R2 should be equal to the ratio R3/R4.

**FIGURE 2-1:** Input Driven by a Single-Ended Output for vcm sel = 0 and 1.

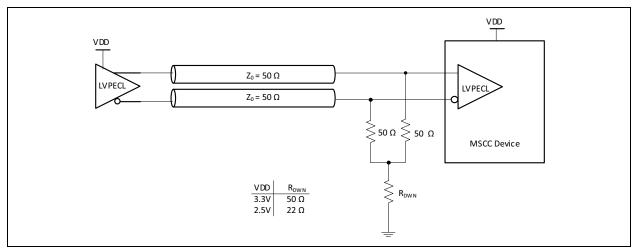

FIGURE 2-2: Input Driven by DC-Coupled LVPECL Output for vcm\_sel = 0.

FIGURE 2-3: Input Driven by DC-Coupled LVPECL Output for vcm\_sel = 0 (Alternative Termination).

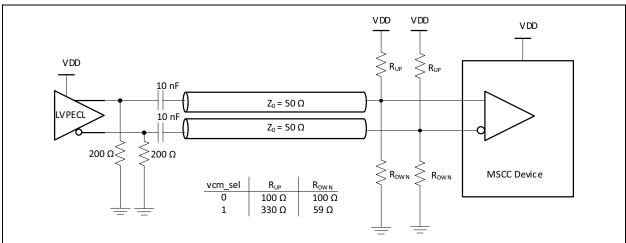

FIGURE 2-4: Input Driven by AC-Coupled LVPECL Output for vcm\_sel = 0 and 1.

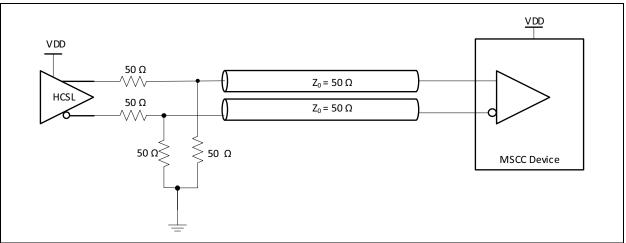

FIGURE 2-5: Input Driven by HCSL Output for vcm\_sel = 1.

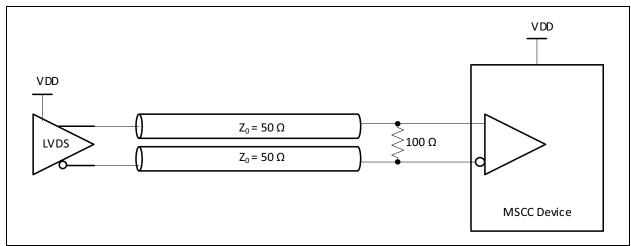

FIGURE 2-6: Input Driven by LVDS Output for vcm\_sel = 0.

FIGURE 2-7: Input Driven by AC-Coupled LVDS for vcm\_sel = 0 and 1.

FIGURE 2-8: Input Driven by an SSTL Output for vcm\_sel = 1.

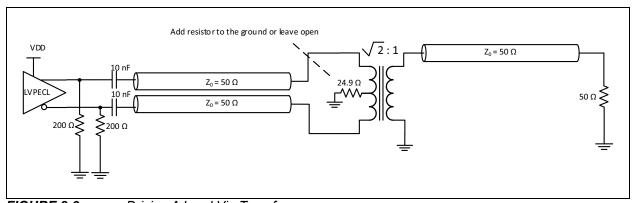

### 2.2 Clock Outputs

Differential outputs LVPECL, LVDS and HCSL should have same termination as corresponding outputs described in **Section 2.1 "Clock Inputs"**.

The device is designed to drive differential input of semiconductor devices. In applications that use a transformer to convert from the differential to the single ended output (for example driving an oscilloscope  $50\Omega$  input), a resistor larger than  $10\Omega$  should be added at the center tap of the primary winding to achieve optimum jitter performance as shown in Figure 2-9. This is to provide a nominal common mode impedance of  $10\Omega$  or higher which is typical for differential terminations.

FIGURE 2-9: Driving A Load Via Transformer.

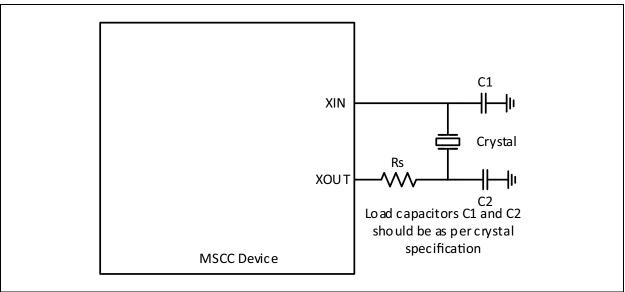

#### 2.3 Crystal Oscillator Input

The crystal oscillator circuit can work with crystal resonators from 8 MHz to 160 MHz. To be able support crystal resonators with different characteristics all internal components are programmable.

The load capacitors can be programmed from 0 to 21.75 pF (4 pF default) with resolution of 0.25 pF which not only meets load requirement for most crystal resonator but also allows for fine tuning of the crystal resonator frequency. The amplifier gain can be adjusted in five steps and series resistor can be adjusted as parallel combination of seven different resistors:  $0\Omega$ ,  $10.5\Omega$ ,  $21\Omega$ ,  $42\Omega$ ,  $84\Omega$ ,  $161\Omega$  and  $312\Omega$ .( $84\Omega$  default) Although the first resistor is  $0\Omega$  the series resistance Rs will be slightly higher than  $0\Omega$  due to parasitic resistance of the switch which connects resistor. Hence the minimum series resistance is achieved when all seven resistors are connected in parallel. The shunt resistor is fixed and its value is  $500 \text{ k}\Omega$ .

In Hardware Controlled mode the capacitive load is set at 4 pF, internal series resistance to  $84\Omega$  and they cannot be changed. For Crystal requiring higher load or series resistance additional capacitance and/or series resistance can be added externally as shown in Figure 2-10.

FIGURE 2-10: Crystal Oscillator Circuit in Hardware Controlled Mode.

### 2.4 Termination of Unused Inputs and Outputs

Unused inputs can be left unconnected or alternatively IN\_0/1 can be pulled-down by 1 k $\Omega$  resistor. Unused outputs should be left unconnected.

### 2.5 Power Consumption

The device total power consumption can be calculated as:

#### **EQUATION 2-1:**

$$P_T = P_S + P_{XTAL} + P_C + P_{O\_DIFF}$$

Where:

| $P_S = V_{DD} \times I_S$                                                                                                                                          | is core power consumed by input buffers. If XTAL is running this power should be set to zero where the static current (IS) is specified in Table 4-3.                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $P_{XTAL} = V_{DD} \times I_{DD\_XTAL}$                                                                                                                            | is core power consumption of XTAL circuit. The current of the XTAL circuit is provided in Table 4-3. If XTAL is not used, the power consumption is equal to zero.                  |

| $P_{C} = V_{DDO} \times I_{DD\_CM}$                                                                                                                                | Common output power shared among all eight outputs. The current I <sub>DD_CM</sub> is specified Table 4-3.                                                                         |

| P <sub>O_DIF</sub> = V <sub>DDO</sub> x (I <sub>DD_LVDS</sub> x N <sub>1</sub> + I <sub>DD_LVPECL</sub> x N <sub>2</sub> + I <sub>DD_HCSL</sub> x N <sub>3</sub> ) | Output power where the output currents are specified Table 4-3. N1, N2 and N3 are number of enabled LVPECL, LVDS and HSCL outputs respectively and N1+N2+N3 is less or equal to 8. |

Power dissipated inside the device can be calculated by subtracting power dissipated in termination/biasing resistors from the power consumption.

#### **EQUATION 2-2:**

$$P_D = P_T - N_1 \times P_{LVPECL} - N_2 \times P_{LVDS} - N_3 \times P_{HCSL}$$

#### Where:

N1, N2 and N3 are the number of enabled LVPECL, LVDS and HSCL outputs respectively. Since there are eight differential outputs N1 + N2 + N3 will be less or equal to 8.

| $P_{\text{LVPECL}} = (V_{\text{SW}} / 50\Omega) \times (V_{\text{SW}} + V_{\text{B}})$ | $V_{SW}$ is voltage swing of LVPECL output. $V_{B}$ is LVPECL bias voltage equal to $V_{DD}-2V$ .                                      |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| $P_{LVDS} = V_{SW} / 100\Omega$                                                        | V <sub>SW</sub> is voltage swing of LVDS output.                                                                                       |

| $P_{HCSL} = (V_{SW} / 50\Omega)^2 \times (50\Omega + 50\Omega)$                        | $V_{SW}$ is voltage swing of HCSL output. $50\Omega$ is termination resistance and $50\Omega$ is series resistance of the HCSL output. |

$V_{SW}$  is voltage swing of HCSL output.  $50\Omega$  is termination resistance and  $50\Omega$  is series resistance of the HCSL output.

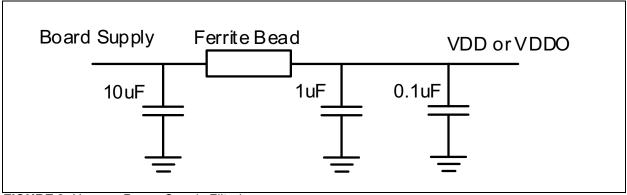

#### 2.6 Power Supply Filtering

Each power pin (VDD and VDDO) should be decoupled with 0.1  $\mu$ F capacitor with minimum equivalent series resistance (ESR) and minimum series inductance (ESL). For example, 0402 X5R Ceramic Capacitors with 6.3V minimum rating could be used. These capacitors should be placed as close as possible to the power pins. To reduce the power noise from adjacent digital components on the board each power supply could be further insulated with low resistance ferrite bead with two capacitors. The ferrite bead will also insulate adjacent component from the noise generated from the device. Figure 2-11 shows recommended decoupling for each power pin.

FIGURE 2-11: Power Supply Filtering.

### 2.7 Power Supplies and Power-up Sequence

The device has two different power supplies: VDD and VDDO which are mutually independent. Voltages supported by each of these power supplies are specified in Table 2-1.

The device is not sensitive to the power-up sequence. For example, commonly used sequence where higher voltage comes up before or at the same time as the lower voltages can be used (or any other sequence).

#### 2.8 Host Interface

ZL40268 can be controlled via hardware pins (SEL pin tied low) or via  $I^2C$  Bus (SEL pin tied high). The mode shall be selected during power up and it cannot be changed on the fly.

#### 2.8.1 HARDWARE CONTROL MODE

In this mode, ZL40268 is controlled via Input Select pins (IN\_SEL[1:0]) which select which one of three inputs is fed to outputs as shown in Table 2-1, OUT\_TYPE\_SEL[1:0] pins which select signal level (HCSL, LVDS, LVPECL or Hi-Z) and output enable pins (OE\_b) for each output as shown in Table 2-2.

All input control pins have low input threshold voltage so they can be driven from the device with low output voltage (FPGA/CPLD). Supported voltages are between 1.2V and VDD (2.5V or 3.3V).

TABLE 2-1: INPUT CLOCK SELECTION

| IN_SEL1 | IN_SEL0 | Selected Input          |

|---------|---------|-------------------------|

| 0       | 0       | IN0_p, IN0_n            |

| 0       | 1       | IN1_p, IN1_n            |

| 1       | X       | XIN (crystal input pin) |

TABLE 2-2: OUTPUT TYPE SELECTION

| OE_N_b | OUT_TYPE_SEL[1:0] | Output                  |

|--------|-------------------|-------------------------|

| 0      | 00                | HCSL                    |

| 0      | 01                | LVDS                    |

| 0      | 10                | LVPECL                  |

| 1      | 00 or 01 or 10    | High-Z (on output N)    |

| X      | 11                | High-Z (on all outputs) |

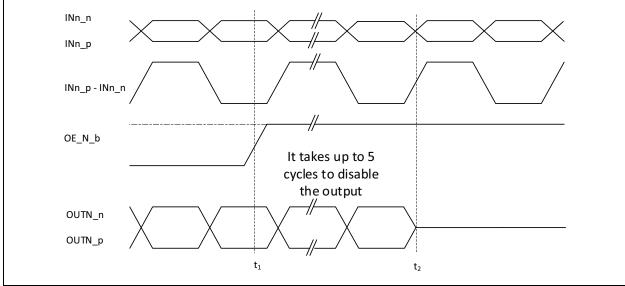

Output is disabled synchronously and depending of the input frequency it can take up to 5 clock cycles to disable the output ( $t_2 - t_1 \le 5$ \*T, where T is the input clock period) as shown in Figure 2-12.

FIGURE 2-12: Output Disable.

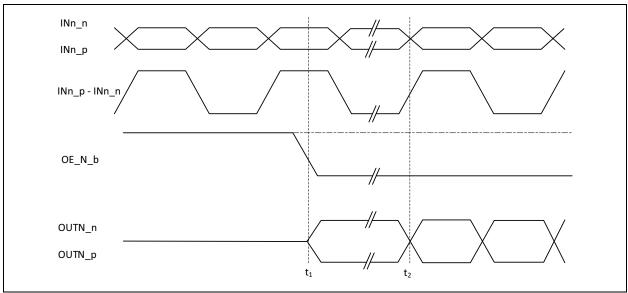

Any outputs can be enabled by pulling the corresponding OE\_b pin low. As soon as OE\_N\_b pin goes low  $(t_1)$  the output N will go from high-Z to low (OUTN\_p = low, OUTN\_n = high) and will start to track the input after up to 5 input clock cycles  $(t_2 - t_1 \le 5^*T)$ , where T is the input clock period) depending on the frequency of the input clock as shown in Figure 2-13.

FIGURE 2-13: Output Enable.

### 2.8.2 I<sup>2</sup>C BUS CONTROL MODE

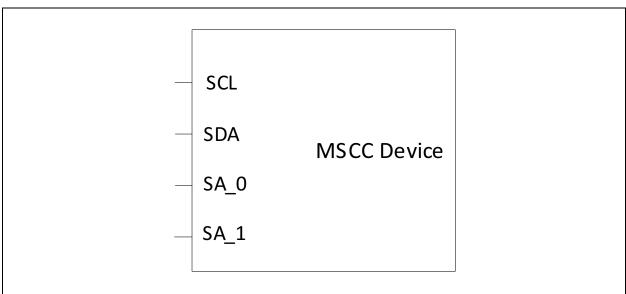

ZL40268 is controlled via four pin I<sup>2</sup>C Bus client interface as shown in Figure 2-14.

FIGURE 2-14: I<sup>2</sup>C Bus Client Interface.

The address selection is done via SA\_0 and SA\_1 hardware pins, which select the appropriate address for the device.

TABLE 2-3: I<sup>2</sup>C BUS ADDRESS TABLE

| SA_1 | SA_0 | I <sup>2</sup> C Bus Address |

|------|------|------------------------------|

| 0    | 0    | 0x34                         |

| 0    | 1    | 0x35                         |

| 1    | 0    | 0x36                         |

| 1    | 1    | 0x37                         |

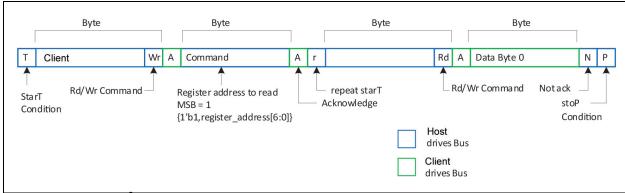

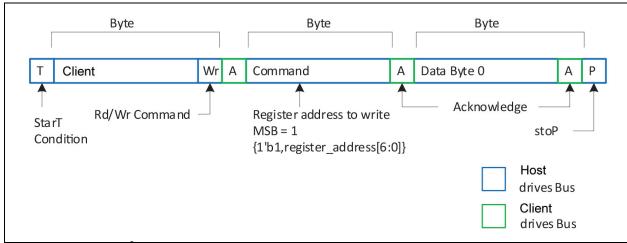

# 2.9 I<sup>2</sup>C Bus Byte Read/Write

Reading or writing a register or registers in a I<sup>2</sup>C Bus client device is MSB first and LBS last in one-byte blocks.

The access from I<sup>2</sup>C host starts with the start condition followed by the client address and the write indicator bit. This is then followed by the command byte which in bits [6:0] contains the address of the register to be accessed for byte mode or the first register to be accessed in the burst mode. The most significant bit in the command byte must be set to 1.

**Byte Read:** The standard byte read is as shown in Figure 2-15. The command byte is followed the client address and read indication bit. The device (client) will respond by sending the requested byte.

FIGURE 2-15: I<sup>2</sup>C Bus Byte Read.

**Write:** Figure 2-16 illustrates the standard byte write After the written byte has been acknowledged by the device, the host will assert the stop signal.

FIGURE 2-16: I<sup>2</sup>C Bus Byte Write.

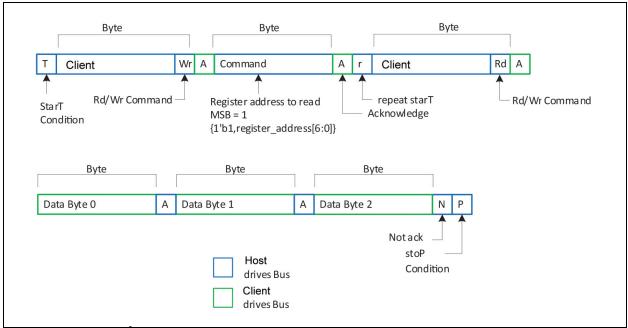

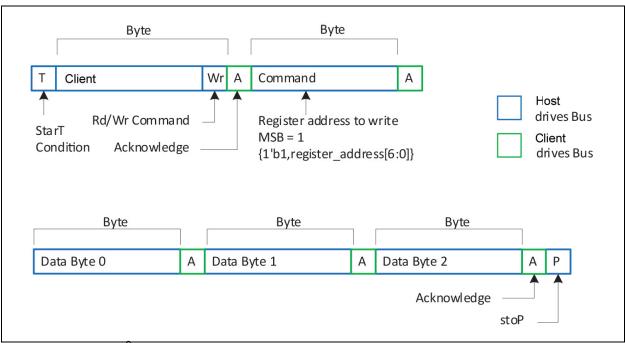

#### 2.10 I<sup>2</sup>C Bus Burst Read/Write

Burst Read and Write are very similar to Byte Read and Write.

**Burst Read:** Figure 2-17 illustrates the Burst Read. The I<sup>2</sup>C host acknowledges after each received byte and finally sends a Not Acknowledge (NACK) followed with Stop Condition.

FIGURE 2-17: I<sup>2</sup>C Bus Burst Read.

Burst Write: Figure 2-18 illustrates the Burst Write. The I<sup>2</sup>C host will send the Stop Condition after the last data byte.

FIGURE 2-18: I<sup>2</sup>C Bus Burst Write.

### 2.11 Typical Phase Noise Characteristics

FIGURE 2-19: 100 MHz HCSL Output Phase Noise.

FIGURE 2-20: 156.25MHz LVDS Output Phase Noise.

FIGURE 2-21: 625 MHz LVPECL Output Phase Noise.

FIGURE 2-22: Phase Noise with 156.25MHz Crystal.

### 3.0 REGISTER MAP

The device is controlled by accessing registers through the serial interface. Table 3-1 provides a summary of the registers available for the configuration of the device. The default settings can be modified via factory programmable OTP memory.

TABLE 3-1: REGISTER MAP

| Address<br>I <sup>2</sup> C A[6:0]<br>Hex (0x) | Name      | Data D[7:0]                                                    |

|------------------------------------------------|-----------|----------------------------------------------------------------|

| 00                                             | XTALBG    | xtal_buf_gain[7:0]                                             |

| 01                                             | XTALDL    | xtal_drive_level[7:0]                                          |

| 02                                             | XTALLC    | xtal_load_cap[7:0]                                             |

| 03                                             | XTALNR    | xtal_normal_run                                                |

| 04                                             | OUTLOWALL | out_low_all                                                    |

| 05                                             | INSEL     | input_select[1:0]                                              |

| 06                                             | _         | not used                                                       |

| 07                                             | DRVTYPE0  | driver_type[7:0] (differential output OUT3, OUT2, OUT1, OUT0)  |

| 08                                             | DRVTYPE1  | driver_type[15:8] (differential output OUT7, OUT6, OUT5, OUT4) |

| 09                                             | Reserved  | Reserved                                                       |

| 0A                                             | OUTLOW    | output_drive_low[7:0]                                          |

| 0B                                             | Reserved  | Reserved                                                       |

| 0C                                             | COMMODSEL | vcm_sel                                                        |

| 0D                                             | _         | not used                                                       |

| 0E                                             | DEVADDR   | dev_addr[2:0]                                                  |

| 0F                                             | Reserved  | Reserved                                                       |

| 10                                             | Reserved  | Reserved                                                       |

| 11                                             | DEVICEID  | Device Identification                                          |

| 12 - 1F                                        | Reserved  | Reserved                                                       |

TABLE 3-2: 0X00 XTALBG-XTAL BUFFER GAIN

| Bit | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Type | Reset |

|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 7:0 | xtal_buf_gain[7:0] | Programs crystal buffer (inverting amplifier) gain.  Every bit pair (bits: 01, 23, 45, 67) of this register correspond to additional equal gain block which can be added (bits set) or removed (bits cleared).  Minimum gain is 0x00 (default) and 0xFF is maximum gain When reference input mode is "bypass XTAL mode" or "differential input modes" with HIGH xtal_normal_run bit, the buffer is disabled and follows "Input Selection".  When xtal_normal_run bit is LOW, XTAL buffer is in the "xtal forced run" mode and keep running.  8'b0000_0000: default crystal buffer strength 8'b0000_011: enable additional buffer strength 8'b0001_0000: enable additional buffer strength 8'b0011_0000: enable additional buffer strength 8'b1100_0000: enable additional buffer strength | RW   | FF    |

TABLE 3-3: 0X01 XTALDL - XTAL DRIVE LEVEL

| Bit | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Туре | Reset |

|-----|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 7:0 | xtal_drive_level[7:0] | Internal damping resistance of crystal circuit to limit external crystal's drive level uW.  The value of damping resistor is determined by crystal's motion resistance of crystal's equivalent circuit.  Drive level should be lower than crystal manufacturer's specification.  Crystal's equivalent values should be requested to the manufacturer, (motion resistance and shunt capacitance).  The selected resistors are connected to XOUT.  Multiple bit combinations available by 7-bit control.  Because they use parallel connections, 0xFF is the smallest resistance and 0x01 is the highest resistance.  8'b0000_0000: disable all resistors 8'b0000_0001: 312 Ohm resistor 8'b0000_0100: 84 Ohm resistor 8'b0000_1000: 42 Ohm resistor 8'b0001_0000: 21 Ohm resistor 8'b0010_0000: 10.5 Ohm resistor 8'b0100_0000: 0 Ohm connection 8'b1000_0000: not used | RW   | 04    |

#### TABLE 3-4: 0X02 XTALLC - XTAL LOAD CAPACITANCE

| Bit | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Type | Reset |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 7:0 | xtal_load_cap[7:0] | Internal load capacitance of crystal circuit (0 pF to 21.75 pF with the resolution of 0.25 pF).  XIN and XOUT have each capacitor connected to GND.  Multiple bit combinations available between 8 capacitors.  8'b0000_0000: disable all xtal load capacitors 8'b0000_0001: enable capacitor 0.25 pF 8'b0000_0100: enable capacitor 0.5 pF 8'b0000_0100: enable capacitor 1 pF 8'b0000_1000: enable capacitor 2 pF 8'b0001_0000: enable capacitor 2 pF 8'b0010_0000: enable capacitor 4 pF 8'b0100_0000: enable capacitor 4 pF 8'b1000_0000: enable capacitor 8 pF | RW   | 40    |

### TABLE 3-5: 0X03 XTALNR - XTAL NORMAL RUN

| Bit | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Туре | Reset   |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 7:1 | Unused          | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R    | 0000000 |

| 0   | xtal_normal_run | When this bit is set high crystal oscillator circuit is running only if input_select[1:0] register at address 0x05 selects crystal mode (2'b10). This value is recommended because it provides best jitter performanceXO circuit is running only when it is needed.  When this bit is set low the crystal oscillator will keep running even if crystal oscillator is not selected in input_select[1:0] register at address 0x05. This mode should only be used when fast switching between input references and crystal oscillator is required. | RW   | 1       |

TABLE 3-6: 0X04 OUTLOWALL - OUTPUT LOW ALL

| Bit | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Туре | Reset   |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 7:1 | Unused      | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R    | 0000000 |

| 0   | out_low_all | OUTLOWALL effects OUTLOW register.  1'b0: Output0 to Output7 are according to their driver_type[n+1, n] values 1'b1: Output0 to Output7 will drive logic LOW.  OTP value load to this bit and/or I <sup>2</sup> C write to this bit in the SCM mode, will affect all the values at OUTLOW register. In other words, loading value of 1'b0 from OTP or writing it from I <sup>2</sup> C, will cause all values in OUTLOW register to be 0's. Same thing for 1'b1.  In SCM, the output_low values per output are controlled individually by accessing the bits in OUTLOW register. However, any subsequent write to this bit will affect the values in those register (OUTLOW). | RW   | 0       |

### TABLE 3-7: 0X05 INSEL - INPUT SELECT REGISTER

| Bit | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Туре | Reset  |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

| 7:2 | Unused            | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R    | 000000 |

| 1:0 | input_select[1:0] | Input reference clock selection. Proper external coupling and termination are required. 2'b00: Differential input from IN0_p and IN0_n 2'b01: Dfferential input from IN1_p and IN1_n 2'b10: Fundamental XTAL mode with XIN and XOUT (Use internal crystal oscillator circuits) or XTAL overdrive mode (single-ended clock signal fed to XIN) 2'b11: XTAL bypass mode (single-ended clock signal with XIN and disabled internal crystal buffer circuit in the analog block) | RW   | 00     |

# TABLE 3-8: 0X07 DRVTYPE0 - (OUTPUT TYPE SELECT 0 TO 3)

| Bit | Name          | Description                                                                                                                        | Туре | Reset |

|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 7:4 | Reserved      | Reserved                                                                                                                           | RW   | 11    |

| 3:2 | driver_type_1 | Output driver type of differential OUT1.  The same bit configuration with OUT0.                                                    | RW   | 11    |