## OCTAL SIMULTANEOUS-SAMPLING 24-BIT ANALOG-TO-DIGITAL CONVERTER

Check for Samples: ADS1278-HT

## **FEATURES**

- Simultaneously Measure Eight Channels

- Up to 128-kSPS Data Rate

- AC Performance: 62-kHz Bandwidth 111-dB SNR (High-Resolution Mode) –108-dB THD

- DC Accuracy: 0.8-µV/°C Offset Drift 1.3-ppm/°C Gain Drift

- Selectable Operating Modes: High-Speed: 128 kSPS, 106 dB SNR High-Resolution: 52 kSPS, 111 dB SNR Low-Power: 52 kSPS, 31 mW/ch Low-Speed: 10 kSPS, 7 mW/ch

- Linear Phase Digital Filter

- SPI™ or Frame-Sync Serial Interface

- Low Sampling Aperture Error

- Modulator Output Option (digital filter bypass)

- Analog Supply: 5 V

- Digital Core: 1.8 V

- I/O Supply: 1.8 V to 3.3 V

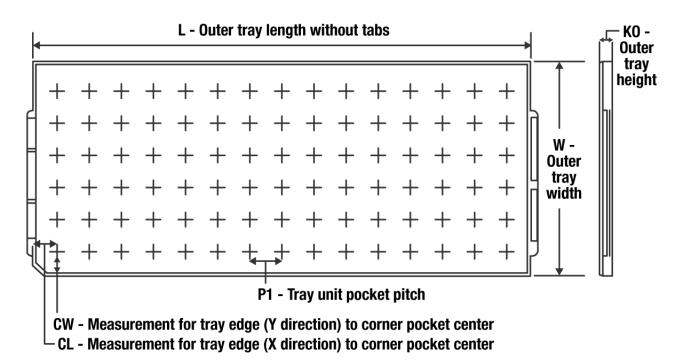

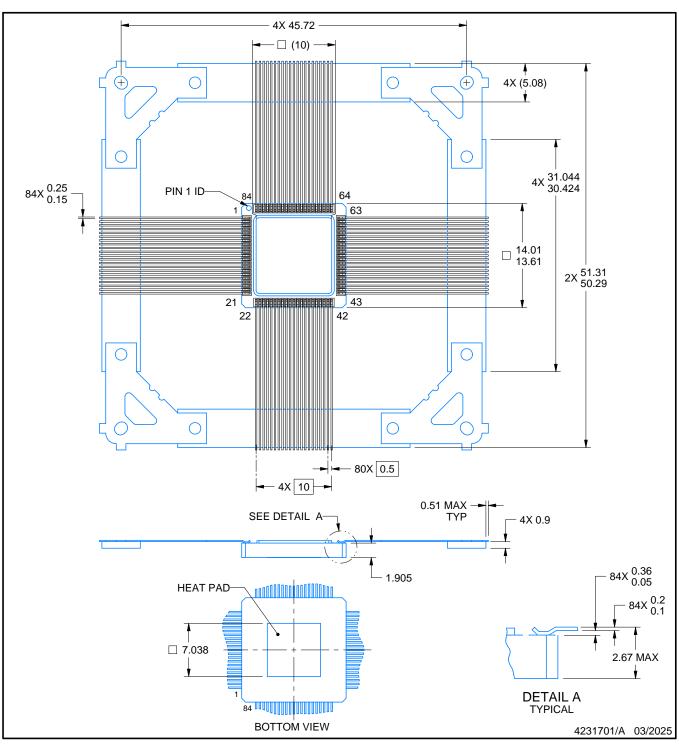

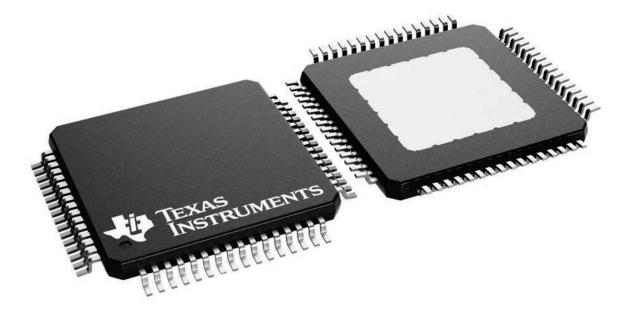

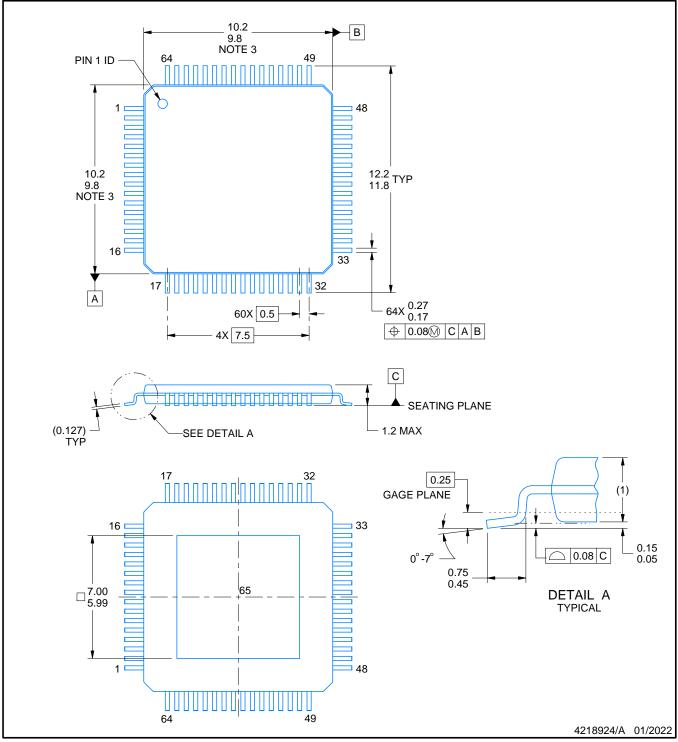

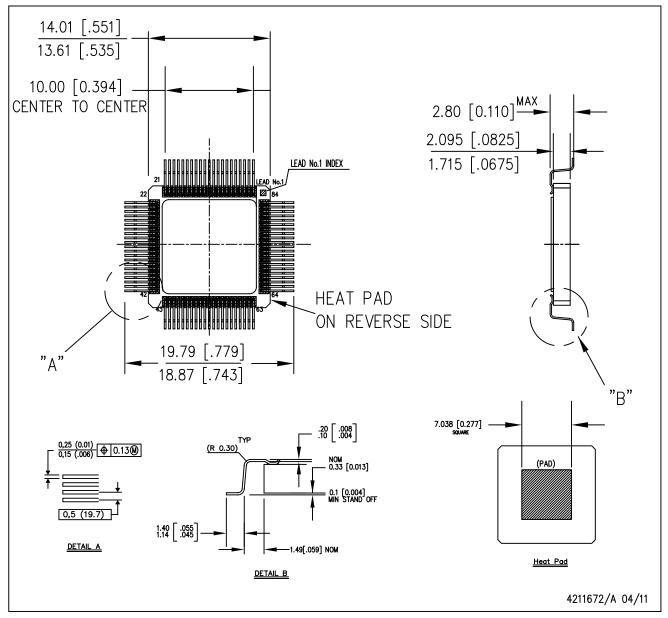

- Currently Available in an HTQFP-64 PowerPAD<sup>™</sup> package, an 84-Pin HFQ Package and a KGD Chiptray Option

# SUPPORTS EXTREME TEMPERATURE APPLICATIONS

- Controlled Baseline

- One Assembly/Test Site

- One Fabrication Site

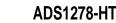

- Available in Extreme (-55°C/210°C) Temperature Range <sup>(1)</sup>

- Extended Product Life Cycle

- Extended Product-Change Notification

- Product Traceability

- Texas Instruments High Temperature Products Utilize Highly Optimized Silicon (Die) Solutions With Dsign and Process Enhancements to Maximize Performance Over Extended Temperatures

## APPLICATIONS

- Down-Hole Drilling

- High Temperature Environments

- Vibration/Modal Analysis

- Multi-Channel Data Acquisition

- Acoustics/Dynamic Strain Gauges

- Pressure Sensors

## DESCRIPTION

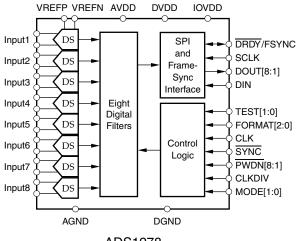

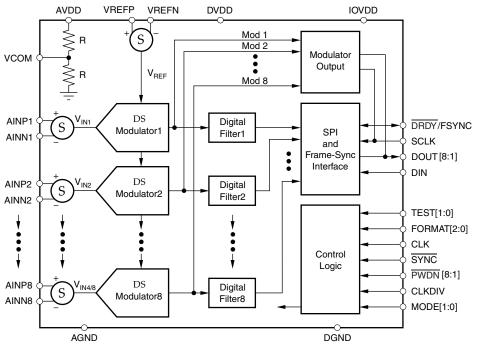

Based on the single-channel ADS1271, the ADS1278 (octal) is a 24-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC) with data rates up to 128 k samples per second (SPS), allowing simultaneous sampling of eight channels.

Traditionally, industrial delta-sigma ADCs offering good drift performance use digital filters with large passband droop. As a result, they have limited signal bandwidth and are mostly suited for dc measurements. High-resolution ADCs in audio applications offer larger usable bandwidths, but the offset and drift specifications are significantly weaker than respective industrial counterparts. The ADS1278 combines these types of converters, allowing highprecision industrial measurement with excellent dc and ac specifications.

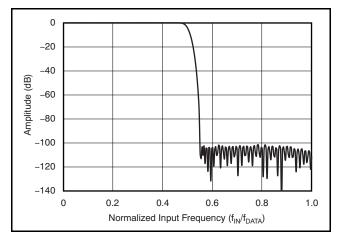

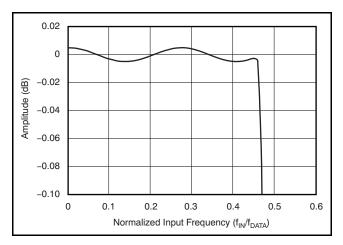

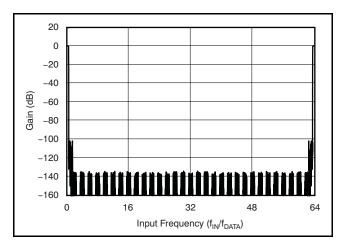

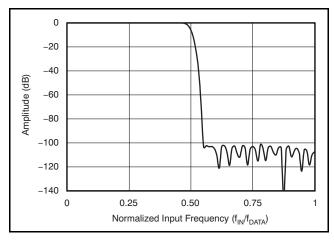

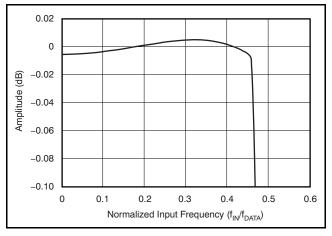

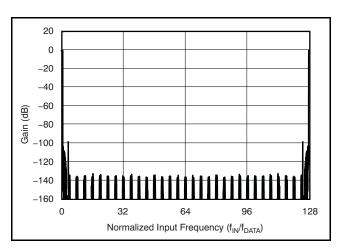

The high-order, chopper-stabilized modulator achieves very low drift with low in-band noise. The onboard decimation filter suppresses modulator and signal out-of-band noise. These ADCs provide a usable signal bandwidth up to 90% of the Nyquist rate with less than 0.005 dB of ripple.

Four operating modes allow for optimization of speed, resolution, and power. All operations are controlled directly by pins; there are no registers to program. The device is fully specified over the extended industrial range (-55°C to 210°C) and is available in an HTQFP-64 PowerPAD package (-55°C to 175°C), an 84-pin HFQ package and a KGD chiptray option.

(1) Custom temperature ranges available

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

#### SBAS447E - MARCH 2009-REVISED APRIL 2013

ADS1278

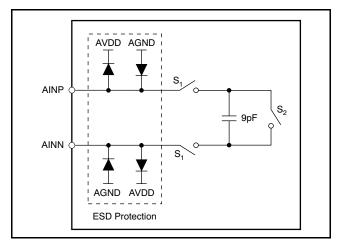

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### Table 1. ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE             | ORDERABLE PART NUMBER |

|----------------|---------------------|-----------------------|

| –55°C to 175°C | PAP                 | ADS1278HPAP           |

|                | HFQ                 | ADS1278SHFQ           |

| –55°C to 210°C | HKP                 | ADS1278SHKP           |

|                | CHIPTRAY (bare die) | ADS1278SKGDA          |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

## ADS1278-HT

SBAS447E – MARCH 2009–REVISED APRIL 2013

www.ti.com

4

## ADS1278-HT

www.ti.com

#### SBAS447E - MARCH 2009-REVISED APRIL 2013

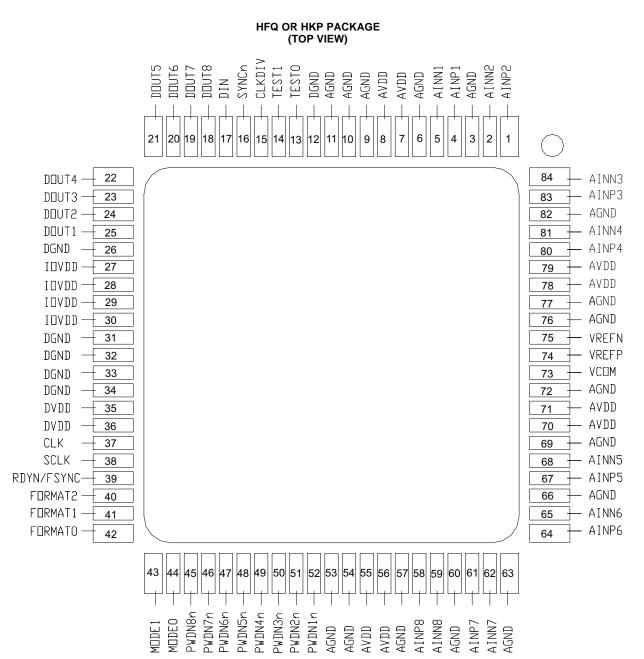

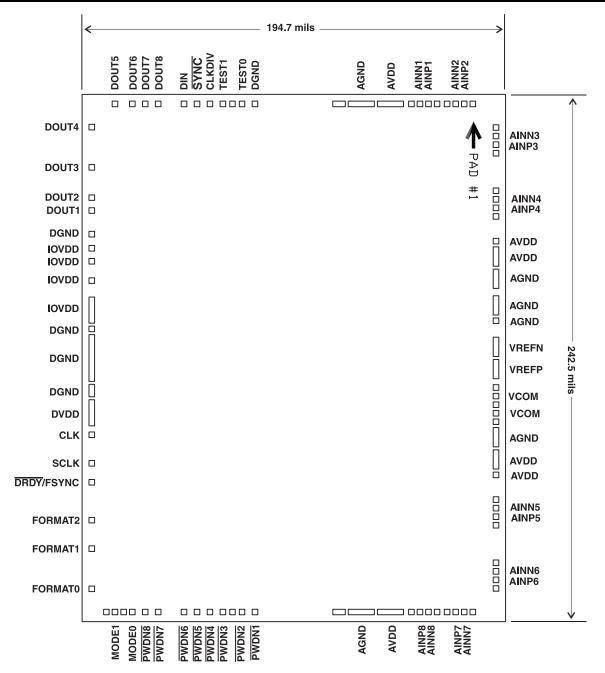

### Table 2. HFQ or HKP PIN DESCRIPTIONS

| PIN NAME       | FUNCTION             | DESCRIPTION                                                                                                                                        |

|----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND           | Analog ground        | Analog ground; connect to DGND using a single plane.                                                                                               |

| AINP1          | Analog input         |                                                                                                                                                    |

| AINP2          | Analog input         |                                                                                                                                                    |

| AINP3          | Analog input         |                                                                                                                                                    |

| AINP4          | Analog input         |                                                                                                                                                    |

| AINP5          | Analog input         | AINP[8:1] Positive analog input, channels 8 through 1.                                                                                             |

| AINP6          | Analog input         |                                                                                                                                                    |

| AINP7          | Analog input         |                                                                                                                                                    |

| AINP8          | Analog input         |                                                                                                                                                    |

| AINN1          | Analog input         |                                                                                                                                                    |

| AINN2          | Analog input         |                                                                                                                                                    |

| AINN3          | Analog input         |                                                                                                                                                    |

| AINN4          | Analog input         |                                                                                                                                                    |

| AINN5          | Analog input         | AINN[8:1] Negative analog input, channels 8 through 1.                                                                                             |

| AINN6          | Analog input         |                                                                                                                                                    |

| AINN7          | Analog input         |                                                                                                                                                    |

| AINN8          | Analog input         |                                                                                                                                                    |

| AVDD           | Analog power supply  | Analog power supply (4.75V to 5.25V).                                                                                                              |

| VCOM           | Analog output        | AVDD/2 Unbuffered voltage output.                                                                                                                  |

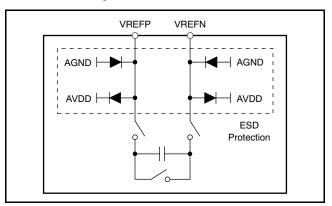

| VREFN          | Analog input         | Negative reference input.                                                                                                                          |

| VREFP          | Analog input         | Positive reference input.                                                                                                                          |

| CLK            | Digital input        | Master clock input.                                                                                                                                |

| CLKDIV         | Digital input        | CLK input divider control: 1 = 32.768MHz (High-Speed mode only) / 27MHz<br>0 = 13.5MHz (low-power) / 5.4MHz (low-speed)                            |

| DGND           | Digital ground       | Digital ground power supply.                                                                                                                       |

| DIN            | Digital input        | Daisy-chain data input.                                                                                                                            |

| DOUT1          | Digital output       | DOUT1 is TDM data output (TDM mode).                                                                                                               |

| DOUT2          | Digital output       |                                                                                                                                                    |

| DOUT3          | Digital output       |                                                                                                                                                    |

| DOUT4          | Digital output       |                                                                                                                                                    |

| DOUT5          | Digital output       | DOUT[8:1] Data output for channels 8 through 1.                                                                                                    |

| DOUT6          | Digital output       |                                                                                                                                                    |

| DOUT7          | Digital output       |                                                                                                                                                    |

| DOUT8          | Digital output       |                                                                                                                                                    |

| DRDY/<br>FSYNC | Digital input/output | Frame-Sync protocol: frame clock input; SPI protocol: data ready output.                                                                           |

| DVDD           | Digital power supply | Digital core power supply (+1.65V to +1.95V).                                                                                                      |

| FORMAT0        | Digital input        |                                                                                                                                                    |

| FORMAT1        | Digital input        | FORMAT[2:0] Selects Frame-Sync/SPI protocol, TDM/discrete data outputs, fixed/dynamic position TDM data, and modulator mode/normal operating mode. |

| FORMAT2        | Digital input        |                                                                                                                                                    |

| IOVDD          | Digital power supply | I/O power supply (+1.65V to +3.6V).                                                                                                                |

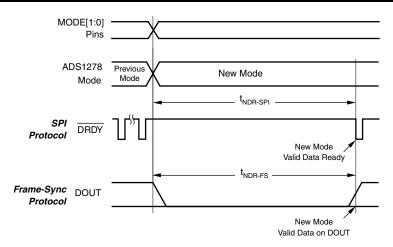

| MODE0          | Digital input        | MODE[1:0] Selects High-Speed, High-Resolution, Low-Power, or Low-Speed mode operation.                                                             |

| MODE1          | Digital input        | work in a selects migh-speed, migh-kesolution, Low-Power, or Low-Speed mode operation.                                                             |

PIN

## Table 2. HFQ or HKP PIN DESCRIPTIONS (continued)

| PIN NAME | FUNCTION             | DESCRIPTION                                            |                                             |                 |  |  |  |  |

|----------|----------------------|--------------------------------------------------------|---------------------------------------------|-----------------|--|--|--|--|

| PWDN1    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| PWDN2    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| PWDN3    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| PWDN4    | Digital input        | PWDN[8:1] Power-down control for channels 8 through 1. |                                             |                 |  |  |  |  |

| PWDN5    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| PWDN6    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| PWDN7    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| PWDN8    | Digital input        |                                                        |                                             |                 |  |  |  |  |

| SCLK     | Digital input/output | Serial clock input, Modulator clo                      | Serial clock input, Modulator clock output. |                 |  |  |  |  |

| SYNC     | Digital input        | Synchronize input (all channels)                       | Synchronize input (all channels).           |                 |  |  |  |  |

| TEST0    | Digital input        | TEST[1:0] Test mode select:                            | 00 = Normal operation                       | 01 = Do not use |  |  |  |  |

| TEST1    | Digital input        |                                                        | 11 = Test mode                              | 10 = Do not use |  |  |  |  |

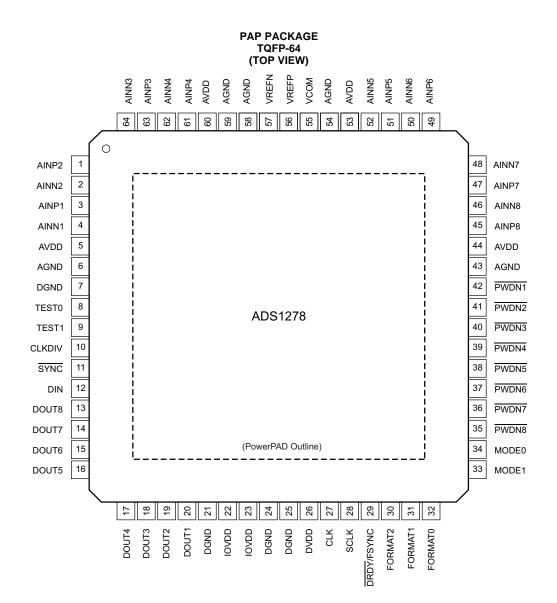

| FIN    |                      |                     |                                                                                                                      |  |  |

|--------|----------------------|---------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO.                  | FUNCTION            | DESCRIPTION                                                                                                          |  |  |

| AGND   | 6, 43, 54,<br>58, 59 | Analog ground       | Analog ground; connect to DGND using a single plane.                                                                 |  |  |

| AINP1  | 3                    | Analog input        |                                                                                                                      |  |  |

| AINP2  | 1                    | Analog input        |                                                                                                                      |  |  |

| AINP3  | 63                   | Analog input        |                                                                                                                      |  |  |

| AINP4  | 61                   | Analog input        | AINP[8:1] Positive analog input, channels 8 through 1.                                                               |  |  |

| AINP5  | 51                   | Analog input        |                                                                                                                      |  |  |

| AINP6  | 49                   | Analog input        |                                                                                                                      |  |  |

| AINP7  | 47                   | Analog input        |                                                                                                                      |  |  |

| AINP8  | 45                   | Analog input        |                                                                                                                      |  |  |

| AINN1  | 4                    | Analog input        |                                                                                                                      |  |  |

| AINN2  | 2                    | Analog input        |                                                                                                                      |  |  |

| AINN3  | 64                   | Analog input        |                                                                                                                      |  |  |

| AINN4  | 62                   | Analog input        | AINN[8:1] Negative analog input, channels 8 through 1.                                                               |  |  |

| AINN5  | 52                   | Analog input        |                                                                                                                      |  |  |

| AINN6  | 50                   | Analog input        |                                                                                                                      |  |  |

| AINN7  | 48                   | Analog input        |                                                                                                                      |  |  |

| AINN8  | 46                   | Analog input        |                                                                                                                      |  |  |

| AVDD   | 5, 44, 53, 60        | Analog power supply | Analog power supply (4.75V to 5.25V).                                                                                |  |  |

| VCOM   | 55                   | Analog output       | AVDD/2 Unbuffered voltage output.                                                                                    |  |  |

| VREFN  | 57                   | Analog input        | Negative reference input.                                                                                            |  |  |

| VREFP  | 56                   | Analog input        | Positive reference input.                                                                                            |  |  |

| CLK    | 27                   | Digital input       | Master clock input (f <sub>CLK</sub> ).                                                                              |  |  |

| CLKDIV | 10                   | Digital input       | CLK input divider control: 1 = 37MHz (High-Speed mode)/otherwise 27MHz<br>0 = 13.5MHz (low-power)/5.4MHz (low-speed) |  |  |

| DGND   | 7, 21, 24, 25        | Digital ground      | Digital ground power supply.                                                                                         |  |  |

| DIN    | 12                   | Digital input       | Daisy-chain data input.                                                                                              |  |  |

| DOUT1  | 20                   | Digital output      | DOUT1 is TDM data output (TDM mode).                                                                                 |  |  |

| DOUT2  | 19                   | Digital output      |                                                                                                                      |  |  |

| DOUT3  | 18                   | Digital output      |                                                                                                                      |  |  |

| DOUT4  | 17                   | Digital output      | DOUT[8:1] Data output for channels 8 through 1.                                                                      |  |  |

#### Table 3. PAP PIN DESCRIPTIONS

#### www.ti.com

**EXAS**

## ADS1278-HT

www.ti.com

#### SBAS447E - MARCH 2009-REVISED APRIL 2013

| I              | PIN    |                      |                                                                                                                                                    |  |  |  |

|----------------|--------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME           | NO.    | FUNCTION             | DESCRIPTION                                                                                                                                        |  |  |  |

| DOUT5          | 16     | Digital output       |                                                                                                                                                    |  |  |  |

| DOUT6          | 15     | Digital output       |                                                                                                                                                    |  |  |  |

| DOUT7          | 14     | Digital output       |                                                                                                                                                    |  |  |  |

| DOUT8          | 13     | Digital output       |                                                                                                                                                    |  |  |  |

| DRDY/<br>FSYNC | 29     | Digital input/output | Frame-Sync protocol: frame clock input; SPI protocol: data ready output.                                                                           |  |  |  |

| DVDD           | 26     | Digital power supply | Digital core power supply.                                                                                                                         |  |  |  |

| FORMAT0        | 32     | Digital input        |                                                                                                                                                    |  |  |  |

| FORMAT1        | 31     | Digital input        | FORMAT[2:0] Selects Frame-Sync/SPI protocol, TDM/discrete data outputs, fixed/dynamic position TDM data, and modulator mode/normal operating mode. |  |  |  |

| FORMAT2        | 30     | Digital input        |                                                                                                                                                    |  |  |  |

| IOVDD          | 22, 23 | Digital power supply | I/O power supply (+1.65V to +3.6V).                                                                                                                |  |  |  |

| MODE0          | 34     | Digital input        | MODE[1:0] Selects High-Speed, High-Resolution, Low-Power, or Low-Speed                                                                             |  |  |  |

| MODE1          | 33     | Digital input        | mode operation.                                                                                                                                    |  |  |  |

| PWDN1          | 42     | Digital input        |                                                                                                                                                    |  |  |  |

| PWDN2          | 41     | Digital input        |                                                                                                                                                    |  |  |  |

| PWDN3          | 40     | Digital input        |                                                                                                                                                    |  |  |  |

| PWDN4          | 39     | Digital input        | PWDN[8:1] Power-down control for channels 8 through 1.                                                                                             |  |  |  |

| PWDN5          | 38     | Digital input        |                                                                                                                                                    |  |  |  |

| PWDN6          | 37     | Digital input        |                                                                                                                                                    |  |  |  |

| PWDN7          | 36     | Digital input        |                                                                                                                                                    |  |  |  |

| PWDN8          | 35     | Digital input        |                                                                                                                                                    |  |  |  |

| SCLK           | 28     | Digital input/output | Serial clock input, Modulator clock output.                                                                                                        |  |  |  |

| SYNC           | 11     | Digital input        | Synchronize input (all channels).                                                                                                                  |  |  |  |

| TEST0          | 8      | Digital input        | TEST[1:0] Test mode select: 00 = Normal operation 01 = Do not use                                                                                  |  |  |  |

| TEST1          | 9      | Digital input        | 11 = Test mode 10 = Do not use                                                                                                                     |  |  |  |

## ADS1278-HT

SBAS447E - MARCH 2009-REVISED APRIL 2013

EXAS

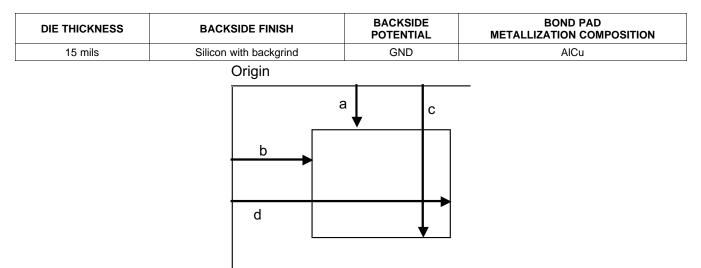

### BARE DIE INFORMATION

Table 4. Bond Pad Coordinates in Microns - Rev A<sup>(1)</sup>

| DISCRIPTION    | PAD NUMBER | а       | b       | С       | d       |

|----------------|------------|---------|---------|---------|---------|

| Do not connect | 1          | 5.00    | 4455.65 | 70.00   | 4520.65 |

| AINP2          | 2          | 5.00    | 4355.65 | 70.00   | 4420.65 |

| AINN2          | 3          | 5.00    | 4255.65 | 70.00   | 4320.65 |

| Do not connect | 4          | 5.00    | 4155.65 | 70.00   | 4220.65 |

| Do not connect | 5          | 5.00    | 4038.30 | 70.00   | 4103.30 |

| AINP1          | 6          | 5.00    | 3938.30 | 70.00   | 4003.30 |

| AINN1          | 7          | 5.00    | 3838.30 | 70.00   | 3903.30 |

| Do not connect | 8          | 5.00    | 3738.30 | 70.00   | 3803.30 |

| AVDD           | 9          | 5.00    | 3373.30 | 70.00   | 3678.30 |

| AGND           | 10         | 5.00    | 3033.30 | 70.00   | 3338.30 |

| Do not connect | 11         | 5.00    | 2853.30 | 70.00   | 2998.30 |

| DGND           | 12         | 5.00    | 1911.65 | 70.00   | 1976.65 |

| TEST0          | 13         | 5.00    | 1760.45 | 70.00   | 1825.45 |

| Do not connect | 14         | 5.00    | 1648.95 | 70.00   | 1713.95 |

| TEST1          | 15         | 5.00    | 1536.60 | 70.00   | 1601.60 |

| CLKDIV         | 16         | 5.00    | 1385.40 | 70.00   | 1450.40 |

| SYNC           | 17         | 5.00    | 1234.20 | 70.00   | 1299.20 |

| DIN            | 18         | 5.00    | 1083.00 | 70.00   | 1148.00 |

| DOUT8          | 19         | 5.00    | 780.60  | 70.00   | 845.60  |

| DOUT7          | 20         | 5.00    | 629.40  | 70.00   | 694.40  |

| DOUT6          | 21         | 5.00    | 478.20  | 70.00   | 543.20  |

| DOUT5          | 22         | 5.00    | 275.80  | 70.00   | 340.80  |

| DOUT4          | 23         | 275.80  | 5.00    | 340.80  | 70.00   |

| DOUT3          | 24         | 745.40  | 5.00    | 810.40  | 70.00   |

| DOUT2          | 25         | 1099.30 | 5.00    | 1164.30 | 70.00   |

| DOUT1          | 26         | 1250.50 | 5.00    | 1315.50 | 70.00   |

| DGND           | 27         | 1525.25 | 5.00    | 1590.25 | 70.00   |

| IOVDD          | 28         | 1691.00 | 5.00    | 1756.00 | 70.00   |

| IOVDD          | 29         | 1842.20 | 5.00    | 1907.20 | 70.00   |

(1) For signal descriptions see the Pin Descriptions table.

SBAS447E - MARCH 2009-REVISED APRIL 2013

## Table 4. Bond Pad Coordinates in Microns - Rev A<sup>(1)</sup> (continued)

| DISCRIPTION            | PAD NUMBER | а                  | b                  | С                  | d                  |

|------------------------|------------|--------------------|--------------------|--------------------|--------------------|

| IOVDD                  | 30         | 2068.10            | 5.00               | 2133.10            | 70.00              |

| IOVDD                  | 31         | 2292.45            | 5.00               | 2597.45            | 70.00              |

| DGND                   | 32         | 2632.45            | 5.00               | 2697.45            | 70.00              |

| DGND                   | 33         | 2732.45            | 5.00               | 3277.45            | 70.00              |

| DGND                   | 34         | 3312.45            | 5.00               | 3457.45            | 70.00              |

| DVDD                   | 35         | 3492.45            | 5.00               | 3797.45            | 70.00              |

| CLK                    | 36         | 3869.40            | 5.00               | 3934.40            | 70.00              |

| SCLK                   | 37         | 4201.90            | 5.00               | 4266.90            | 70.00              |

| DRDY/FSYNC             | 38         | 4423.90            | 5.00               | 4488.90            | 70.00              |

| FORMAT2                | 39         | 4866.90            | 5.00               | 4931.90            | 70.00              |

| FORMAT1                | 40         | 5199.40            | 5.00               | 5264.40            | 70.00              |

| FORMATO                | 41         | 5669.00            | 5.00               | 5734.00            | 70.00              |

| MODE1                  | 42         | 5939.80            | 275.80             | 6004.80            | 340.80             |

| MODE0                  | 43         | 5939.80            | 478.20             | 6004.80            | 543.20             |

| PWDN8                  | 43         | 5939.80            | 629.40             | 6004.80            | 694.40             |

| PWDN8                  | 44         | 5939.80            | 780.60             | 6004.80            | 845.60             |

| PWDN6                  | 46         | 5939.80            | 1083.00            | 6004.80            | 1148.00            |

| PWDN5                  | 40         | 5939.80            | 1234.20            | 6004.80            | 1299.20            |

| PWDN3                  | 47         | 5939.80            | 1385.40            | 6004.80            | 1299.20            |

| PWDN4<br>PWDN3         | 48         | 5939.80            | 1536.60            | 6004.80            | 1601.60            |

| Do not connect         | 50         | 5939.80            | 1648.95            | 6004.80            | 1713.95            |

| PWDN2                  | 50         | 5939.80            | 1760.45            | 6004.80            | 1825.45            |

| PWDN2<br>PWDN1         | 52         |                    |                    |                    | 1976.65            |

|                        |            | 5939.80            | 1911.65            | 6004.80            |                    |

| Do not connect<br>AGND | 53         | 5939.80<br>5939.80 | 2853.30<br>3033.30 | 6004.80            | 2998.30<br>3338.30 |

| AGND                   | 55         | 5939.80            | 3373.30            | 6004.80<br>6004.80 | 3678.30            |

|                        | 55         |                    |                    |                    | 3803.30            |

| Do not connect         |            | 5939.80            | 3738.30            | 6004.80            |                    |

| AINP8                  | 57         | 5939.80            | 3838.30            | 6004.80            | 3903.30            |

| AINN8                  | 58         | 5939.80            | 3938.30            | 6004.80            | 4003.30            |

| Do not connect         | 59         | 5939.80            | 4038.30            | 6004.80            | 4103.30            |

| Do not connect         | 60         | 5939.80            | 4155.65            | 6004.80            | 4220.65            |

| AINP7                  | 61         | 5939.80            | 4255.65            | 6004.80            | 4320.65            |

| AINN7                  | 62         | 5939.80            | 4355.65            | 6004.80            | 4420.65            |

| Do not connect         | 63         | 5939.80            | 4455.65            | 6004.80            | 4520.65            |

| Do not connect         | 64         | 5664.20            | 4726.45            | 5729.20            | 4791.45            |

| AINP6                  | 65         | 5564.20            | 4726.45            | 5629.20            | 4791.45            |

| AINN6                  | 66         | 5464.20            | 4726.45            | 5529.20            | 4791.45            |

| Do not connect         | 67         | 5364.20            | 4726.45            | 5429.20            | 4791.45            |

| Do not connect         | 68         | 4925.95            | 4726.45            | 4990.95            | 4791.45            |

| AINP5                  | 69         | 4825.95            | 4726.45            | 4890.95            | 4791.45            |

| AINN5                  | 70         | 4725.95            | 4726.45            | 4790.95            | 4791.45            |

| Do not connect         | 71         | 4625.95            | 4726.45            | 4690.95            | 4791.45            |

| AVDD                   | 72         | 4337.40            | 4726.45            | 4402.40            | 4791.45            |

| AVDD                   | 73         | 4077.40            | 4726.45            | 4302.40            | 4791.45            |

| AGND                   | 74         | 3817.40            | 4726.45            | 4042.40            | 4791.45            |

| Do not connect         | 75         | 3717.40            | 4726.45            | 3782.40            | 4791.45            |

| VCOM                   | 76         | 3617.40            | 4726.45            | 3682.40            | 4791.45            |

Copyright © 2009–2013, Texas Instruments Incorporated

www.ti.com

| Table 4. Bond Pad Coordinates in Microns - Rev | A <sup>(1)</sup> (continued) |

|------------------------------------------------|------------------------------|

|------------------------------------------------|------------------------------|

| DISCRIPTION    | PAD NUMBER | а       | b       | C       | d       |  |  |

|----------------|------------|---------|---------|---------|---------|--|--|

| Do not connect | 77         | 3517.40 | 4726.45 | 3582.40 | 4791.45 |  |  |

| VCOM           | 78         | 3417.40 | 4726.45 | 3482.40 | 4791.45 |  |  |

| Do not connect | 79         | 3317.40 | 4726.45 | 3382.40 | 4791.45 |  |  |

| VREFP          | 80         | 3022.40 | 4726.45 | 3247.40 | 4791.45 |  |  |

| VREFN          | 81         | 2762.40 | 4726.45 | 2987.40 | 4791.45 |  |  |

| AGND           | 82         | 2537.40 | 4726.45 | 2602.40 | 4791.45 |  |  |

| AGND           | 83         | 2277.40 | 4726.45 | 2502.40 | 4791.45 |  |  |

| AGND           | 84         | 1967.40 | 4726.45 | 2192.40 | 4791.45 |  |  |

| AVDD           | 85         | 1707.40 | 4726.45 | 1932.40 | 4791.45 |  |  |

| AVDD           | 86         | 1607.40 | 4726.45 | 1672.40 | 4791.45 |  |  |

| Do not connect | 87         | 1318.85 | 4726.45 | 1383.85 | 4791.45 |  |  |

| AINP4          | 88         | 1218.85 | 4726.45 | 1283.85 | 4791.45 |  |  |

| AINN4          | 89         | 1118.85 | 4726.45 | 1183.85 | 4791.45 |  |  |

| Do not connect | 90         | 1018.85 | 4726.45 | 1083.85 | 4791.45 |  |  |

| Do not connect | 91         | 580.60  | 4726.45 | 645.60  | 4791.45 |  |  |

| AINP3          | 92         | 480.60  | 4726.45 | 545.60  | 4791.45 |  |  |

| AINN3          | 93         | 380.60  | 4726.45 | 445.60  | 4791.45 |  |  |

| Do not connect | 94         | 280.60  | 4726.45 | 345.60  | 4791.45 |  |  |

| Do not connect | 95         | 5939.80 | 377.00  | 6004.80 | 442.00  |  |  |

| Do not connect | 96         | 5939.80 | 175.80  | 6004.80 | 240.80  |  |  |

**EXAS**

INSTRUMENTS

SBAS447E - MARCH 2009-REVISED APRIL 2013

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range, unless otherwise noted<sup>(1)</sup>

|                                 |                      |                    | UNIT |

|---------------------------------|----------------------|--------------------|------|

| AVDD to AGND                    |                      | -0.3 to 6.0        | V    |

| DVDD, IOVDD to DGND             |                      | -0.3 to 3.6        | V    |

| AGND to DGND                    |                      | -0.3 to 0.3        | V    |

|                                 | Momentary            | 100                | mA   |

| Input current                   | Continuous           | 10                 | mA   |

| Analog input to AGND            |                      | -0.3 to AVDD + 0.3 | V    |

| Digital input or output to DGND |                      | -0.3 to DVDD + 0.3 | V    |

| Junction temperature range      | HFQ and HKP Packages | -55 to 217         | °C   |

|                                 | D Package            | -55 to 175         |      |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### THERMAL INFORMATION

|                         |                                                             | ADS     |         |                |

|-------------------------|-------------------------------------------------------------|---------|---------|----------------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | PAP     | HFQ/HKP | UNITS          |

|                         |                                                             | 64 PINS | 84 PINS |                |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 33.1    | 21.813  |                |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 6.2     | 0.849   |                |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(4)</sup>         | 7.9     | N/A     | 0 <b>0</b> AA/ |

| Ψ <sub>JT</sub>         | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.2     | N/A     | °C/W           |

| $\Psi_{JB}$             | Junction-to-board characterization parameter <sup>(6)</sup> | 7.8     | N/A     |                |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 0.2     | N/A     |                |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

www.ti.com

#### ELECTRICAL CHARACTERISTICS

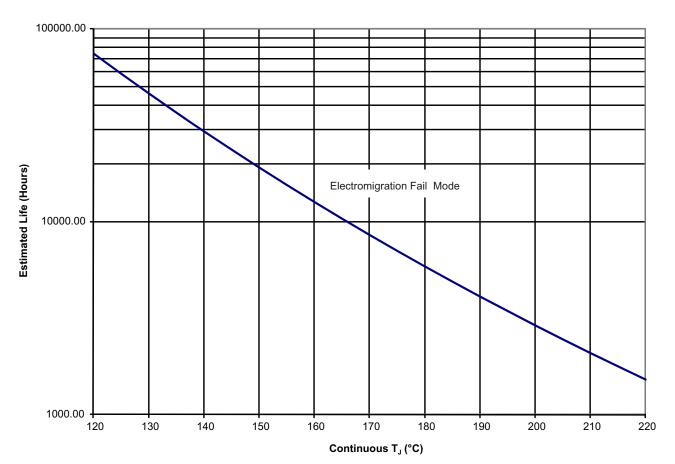

All specifications at  $T_A = T_J = -55^{\circ}$ C to 210°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

|                                                               |                                |                                             | T <sub>A</sub> = - | -55°C to 12   | 5°C           | T <sub>A</sub> | = 210°C <sup>(1)</sup> |               |                      |

|---------------------------------------------------------------|--------------------------------|---------------------------------------------|--------------------|---------------|---------------|----------------|------------------------|---------------|----------------------|

| PA                                                            | RAMETER                        | TEST CONDITIONS                             | MIN                | ТҮР           | MAX           | MIN            | TYP                    | MAX           | UNIT                 |

| Analog Inputs                                                 |                                |                                             |                    |               |               |                |                        |               |                      |

| Full-scale input vo                                           | Itage (FSR <sup>(2)</sup> )    | $V_{IN} = (AINP - AINN)$                    |                    | $\pm V_{REF}$ |               |                | $\pm V_{REF}$          |               | V                    |

| Absolute input volt                                           | age                            | AINP or AINN to AGND                        | AGND –<br>0.1      |               | AVDD +<br>0.1 | AGND –<br>0.1  |                        | AVDD +<br>0.1 | V                    |

| Common-mode in                                                | put voltage (V <sub>CM</sub> ) | $V_{CM} = (AINP + AINN)/2$                  |                    | 2.5           |               |                | 2.5                    |               | V                    |

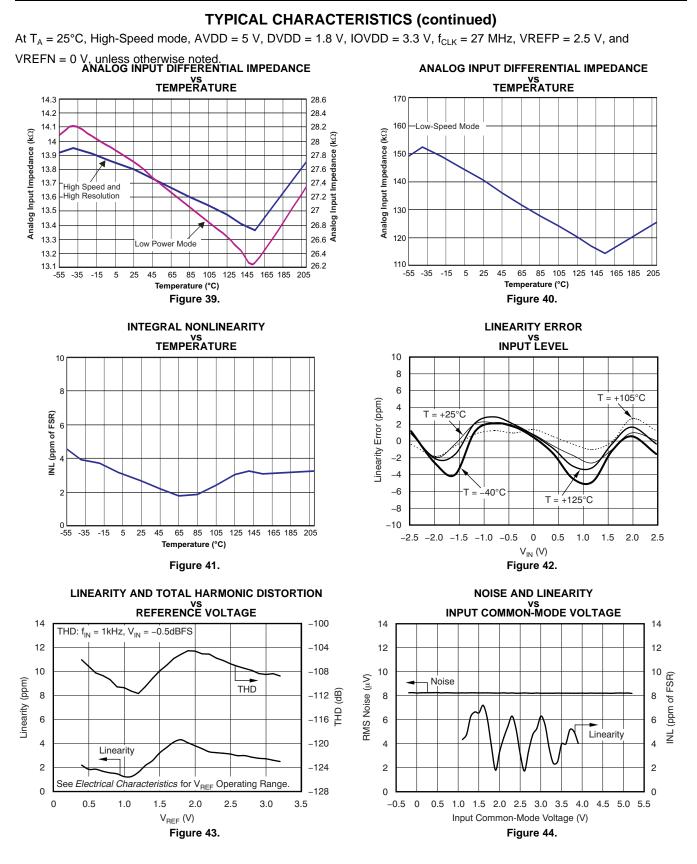

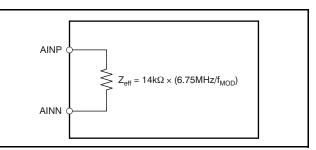

|                                                               | High-Speed mode                |                                             |                    | 14            |               |                | 14                     |               | kΩ                   |

| Differential input                                            | High-Resolution mode           |                                             |                    | 14            |               |                | 14                     |               | kΩ                   |

| impedance                                                     | Low-Power mode                 |                                             |                    | 28            |               |                | 28                     |               | kΩ                   |

|                                                               | Low-Speed mode                 |                                             |                    | 140           |               |                | 140                    |               | kΩ                   |

| DC Performance                                                |                                |                                             | 1                  |               |               |                |                        |               |                      |

| Resolution                                                    |                                | No missing codes                            | 24                 |               |               |                |                        |               | Bits                 |

|                                                               |                                | f <sub>CLK</sub> = 32.768MHz <sup>(3)</sup> |                    | 128,000       |               |                | 128,000                |               | SPS                  |

| Data rate (f <sub>DATA</sub> )                                | High-Speed mode                | f <sub>CLK</sub> = 27MHz                    |                    | 105,469       |               |                | 105,469                |               | SPS <sup>(4)</sup>   |

|                                                               | High-Resolution mode           |                                             |                    | 52,734        |               |                | 52,734                 |               | SPS                  |

|                                                               | Low-Power mode                 |                                             |                    | 52,734        |               |                | 52,734                 |               | SPS                  |

|                                                               | Low-Speed mode                 |                                             |                    | 10,547        |               |                | 10,547                 |               | SPS                  |

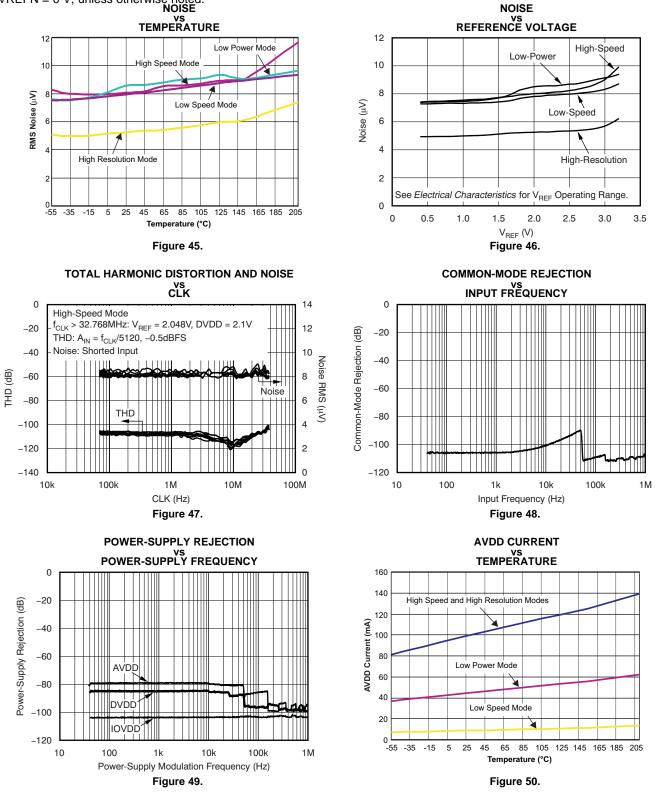

| Integral nonlinearity (INL) <sup>(5)</sup>                    |                                | Differential input, V <sub>CM</sub> = 2.5V  |                    | ±0.0003       | ±0.0012       |                |                        | ±0.0014       | % FSR <sup>(2)</sup> |

| Offset error                                                  |                                |                                             |                    | 0.25          | 2             |                |                        | 2             | mV                   |

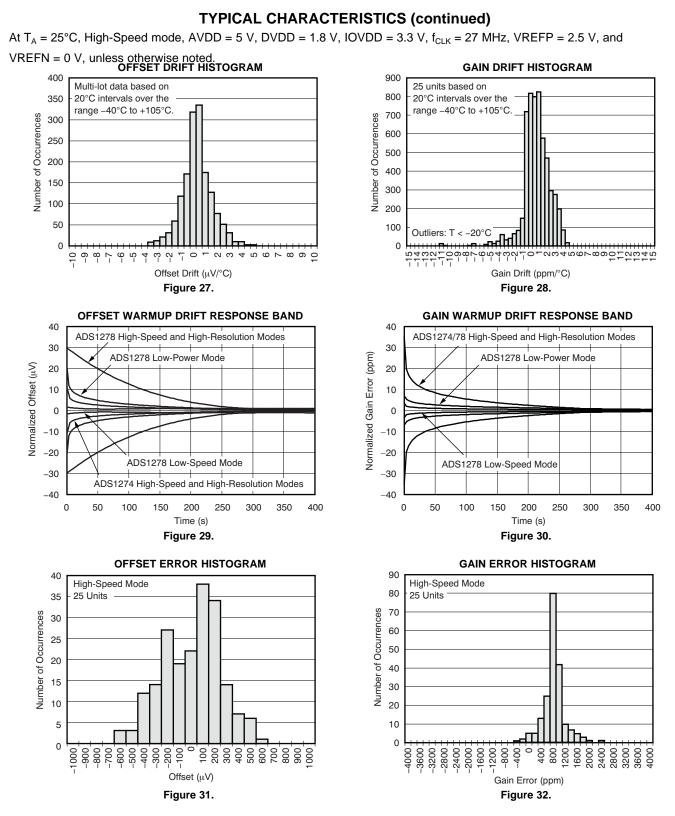

| Offset drift                                                  |                                |                                             |                    | 0.8           |               |                |                        |               | µV/°C                |

| Gain error                                                    |                                |                                             |                    | 0.1           | 0.5           |                |                        | 0.5           | % FSR                |

| Gain drift                                                    |                                |                                             |                    | 1.3           |               |                |                        |               | ppm/°C               |

|                                                               | High-Speed mode                | Shorted input                               |                    | 8.5           | 21            |                |                        | 21            | μV, rms              |

|                                                               | High-Resolution mode           | Shorted input                               |                    | 5.5           | 13            |                |                        | 13            | μV, rms              |

| Noise                                                         | Low-Power mode                 | Shorted input                               |                    | 8.5           | 21            |                |                        | 21            | μV, rms              |

|                                                               | Low-Speed mode                 | Shorted input                               |                    | 8.0           | 21            |                |                        | 21            | μV, rms              |

| Common-mode re                                                | jection                        | $f_{CM} = 60Hz$                             | 90                 | 108           |               | 90             |                        |               | dB                   |

|                                                               | AVDD                           |                                             |                    | 80            |               |                | 80                     |               | dB                   |

| Power-supply<br>rejection                                     | DVDD                           | f <sub>PS</sub> = 60Hz                      |                    | 85            |               |                | 85                     |               | dB                   |

| rejection                                                     | IOVDD                          |                                             |                    | 105           |               |                | 102                    |               | dB                   |

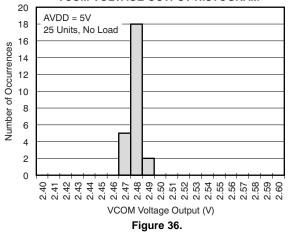

| V <sub>COM</sub> output voltage                               | je                             | No load                                     |                    | AVDD/2        |               |                | AVDD/2                 |               | V                    |

| AC Performance                                                |                                | +                                           | 1                  |               |               |                |                        |               |                      |

| Crosstalk                                                     |                                | f = 1kHz, -0.5dBFS <sup>(6)</sup>           |                    | -107          |               |                |                        |               | dB                   |

|                                                               | High-Speed mode                |                                             | 98                 | 106           |               | 96             |                        |               | dB                   |

| Signal to poice                                               |                                | V <sub>REF</sub> = 2.5V                     | 101                | 110           |               | 101            |                        |               | dB                   |

| Signal-to-noise<br>ratio (SNR) <sup>(7)</sup><br>(unweighted) | High-Resolution mode           | V <sub>REF</sub> = 3V                       |                    | 111           |               |                |                        |               | dB                   |

|                                                               | Low-Power mode                 |                                             | 98                 | 106           |               | 97             |                        |               | dB                   |

|                                                               | Low-Speed mode                 |                                             | 98                 | 107           |               | 98             |                        |               | dB                   |

| Total harmonic dis                                            |                                | V <sub>IN</sub> = 1kHz, –0.5dBFS            |                    | -108          | -96           |                |                        | -96           | dB                   |

| Spurious-free dyna                                            |                                |                                             |                    | 109           |               |                |                        |               | dB                   |

| Passband ripple                                               | <u> </u>                       |                                             |                    | ±0.005        |               |                |                        |               | dB                   |

(1) Minimum and maximum parameters are characterized for operation at  $T_A = 175^{\circ}C$  but may not be production tested at that temperature. Production test limits with statistical guardbands are used to ensure high temperature performance.

(2)  $FSR = full-scale range = 2V_{REF}$ .

(3)  $f_{CLK} = 32.768MHz$  max for High-Speed mode, and 27MHz max for all other modes. When  $f_{CLK} > 27MHz$ , operation is limited to Frame-Sync mode and  $V_{REF} \le 2.6V$ .

(4) SPS = samples per second.

(5) Best fit method.

- (6) Worst-case channel crosstalk between one or more channels.

- (7) Minimum SNR is ensured by the limit of the DC noise specification.

- (8) THD includes the first nine harmonics of the input signal; Low-Speed mode includes the first five harmonics.

Copyright © 2009–2013, Texas Instruments Incorporated

www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = T_J = -55^{\circ}$ C to 210°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

|                                  |                      |                                             | T <sub>A</sub> = -         | -55°C to 12          | 5°C                                         | T <sub>A</sub> = 210°C <sup>(1)</sup> |      |               |      |

|----------------------------------|----------------------|---------------------------------------------|----------------------------|----------------------|---------------------------------------------|---------------------------------------|------|---------------|------|

| PA                               | ARAMETER             | TEST CONDITIONS                             | MIN                        | ТҮР                  | MAX                                         | MIN                                   | TYP  | MAX           | UNIT |

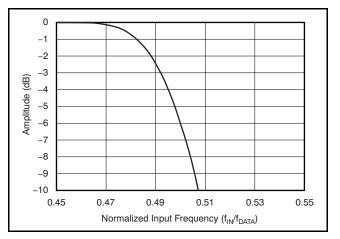

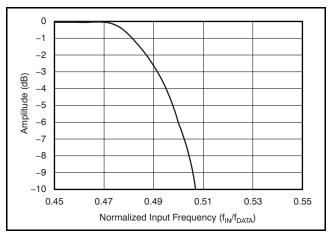

| Passband                         |                      |                                             |                            | 0.453                |                                             |                                       |      |               | Hz   |

| -3dB Bandwidth                   |                      |                                             |                            |                      | f <sub>DATA</sub><br>0.49 f <sub>DATA</sub> |                                       |      |               | Hz   |

| Stop band                        | High-Resolution mode |                                             | 95                         | UNITA DATA           |                                             |                                       |      |               | dB   |

| attenuation                      | All other modes      |                                             | 100                        |                      |                                             |                                       |      |               | u.D  |

|                                  |                      |                                             | 0.547                      |                      | 127.453                                     |                                       |      |               |      |

| Stop band                        | High-Resolution mode |                                             | f <sub>DATA</sub>          |                      | f <sub>DATA</sub>                           |                                       |      |               | Hz   |

| Stop band                        | All other modes      |                                             | 0.547<br>f <sub>DATA</sub> |                      | 63.453<br>f <sub>DATA</sub>                 |                                       |      |               | Hz   |

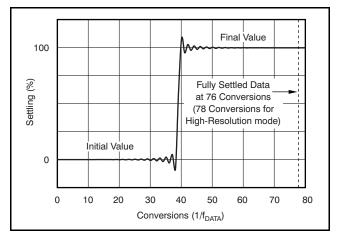

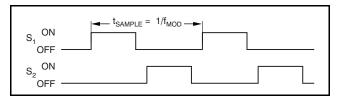

| Crown dolou                      | High-Resolution mode |                                             |                            | 39/f <sub>DATA</sub> |                                             |                                       |      |               | S    |

| Group delay                      | All other modes      |                                             |                            | 38/f <sub>DATA</sub> |                                             |                                       |      |               | S    |

| Settling time                    | High-Resolution mode | Complete settling                           |                            | 78/f <sub>DATA</sub> |                                             |                                       |      |               | S    |

| (latency) All other modes        |                      | Complete settling                           |                            | 76/f <sub>DATA</sub> |                                             |                                       |      |               | s    |

| Voltage Reference                | ce Inputs            |                                             | 1                          |                      |                                             |                                       |      |               |      |

| Reference input v                | oltage (VPEE)        | f <sub>CLK</sub> = 27MHz                    | 0.5                        | 2.5                  | 3.1                                         | 0.5                                   | 2.5  | 3.1           | V    |

| $(V_{REF} = VREFP -$             | VREFN)               | f <sub>CLK</sub> = 32.768MHz <sup>(3)</sup> | 0.5                        | 2.5                  | 2.6                                         | 0.5                                   | 2.5  | 2.6           | V    |

| Negative reference input (VREFN) |                      |                                             | AGND -<br>0.1              |                      | AGND +<br>0.1                               | AGND –<br>0.1                         |      | AGND +<br>0.1 | V    |

| Positive reference               | e input (VREFP)      |                                             | VREFN +<br>0.5             |                      | AVDD +<br>0.1                               | VREFN +<br>0.5                        |      | AVDD +<br>0.1 | V    |

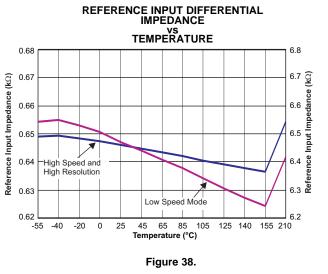

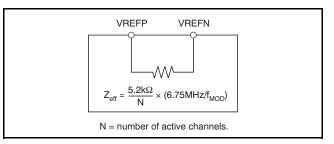

|                                  | High-Speed mode      |                                             |                            | 0.65                 |                                             |                                       | 0.65 |               | kΩ   |

| Reference Input<br>impedance     | High-Resolution mode |                                             |                            | 0.65                 |                                             |                                       | 0.65 |               | kΩ   |

|                                  | Low-Power mode       |                                             |                            | 1.3                  |                                             |                                       | 1.3  |               | kΩ   |

|                                  | Low-Speed mode       |                                             |                            | 6.5                  |                                             |                                       | 6.5  |               | kΩ   |

| Digital Input/Out<br>3.6V)       | put (IOVDD = 1.8V to |                                             |                            |                      |                                             |                                       |      | ·             |      |

| VIH                              |                      |                                             | 0.7<br>IOVDD               |                      | IOVDD                                       | 0.7<br>IOVDD                          |      | IOVDD         | V    |

| V <sub>IL</sub>                  |                      |                                             | DGND                       |                      | 0.3<br>IOVDD                                | DGND                                  |      | 0.3<br>IOVDD  | V    |

| V <sub>OH</sub>                  |                      | I <sub>OH</sub> = 4mA                       | 0.8<br>IOVDD               |                      | IOVDD                                       | 0.8<br>IOVDD                          |      | IOVDD         | V    |

| V <sub>OL</sub>                  |                      | I <sub>OL</sub> = 4mA                       | DGND                       |                      | 0.2<br>IOVDD                                | DGND                                  |      | 0.2<br>IOVDD  | V    |

| Input leakage                    |                      | 0 < V <sub>IN DIGITAL</sub> < IOVDD         |                            |                      | ±10                                         |                                       |      |               | μA   |

| Master clock rate                | (four)               | High-Speed mode <sup>(9)</sup>              | 0.1                        |                      | 32.768                                      | 0.1                                   |      | 32.768        | MH:  |

|                                  | (ICLK)               | Other modes                                 | 0.1                        |                      | 27                                          | 0.1                                   |      | 27            | MH:  |

| Power Supply                     |                      | T                                           | 1                          |                      |                                             |                                       |      |               |      |

| AVDD                             |                      |                                             | 4.75                       | 5                    | 5.25                                        | 4.75                                  | 5    | 5.25          | V    |

| DVDD                             |                      |                                             | 1.65                       | 1.8                  | 1.95                                        | 1.65                                  | 1.8  | 1.95          | V    |

| IOVDD                            | 1                    |                                             | 1.65                       |                      | 3.6                                         | 1.65                                  |      | 3.6           | V    |

|                                  | AVDD                 |                                             |                            | 1                    | 10                                          |                                       | 65   |               | μA   |

| Power-down<br>current            | DVDD                 |                                             |                            | 1                    | 50                                          |                                       | 200  |               | μA   |

|                                  | IOVDD                |                                             |                            | 1                    | 11                                          |                                       | 25   |               | μA   |

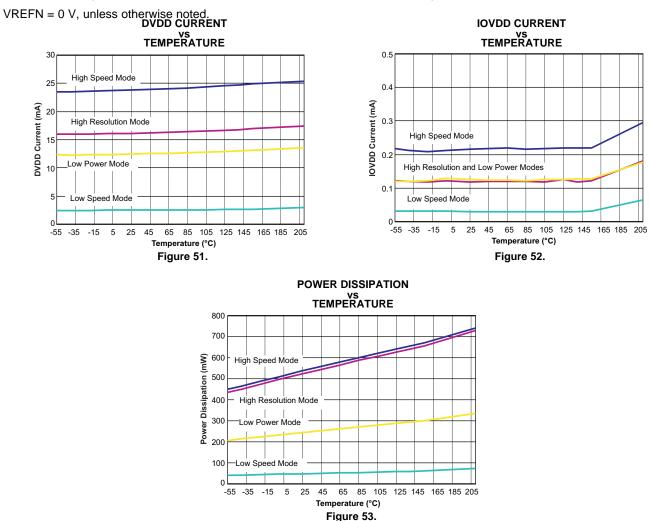

|                                  | High-Speed mode      |                                             |                            | 97                   | 145                                         |                                       | 135  | 185           | mA   |

|                                  | High-Resolution mode |                                             |                            | 97                   | 145                                         |                                       | 135  | 185           | mA   |

| AVDD current                     | Low-Power mode       |                                             |                            | 44                   | 64                                          |                                       | 60   | 84            | mA   |

|                                  | Low-Speed mode       |                                             |                            | 9                    | 14                                          |                                       | 12   | 22            | mA   |

(9)  $f_{CLK} = 32.768MHz$  max for High-Speed mode, and 27MHz max for all other modes. When  $f_{CLK} > 27MHz$ , operation is limited to Frame-Sync mode and  $V_{REF} \le 2.6V$ .

## ADS1278-HT

SBAS447E - MARCH 2009-REVISED APRIL 2013

www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = T_J = -55^{\circ}$ C to 210°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

|                   |                      |                 | T <sub>A</sub> = -5 | T <sub>A</sub> = –55°C to 125°C |     | T <sub>A</sub> = | 210°C <sup>(1)</sup> |      |      |

|-------------------|----------------------|-----------------|---------------------|---------------------------------|-----|------------------|----------------------|------|------|

| PA                | RAMETER              | TEST CONDITIONS | MIN                 | ТҮР                             | MAX | MIN              | TYP                  | MAX  | UNIT |

|                   | High-Speed mode      |                 |                     | 23                              | 30  |                  | 24                   | 31   | mA   |

| DVDD current      | High-Resolution mode |                 |                     | 16                              | 20  |                  | 17                   | 20   | mA   |

|                   | Low-Power mode       |                 |                     | 12                              | 17  |                  | 13                   | 17   | mA   |

|                   | Low-Speed mode       |                 |                     | 2.5                             | 4.5 |                  | 3                    | 5    | mA   |

|                   | High-Speed mode      |                 |                     | 0.25                            | 1   |                  | 0.3                  | 1.15 | mA   |

| IOVDD current     | High-Resolution mode |                 |                     | 0.125                           | 0.6 |                  | 0.2                  | 0.75 | mA   |

| IOVDD current     | Low-Power mode       |                 |                     | 0.125                           | 0.6 |                  | 0.2                  | 0.75 | mA   |

|                   | Low-Speed mode       |                 |                     | 0.035                           | 0.3 |                  | 0.1                  | 0.45 | mA   |

|                   | High-Speed mode      |                 |                     | 530                             | 785 |                  |                      | 985  | mW   |

| Power dissipation | High-Resolution mode |                 |                     | 515                             | 765 |                  |                      | 985  | mW   |

|                   | Low-Power mode       |                 |                     | 245                             | 355 |                  |                      | 455  | mW   |

|                   | Low-Speed mode       |                 |                     | 50                              | 80  |                  |                      | 120  | mW   |

www.ti.com

## ELECTRICAL CHARACTERISTICS

All specifications at  $T_A = -55^{\circ}$ C to 175°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

|                                                            |                          |                                             | T <sub>A</sub> = -55°C to 1 | 75°C (PAP P             | ackage)       |                      |

|------------------------------------------------------------|--------------------------|---------------------------------------------|-----------------------------|-------------------------|---------------|----------------------|

| P                                                          | ARAMETER                 | TEST CONDITIONS                             | MIN                         | TYP                     | MAX           | UNIT                 |

| Analog Inputs                                              |                          |                                             | -                           |                         |               |                      |

| Full-scale input voltage                                   | (FSR <sup>(1)</sup> )    | $V_{IN} = (AINP - AINN)$                    |                             | $\pm V_{REF}$           |               | V                    |

| Absolute input voltage                                     |                          | AINP or AINN to AGND                        | AGND – 0.1                  |                         | AVDD +<br>0.1 | V                    |

| Common-mode input vo                                       | Itage (V <sub>CM</sub> ) | $V_{CM} = (AINP + AINN)/2$                  |                             | 2.5                     |               | V                    |

|                                                            | High-Speed mode          |                                             |                             | 14                      |               | kΩ                   |

| Differential input<br>impedance                            | High-Resolution mode     |                                             |                             | 14                      |               | kΩ                   |

|                                                            | Low-Power mode           |                                             |                             | 28                      |               | kΩ                   |

|                                                            | Low-Speed mode           |                                             |                             | 140                     |               | kΩ                   |

| DC Performance                                             |                          |                                             |                             |                         | I             |                      |

| Resolution                                                 |                          | No missing codes                            | 24                          |                         |               | Bits                 |

|                                                            |                          | f <sub>CLK</sub> = 32.768MHz <sup>(2)</sup> |                             | 128,000                 |               | SPS                  |

|                                                            | High-Speed mode          | f <sub>CLK</sub> = 27MHz                    |                             | 105,469                 |               | SPS <sup>(3)</sup>   |

| Data rate (f <sub>DATA</sub> )                             | High-Resolution mode     |                                             |                             | 52,734                  |               | SPS                  |

|                                                            | Low-Power mode           |                                             |                             | 52,734                  |               | SPS                  |

|                                                            | Low-Speed mode           |                                             |                             | 10,547                  |               | SPS                  |

| Integral nonlinearity (INL                                 | ) <sup>(4)</sup>         | Differential input, $V_{CM} = 2.5V$         |                             | ±0.0003                 | ±0.0015       | % FSR <sup>(1)</sup> |

| Offset error                                               |                          |                                             |                             | 0.25                    | 3             | mV                   |

| Offset drift                                               |                          |                                             |                             | 0.8                     |               | µV/°C                |

| Gain error                                                 |                          |                                             |                             | 0.1                     | 0.5           | % FSR                |

| Gain drift                                                 |                          |                                             |                             | 1.3                     |               | ppm/°C               |

|                                                            | High-Speed mode          | Shorted input                               |                             | 8.5                     | 68            | μV, rms              |

|                                                            | High-Resolution mode     | Shorted input                               |                             | 5.5                     | 13            | μV, rms              |

| Noise                                                      | Low-Power mode           | Shorted input                               |                             | 8.5                     | 21            | μV, rms              |

|                                                            | Low-Speed mode           | Shorted input                               |                             | 8.0                     | 21            | μV, rms              |

| Common-mode rejectior                                      | 1                        | f <sub>CM</sub> = 60Hz                      | 90                          | 108                     |               | dB                   |

|                                                            | AVDD                     |                                             |                             | 80                      |               | dB                   |

| Power-supply rejection                                     | DVDD                     | f <sub>PS</sub> = 60Hz                      |                             | 85                      |               | dB                   |

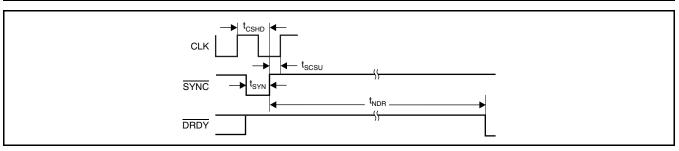

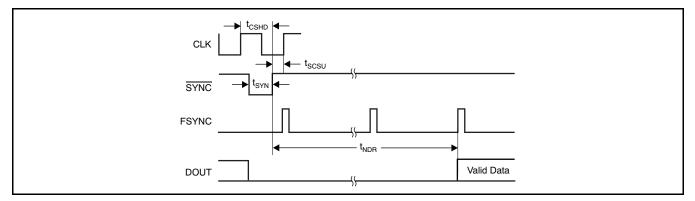

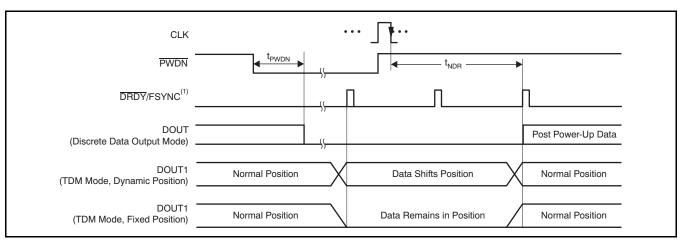

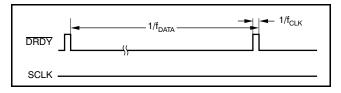

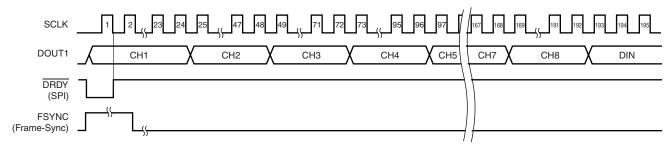

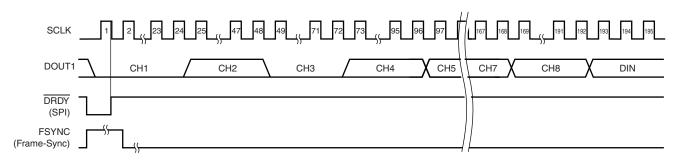

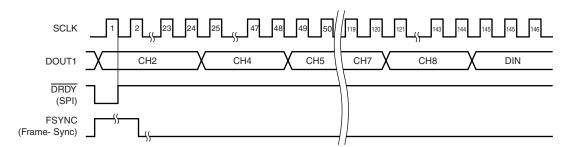

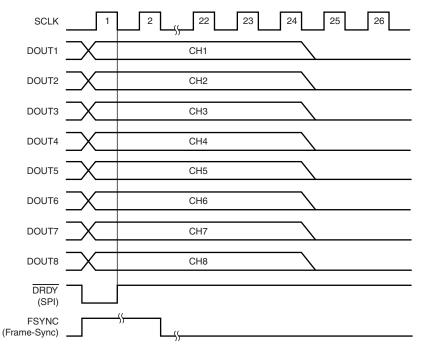

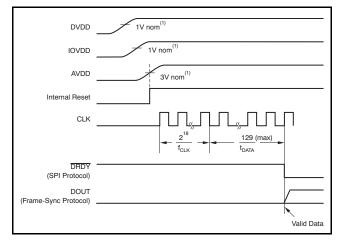

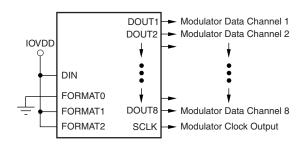

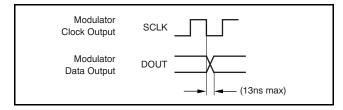

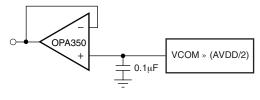

|                                                            | IOVDD                    |                                             |                             | 105                     |               | dB                   |