DRV8860, DRV8860A

## SLRS065E - SEPTEMBER 2013-REVISED NOVEMBER 2015

## DRV8860x 38-V 8-Channel Serial Interface Low-Side Driver

#### **Features**

- 8-Channel Protected Low-side Driver

- Eight NMOS FETs with Overcurrent Protection

- Integrated Inductive Catch Diodes

- Serial Interface

- Open/Short Load Detection (DRV8860 only)

- Configurable 100% Output Timing

- Configurable PWM Duty Cycle

- Continuous Current Driving Capability

- 560 mA (Single Channel on) PW and PWP

- 200 mA (8 Channels on) PW

- 330 mA (8 Channels on) PWP

- Support Parallel Configuration

- 8 V to 38 V Supply Voltage Range

- Input Digital Noise Filter for Noise Immunity

- Internal Data Read Back Capability for Reliable Control

- Protection and Diagnostic Features

- Overcurrent Protection (OCP)

- Open Load Detection (OL)

- Overtemperature Shutdown (OTS)

- Undervoltage Lockout (UVLO)

- Individual Channel Status Report

- Fault Condition Alarm

## 2 Applications

- Relays, Unipolar Stepper Motors

- Solenoids, Electromagnetic Drivers

- General Low-side Switch Applications

- LED driver with dimmer functionality (DRV8860A)

## 3 Description

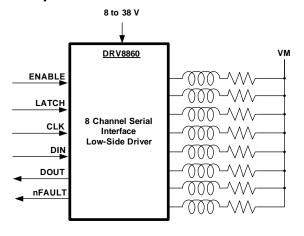

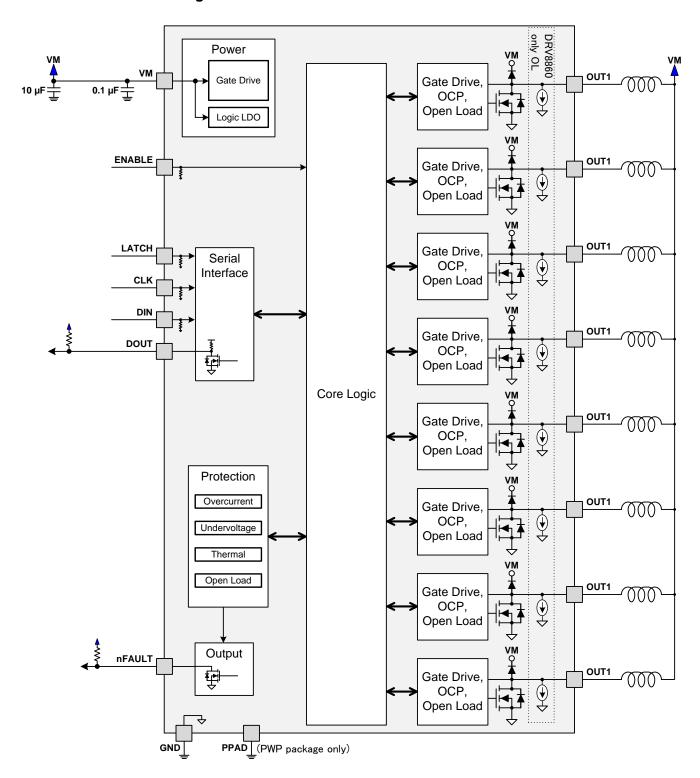

The DRV8860 provides an 8-channel low side driver with overcurrent protection and open/shorted load detection. It has built-in diodes to clamp turn-off transients generated by inductive loads, and can be used to drive unipolar stepper motors, DC motors, relays, solenoids, or other loads.

The PWP package can supply up to 330 mA x 8 channel and The PW package can supply up to 200 mA × 8 channel continuous output current. A single channel can deliver up to 560 mA continuous output current.

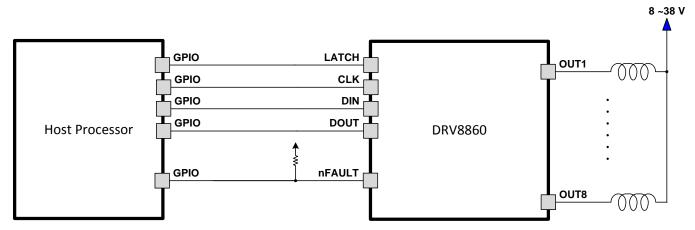

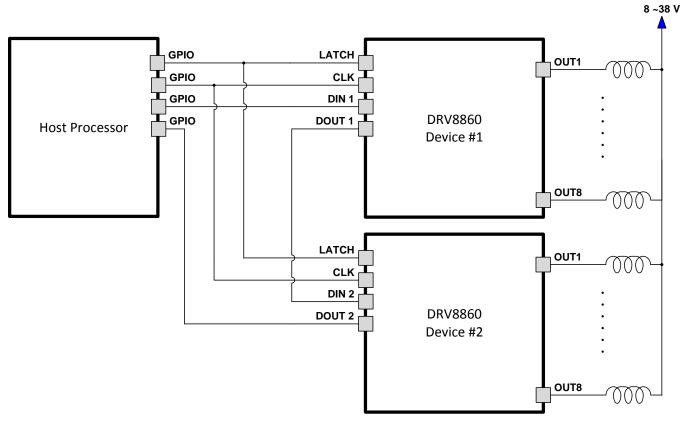

A serial interface is provided to control the DRV8860 output drivers, configure internal setting register and read the fault status of each channel. DRV8860 devices can be daisy-chained together to use a single serial interface. Energizing-time and holding-PWM-Duty cycles are configurable through serial interface as well. These functions allow for cooler running than always-on solutions.

Internal shutdown functions provided for are overcurrent protection, short-circuit protection, undervoltage lockout, and overtemperature. DRV8860A does not include open load detection. Fault information for each channel can be read out through serial interface and indicated by an external fault pin.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |

|-------------|-------------|-------------------|

| DDV/0000    | TSSOP (16)  | 5.00 mm × 6.40 mm |

| DRV8860     | HTSSOP (16) | 5.00 mm × 4.40 mm |

| DRV8860A    | TSSOP (16)  | 5.00 mm × 6.40 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

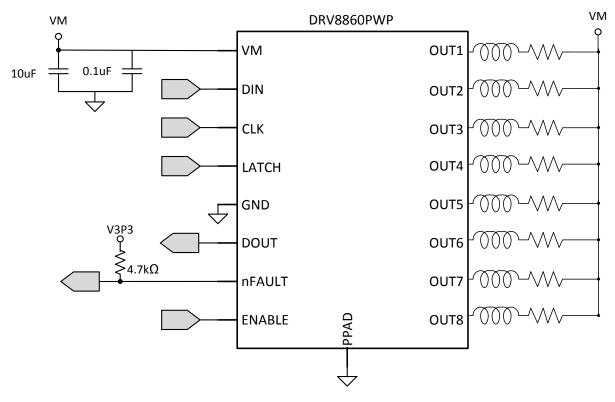

## **Simplified Schematic**

## **Table of Contents**

| 1 | Features 1                                      |    | 8.4 Device Functional Modes                      | 14               |

|---|-------------------------------------------------|----|--------------------------------------------------|------------------|

| 2 | Applications 1                                  |    | 8.5 Programming                                  | 16               |

| 3 | Description 1                                   |    | 8.6 Register Maps                                | 27               |

| 4 | Simplified Schematic1                           | 9  | Application and Implementation                   | 28               |

| 5 | Revision History2                               |    | 9.1 Application Information                      | 28               |

| 6 | Pin Configuration and Functions 4               |    | 9.2 Typical Application                          | 28               |

| 7 | _                                               | 10 | Power Supply Recommendations                     | 30               |

| ′ | Specifications 5 7.1 Absolute Maximum Ratings 5 |    | 10.1 Power Supply and Logic Sequencing           | 30               |

|   | g                                               | 11 | Layout                                           | <mark>3</mark> 1 |

|   | 7.2 Handling Ratings                            |    | 11.1 Layout Guidelines                           | 31               |

|   | 7.4 Thermal Information5                        |    | 11.2 Layout Example                              | 31               |

|   | 7.5 Electrical Characteristics 6                |    | 11.3 Thermal Consideration                       |                  |

|   |                                                 | 12 | Device and Documentation Support                 | 33               |

|   | 7.6 Timing Requirements                         |    | 12.1 Community Resources                         |                  |

| 8 | • •                                             |    | 12.2 Trademarks                                  |                  |

| 0 | Detailed Description 8                          |    | 12.3 Electrostatic Discharge Caution             |                  |

|   | 8.1 Overview                                    |    | 12.4 Glossary                                    |                  |

|   | 8.2 Functional Block Diagram                    | 13 | Mechanical, Packaging, and Orderable Information |                  |

## **5 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision D (October 2015) to Revision E                                          | Page |

|---|----------------------------------------------------------------------------------------------|------|

| • | Added timing diagrams Figure 1, Figure 2 and Table 2, Table 3                                | 7    |

| С | hanges from Revision C (October 2014) to Revision D                                          | Page |

| • | Added I <sub>(VM)</sub> MAX = 4.5 V                                                          | 6    |

| • | Added I <sub>OFF</sub> for DRV8860A                                                          |      |

| • | Changed t <sub>OCP</sub> From: MIN = 2.7 To: 2.0 µs                                          | 6    |

| • | Updated Functional Block Diagram                                                             | 9    |

| С | hanges from Revision B (July 2014) to Revision C                                             | Page |

| • | Added DRV8860A part to datasheet.                                                            | 1    |

| • | Added caption to Figure 9                                                                    | 14   |

| • | Added caption to Figure 10                                                                   |      |

| • | Moved the Serial Control Interface information into the Programming section of the datasheet |      |

| _ |                                                                                              | 16   |

| • | Moved the Register Maps information into the Detailed Description section of the datasheet   |      |

| • | Moved the Register Maps information into the Detailed Description section of the datasheet   | 27   |

Submit Documentation Feedback

| Cł | nanges from Revision A (November 2013) to Revision B                                                                                                                                                                    | Page         |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| •  | Added Feature: Serial Interface                                                                                                                                                                                         | 1            |

| •  | Changed the Features list for: Continuous Current Driving Capability                                                                                                                                                    | 1            |

| •  | Deleted Features: Programmable Current Profile                                                                                                                                                                          | 1            |

| •  | Updated the Application List                                                                                                                                                                                            | 1            |

| •  | Changed Description sentence From: These functions allow for lower temperature operation rather than traditional always-on solutions. To: These functions allow for cooler running than traditional always-on solutions |              |

| •  | Added the Handling Ratings table                                                                                                                                                                                        | <del>[</del> |

| •  | Changed the MIN value for VM in the Recommended Operating Conditions table From: 8.2 V To: 8 V                                                                                                                          | <del>[</del> |

| •  | Added HTTSSOP (PWP) to the Thermal Information table                                                                                                                                                                    | <del>[</del> |

| •  | Changed V <sub>IL</sub> From: MIN = - To: 0 V, TYP = 0.6 V To: -                                                                                                                                                        | 6            |

| •  | Changed V <sub>IH</sub> From: MIN = 2 V To: 1.5 V, MAX = - To: 5.3 V                                                                                                                                                    | (            |

| •  | Changed V <sub>HYS</sub> From: MIN = - To: 100 mV, TYP = 0.45 V To:                                                                                                                                                     | 6            |

| •  | Added the Timing Requirements table                                                                                                                                                                                     | 6            |

| •  | Added the Overview section                                                                                                                                                                                              | 8            |

| •  | Changed the description of the Recommended Output Current section                                                                                                                                                       | 10           |

| •  | Deleted the Example Output Configuration section.                                                                                                                                                                       | 12           |

| •  | Changed the Serial Control Interface description text                                                                                                                                                                   | 16           |

| Cł | nanges from Original (September 2013) to Revision A                                                                                                                                                                     | Page         |

| •  | Added Features: Programmable Current Profile                                                                                                                                                                            |              |

| •  | Changed the MIN value for VM in the Recommended Operating Conditions table From: 8 V To: 8.2 V                                                                                                                          |              |

| •  | Added the Example Output Configuration section.                                                                                                                                                                         | 12           |

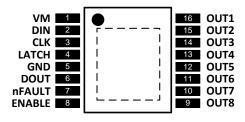

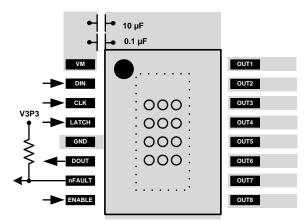

## 6 Pin Configuration and Functions

#### PW (TSSOP) PACKAGE (TOP VIEW)

# PWP (HTSSOP) PACKAGE (TOP VIEW)

## **Pin Functions**

| NAME   | PIN | I/O<br>(1) | DESCRIPTION                       | EXTERNAL COMPONENTS OR CONNECTIONS                                                                                                                               |  |

|--------|-----|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND    | 5   | _          | Device ground                     | All pins must be connected to ground                                                                                                                             |  |

| VM     | 1   | _          | Motor power supply                | Connect to motor supply voltage. Bypass to GND with a 0.1 $\mu$ F ceramic capacitor plus a 10 $\mu$ F electrolytic capacitor.                                    |  |

| ENABLE | 8   | I          | Output stage enable control input | Logic high to enable outputs, logic low to disable outputs. Internal logic and registers can be read and written to when ENABLE is logic low. Internal pulldown. |  |

| LATCH  | 4   | I          | Serial latch signal               | Refer to serial communication waveforms. Internal pulldown.                                                                                                      |  |

| CLK    | 3   | ı          | Serial clock input                | Rising edge clocks data into part for write operations. Falling edge clocks data out of part for read operations. Internal pulldown.                             |  |

| DIN    | 2   | I          | Serial data input                 | Serial data input from controller. Internal pulldown.                                                                                                            |  |

| DOUT   | 6   | 0          | Serial data output                | Serial data output to controller. Open-drain output with internal pullup.                                                                                        |  |

| nFAULT | 7   | OD         | Fault                             | Logic low when in fault condition. Open-drain output requires external pullup. Faults: OCP, OTS, UVLO, OL (DRV8860 only)                                         |  |

| OUT1   | 16  | 0          | Low-side output 1                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT2   | 15  | 0          | Low-side output 2                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT3   | 14  | 0          | Low-side output 3                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT4   | 13  | 0          | Low-side output 4                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT5   | 12  | 0          | Low-side output 5                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT6   | 11  | 0          | Low-side output 6                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT7   | 10  | 0          | Low-side output 7                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

| OUT8   | 9   | 0          | Low-side output 8                 | NFET output driver. Connect external load between this pin and VM                                                                                                |  |

(1) Directions: I = input, O = output, OD = open-drain output

## **Table 1. External Components**

| COMPONENT             | PIN 1               | PIN 2 RECOMMENDED |                                           |

|-----------------------|---------------------|-------------------|-------------------------------------------|

| 0                     |                     |                   | 0.1 μF ceramic capacitor rated for VM     |

| C <sub>(VM1)</sub>    | VIVI                | 10 μF electrolyt  | 10 μF electrolytic capacitor rated for VM |

| R <sub>(nFAULT)</sub> | V3P3 <sup>(1)</sup> | nFAULT            | > 4.7 kΩ                                  |

(1) V3P3 is not a pin on the DRV8860, but a V3P3 supply voltage pullup is required for open-drain output nFAULT.

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2) (3)

|                                             |                           | MIN  | MAX | UNIT |

|---------------------------------------------|---------------------------|------|-----|------|

| Power supply voltage range                  | VM                        | -0.3 | 40  | V    |

| Digital input pin current range             | ENABLE, LATCH, CLK, DIN   | 0    | 20  | mA   |

| Digital output pin voltage range            | DOUT, nFAULT              | -0.5 | 7   | V    |

| Digital output pin current                  | DOUT, nFAULT              | -0.5 | 7   | V    |

| Output voltage range                        | OUTx                      | -0.3 | 40  | V    |

| utput current range OUTx Internally limited |                           | Α    |     |      |

| Operating virtual junction temperat         | ure range, T <sub>J</sub> | -40  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

## 7.2 Handling Ratings

|                         |                                                                             |                                                                               | MIN  | MAX | UNIT |

|-------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>        | Storage temperature rang                                                    | e                                                                             | -60  | 150 | °C   |

| V Floring the discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | -2                                                                            | 2    | kV  |      |

| V(ESD)                  | V <sub>(ESD)</sub> Electrostatic discharge                                  | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -500 | 500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                     | MIN | NOM MAX | UNIT |

|------------------|-------------------------------------|-----|---------|------|

| VM               | Motor power supply voltage range    | 8   | 38      | V    |

| I <sub>OUT</sub> | Low-side driver current capability  |     | 560     | mA   |

| T <sub>A</sub>   | Operating ambient temperature range | -40 | 85      | °C   |

## 7.4 Thermal Information (1)

over operating free-air temperature range (unless otherwise noted)

|                         | THERMAL METRIC                               | TSSOP        | HTSSOP        | UNIT |

|-------------------------|----------------------------------------------|--------------|---------------|------|

|                         | THERMAL METRIC                               | PW (16 PINS) | PWP (16 PINS) | UNII |

| $\Theta_{JA}$           | Junction-to-ambient thermal resistance       | 103          | 40.9          | °C/W |

| $R_{\theta JC(TOP)}$    | Junction-to-case (top) thermal resistance    | 37.9         | 28.5          | °C/W |

| $R_{\theta JB}$         | Junction-to-board thermal resistance         | 48           | 23.2          | °C/W |

| $\Psi_{JT}$             | Junction-to-top characterization parameter   | 3            | 0.9           | °C/W |

| $\Psi_{JB}$             | Junction-to-board characterization parameter | 47.4         | 23.0          | °C/W |

| $R_{\theta JC(BOTTOM)}$ | Junction-to-case (bottom) thermal resistance | N/A          | 3.0           | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>2)</sup> All voltage values are with respect to network ground terminal.

<sup>(3)</sup> Power dissipation and thermal limits must be observed

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.5 Electrical Characteristics

$T_A = 25$ °C, over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                          | TEST CONDITIONS                                                     | MIN  | TYP  | MAX | UNIT |

|---------------------|------------------------------------|---------------------------------------------------------------------|------|------|-----|------|

| POWER               | SUPPLIES                           |                                                                     |      |      |     |      |

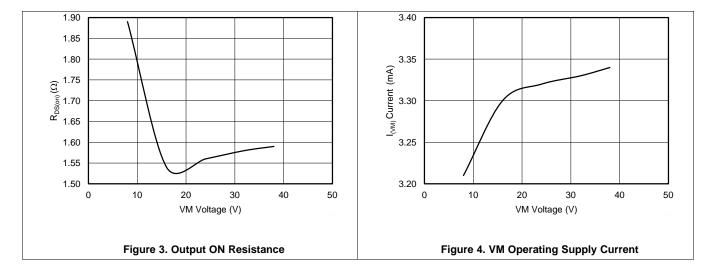

| I <sub>(VM)</sub>   | VM operating supply current        | VM = 24 V                                                           |      | 3    | 4.5 | mA   |

| V <sub>(UVLO)</sub> | VM undervoltage lockout voltage    | VM rising                                                           |      |      | 8.2 | V    |

| LOGIC-L             | EVEL INPUTS (DIN, CLK, LATCH, ENA  | ABLE)                                                               | ,    |      | ,   |      |

| V <sub>IL</sub>     | Input low voltage                  |                                                                     | 0    |      | 0.7 | V    |

| V <sub>IH</sub>     | Input high voltage                 |                                                                     | 1.5  |      | 5.3 | V    |

| V <sub>HYS</sub>    | Input hysteresis                   |                                                                     | 100  |      |     | mV   |

| I <sub>IL</sub>     | Input low current                  | V <sub>IN</sub> = 0                                                 | -20  |      | 20  | μA   |

| I <sub>IH</sub>     | Input high current                 | V <sub>IN</sub> = 3.3 V                                             |      |      | 100 | μA   |

| R <sub>PD</sub>     | Input pulldown resistance          |                                                                     |      | 100  |     | kΩ   |

| nFAULT,             | DOUT OUTPUTS (OPEN-DRAIN OUTF      | PUTS)                                                               |      |      |     |      |

| V <sub>OL</sub>     | Output low voltage                 | I <sub>O</sub> = 5 mA                                               |      |      | 0.5 | V    |

| I <sub>OH</sub>     | Output high leakage current        | V <sub>O</sub> = 3.3 V, nFAULT                                      | -1   |      | 1   | μΑ   |

| R <sub>PU</sub>     | Input pullup resistance            | DOUT only (Pull up to internal 5.7 V)                               |      | 1.4  |     | kΩ   |

| LOW-SID             | E FET DRIVERS                      |                                                                     |      |      |     |      |

| D                   | EET an anaistan an                 | VM = 24 V, I <sub>O</sub> = 150 mA, T <sub>J</sub> = 25°C           |      | 1.5  |     |      |

| R <sub>ds(on)</sub> | FET on resistance                  | $VM = 24 \text{ V}, I_O = 150 \text{ mA}, T_J = 85^{\circ}\text{C}$ |      | 1.8  |     | Ω    |

|                     | Off state leader we summed         | VM = 24 V, T <sub>J</sub> = 25°C, DRV8860                           | 0    | 30   |     |      |

| I <sub>OFF</sub>    | Off-state leakage current          | VM = 24 V, T <sub>J</sub> = 25°C, DRV8860A                          | -0.5 |      | 0.5 | μΑ   |

| HIGH-SIE            | DE FREE-WHEELING DIODES            |                                                                     |      |      |     |      |

| V <sub>F</sub>      | Diode forward voltage              | VM = 2 4V, I <sub>O</sub> = 150 mA, T <sub>J</sub> = 25°C           |      | 0.9  |     | V    |

| PROTEC              | TION CIRCUITS                      |                                                                     |      |      |     |      |

| I <sub>OCP</sub>    | Overcurrent protection trip level  | Each channel separately monitored                                   |      | 620  |     | mA   |

| I <sub>OL</sub>     | Open load detect pull-down current | Per channel, DRV8860 only                                           |      | 30   |     | μA   |

| V <sub>OL</sub>     | Open load detect threshold voltage | Per channel, DRV8860 only                                           |      | 1.2  |     | V    |

| T <sub>TSD</sub>    | Thermal shutdown temperature       | Die temperature                                                     | 150  | 160  | 180 | °C   |

| T <sub>HYS</sub>    | Thermal shutdown hysteresis        | Die temperature                                                     |      | 35   |     | °C   |

| PWM CH              | OPPING FREQUENCY                   |                                                                     |      |      | '   |      |

|                     |                                    | Duty cycle is > 25%                                                 | 45   | 50   | 55  |      |

| $f_{PWM}$           | PWM chopping frequency             | Duty cycle is 25%                                                   | 22   | 25   | 28  | kHz  |

|                     |                                    | Duty cycle is 12.5%                                                 | 11   | 12.5 | 14  |      |

## 7.6 Timing Requirements

|                  |                                      |                                                    | DAIL! | TVD | BAAY | LINIT |

|------------------|--------------------------------------|----------------------------------------------------|-------|-----|------|-------|

|                  |                                      |                                                    | MIN   | TYP | MAX  | UNIT  |

| $t_{F}$          | Fall time                            | I <sub>O</sub> = 150 mA, VM = 24 V, resistive load | 50    |     | 300  | ns    |

| t <sub>OCP</sub> | Overcurrent protection deglitch time | VM = 24 V                                          | 2.0   | 3.0 | 3.85 | μs    |

| t <sub>OL</sub>  | Open load detect deglitch time       | Each channel separately monitored                  | 14    | 17  | 20   | μs    |

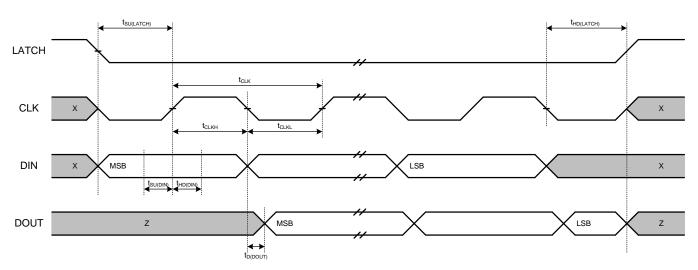

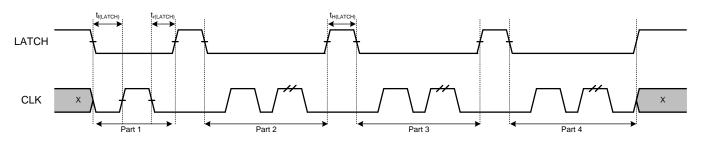

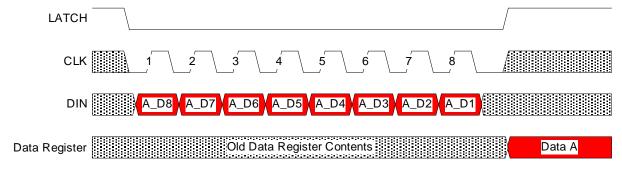

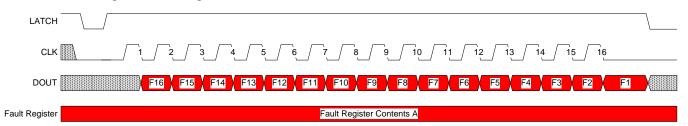

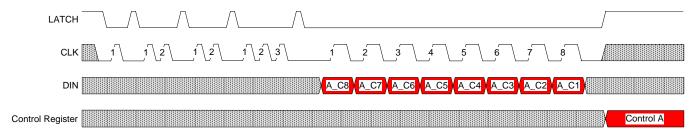

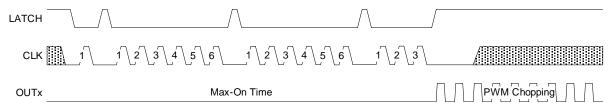

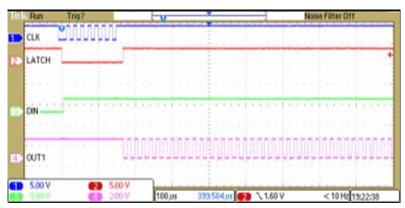

Figure 1. Serial Interface

**Table 2. Serial Timing**

| NO. | REF DES                 | DESCRIPTION                           | MIN | TYP | MAX | UNIT |

|-----|-------------------------|---------------------------------------|-----|-----|-----|------|

| 1   | t <sub>CLK</sub>        | CLK cycle time                        | 5   |     |     | μs   |

| 2   | t <sub>CLKH</sub>       | CLK high time                         | 2.5 |     |     | μs   |

| 3   | t <sub>CLKL</sub>       | CLK low time                          | 2.5 |     |     | μs   |

| 4   | t <sub>SU(DIN)</sub>    | Setup time, DIN to CLK                | 1   |     |     | μs   |

| 5   | t <sub>H(DIN)</sub>     | Hold time, DIN to CLK                 | 1   |     |     | μs   |

| 6   | t <sub>SU(LATCH)</sub>  | Setup time, LATCH to CLK              | 1   |     |     | μs   |

| 7   | t <sub>H(LATCH)</sub>   | Hold time, LATCH to CLK               | 1   |     |     | μs   |

| 8   | t <sub>OFF(LATCH)</sub> | Inactive time between writes and read | 2   |     |     | μs   |

| 9   | t <sub>D(DOUT)</sub>    | Delay time, CLK to DOUT               |     |     | 1.5 | μs   |

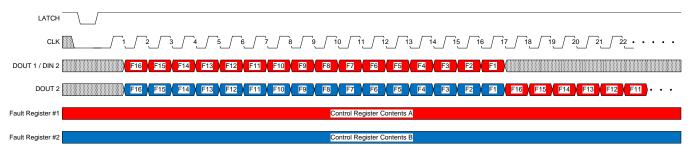

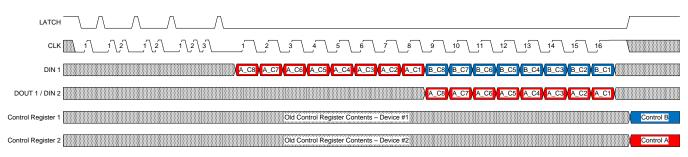

Figure 2. Special Commands

**Table 3. Special Commands**

| NO. | REF DES               | DESCRIPTION            | MIN | TYP | MAX | UNIT |

|-----|-----------------------|------------------------|-----|-----|-----|------|

| 10  | t <sub>f(LATCH)</sub> | LATCH fall to CLK rise | 1   |     |     | μs   |

| 11  | t <sub>r(LATCH)</sub> | CLK fall to LATCH rise | 1   |     |     | μs   |

| 12  | t <sub>H(LATCH)</sub> | LATCH high time        | 2   |     |     | μs   |

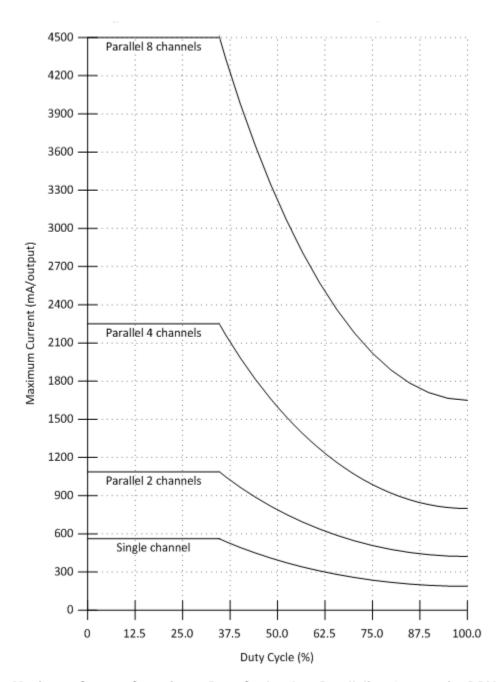

#### 7.7 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

The DRV8860 is an integrated 8-channel low side driver with overcurrent protection and open/short detection. It has built-in diodes to clamp turn-off transients generated by inductive loads, and can be used to drive unipolar stepper motors, DC motors, relays, solenoids, or other loads.

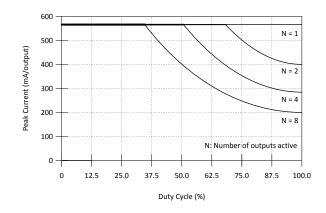

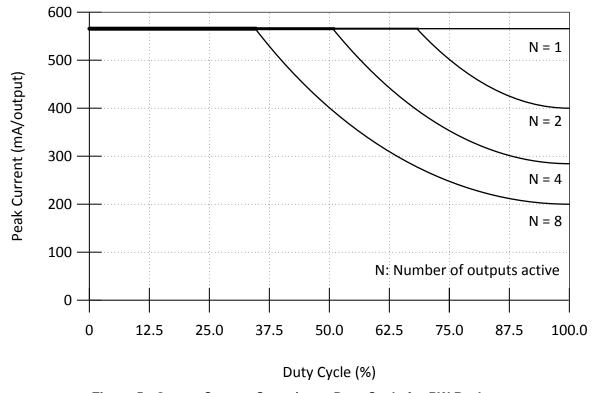

DRV8860 can supply up to 200 mA x 8 channel continuous output current. The current driving capability increases with lower PWM duty cycle. A single channel can deliver up to 560 mA continuous output current. Refer to the current capability table for details.

A serial interface is provided to control the DRV8860 output drivers, configure internal register settings, and read the fault status of each channel. Multiple DRV8860 devices can be daisy-chained together to use a single serial interface. Energizing-time and holding-PWM-duty cycle are configurable through the serial interface as well. These functions allow for cooler running than traditional always-on solutions.

Internal shutdown functions are provided for overcurrent protection, short-circuit protection, under voltage lockout and over temperature. DRV8860 can diagnosis an open load condition. DRV8860A does not include open load detection. Fault information for each channel can be read out through serial interface and is indicated by an external fault pin.

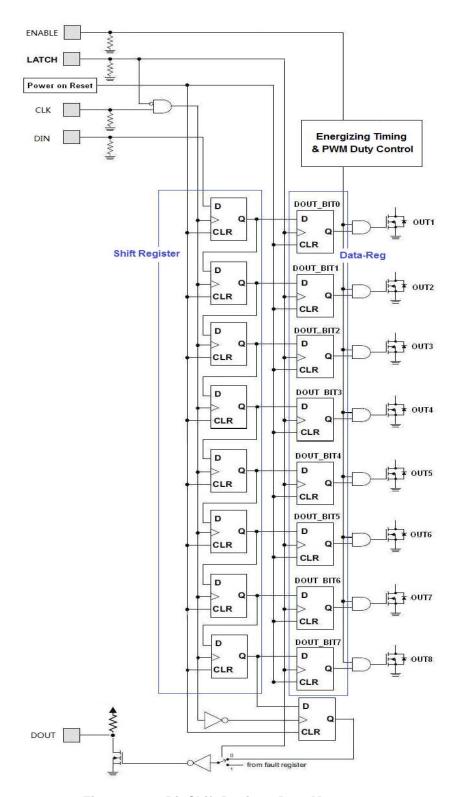

## 8.2 Functional Block Diagram

## 8.3 Feature Description

## 8.3.1 Recommended Output Current

DRV8860 current capability will depend on several system application parameters such as system ambient temperature, maximum case temperature, and overall output duty cycle. The PWP package provides a better heatsinking capability through the PowerPAD™; and therefore, is cable of driving higher output current or operating at a slightly lower temperature than the device in PW package.

| OUTPUT CURRENT RECOMMEND        | OUTPUT CURRENT RECOMMENDATION (PW PACKAGE) T <sub>A</sub> = 25°C |  |  |  |  |  |  |  |  |  |

|---------------------------------|------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| CONFIGURATION                   | OUTPUT CURRENT CAPACITY                                          |  |  |  |  |  |  |  |  |  |

| 1x output on (100% duty cycle)  | 566 mA                                                           |  |  |  |  |  |  |  |  |  |

| 2x outputs on (100% duty cycle) | 400 mA per output                                                |  |  |  |  |  |  |  |  |  |

| 4x outputs on (100% duty cycle) | 283 mA per output                                                |  |  |  |  |  |  |  |  |  |

| 8x outputs on (100% duty cycle) | 200 mA per output                                                |  |  |  |  |  |  |  |  |  |

Figure 5. Output Current Capacity vs Duty Cycle for PW Package

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

Figure 6. Maximum Current Capacity vs Duty Cycle when Paralleling Outputs for DRV8860PW

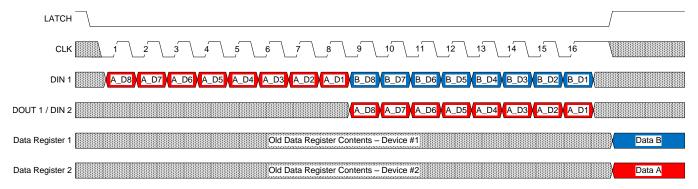

## 8.3.2 Daisy Chain Connection

Two or more DRV8860 devices may be connected together to use a single serial interface. The SDATOUT pin of the first device in the chain is connected to the SDATIN pin of the next device. The SCLK, LATCH, RESET, and nFAULT pins are connected together.

Timing diagrams are shown in Figure 7 and Figure 8 for the configuration of single devices, as well as two devices in daisy-chain connection.

Figure 7. Single Device Connection

Figure 8. Daisy-Chain Connection

#### 8.3.3 Protection Circuits

The DRV8860 is fully protected against undervoltage, overcurrent and overtemperature events.

## 8.3.3.1 Overcurrent Protection (OCP)

When output current exceeds OCP trigger level, corresponding channel will be automatically turned off. nFault pin will be set low and corresponding OCP flag in fault register will be set to 1.

Over current faults are automatically cleared whenever the corresponding output is turned off by setting the Data register bit to '0'. Alternatively, a Fault Reset special command will also clear this value. In either case, once all bits in the Fault register are clear, nFAULT is released.

## 8.3.3.2 Open Load Detection (OL) - DRV8860 only

When any output is in off status (the corresponding Data Register bit is set to '0'), a current sink pulls the node down with approximately 30  $\mu$ A. If the voltage on the pin is sensed to be less than 1.2 V, then an open load condition is reported. nFAULT is driven low and the OL bit of the fault register (F8:F1) corresponding to the specific channel is set.

Open load faults are automatically cleared whenever the corresponding output is turned on by setting the Data register bit to '1'. Alternatively, a Fault Reset special command will also clear this value. In either case, once all bits in the Fault register are clear, nFAULT is released.

## 8.3.3.3 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all outputs will be disabled, and the nFAULT pin will be driven low. Once the die temperature has fallen to a safe level, operation will automatically resume. The nFAULT pin will be released after operation has resumed.

## 8.3.3.4 Undervoltage Lockout (UVLO)

If at any time the voltage on the VM pin falls below the undervoltage lockout threshold voltage, all circuitry in the device will be disabled and internal logic will be reset. Operation will resume when VM rises above the UVLO threshold. nFAULT will not be asserted in this condition.

#### 8.3.3.5 Digital Noise Filter

The DRV8860 features an internal noise filter on all digital inputs. In a noisy system, noise may disturb the serial daisy-chain interface. Without an input filter, this noise may result in an unexpected behavior or output state. The digital input filter is capable of removing unwanted noise frequencies while allowing fast communication over the serial interface.

#### 8.4 Device Functional Modes

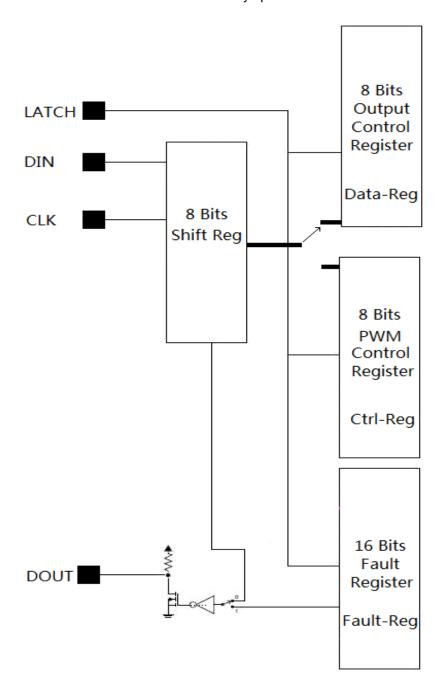

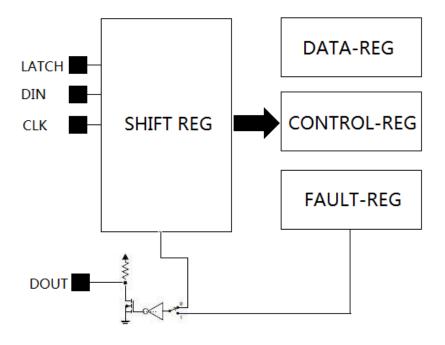

## 8.4.1 Internal Registers

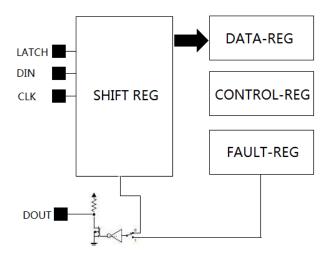

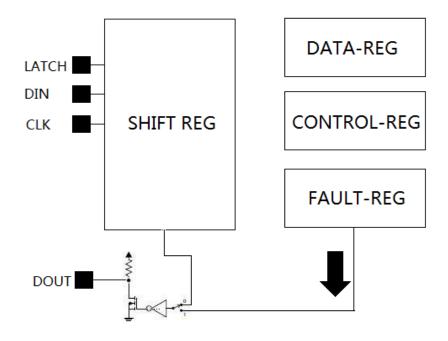

The DRV8860 is controlled with a simple serial interface. There are three register banks that are used during operation: the Data register, the Control register, and the Fault register.

Register data movement flow and direction will be affected by special command.

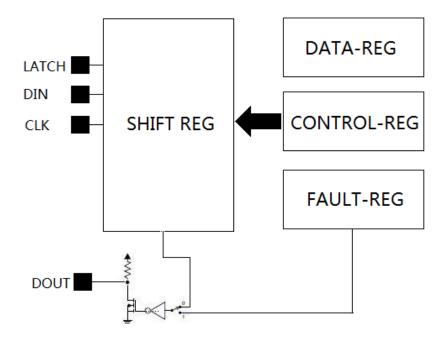

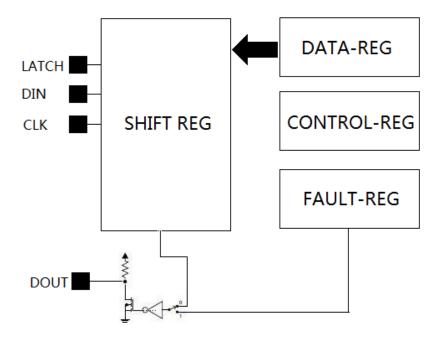

Figure 9. Register Data Movement

In default condition, 8 Bit shift register data moves into output control register DATA-REG.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

## **Device Functional Modes (continued)**

Figure 10. 8 Bit Shift Register Data Movement

#### 8.5 Programming

## 8.5.1 Serial Control Interface

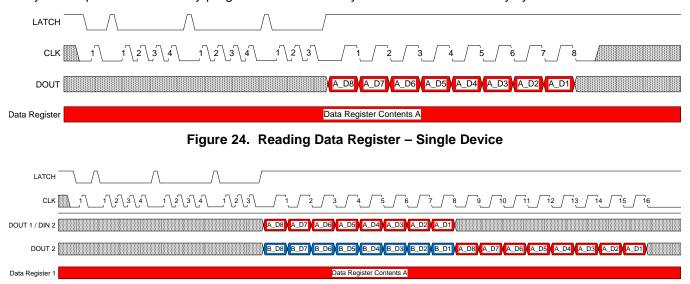

DRV8860 is using a daisy chain serial interface. Data is latched into the register on the rising edge of the LATCH pin. Data is clocked in on the rising edge of CLK when writing, and data is clocked out on the falling edge of CLK when reading.

## 8.5.1.1 Data Writing Waveform

Figure 11. Writing Data Register – Single Device

Figure 12. Writing Data Register - Daisy Chan

Figure 13. Writing Data Register - Data Flow

## **Programming (continued)**

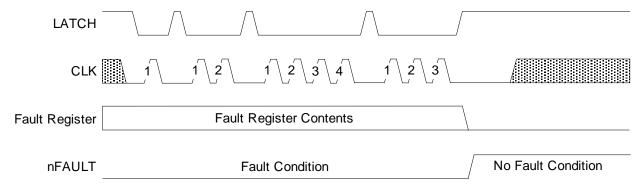

## 8.5.1.2 Fault Register Reading Waveform

Figure 14. Reading Fault Register - Single Device

Figure 15. Reading Fault Register - Daisy Chain

Figure 16. Reading Fault Register - Data Flow

## **Programming (continued)**

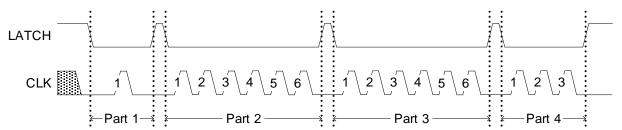

## 8.5.1.3 Special Command

Besides output ON/OFF control and fault status reading back, DRV8860 has special functions to make system more robust or power efficient. These functions will need special command to initiate the device or configure the internal registers.

There are 5 Special Commands:

- 1. Write Control Register command

- 2. Read Control Register command

- 3. Read Data Register command

- 4. Fault Register Reset command

- 5. PWM Start command

Special wave form pattern on CLK and LATCH pin will issue the special command, as below

Figure 17. Special Command

| SPECIAL COMMAND        | CLK CYCLES IN EACH PART |        |        |        |  |  |  |  |  |

|------------------------|-------------------------|--------|--------|--------|--|--|--|--|--|

| SPECIAL COMMAND        | Part 1                  | Part 2 | Part 3 | Part 4 |  |  |  |  |  |

| Write Control Register | 1                       | 2      | 2      | 3      |  |  |  |  |  |

| Read Control Register  | 1                       | 4      | 2      | 3      |  |  |  |  |  |

| Read Data Register     | 1                       | 4      | 4      | 3      |  |  |  |  |  |

| Fault Register Reset   | 1                       | 2      | 4      | 3      |  |  |  |  |  |

| PWM Start              | 1                       | 6      | 6      | 3      |  |  |  |  |  |

## 8.5.1.3.1 Special command: Write Control Register

When Write-Control-Register command is issued, the following serial data will be latched into timing and duty control register.

Figure 18. Writing Control Register - Single Device

Figure 19. Writing Control Register - Daisy Chain

Figure 20. Writing Control Register - Data Flow

Copyright © 2013–2015, Texas Instruments Incorporated

Control Register #1

Control Register #2

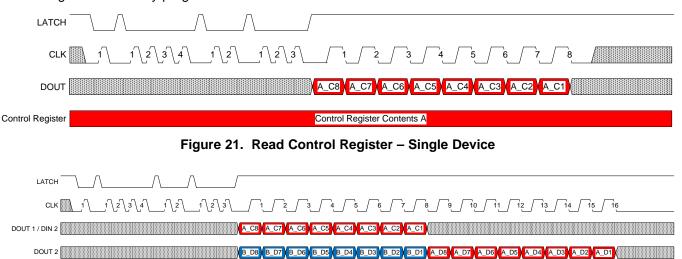

## 8.5.1.3.2 Special command: Read Control Register

When Read-Control-Register command is issued, control register content will be copied to internal shift register and following CLK will shift this content out from DOUT pin. This provides a mechanism for system to verify the control register is correctly programmed.

Figure 22. Read Control Register - Daisy Chain

Control Register Contents B

Figure 23. Read Control Register - Data Flow

Data Register 2

## 8.5.1.3.3 Special command: Read Data Register

When Read-Data-Register command is issued, internal output data register content will be copied to internal shift register and following CLK will shift this content out from DOUT pin. This provides a mechanism for system to verify the output data is correctly programmed. It makes system more robust in noisy system.

Figure 25. Reading Data Register - Daisy Chain

Figure 26. Reading Data Register - Data Flow

Submit Documentation Feedback

## 8.5.1.3.4 Special command: Fault Register Reset

When Fault-Register-Reset command is issued, internal 16bit fault register will be cleared. System can use this method to clear out all fault condition in every chained device at once.

Figure 27. Fault Register Reset

#### 8.5.1.3.5 Special command: PWM Start

When Fault-Register-Reset command is issued, output channel will ignore energizing time and directly enter into PWM mode following the setting in control register.

Figure 28. PWM Start Command

## 8.5.1.4 Output Energizing and PWM Control

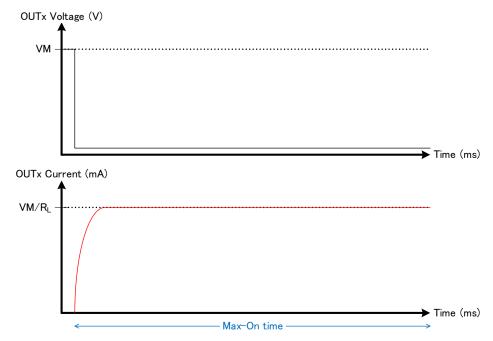

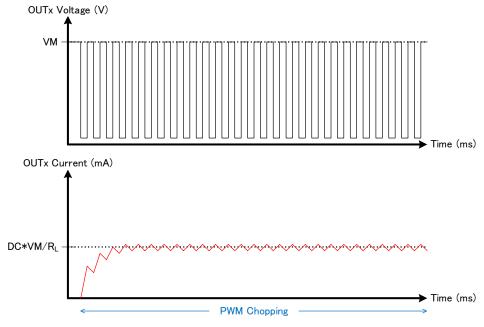

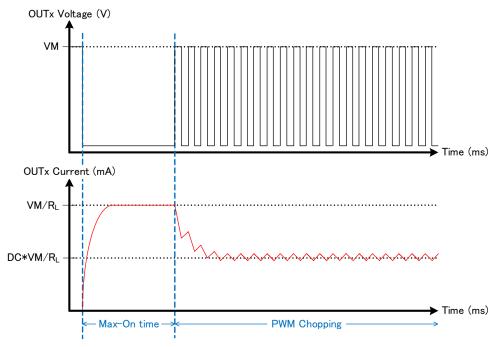

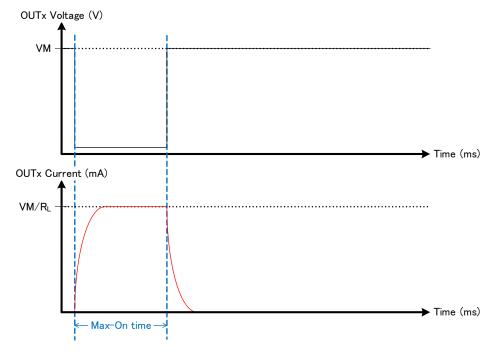

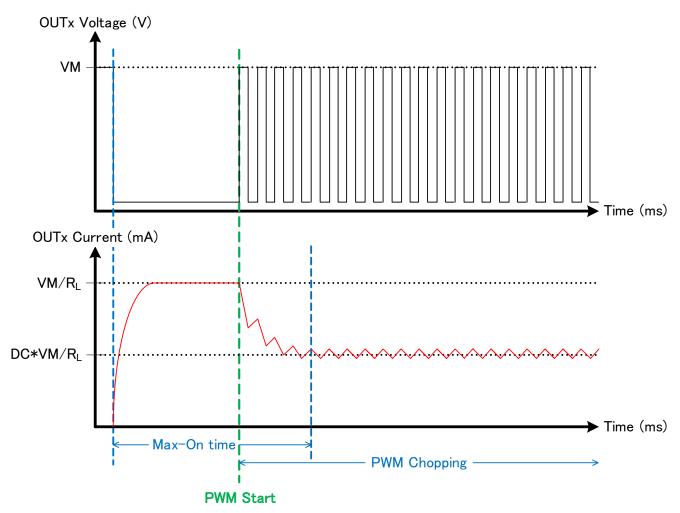

The device output is defined by two stages: Energizing Phase and PWM Phase.

During the Energizing phase, the channel is turned on with 100% duty cycle for a duration set by Control register bits C4:C1.

In PWM chopping phase, with the PWM Duty Cycle defined by Control register bits C7:C5.

The behavior of each bit in the Control Register is described in Table 4.

**Table 4. Control Register Settings**

|    |    |    |    |    |    |    |    |        | 3                                                                        |                                                                                 |  |  |  |

|----|----|----|----|----|----|----|----|--------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|

| C8 | C7 | C6 | C5 | C4 | C3 | C2 | C1 | Value  |                                                                          | DESCRIPTION                                                                     |  |  |  |

| 0  | Х  | Х  | X  | X  | X  | Х  | Х  | N/A    |                                                                          | Outputs always in Energizing mode                                               |  |  |  |

| 1  | Х  | X  | Х  | 0  | 0  | 0  | 0  | 0 ms   | No                                                                       | Energizing, starts in PWM chopping                                              |  |  |  |

| 1  | Х  | X  | Х  | 0  | 0  | 0  | 1  | 3 ms   |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 0  | 0  | 1  | 0  | 5 ms   |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 0  | 0  | 1  | 1  | 10 ms  |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 0  | 1  | 0  | 0  | 15 ms  |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 0  | 1  | 0  | 1  | 20 ms  |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 0  | 1  | 1  | 0  | 30 ms  | Sets the Energizing Time (100% duty cycle) before switching to PWM Phase |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 0  | 1  | 1  | 1  | 50 ms  |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 0  | 0  | 0  | 80 ms  |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 0  | 0  | 1  | 110 ms |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 0  | 1  | 0  | 140 ms |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 0  | 1  | 1  | 170 ms |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 1  | 0  | 0  | 200 ms |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 1  | 0  | 1  | 230 ms |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 1  | 1  | 0  | 260 ms |                                                                          |                                                                                 |  |  |  |

| 1  | Х  | Х  | Х  | 1  | 1  | 1  | 1  | 300 ms |                                                                          |                                                                                 |  |  |  |

| 1  | 0  | 0  | 0  | Х  | Х  | Х  | Х  | 0%     | (                                                                        | Output is off after Energizing Phase                                            |  |  |  |

| 1  | 0  | 0  | 1  | Х  | Х  | Х  | Х  | 12.50% | 12.5 kHz                                                                 |                                                                                 |  |  |  |

| 1  | 0  | 1  | 0  | Х  | Х  | Х  | Х  | 25.00% | 25 kHz                                                                   |                                                                                 |  |  |  |

| 1  | 0  | 1  | 1  | Х  | Х  | Х  | Х  | 37.50% |                                                                          |                                                                                 |  |  |  |

| 1  | 1  | 0  | 0  | Х  | Х  | Х  | Х  | 50.00% |                                                                          | Sets PWM chopping duty cycle. DC is the duty cycle that the low-side FET is on. |  |  |  |

| 1  | 1  | 0  | 1  | Х  | Х  | Х  | Х  | 62.50% | 50 kHz                                                                   | daty cycle that the low-side i Li is oil.                                       |  |  |  |

| 1  | 1  | 1  | 0  | Х  | Х  | Х  | Х  | 75.00% |                                                                          |                                                                                 |  |  |  |

| 1  | 1  | 1  | 1  | Х  | Х  | Х  | Х  | 87.50% | 1                                                                        |                                                                                 |  |  |  |

|    |    |    |    |    |    |    |    |        |                                                                          |                                                                                 |  |  |  |

There are five operation cases as described in Figure 29 through Figure 33.

The output is turned on with 100% duty cycle.

Figure 29. Case 1: Timer Enable Bit (C8) is 0 (Default Value)

The output is turned on in PWM chopping mode with duty cycle defined by Control register bits C7:C5.

Figure 30. Case 2: Timer Enable Bit (C8) is 1 and Energizing Timing Bits (C4:C1) are 0000

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

The output is turned on in Energizing mode with 100% duty cycle for a duration set by Control register bits C4:C1. After the timer expires, the output switches to PWM chopping mode with PWM Duty Cycle defined by Control register bits C7:C5.

Figure 31. Case 3: Timer Enable Bit (C8) is 1, Energizing Timing Bits (C4:C1) are NOT 0000, and PWM Duty Bits (C7:C5) are NOT 000

The output is turned on in Energizing mode with 100% duty cycle for a duration set by Control register bits C4:C1. After the timer expires, the output is turned off.

Figure 32. Case 4: Timer Enable Bit (C8) is 1, Energizing Timing Bits (C4:C1) are NOT 0000, and PWM Duty Bits (C7:C5) are 00

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback

## 8.5.1.4.1 PWM Start Special Command Used

The output is turned on in Energizing mode with 100% duty cycle, and a timer is enabled with duration set by Control register bits C4:C1. If the PWM Start special command is received before the timer expires, then the output switches to PWM chopping mode with PWM Duty Cycle defined by Control register bits C7:C5. If the timer expires and no PWM Start is received, then the device will stay in Energizing mode regardless of other PWM Start commands.

Figure 33. Case 5: Timer Enable Bit (C8) is 0, Energizing Timing Bits (C4:C1) are NOT 0000, and PWM Duty Bits (C7:C5) are NOT 000

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

## 8.6 Register Maps

## 8.6.1 Data Register

The Data register is used to control the status of each of the eight outputs:

Figure 34. Data Register

| D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   |

|------|------|------|------|------|------|------|------|

| OUT8 | OUT7 | OUT6 | OUT5 | OUT4 | OUT3 | OUT2 | OUT1 |

| R/W  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

When any bit is '1', the corresponding output will be active. When any bit is '0', the output will be inactive.

The data register is the default write location for the serial interface. In order to read back data from this register, the Data Register Readout special command is used.

#### 8.6.2 Fault Register

The Fault register can be read to determine if any channel exist fault condition. OCP is an overcurrent fault and OLD is an open load fault. OLD is not included on the DRV8860A

Figure 35. Fault Register

| F16      | F15      | F14      | F13      | F12      | F11      | F10      | F9       |

|----------|----------|----------|----------|----------|----------|----------|----------|

| OUT8 OCP | OUT7 OCP | OUT6 OCP | OUT5 OCP | OUT4 OCP | OUT3 OCP | OUT2 OCP | OUT1 OCP |

| R/W      |

| F8       | F7       | F6       | F5       | F4       | F3       | F2       | F1       |

| OUT8 OL  | OUT7 OL  | OUT6 OL  | OUT5 OL  | OUT4 OL  | OUT3 OL  | OUT2 OL  | OUT1 OL  |

| R/W      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

When any fault occurs, nFAULT pin will be driven low and corresponding Fault register bit will be set up as '1'. OCP is a flag indicating overcurrent fault. ODP is a flag indicating open load fault.

Fault bits can be reset by two approaches:

- 1. Special command 'FAULT RESET' clear all fault bits.

- 2. Setting Data register to ON will clear corresponding OLD bits (DRV8860 only) Setting Data register to OFF will clear corresponding OCP bits.

## 8.6.3 Control Register

The Control register is used to adjust the Energizing Time and PWM Duty Cycle of outputs:

Figure 36. Control Register

| C8              | C7 |                  |       | C4                      | C3 | C2 | C1 |  |  |

|-----------------|----|------------------|-------|-------------------------|----|----|----|--|--|

| Over All Enable | PW | M Duty Cycle cor | ntrol | Energizing Time control |    |    |    |  |  |

| R/W             |    | R/W              |       |                         | R/ | W  |    |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Special command 'WRITE CONTROL REGISTER' is used to program control register.

Special command 'READ CONTROL REGISTER' is used to read back control register content.

## 9 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The DRV8860 is an eight channel low side driver with protection features. The following design is a common application of the DRV8860.

## 9.2 Typical Application

## 9.2.1 Design Requirements

**Table 5. Design Parameters**

| Parameter           | Value              |

|---------------------|--------------------|

| Input voltage range | 8 V – 38 V         |

| Current             | 330 mA per channel |

Product Folder Links: DRV8860 DRV8860A

## 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Drive Current

The current path is from VM, through the load, into the low-side sinking driver. Power dissipation  $I^2R$  losses in one sink are calculated using Equation 1.

$$P_D = I^2 \times R_{DS(on)} \tag{1}$$

## 9.2.3 Application Curves

Figure 37. PWM Operation

Copyright © 2013–2015, Texas Instruments Incorporated

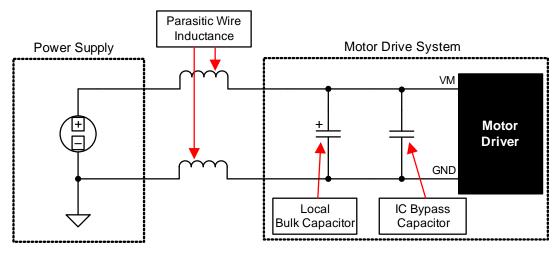

## 10 Power Supply Recommendations

The DRV8860 is designed to operate from an input voltage supply (VM) range between 8 and 38 V. A 0.1-µF ceramic capacitor rated for VM must be placed as close as possible to the VM pin. In addition to the local decoupling cap, additional bulk capacitance is required and must be sized accordingly to the application requirements.

Bulk capacitance sizing is an important factor in motor drive system design. It is dependent on a variety of factors including:

- Type of power supply

- Acceptable supply voltage ripple

- Parasitic inductance in the power supply wiring

- Type of load

- Load startup current

The inductance between the power supply and motor drive system will limit the rate current can change from the power supply. If the local bulk capacitance is too small, the system will respond to excessive current demands or dumps from the motor with a change in voltage. The user should size the bulk capacitance to meet acceptable voltage ripple levels.

The datasheet generally provides a recommended value but system level testing is required to determine the appropriate sized bulk capacitor.

Figure 38. Example Setup of Motor Drive System with External Power Supply

## 10.1 Power Supply and Logic Sequencing

There is no specific sequence for powering-up the DRV8860. It is okay for digital input signals to be present before VM is applied. After VM is applied to the DRV8860, it begins operation based on the status of the control pins.

## 11 Layout

## 11.1 Layout Guidelines

- The VM pin should be bypassed to GND using a low-ESR ceramic bypass capacitor with a recommended value of 0.1-μF rated for VM.

- This capacitor should be placed as close as possible to the VM pin on the device with a thick trace or ground plane connection to the device GND pin.

- The VM pin must be bypassed to ground using and appropriate bulk capacitor. This component must be located close to the DRV8860.

## 11.2 Layout Example

Where the pull-up voltage (V3P3) is an external supply in the range of the recommended operating conditions for the digital open-drain outputs.

Figure 39. DRV8860 Layout

Copyright © 2013–2015, Texas Instruments Incorporated

#### 11.3 Thermal Consideration

The DRV8860 device has thermal shutdown (TSD) as described in the Thermal Shutdown (TSD) section. If the die temperature exceeds approximately 150°C, the device is disabled until the temperature drops to a safe level.

Any tendency of the device to enter TSD is an indication of either excessive power dissipation, insufficient heatsinking, or too high of an ambient temperature.

## 11.3.1 Power Dissipation

Power dissipation in the DRV8860 device is dominated by the power dissipated in the output FET resistance, R<sub>DS(on)</sub>. Use the following equation to calculate the estimated average power dissipation of each output when running a driving a load.

$$P_D = R_{DS(on)} \times I_O^2$$

#### where:

- P<sub>D</sub> is the power dissipation of one channel

- R<sub>DS(on)</sub> is the resistance of each FET

- Io is the RMS output current being applied to each channel

(2)

Io is equal to the average current into the channel. Note that at startup, this current is much higher than normal running current; these peak currents and their duration must be also be considered.

The total device dissipation is the power dissipated in each channel added together.

The maximum amount of power that can be dissipated in the device is dependent on ambient temperature and heatsinking.

#### **NOTE**

R<sub>DS(on)</sub> increases with temperature, so as the device heats, the power dissipation increases. This fact must be taken into consideration when sizing the heatsink.

## 11.3.2 Heatsinking

The PowerPAD package uses an exposed pad to remove heat from the device. For proper operation, this pad must be thermally connected to copper on the PCB to dissipate heat. On a multi-layer PCB with a ground plane, this connection can be accomplished by adding a number of vias to connect the thermal pad to the ground plane.

On PCBs without internal planes, a copper area can be added on either side of the PCB to dissipate heat. If the copper area is on the opposite side of the PCB from the device, thermal vias are used to transfer the heat between top and bottom layers.

For details about how to design the PCB, refer to the TI application report, PowerPAD<sup>TM</sup> Thermally Enhanced Package (SLMA002), and the TI application brief, PowerPAD Made Easy™ (SLMA004), available at www.ti.com. In general, the more copper area that can be provided, the more power can be dissipated.

## 12 Device and Documentation Support

## 12.1 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.2 Trademarks

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

## 12.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 12.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

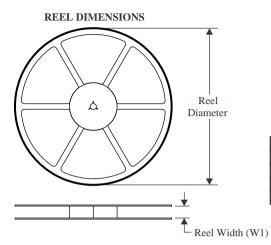

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 28-Mar-2025

#### PACKAGING INFORMATION

| Orderable Device | Status   | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|----------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |          |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| DRV8860APW       | OBSOLETE | TSSOP        | PW                 | 16   |                | TBD          | Call TI                       | Call TI             | -40 to 85    | 8860A                |         |

| DRV8860APWR      | ACTIVE   | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | 8860A                | Samples |

| DRV8860PW        | OBSOLETE | TSSOP        | PW                 | 16   |                | TBD          | Call TI                       | Call TI             | -40 to 85    | 8860                 |         |

| DRV8860PWPR      | ACTIVE   | HTSSOP       | PWP                | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | 8860PWP              | Samples |

| DRV8860PWR       | ACTIVE   | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | 8860                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

## **PACKAGE OPTION ADDENDUM**

www.ti.com 28-Mar-2025

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Mar-2025

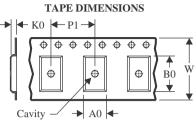

## TAPE AND REEL INFORMATION

|    | -                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

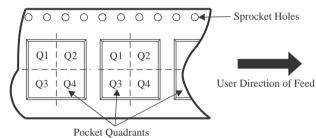

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV8860APWR | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| DRV8860PWPR | HTSSOP          | PWP                | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| DRV8860PWR  | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 21-Mar-2025

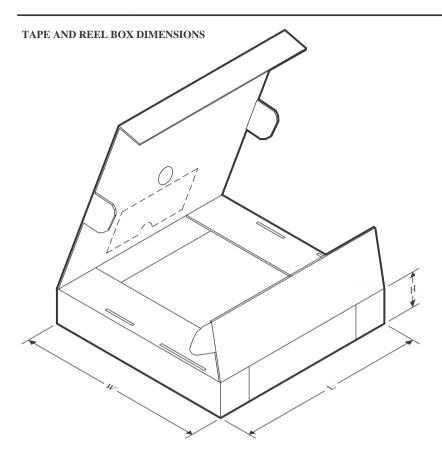

## \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV8860APWR | TSSOP        | PW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| DRV8860PWPR | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| DRV8860PWR  | TSSOP        | PW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

#### NOTES:

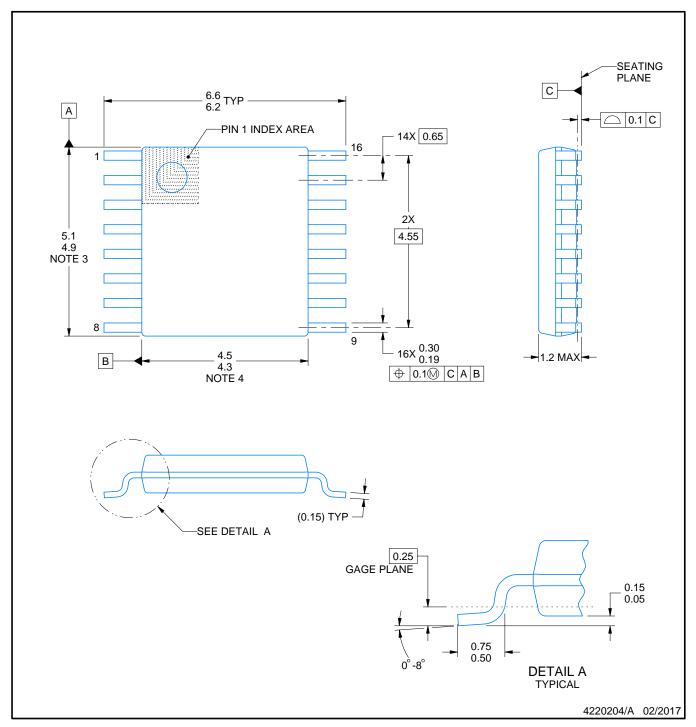

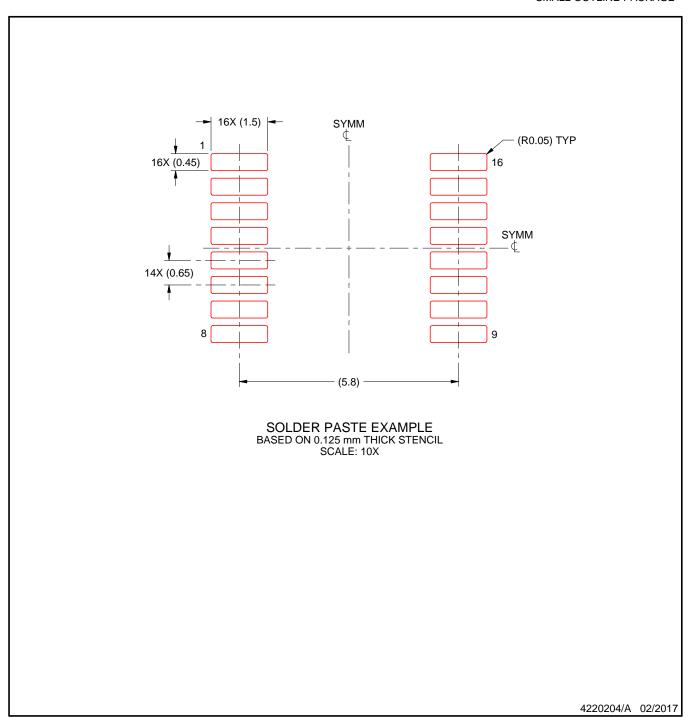

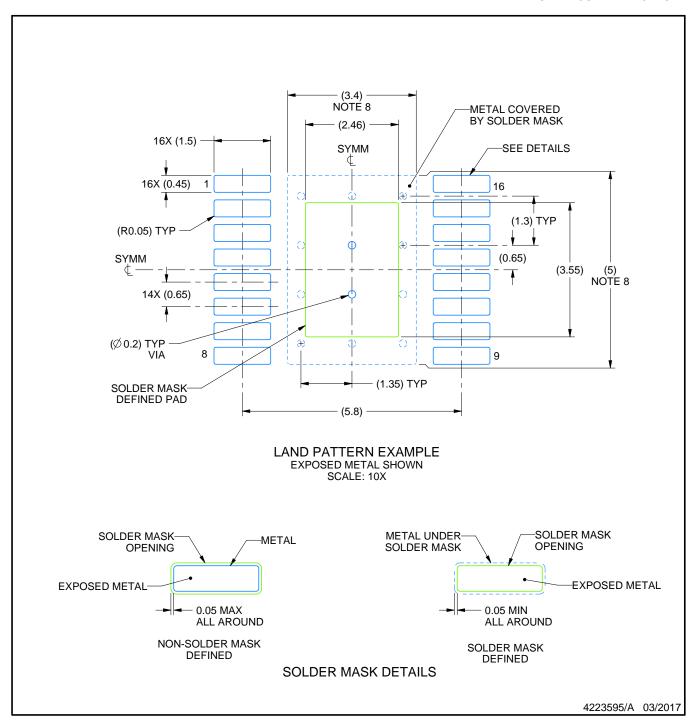

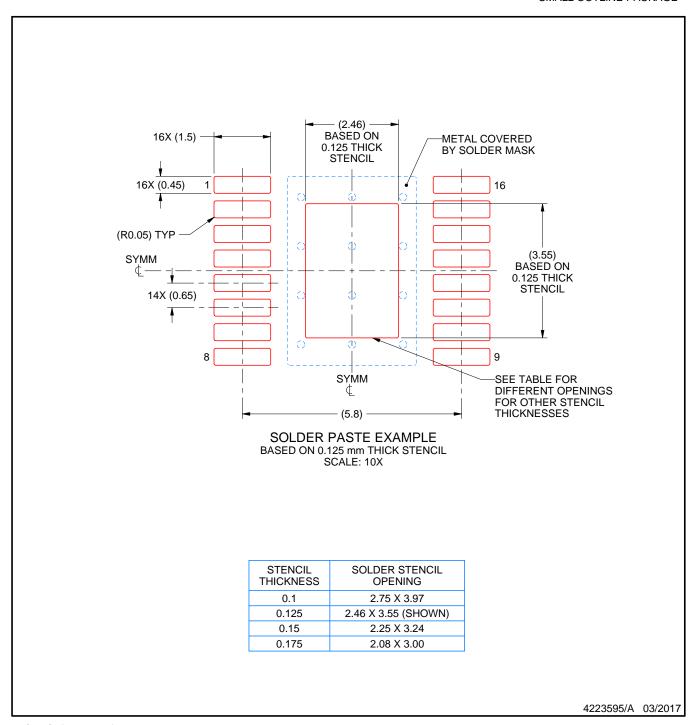

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

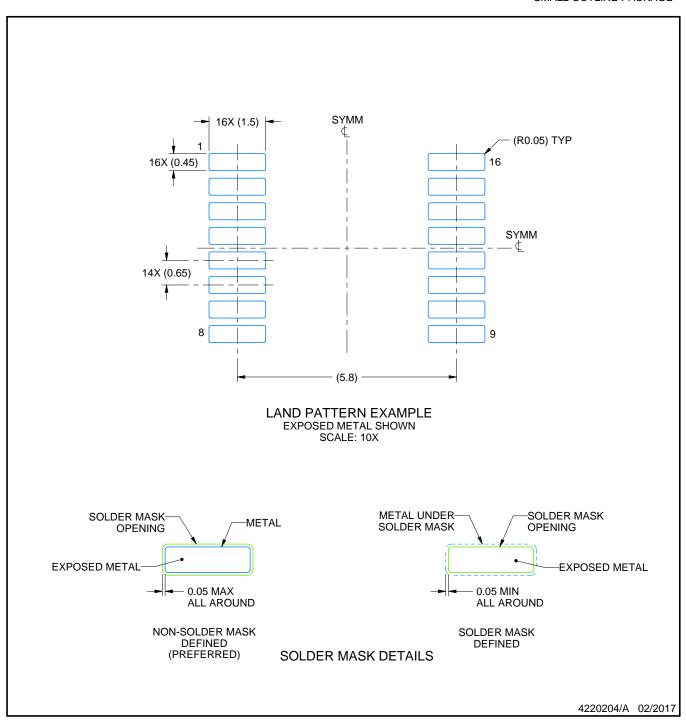

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

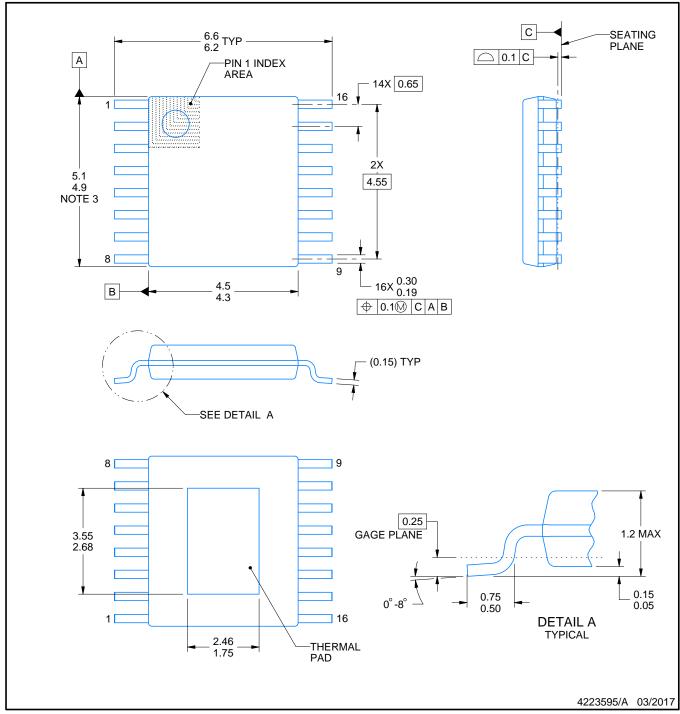

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

#### NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.

- 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 7. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 8. Size of metal pad may vary due to creepage requirement.

- 9. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

NOTES: (continued)

- 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 11. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated