### Quad low-side intelligent power switch

#### **Product status link**

IPS4260L

#### Product label

#### **Features**

- 8 V to 50 V operating voltage range

- Four independent protected channels

- V<sub>CC</sub> undervoltage lock-out

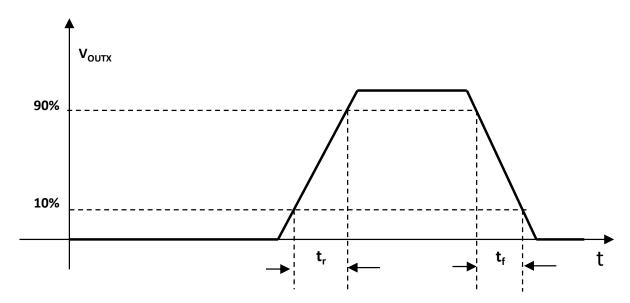

- High speed operation (t<sub>r</sub>, t<sub>f</sub> < 1 μs)</li>

- · Programmable load current limitation level by external resistor

- Typical operating load current: 0.5 A (per channel) / 2 A (one channel)

- Thermally independent junction overtemperature protections

- Programmable non-dissipative short-circuit protection (cut-off) by external resistor

- Open load (off-state) and short-to-ground activated by external pull-down resistors

- Fast demagnetization of inductive loads with integrated catch diodes clamping turn-off transients

- Ground and V<sub>CC</sub> wire break protection

- V<sub>CC</sub> overvoltage protection

- Common open load diagnostic

- Common thermal shutdown and overload diagnostic

- · Per channel thermal shutdown diagnostic

- Designed to meet IEC 61131-2, IEC61000-4-2, IEC61000-4-4 and IEC61000-4-5

- Miniaturized HTSSOP20 package

#### **Application**

- Programmable logic control

- Industrial PC peripheral input/output

- · Numerical control machines

- General low-side switch applications

#### **Description**

The IPS4260L is a monolithic high speed (f<sub>SW</sub> up to 250 kHz) device, which can drive four independent capacitive, resistive or inductive loads with one side connected to supply voltage. The channels can be parallelized to reduce power dissipation. When connected to Vcc rail, four integrated catch diodes clamp the turn-off transients generated by inductive loads even with huge inductance; combined with proper external TVS connected to VCC or to GND the IC allows fast decay, too. Each channel is protected against overload or short circuit event: the intervention level can be set by an external resistor on  $I_{\text{LIM}}$  pin . Built-in thermal shutdown protects the chip against overtemperature even in case of short-circuit. If enabled, the integrated cutoff protection features a non-dissipative protection in case of overload; it limits both the output average current value and, consequently, the device overheating. Cut-off delay/restart can be programmed by external resistors on CoD pin; it can be disabled by shorting CoD to GND. Two common diagnostic open drains pins (OL, for open load and FLT for cut-off and thermal shutdown) together with the four open drain on each INx pin (cut-off and thermal shutdown) feature an extensive diagnostic of the chip.

# 1 Block diagram

VCC VΖ UVLO  $V_{\text{CLAMP}}$ IN1 OUT1 OUT2 IN2 GATE **DRIVERS** OUT3 IN3 LOGIC INTERFACE OUT4 IN4  $\mathbf{I}_{\mathsf{LIM}}$  $\overline{\mathbf{OL}}$ CURRENT LIMITATION CUT-OFF  $I_{COD}$ THERMAL JUNCTION  $\overline{FLT}$ OPEN LOAD ₹ R<sub>ILIM</sub>

PGND

SGND

Figure 1. Block diagram

DS12305 - Rev 7 page 2/25

## 2 Pin description

20 \_ PGND **PGND** 19 PGND [ **PGND** 18 VZ VΖ 17 IN1 OUT1 IN2 5 16 OUT2 IN3 6 15 OUT3 IN4 OUT4 13 SGND VCC 12 OL 9 ILIM 11 \_ FLT 10 CoD

Figure 2. Pin connection (top view)

Table 1. Pin configuration

| Number         | Name                                                                                                                                                                                                | Function                                                                                                                                                                                                                                                                                    | Туре                    |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1, 2, 19, 20   | PGND                                                                                                                                                                                                | Integrated power switch ground                                                                                                                                                                                                                                                              | Supply                  |

| 3, 18          | VZ                                                                                                                                                                                                  | Load clamp voltage pins. Pins 3 and 18 must be shorted on the application board and then connected directly to the supply rail, or by an external Zener or TVS diode to the supply rail or to PGND (see Section 2.3 VZ)                                                                     | Analog Output           |

| 4              | IN1                                                                                                                                                                                                 | Channel 1 input / cut-off and thermal shutdown diagnostic                                                                                                                                                                                                                                   | Input/output open drain |

| 5              | IN2                                                                                                                                                                                                 | Channel 2 input / cut-off and thermal shutdown diagnostic                                                                                                                                                                                                                                   | Input/output open drain |

| 6              | IN3                                                                                                                                                                                                 | Channel 3 input / cut-off and thermal shutdown diagnostic                                                                                                                                                                                                                                   | Input/output open drain |

| 7              | IN4                                                                                                                                                                                                 | Channel 4 input / cut-off and thermal shutdown diagnostic                                                                                                                                                                                                                                   | Input/output open drain |

| 8, exposed pad | SGND                                                                                                                                                                                                | Logic interface block ground                                                                                                                                                                                                                                                                | Supply                  |

| 9              | ŌL                                                                                                                                                                                                  | Cumulative power stage open load or short ground common diagnostic                                                                                                                                                                                                                          | Output open drain       |

| 10             | FLT                                                                                                                                                                                                 | Cut-off and thermal shutdown pin. Common diagnostic pin both for thermal shutdown and cut-off                                                                                                                                                                                               | Output open drain       |

| 11             | CoD                                                                                                                                                                                                 | Programmable cut-off intervention delay during overcurrent operation. It cannot be left floating: connect to PCB SGND ground plane to disable the cut-off function or connect a resistor between CoD and PCB ground plane to set the delay (see Section 6.3 Current limitation and cut-off) | Analog Output           |

| 12             | Limitation current adjustment. It cannot be left floating: connect a resistor between I <sub>LIM</sub> and SGND to set the current limit threshold (see Section 6.3 Current limitation and cut-off) |                                                                                                                                                                                                                                                                                             | Analog Output           |

| 13             | VCC                                                                                                                                                                                                 | Supply voltage. Connect to the supply rail                                                                                                                                                                                                                                                  | Supply                  |

| 14             | OUT4                                                                                                                                                                                                | Power stage, channel 4                                                                                                                                                                                                                                                                      | Analog Output           |

| 15             | OUT3                                                                                                                                                                                                | Power stage, channel 3                                                                                                                                                                                                                                                                      | Analog Output           |

| 16             | OUT2                                                                                                                                                                                                | Power stage, channel 2                                                                                                                                                                                                                                                                      | Analog Output           |

| 17             | OUT1                                                                                                                                                                                                | Power stage, channel 1                                                                                                                                                                                                                                                                      | Analog Output           |

DS12305 - Rev 7 page 3/25

#### 2.1 VCC

IC supply voltage. This pin has to be connected to the supply rail of the application.

#### 2.2 PGND, SGND

PGND stands for power ground and it is internally connected to the source of the integrated switches. SGND stands for signal ground and it is the reference level for the logic interface. SGND and PGND pins must be shorted on the application board. In order to reduce as much as possible the switching noises from PGND to SGND, the application board has to be designed with two different ground planes for SGND and PGND. The two ground planes have to be shorted by a dedicated net.

#### 2.3 VZ

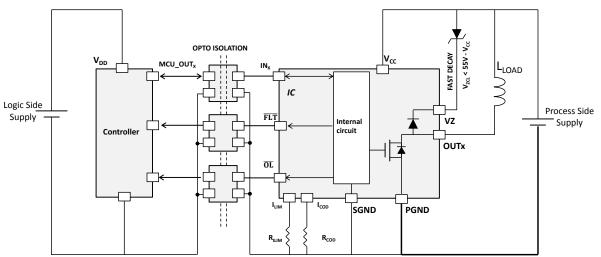

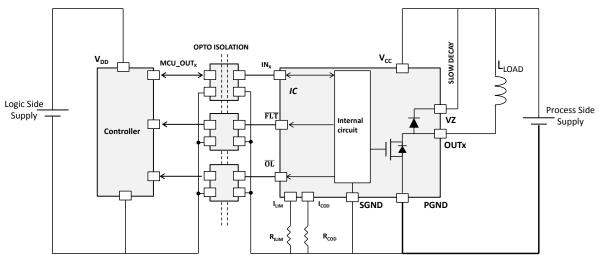

These two pins (corresponding to the cathodes of the clamp diodes) must be shorted together on the application and connected directly to supply rail or, alternatively, connected by a Zener or TVS diode to supply rail or PGND. Connecting VZ pins directly to the supply rail implies that the inductive loads are demagnetized without fast decay option: in fact the V<sub>OUTx</sub> (voltage on OUTx pin) is forced to the forward voltage of the integrated clamp diodes. The connection by a Zener or TVS allows to drive loads requiring fast current decay (fast demagnetization). For the proper selection of the external Zener or TVS, please refer to Section 7.1 Fast current decay with TVS between VZ and PGND

Note: Leaving VZ pins floating, the integrated output voltage clamp is activated and the fast current decay capability is limited by the heatsink capability of the IC. See E<sub>AS</sub> in Table 2. Absolute maximum ratings.

#### 2.4 IN1, IN2, IN3, IN4

These pins drive the power stage on pins OUT1, OUT2, OUT3 and OUT4. Besides an internal weak pull-down resistor, each IN1, IN2, IN3, IN4, is internally wired to an open drain transistor, used for diagnostic purposes, and must be driven through a series resistor. The open drain transistor is turned-on in case of thermal shutdown or cut-off protection of the relative channel (see Section 6.2 Overtemperature and Section 6.3 Current limitation and cut-off).

#### 2.5 OUT1, OUT2, OUT3, OUT4

Power stage load connection pins: integrated power transistor are in low-side configuration, so the load has to be connected between OUTx pin and supply rail. The power stage channels can be paralleled.

#### 2.6 Open load in off-state

OL pin is used for diagnostic purpose and it is internally wired to an open drain transistor. If the open load feature is enabled (see Section 6.4 Open load in off-state) the open drain transistor is activated when OUTx is in off state and the open load threshold (VOLoff) is triggered (see Table 8. Protection and diagnostic).

#### 2.7 FLT

This pin is used for diagnostic purpose and it is internally wired to an open drain transistor. The open drain transistor is turned on in case of junction thermal shutdown or during the cut-off protection.

#### 2.8 I<sub>LIM</sub>

This pin cannot be left floating and can be used to program the limitation current value through an external resistor  $R_{\text{ILIM}}$  (see Table 8. Protection and diagnostic). The resistor  $R_{\text{ILIM}}$  has to be connected between  $I_{\text{LIM}}$  and SGND pins. When more than one ICs are used in the same application, their  $I_{\text{LIM}}$  pins cannot be wired together: each IC must be connected to its own resistor (see Section 6.3 Current limitation and cut-off)

#### 2.9 CoD

This pin cannot be left floating and can be used to program the cut-off delay time  $t_{coff}$  (see Table 8. Protection and diagnostic) through an external resistor ( $R_{CoD}$ ). The resistor  $R_{CoD}$  has to be connected between CoD and SGND pins. The cut-off function can be completely disabled by shorting CoD pin to SGND: in this condition the power stage channel remains ON in limitation condition, supplying the current to the load until the input is forced LOW or the thermal shutdown threshold is triggered (see Section 6.3 Current limitation and cut-off).

DS12305 - Rev 7 page 4/25

## 3 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol                               | Parameter                                                                                                                            | Value                      | Unit |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|

| V <sub>CC</sub>                      | Supply voltage                                                                                                                       | -0.3 to 55                 | V    |

| V <sub>Z</sub>                       | Internal clamp diode supply                                                                                                          | -0.3 to 55                 | V    |

| V <sub>OUTx</sub>                    | Power stage (OUTx channel) voltage                                                                                                   | -0.3 to V <sub>DEMAG</sub> | V    |

| V <sub>INx</sub>                     | INx pin voltage                                                                                                                      | -0.3 to 5.5                | V    |

| I <sub>INx</sub>                     | INx pin current                                                                                                                      | -10 to +10                 | mA   |

| V <sub>COD</sub> , V <sub>ILIM</sub> | CoD and I <sub>LIM</sub> pin voltage                                                                                                 | 5.5                        | V    |

| I <sub>COD</sub> , I <sub>ILIM</sub> | CoD and I <sub>LIM</sub> pin current                                                                                                 | -1/+5                      | mA   |

| V <sub>OD</sub>                      | Open drain fault pins (FLT and OL) voltage                                                                                           | -0.3 to 5.5                | V    |

| I <sub>OD</sub>                      | Open drain fault pins (FLT and OL) current                                                                                           | -10/10                     | mA   |

| I <sub>CC</sub>                      | Maximum DC reverse current (from GND to $V_{CC}$ )                                                                                   | -250                       | mA   |

| I <sub>OUTHx</sub>                   | Power stage (OUTx channel) current                                                                                                   | Internally limited         | А    |

| -l <sub>OUTHx</sub>                  | DC Reverse current on OUTx channel                                                                                                   | 5                          | А    |

| l <sub>z</sub>                       | DC current on V <sub>Z</sub> (pins 3 and 18 connected together in the application board)                                             | 5                          | А    |

| EAS                                  | Single pulse avalanche energy per channel not simultaneously @T <sub>AMB</sub> = 125 °C, I <sub>OUT</sub> = 500 mA, VZ pins floating | 0.9                        | J    |

| P <sub>TOT</sub>                     | Power dissipation at T <sub>C</sub> = 25 °C                                                                                          | Internally limited         | W    |

| T <sub>STG</sub>                     | Storage temperature range                                                                                                            | -55 to 150                 | °C   |

| TJ                                   | Junction temperature                                                                                                                 | -40 to 150                 | °C   |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND.

Table 3. Thermal data

| Symbol               | Termal resistance   | Conditions                                         | Value | Unit |

|----------------------|---------------------|----------------------------------------------------|-------|------|

| R <sub>TH(JA)</sub>  | Junction to ambient | 2s2p (4L) board  Natural convection <sup>(1)</sup> | 43    | °C/W |

| R <sub>TH(J-C)</sub> | Junction to case    | Cold plate (infinite headsink like) <sup>(2)</sup> | 3     | °C/W |

1. JESD51-7.

2. JESD51-12.01

DS12305 - Rev 7 page 5/25

## 4 Electrical characteristics

(8 V < V<sub>CC</sub> < 50 V; -40 °C < T<sub>J</sub> < 125 °C, unless otherwise specified)

Table 4. Supply

| Symbol             | Parameter                        | Test conditions                                             |                   | Тур. | Max. | Unit |  |

|--------------------|----------------------------------|-------------------------------------------------------------|-------------------|------|------|------|--|

| V <sub>CC</sub>    | Operating voltage range          |                                                             | V <sub>UVON</sub> |      | 50   | V    |  |

| V <sub>UVON</sub>  | Undervoltage on threshold        | V <sub>CC</sub> increasing                                  |                   |      | 8    | V    |  |

| V <sub>UVOFF</sub> | Undervoltage off threshold       | V <sub>CC</sub> decreasing                                  |                   |      | 7.5  | V    |  |

| V <sub>UVH</sub>   | Undervoltage hysteresis          |                                                             | 0.2               | 0.5  |      | V    |  |

| _                  | Overally averaged in affindation | V <sub>CC</sub> = 24 V; all INx OFF                         |                   | 1    |      | 4    |  |

|                    | Supply current in off-state      | V <sub>CC</sub> = 50 V; all INx OFF                         |                   | 1.2  | 1.6  | mA   |  |

| I <sub>S</sub>     | Overally averaged in the state   | V <sub>CC</sub> = 24 V; all INx ON, OUTx open load [x = 14] |                   | 2    |      | ^    |  |

|                    | Supply current in on-state       | V <sub>CC</sub> = 50 V; all INx ON, OUTx open load [x = 14] |                   | 2.4  | 3    | mA   |  |

Table 5. Output stage

| Symbol                | Parameter                                           | Parameter Test conditions                                                  |                    | Тур. | Max. | Unit  |

|-----------------------|-----------------------------------------------------|----------------------------------------------------------------------------|--------------------|------|------|-------|

| Racionii              | On-state resistance                                 | R <sub>LOAD</sub> = 48 Ω, V <sub>CC</sub> = 24 V @ T <sub>J</sub> = 25 °C  |                    | 260  |      | mΩ    |

| R <sub>DS(ON)</sub>   | On-State resistance                                 | R <sub>LOAD</sub> = 48 Ω, V <sub>CC</sub> = 24 V @ T <sub>J</sub> = 125 °C |                    |      | 560  | 11122 |

| V <sub>OUT(OFF)</sub> | Off-state power stage voltage                       | V <sub>IN</sub> = 0 V and I <sub>OUT</sub> = 0 A                           | V <sub>CC</sub> -2 |      |      | V     |

| 1                     | Off state nawer stage current                       | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = V <sub>CC</sub> = 24 V           |                    | 0.5  |      |       |

| 'OUT(OFF)             | I <sub>OUT(OFF)</sub> Off-state power stage current | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = V <sub>CC</sub> = 50 V           |                    |      | 10   | μA    |

| V <sub>FCD</sub>      | Catch diodes forward voltage                        | I <sub>forward</sub> = 500 uA                                              | 0.21               | 0.50 | 0.73 | V     |

| I <sub>RRM</sub>      | Catch diodes reverse current                        | V <sub>rrm</sub> = 55 V                                                    |                    |      | 1    | uA    |

Table 6. Switching (V<sub>CC</sub> = 24 V; R<sub>LOAD</sub> = 24  $\Omega$ , input rise time < 0.1  $\mu s$  )

| Symbol               | Parameter                                       | Test conditions                                             | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| t <sub>r</sub>       | Rise time                                       |                                                             |      | 450  | 700  |      |

| t <sub>f</sub>       | Fall time                                       | see Figure 3. t <sub>rise</sub> and t <sub>fall</sub>       |      | 500  | 600  | 20   |

| t <sub>PD(H-L)</sub> | Propagation delay time INx to OUTx, low to high | and Figure 4. t <sub>PD(L-H)</sub> and t <sub>PD(H-L)</sub> |      | 500  | 700  | ns   |

| t <sub>PD(L-H)</sub> | Propagation delay time INx to OUTx, high to low |                                                             |      | 400  | 600  |      |

DS12305 - Rev 7 page 6/25

Figure 4. t<sub>PD(L-H)</sub> and t<sub>PD(H-L)</sub>

DS12305 - Rev 7 page 7/25

### Table 7. Logic inputs

| Symbol               | Parameter                            | Test conditions                                                                   | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IL</sub>      | Input low level voltage              | V <sub>IN</sub> decreasing                                                        |      |      | 0.8  |      |

| V <sub>IH</sub>      | Input high level voltage             | V <sub>IN</sub> increasing                                                        | 2.0  |      |      |      |

| V <sub>I(HYST)</sub> | Input hysteresis voltage             |                                                                                   |      | 0.4  |      |      |

| V <sub>OL</sub>      | Voltage drop on OL pin               | $I_{OL}$ = 5 mA, $V_{INx}$ = 0 V, OUTx = open load, $R_{PD}$ between OUTx and GND |      |      | 0.1  | V    |

| V <sub>FAULT</sub>   | Voltage drop on FAULT pin or INx pin | $I_{FLT}$ = 5 mA, $V_{INx}$ = 0 V, $(T_{JX} > T_{JSD})$ or cut-off event)         |      |      | 0.1  |      |

| I <sub>INX</sub>     | All digital input/output pin current | V <sub>IN</sub> = 5 V                                                             |      |      | 70   | μА   |

Table 8. Protection and diagnostic

| Symbol             | Parameter                                                    | Test conditions                                                                                                | Min.                                                                  | Тур.                         | Max.    | Unit |

|--------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------|---------|------|

| V <sub>clamp</sub> | V <sub>CC</sub> clamp voltage                                | I <sub>CC</sub> ≤ 10 mA                                                                                        | 55                                                                    | 58                           | 60      | V    |

| V <sub>demag</sub> | Demagnetization voltage                                      | I <sub>OUT</sub> = 0.5 A; load ≥10 mH                                                                          | 55                                                                    | 58                           | 60      | V    |

| I <sub>peak</sub>  | Current limitation activation threshold.                     | I <sub>OUT</sub> increasing from 0 A to short circuit.                                                         |                                                                       | I <sub>LIM</sub> +20%        |         | А    |

|                    | Owner at limitation lavel                                    | 30 kΩ ≤ R <sub>ILIM</sub> < 120 kΩ                                                                             | 6                                                                     | $0/R_{ILIM}[k\Omega] \pm 30$ | %       |      |

| I <sub>LIM</sub>   | Current limitation level                                     | 0 < R <sub>ILIM</sub> < 30 kΩ                                                                                  |                                                                       | 3 ± 30%                      |         | _ A  |

| t <sub>coff</sub>  | Cut-off current delay time                                   | Programmable by external resistor on "cut-off" pin (valid in the range from 60 k $\Omega$ to 240 k $\Omega$ ). | R <sub>CoD</sub> [kΩ]/120 ± 15%                                       |                              | 5%      | ms   |

|                    |                                                              | $R_{CoD}$ = 0 $\Omega$ cut-off disabled                                                                        | The IC is protected against overheating be the thermal shutdown only. |                              |         |      |

| t <sub>res</sub>   | Power stage restart delay time                               |                                                                                                                |                                                                       | 31*t <sub>coff</sub> ± 15%   |         | ms   |

| t <sub>BKT</sub>   | Open load blanking time                                      |                                                                                                                | 10                                                                    | 16                           | 22      | μs   |

| I <sub>VD</sub>    | Vcc wire break power stage current                           | $V_{INx} = V_{CC} = 0 \text{ V}; V_{OUTx} = 24$<br>V, $V_z$ floating                                           |                                                                       |                              | 50      | μА   |

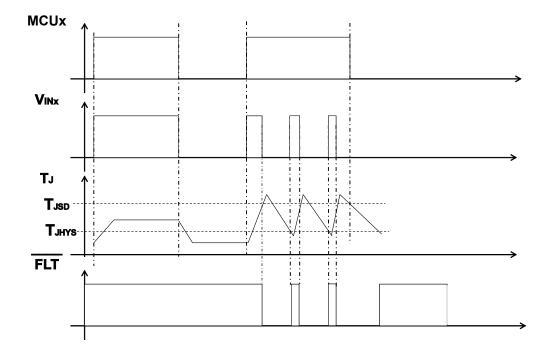

| T <sub>JSD</sub>   | Junction temperature shutdown                                |                                                                                                                |                                                                       | 160                          |         | °C   |

| T <sub>JHYST</sub> | Junction temperature thermal hysteresis                      |                                                                                                                |                                                                       | 20                           |         | °C   |

| V <sub>OLoff</sub> | Open load (off-state) or short-to-ground detection threshold |                                                                                                                | Vcc-4.5                                                               | Vcc-3.5                      | Vcc-2.5 | V    |

DS12305 - Rev 7 page 8/25

## Power stage logic

Table 9. Power stage (OUTx pin) truth table

| Operation                | MCU_OUTx | INx | OUTx | FLT | OL |

|--------------------------|----------|-----|------|-----|----|

| Normal                   | L        | L   | Н    | Н   | Н  |

| Normal                   | Н        | Н   | L    | Н   | н  |

| Cut-off                  | L        | L   | Н    | L   | Н  |

| Cut-oii                  | Н        | L   | Н    | L   | Н  |

| UVLO                     | L        | L   | Н    | X   | X  |

| UVLO                     | Н        | Н   | Н    | Х   | X  |

| Open load / short to CND | L        | L   | L    | Н   | L  |

| Open load / short-to-GND | Н        | Н   | L    | Н   | Н  |

| Overtemperature          | L        | L   | Н    | L   | Н  |

| Overtemperature          | Н        | L   | Н    | L   | Н  |

Figure 5. Application circuit (fast decay enabled by TVS between Vz and supply rail)

Figure 6. Application circuit (fast decay enabled by TVS between VZ and PGND).

DS12305 - Rev 7 page 9/25

Figure 7. Application circuit (fast decay disabled by Vz shorted to supply rail) .

DS12305 - Rev 7 page 10/25

### 6 Protection and diagnostic

The IC integrates several protections to ease the design of a robust application.

#### 6.1 Undervoltage lock-out

The device turns off if the supply voltage falls below the turn-off threshold  $(V_{UV(off)})$ . Normal operation restarts after  $V_{CC}$  exceeds the turn-on threshold  $(V_{UV(on)})$ . Turn-on and turn-off thresholds are defined in Table 4. Supply.

#### 6.2 Overtemperature

The power stage of each channel is turned off as its internal junction temperature  $(T_J)$  exceeds the shutdown threshold  $(T_{JSD})$ . Normal operation restarts when  $T_J$  comes back below the reset threshold (see Table 8. Protection and diagnostic). The internal fault signal is set when the channel is OFF due to thermal protection. The thermal fault is reported both on the FLT pin and on the INx pin of the corresponding OUTx in fault. Note that the FLT pin reports the logic OR of the four output channels faults.

Figure 8. Thermal protection signalization behavior on FLT

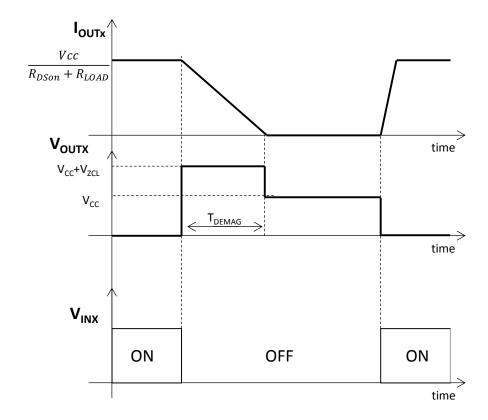

#### 6.3 Current limitation and cut-off

The load current flows through the integrated power stage and it is internally limited by the specific  $I_{LIM}$  threshold that can be set by an external resistor ( $R_{ILIM}$ ) placed between  $I_{LIM}$  and SGND ground plane. The design rule for the  $R_{ILIM}$  resistor is:

#### Equation 1:

(1)

$I_{LIM} = 60/R_{ILIM}[k\Omega]$

The above design rule is valid in the range 30 k $\Omega$   $\leq$  R<sub>ILIM</sub>  $\leq$  120 k $\Omega$ . For 0  $\Omega$   $\leq$  R<sub>ILIM</sub> < 30 k $\Omega$ , the current is internally limited up to 3 A (typical). For R<sub>ILIM</sub> > 120 k $\Omega$  the current is anyway limited but the linearity is not guaranteed.

The IC implements the cut-off feature which limits the duration of the current limitation condition. The duration of the current limitation condition ( $T_{coff}$ ) can be set by a resistor ( $R_{CoD}$ ) placed between CoD and SGND ground plane. The design rule for  $R_{CoD}$  is:

DS12305 - Rev 7 page 11/25

#### **Equation 2:**

(2)

#### $T_{coff} = R_{CoD}[k\Omega]/120$

The above design rule is valid in the range 60 k $\Omega$  ≤  $R_{CoD}$  ≤ 240 k $\Omega$ . As 0  $\Omega$  <  $R_{CoD}$  < 60 k $\Omega$ ,  $T_{coff}$  anyway decreases but the linearity of the above design rule is not guaranteed. As  $R_{CoD}$  = 0  $\Omega$  (short-to-ground plane) the cut-off feature is disabled, by means the IC is protected by thermal shutdown only. Concerning  $R_{CoD}$  > 240 k $\Omega$ ,  $T_{coff}$  increases but linearity of equation 2 is not guaranteed.

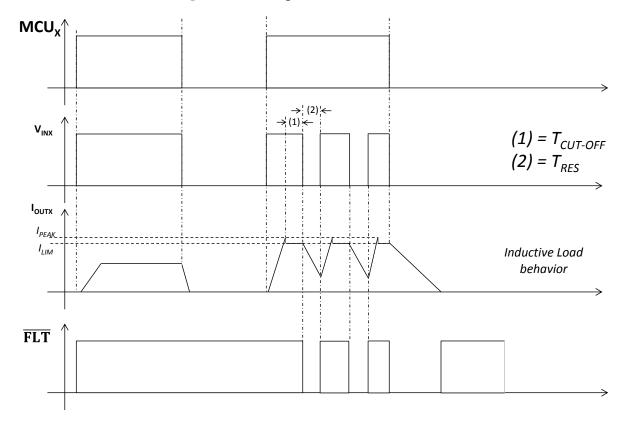

In case  $I_{LIM}$  threshold is triggered, the power stage remains in the current limitation condition ( $I_{OUTx} = I_{LIM}$ ) at least for  $t_{coff}$ . When  $t_{coff}$  elapses, the power stage is turned off and restarted after the  $t_{res}$  restart time. The fault condition is reported both on  $\overline{FLT}$  pin and on the input pin (INx) corresponding to the channel in fault. The internal cut-off flag signal is latched at power stage switch-off and released after the time  $t_{res}$ . The same behavior is reported on  $\overline{FLT}$  pin and on the INx pins related to the OUTx in fault. If one of the four channels is in overload protection, the other channels (in operating conditions) work properly. The status of  $\overline{FLT}$  is independent of the INx pin status, and is low during the whole cut-off time ( $t_{res}$ ). The same behavior has to be respected on fault signals on input pins.

If CoD pin is shorted to SGND ground plane (cut-off feature disabled) then the output channel remains ON, in current limitation condition, until the related input becomes LOW or the thermal protection threshold is triggered.

Figure 9. Cut-off signalization behavior on FLT

DS12305 - Rev 7 page 12/25

#### 6.4 Open load in off-state

The IC provides the open load detection feature, which detects if the load is disconnected (wire break) from the OUTx pin when in OFF-state (INx = LOW). This feature can be activated by placing a proper resistor ( $R_{PD}$ ) between OUTx and PGND ground plane.

SUPPLY RAIL

Voc

Open Load

Detection Signal

GROUND PLANE

Figure 10. Open load off-state

The voltage on OUTx pin  $(V_{OUTx})$  is internally compared with the  $V_{OLOFF}$  threshold: if the related INx pin is LOW and the  $V_{OUTX}$  goes lower than  $V_{OLOFF}$  then the open load condition is triggered. The fault condition is reported on the  $\overline{OL}$  pin and the fault reset occurs when load is reconnected. If the channel is switched ON by the related INx pin, the fault condition is no longer detected.

In OFF state, the IC achieves the open load detection feature by forcing the internally generated current  $I_{PU}$  (= 20  $\mu$ A) on the external pull-down resistor  $R_{PD}$ . The following design rule has to be followed in order to set the proper value of  $R_{PD}$ :

#### **Equation 3:**

$$R_{PD} < \frac{V_{OLOFF(\min)}}{I_{PU}} = \frac{V_{CC} - 4.5}{I_{PU}}$$

(3)

Note: When the load is connected the open load detection threshold must not be triggered:

#### **Equation 4:**

$$V_{OUTX} = V_{CC} * \frac{R_{PD}}{(R_{PD} + R_{LOAD})} > V_{OLOFF \text{ (max)}}$$

(4)

Therefore:

Equation 5:

$$R_{PD} > R_{LOAD} * \left[ \frac{V_{OLOFF(max)}}{\left( V_{CC} - V_{OLOFF(max)} \right)} \right]$$

(5)

Note: if two or more channels are parallelized then  $R_{PD}$  must be calculated according to the n\*Ipu (e.g. in case of 4 channels in parallel the total Ipu becomes 80uA).

DS12305 - Rev 7 page 13/25

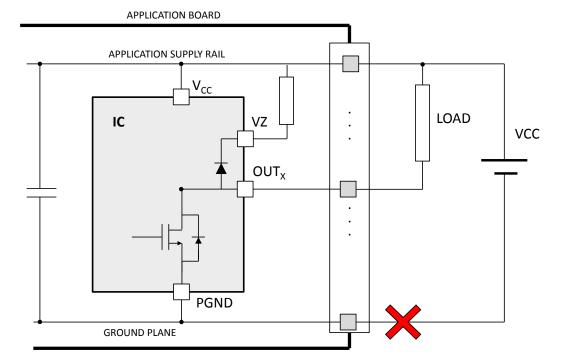

#### 6.5 GND wire break protection

GND wire break is intended as the disconnection event of the application board ground (where both SGND and PGND signals are connected) from the system ground of the external supply rail (see Figure 11. GND wire break where the shape between VZ and supply rail represents one of the application configurations: open circuit, short circuit or an external TVS).

When this event happens, the supply voltage at Vcc pin decreases until Vuvoff is triggered and then all power stages are turned off independently of the input status.

In case of inductive load, if the ground disconnection event happens while one or more channels are active:

- in case of Vz pins floating, the residual current in the inductor flows through the integrated power switch, which is activated by active clamp as if the input had been deactivated.

- in case of Vz pins connected to supply rail (by short circuit or by TVS), the residual current in the inductor flows through the catch diodes. Similarly, the catch diodes allows the proper ground disconnection protection even in case of Vz pins connected by a TVS to ground layer.

Figure 11. GND wire break

DS12305 - Rev 7 page 14/25

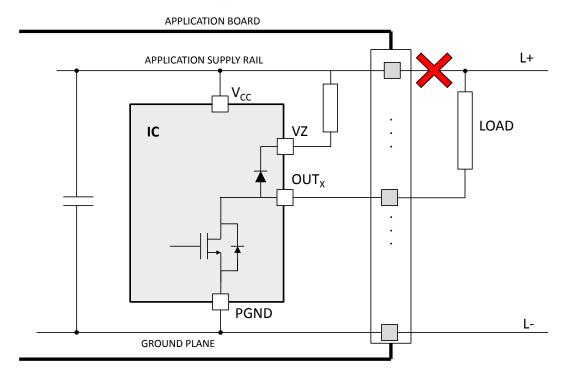

#### 6.6 VCC wire break protection

VCC wire break is intended as the disconnection of the application board form rail supply (see Figure 12. VCC wire break , where the shape between VZ and supply rail represents one of the application configurations: open circuit, short circuit or an external TVS). When this condition is detected, all power stage channels are turned off independently of the input status. The maximum steady-state current measured through a channel in short to the supply voltage is not greater than  $I_{VD}$  (see Table 7. Logic inputs). The same behavior is guaranteed when all channels are simultaneously in short to the supply voltage. In case of inductive load, if the VCC is disconnected while one or more channels are active, the current flows through the power, which is activated by the active clamp as if the input had been deactivated.

Figure 12. VCC wire break

VCC wire break protection is guaranteed when VZ floats or when VZ is connected to GND by a proper TVS, while it is limited (see below) when VZ is shorted to  $V_{CC}$ .

If VZ is connected to  $V_{CC}$  by a TVS (with clamping voltage =  $V_{CL}$ ), then VCC wire break protection is limited by the following design rule:  $V_{CL} > V_{L} + - (V_{OUT} + V_{D} + V_{UVLO})$ .

DS12305 - Rev 7 page 15/25

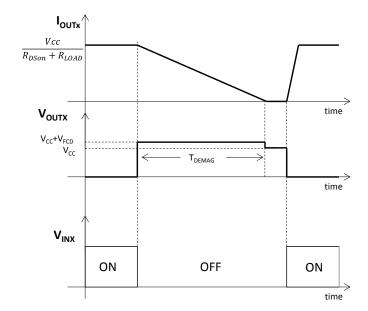

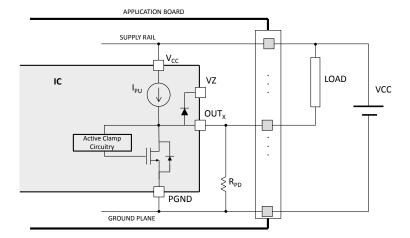

## 7 Active clamp

Active clamp is also known as fast demagnetization of inductive loads or fast current decay. When a low-side driver turns off an inductance, an overvoltage on load is detected. If VZ pins are directly shorted to the supply rail (see Figure 3) then the fast current decay is disabled: the inductive load is demagnetized slowly and according to the forward voltage of the integrated clamp diodes (V<sub>FCD</sub>). The figure below shows the typical waveforms of the load voltage and current in case of slow demagnetization.

Figure 13. V<sub>OUT</sub> and I<sub>OUT</sub> in case of slow demagnetization

If VZ pins are left floating (see Figure 1) or connected by a Zener or TVS diode to supply rail (see Figure 1) or PGND (see Figure 2) then the fast decay is activated. When VZ pins are left floating the integrated clamping circuit protects the IC despite overvoltages: the conduction state of the integrated switches is modulated in order to keep the OUTx pin voltage <  $V_{demag}$  until the energy in the load has been dissipated. The demagnetization energy is dissipated in the IC and it is limited by the internal heatsink capability, see EAS in Table 2. Absolute maximum ratings .

Figure 14. Active clamp equivalent principle schematic.

DS12305 - Rev 7 page 16/25

### 7.1 Fast current decay with TVS between VZ and supply rail

Being  $V_{CLZ}$  the clamping voltage of the external TVS, when the inductive load is turned off the OUTx pin is pulled up to  $V_{CC}+V_{CLZ}$ . In order to avoid any damage to the IC, the external diode must be selected such that  $V_{CLZ} < (V_{DEMAG(MIN)} - V_{CC})$ . Furthermore, the external diode must be selected such that it is able to dissipate the power due to the demagnetization currents flowing from the active channels.

Figure 15. V<sub>OUT</sub> and I<sub>OUT</sub> in case of fast demagnetization (fast decay)

#### 7.2 Fast current decay with TVS between VZ and PGND

Being  $V_{CLZ}$  the clamping voltage of the external TVS, when the inductive load is turned off the OUTx pin is clamped by the lower voltage between  $V_{CLZ}$  and  $V_{DEMAG(MIN)}$ . In order to avoid any leakage currrent on the external TVS has to be selected such that its  $V_{BR}$  results >  $V_{CC}$ , while in order to avoid any damage to the IC the  $V_{CLZ}$  of the external TVS must be selected such that  $V_{CLZ} < V_{DEMAG(MIN)}$ . Further, the external diode must be selected such that it is able to dissipate the power due to the demagnetization currents flowing from the active channels.

DS12305 - Rev 7 page 17/25

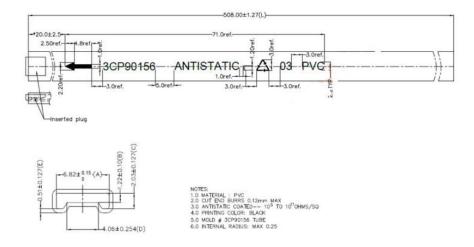

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

### 8.1 HTSSOP20 package information

Figure 16. HTSSOP20 package outline

Table 10. HTSSOP20 mechanical data

| ъ:   |      | mm   |      |       | inch   |        |  |

|------|------|------|------|-------|--------|--------|--|

| Dim. | Min. | Тур. | Max. | Min.  | Тур.   | Max.   |  |

| Α    |      |      | 1.2  |       |        | 0.047  |  |

| A1   |      |      | 0.15 |       | 0.004  | 0.006  |  |

| A2   | 0.8  | 1    | 1.05 | 0.031 | 0.039  | 0.041  |  |

| b    | 0.19 |      | 0.30 | 0.007 |        | 0.012  |  |

| С    | 0.09 |      | 0.20 | 0.004 |        | 0.0089 |  |

| D    | 6.4  | 6.5  | 6.6  | 0.252 | 0.256  | 0.260  |  |

| D1   | 4.1  | 4.2  | 4.3  | 0.161 | 0.165  | 0.169  |  |

| E    | 6.2  | 6.4  | 6.6  | 0.244 | 0.252  | 0.260  |  |

| E1   | 4.3  | 4.4  | 4.5  | 0.169 | 0.173  | 0.177  |  |

| E2   | 2.9  | 3.0  | 3.1  | 0.114 | 0.118  | 0.122  |  |

| е    |      | 0.65 |      |       | 0.0256 |        |  |

| K    | 0°   |      | 8°   | 0°    |        | 8°     |  |

| L    | 0.45 | 0.60 | 0.75 | 0.018 | 0.024  | 0.030  |  |

DS12305 - Rev 7 page 18/25

## 9 Packaging information

### 9.1 HTSSOP20 packaging information

Figure 17. Carrier Tape for HTSSOP20 20L

Figure 18. HTSSOP20 Shipping Tube

DS12305 - Rev 7 page 19/25

# 10 Ordering information

### **Table 11. Ordering information**

| Order code | Package   | Packing       |

|------------|-----------|---------------|

| IPS4260L   | HTSSOP20  | Tube          |

| IPS4260LTR | 111330F20 | Tape and reel |

DS12305 - Rev 7 page 20/25

## **Revision history**

**Table 12. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Oct-2017 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20-Sep-2019 | 2        | Modified Table 3. Thermal data, Features update () , Minor text updates inside Description , Rephrased Section 2.3 VZ , Rephrased Section 2.6 Open load in off-state, Updated Typ. in Table 5. Output stage, Updated Max. in Table 6. Switching (V $_{CC}$ = 24 V; R $_{LOAD}$ = 24 $\Omega$ , input rise time < 0.1 $\mu s$ ), Tcoff and IVD updated in Table 8. Protection and diagnostic , Rephrased Section 6.2 Overtemperature, Updated Equation 3: Equation 4: Equation 5: Added fig 18 Figure 2 . |

| 06-Apr-2020 | 3        | Modified Table 4. Supply, Table 5. Output stage, Table 8. Protection and diagnostic, minor text updates inside the document.                                                                                                                                                                                                                                                                                                                                                                             |

| 29-Jun-2020 | 4        | Correct thermal data values in Table 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30-Jul-2021 | 5        | Updated section Section 6.4 Open load in off-state                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18-Sep-2023 | 6        | Added $I_Z$ value in Table 2. Absolute maximum ratings; changed values of $t_{\text{BKT}}$ in Table 8. Protection and diagnostic.                                                                                                                                                                                                                                                                                                                                                                        |

| 07-Nov-2023 | 7        | Added standard compliances in Section Features; changed $LOAD_X$ to $OUT_X$ pin name in the whole document; changed $CoD$ , $I_{LIM}$ and $LOAD_X$ pin type in Table 1. Pin configuration; some minor changes.                                                                                                                                                                                                                                                                                           |

DS12305 - Rev 7 page 21/25

## **Contents**

| 1    | Bloc           | ck diagram                                             | 2  |  |

|------|----------------|--------------------------------------------------------|----|--|

| 2    | Pin            | description                                            | 3  |  |

|      | 2.1            | VCC                                                    | 4  |  |

|      | 2.2            | PGND, SGND                                             | 4  |  |

|      | 2.3            | VZ                                                     | 4  |  |

|      | 2.4            | IN1, IN2, IN3, IN4                                     | 4  |  |

|      | 2.5            | OUT1, OUT2, OUT3, OUT4                                 | 4  |  |

|      | 2.6            | Open load in off-state                                 | 4  |  |

|      | 2.7            | FLT                                                    | 4  |  |

|      | 2.8            | I <sub>LIM</sub>                                       | 4  |  |

|      | 2.9            | CoD                                                    | 4  |  |

| 3    | Abs            | olute maximum ratings                                  | 5  |  |

| 4    | Elec           | trical characteristics                                 | 6  |  |

| 5    | Pow            | ver stage logic                                        | 9  |  |

| 6    | Prot           | ection and diagnostic                                  | 11 |  |

|      | 6.1            | Undervoltage lock-out                                  | 11 |  |

|      | 6.2            | Overtemperature                                        | 11 |  |

|      | 6.3            | Current limitation and cut-off                         | 11 |  |

|      | 6.4            | Open load in off-state                                 | 13 |  |

|      | 6.5            | GND wire break protection                              | 14 |  |

|      | 6.6            | VCC wire break protection                              | 15 |  |

| 7    | Acti           | ve clamp                                               | 16 |  |

|      | 7.1            | Fast current decay with TVS between VZ and supply rail | 17 |  |

|      | 7.2            | Fast current decay with TVS between VZ and PGND        | 17 |  |

| 8    | Pacl           | kage information                                       | 18 |  |

|      | 8.1            | HTSSOP20 package information                           | 18 |  |

| 9    | Pacl           | kaging information                                     | 19 |  |

|      | 9.1            | HTSSOP20 packaging information                         | 19 |  |

| 10   | Orde           | ering information                                      | 20 |  |

| Rev  |                | history                                                |    |  |

|      | _ist of tables |                                                        |    |  |

| List | ist of figures |                                                        |    |  |

## **List of tables**

| Table 1.  | Pin configuration                                                                       | . 3 |

|-----------|-----------------------------------------------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                                                                | . 5 |

| Table 3.  |                                                                                         |     |

| Table 4.  | Supply                                                                                  | . 6 |

| Table 5.  | Output stage                                                                            | . 6 |

| Table 6.  | Switching ( $V_{CC}$ = 24 V; $R_{LOAD}$ = 24 $\Omega$ , input rise time < 0.1 $\mu s$ ) | . 6 |

| Table 7.  | Logic inputs                                                                            | . 8 |

| Table 8.  | Protection and diagnostic                                                               | . 8 |

| Table 9.  | Power stage (OUTx pin) truth table                                                      | . 9 |

| Table 10. | HTSSOP20 mechanical data                                                                | 18  |

| Table 11. | Ordering information                                                                    | 20  |

| Table 12. | Document revision history                                                               | 21  |

# **List of figures**

| Figure 1.  | Block diagram                                                                      | . 2 |

|------------|------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connection (top view)                                                          | . 3 |

| Figure 3.  | $t_{\text{rise}}$ and $t_{\text{fall}}$                                            | . 7 |

| Figure 4.  | $t_{PD(L-H)}$ and $t_{PD(H-L)}$                                                    | . 7 |

| Figure 5.  | Application circuit (fast decay enabled by TVS between Vz and supply rail)         |     |

| Figure 6.  | Application circuit (fast decay enabled by TVS between VZ and PGND)                | . 9 |

| Figure 7.  | Application circuit (fast decay disabled by Vz shorted to supply rail)             | 10  |

| Figure 8.  | Thermal protection signalization behavior on FLT                                   | 11  |

| Figure 9.  | Cut-off signalization behavior on FLT                                              | 12  |

| Figure 10. | Open load off-state                                                                |     |

| Figure 11. | GND wire break                                                                     |     |

| Figure 12. | VCC wire break                                                                     |     |

| Figure 13. | V <sub>OUT</sub> and I <sub>OUT</sub> in case of slow demagnetization              | 16  |

| Figure 14. | Active clamp equivalent principle schematic                                        | 16  |

| Figure 15. | V <sub>OUT</sub> and I <sub>OUT</sub> in case of fast demagnetization (fast decay) | 17  |

| Figure 16. | HTSSOP20 package outline                                                           | 18  |

| Figure 17. | Carrier Tape for HTSSOP20 20L                                                      | 19  |

| Figure 18. | HTSSOP20 Shipping Tube                                                             | 19  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

DS12305 - Rev 7 page 25/25