# L9800

# Automotive 8-channel LS driver

# Features

| Symbol               | Parameter                                                   | Values                           |

|----------------------|-------------------------------------------------------------|----------------------------------|

| V <sub>BATT</sub>    | Supply voltage                                              | 3 V to 28 V                      |

| V <sub>DDIO</sub>    | Supply and SO buffer voltage                                | 3 V to 5.5 V                     |

| R <sub>DS(ON)</sub>  | Maximum on-state resistance at T <sub>J</sub> = 150 °C      | 1.7 Ω                            |

| I <sub>L(NOM)</sub>  | Nominal load current (T <sub>A</sub> = 85 °C, all channels) | 330 mA                           |

| E <sub>AR</sub>      | Maximum energy dissipation - repetitive                     | 10 mJ at I <sub>L</sub> = 220 mA |

| V <sub>DS(CL)</sub>  | Minimum drain-source clamping voltage                       | 42 V                             |

| I <sub>L(OVL0)</sub> | Maximum overload switch off threshold                       | 3 A                              |

| f <sub>SCLK</sub>    | Maximum SPI clock frequency                                 | 8 MHz                            |

Product status link

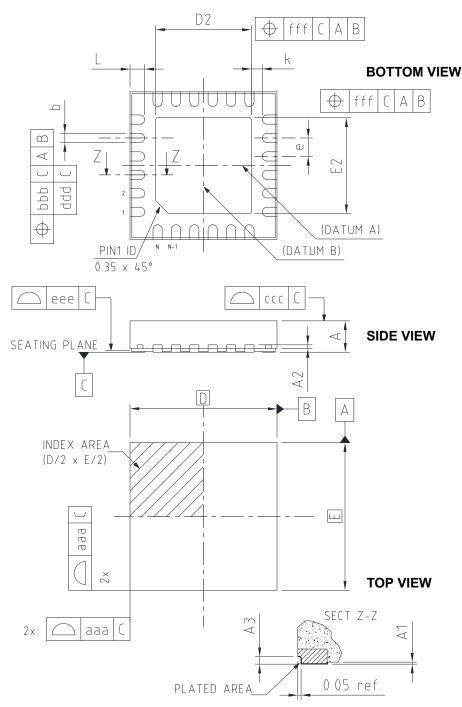

TFQFN24 4x4x0.9

| Product summary |                 |  |  |  |

|-----------------|-----------------|--|--|--|

| Order code      | L9800           |  |  |  |

| Package         | TFQFN24 4x4x0.9 |  |  |  |

| Packing         | Tray            |  |  |  |

| Order code      | L9800-TR        |  |  |  |

| Package         | TFQFN24 4x4x0.9 |  |  |  |

| Packing         | Tape and reel   |  |  |  |

- AEC-Q100 qualified

- Full ISO26262 compliant, ASIL-B systems ready

- General

•

- Eight LS drivers

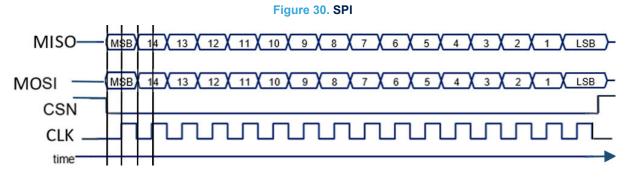

- 16-bit SPI interface for outputs control and for diagnosis data communication

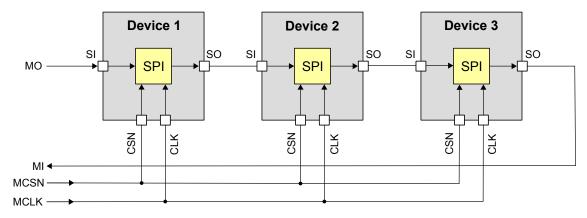

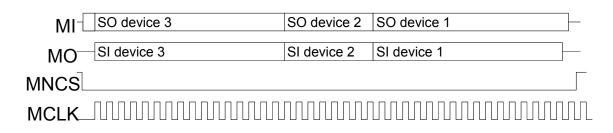

- Daisy chain compatible and available even with 8-bit SPI

- 2 parallel input pins with input mapping functionality

- Cranking capability down to V<sub>BATT</sub> = 3 V

- Digital supply voltage range compatible with 3.3 V and 5 V MCU

- Bulb inrush mode (BIM) to drive 2 W lamps and electronic loads

- Two independent internal PWM generators for MCU offloads and to drive LEDs

- Very low quiescent current (with usage of IDLE pin)

- Limp-home mode (with usage of IDLE and IN pins)

- Safety features

- Temperature sensor and monitoring

- Serial communications using address feedback, 1 parity bit, frame counter and short frame detection

- Fail-safe activation via input pins

- Safe operation at low battery voltage (cranking)

- Protective functions

0

- Overcurrent latch off

- Lower supply voltage range for extended operation

- Electrostatic discharge (ESD) protection

- Reverse battery protection on VBATT without external components

- Short circuit battery protection

- Thermal shutdown latch off

- Diagnostic features

- Latched diagnostic information via SPI register

- Overcurrent and overtemperature detection at on state

- Off state diagnosis, able to detect and distinguish open load and short to GND conditions

# **Applications**

- Low-side switches for 12 V in automotive or industrial applications such as lighting, heating, motor driving, energy and power distribution

- Especially designed for driving relays, LEDs and motors

## **Description**

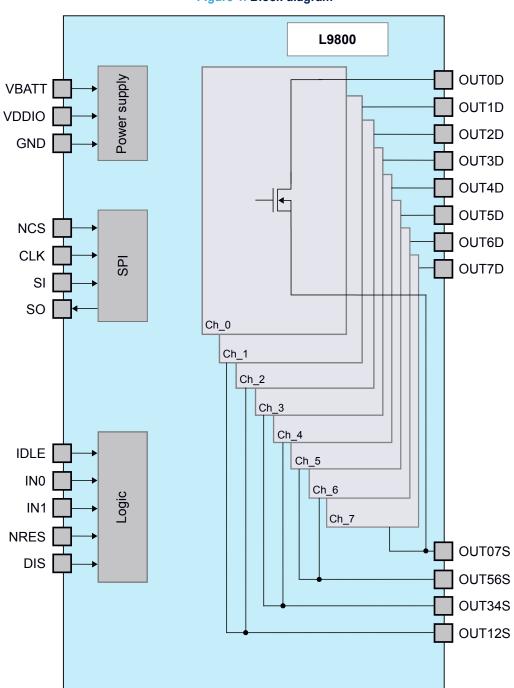

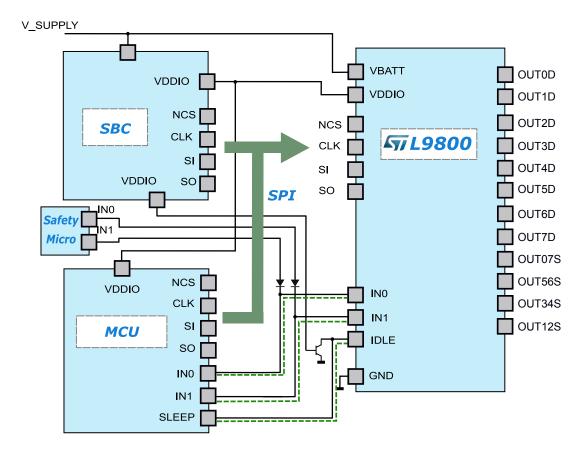

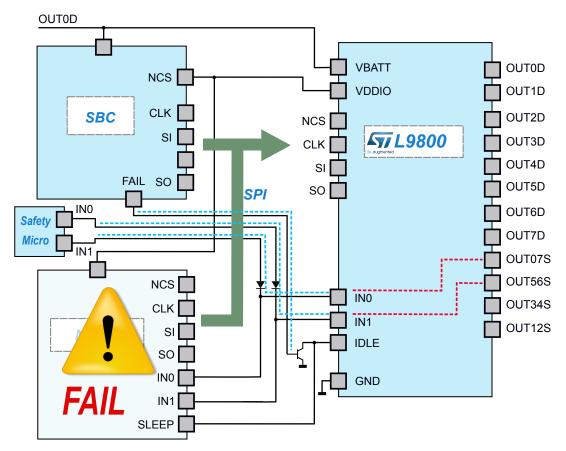

The L9800 is an 8-channel LS driver designed for automotive applications (LEDs and relays) and compatible with resistive, inductive and capacitive loads. The device offers advanced diagnostic and protection functionalities such as open load, overcurrent and overtemperature detections, short to GND. The eight output channels can be driven by SPI or by dedicated parallel inputs. Limp-home functionality is present. Daisy chain available (no constraint on SPI number of bits of devices in chain). The device is able to guarantee cranking scenario down to  $V_{BATT} = 3 V$  and ensures very low-quiescent current under RESET.

The device is an 8-channel low-side power switch in a TFQFN24 4x4x0.9 package. It is specially designed to control relays and LEDs in automotive and industrial applications.

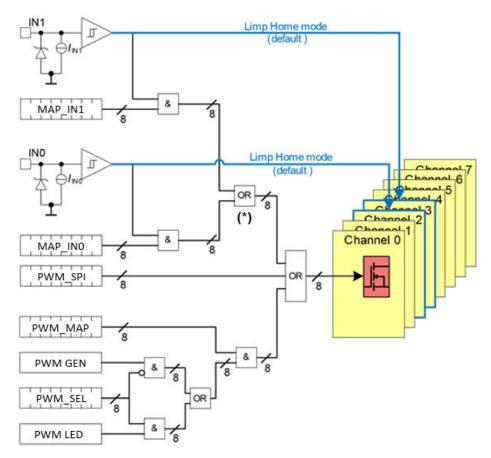

A serial peripheral interface (SPI) is used for control and diagnosis of the loads as well as of the device. For direct control and PWM there are two input pins (IN0 and IN1) available, connected to two outputs by default (OUT2 and OUT3). Additional or different outputs can be controlled by the same input pins if programmed by SPI.

# 1 Detailed description

The L9800 is an 8-channel IC, made of low-side drivers. All the outputs have typical  $R_{DS(ON)} = 0.77 \ \Omega$  at  $T_J = 25 \ ^{\circ}C$ . The 16-bit serial peripheral interface (SPI) is used to control and diagnose the device and the loads. The SPI interface provides daisy chain capability to assemble multiple devices in one SPI chain by using the same number of microcontroller pins.

This device is designed for low supply voltage operation, it is able to maintain its functionality at low battery voltage (VBATT  $\geq$  3 V). The SPI communication, including the ability to program the device, are present only when the digital power supply is available (VDDIO  $\geq$  3 V).

The L9800 has two input pins (IN0 and IN1) respectively connected by default to the outputs OUT2 and OUT3, making them controllable even when the digital supply voltage is not available. Thanks to the input mapping functionality, it is possible to connect the input pins to different outputs, or to assign more outputs to the same input pin. In this case, when the device is in fail-safe mode (limp-home), more channels can be controlled with one signal applied to one input pin.

In limp-home mode the IN0 is mapped on channel 2 and IN1 is mapped on channel 3. When the IDLE pin is "low", it is possible to activate the two channels using the input pins independently from the presence of the digital supply voltage VDDIO.

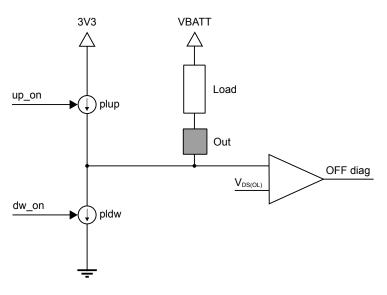

The device provides diagnosis of the load by detecting the open-load in the off state and the short-circuit. For diagnosis of the off state (triggered by the SPI request), two current sources (pull-up and pull-down current) are activated in two separate steps. The device detects an abnormal voltage on the output and, in case of fault detection, it is able to differentiate open-load from short condition.

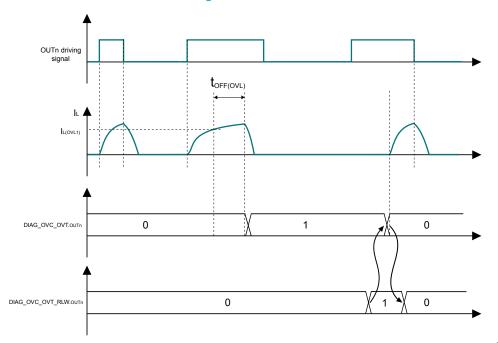

Each output stage is able to avoid short circuits. In case of overload, the affected channel is switched off with an increased slew rate (gate kill) when the overload detection current  $I_{L(OVLn)}$  is reached and can be reactivated via SPI after clearing the register in which the fault is registered.

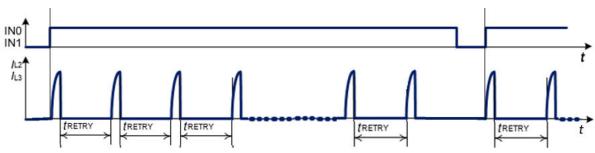

In limp-home state, the channel linked to an input pin set to 'high' where an OVL fault is detected is automatically restarted after the restart time of the t<sub>RETRY</sub> output.

Temperature sensors are available for each channel to protect the device in case of over-temperature in the on condition.

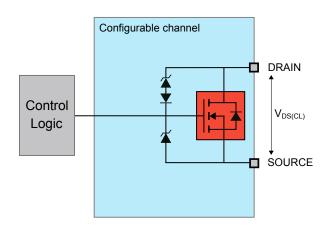

The power transistors are built by N-channel power MOSFET. The device is integrated in Smart Power technology.

# 2 Block diagram and pin description

Figure 1. Block diagram

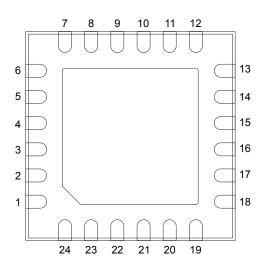

# Figure 2. Pin configuration (bottom view)

#### Table 1. Pin description

| Pin # | Pin name | Description              | I/O type |

|-------|----------|--------------------------|----------|

| 1     | OUT7D    | Drain 7                  | 0        |

| 2     | OUT6D    | Drain 6                  | 0        |

| 3     | OUT56S   | Source 5–6               | 0        |

| 4     | OUT5D    | Drain 5                  | 0        |

| 5     | NRES     | NRES function            | I        |

| 6     | IN1      | Parallel command input 1 | I        |

| 7     | INO      | Parallel command input 2 | I        |

| 8     | GND      | Ground pin               |          |

| 9     | IDLE     | Idle function            | I        |

| 10    | VDDIO    | IO supply                |          |

| 11    | SO       | SPI output stream        | 0        |

| 12    | CLK      | SPI clock                | I        |

| 13    | NCS      | SPI chip select          | I        |

| 14    | SI       | SPI input stream         | I        |

| 15    | OUT4D    | Drain 4                  | 0        |

| 16    | OUT34S   | Source 4                 | 0        |

| 17    | OUT3D    | Drain 3                  | 0        |

| 18    | DIS      | Channel disable          | I        |

| 19    | OUT2D    | Drain 2                  | 0        |

| 20    | OUT12S   | Source 1–2               | 0        |

| 21    | OUT1D    | Drain 1                  | 0        |

| 22    | VBATT    | Battery voltage          |          |

| 23    | OUT07S   | Source 0–7               | 0        |

| 24    | OUT0D    | Drain 0                  | 0        |

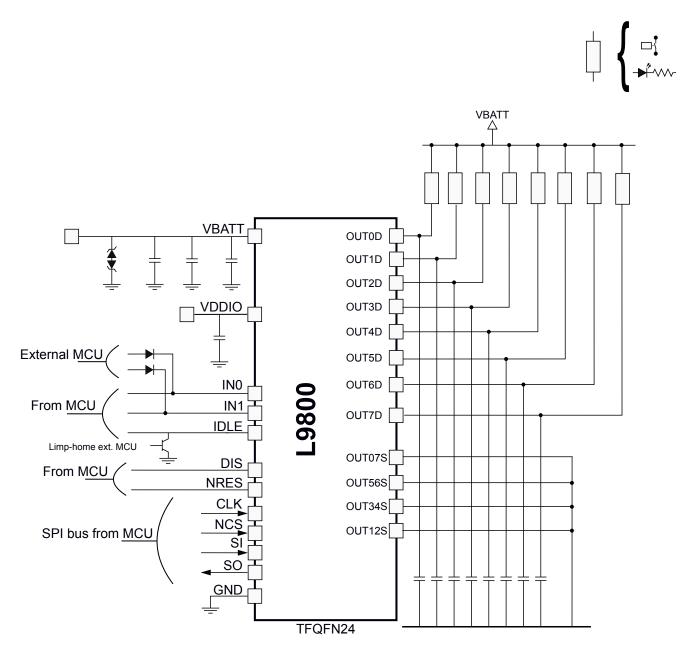

# 3 Application circuit

Here below a general application circuit with the TFQFN24 package.

#### Figure 3. L9800 application circuit

| Pin                                 | External components |                     |      |      |      | Requirement <sup>(1)</sup> | Comment                                        |

|-------------------------------------|---------------------|---------------------|------|------|------|----------------------------|------------------------------------------------|

| F 111                               | Туре                | Min.                | Тур. | Max. | Unit | Requirement                | Comment                                        |

| Capacitor 120 nF 2., 3. Tolerance : |                     | Tolerance ±20% 50 V |      |      |      |                            |                                                |

|                                     | Capacitor           |                     | 100  |      | μF   | 2.                         | 50 V, Transient and load dump protection       |

| VBATT                               | TVS                 | -15                 |      | 38   | V    | 4.                         | Transient voltage suppressor                   |

|                                     | Capacitor           |                     | 10   |      | μF   | 2., 3.                     | Tolerance ±20%                                 |

|                                     | Capacitor           |                     | 10   |      | μι   | 2., 3.                     | 50 V, Transient and load dump protection       |

| VDDIO                               | Capacitor           |                     | 100  |      | nF   | 2.                         | Tolerance ±10% 50 V                            |

| OUT2D-OUT7D                         | Capacitor           |                     |      | 12   | nF   | 3.                         | Maximum total capacitance value at output load |

Table 2. External components list

1. Refer to the following Items.

In the list of external components, the different parts are marked following the items reported below:

- 1. Mandatory components for L9800 functionality.

- 2. Recommended components for EMC robustness.

- 3. Recommended components for ESD trials.

- 4. Recommended system component.

*Note:* Recommended components may depend on the requirements at system level and shall be confirmed by specific tests on the final applications.

# 4 Product characteristics

### 4.1 Operating range

Within the operating range, the part operates as specified and without parameter deviations. The device may not operate properly if maximum operating conditions are exceeded.

Exceeding operating conditions and going back within, the part recovers with no damage or degradation. Additional supply voltage and temperature conditions are given separately at the beginning of each electrical specification table.

All voltages are related to the GND ground pin.

#### Table 3. Operating conditions

| Symbol | Description                                                                  | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------------------------------------|------|------|------|------|

|        | Operating ranges                                                             |      |      |      |      |

|        | Supply voltage range for normal operations                                   | 6    | -    | 18   | V    |

|        | Upper supply voltage range for extended operations                           | 18   | -    | 28   | V    |

| VBATT  | Load dump voltage range for extended operations                              | 28   | -    | 42   | V    |

|        | Lower supply voltage range for extended operations                           | 3    | -    | 6    | V    |

|        | Supply voltage range for normal operations while shorted externally to VDDIO | 3    | -    | 5.5  | V    |

| VDDIO  | Logic supply voltage                                                         | 3    | -    | 5.5  | V    |

| TJ     | Operating junction temperature range                                         | -40  | -    | 150  | °C   |

#### 4.1.1 Supply voltage ranges

The device operates on the 12 V system. Transient operation for these systems can reach 40 V maximum. Particular care has to be taken in PCB manufacturing to keep thermal dissipation to a reasonable level.

- For VBATT < 3 V, if VDDIO is included in its operative range, the device is in a safety state (internal circuitries are on but all the outputs are off). VS\_UV function can be disabled by VS\_UV\_MASK bit of the CFG\_0 register.

- For VBATT up to 40 V, all the functions are granted with increased power dissipation and no reset is asserted during the transient.

For detailed functionality description, refer to the Table 9.

### 4.2 Absolute maximum ratings

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

All voltages are related to the potential at the ground pin (GND).

| Table 4. Absolute maximum rate | capabilities |      |

|--------------------------------|--------------|------|

| Description                    | Min.         | Тур. |

| Symbol                | Description                                    | Min. | Тур. | Max.                | Unit |  |  |  |

|-----------------------|------------------------------------------------|------|------|---------------------|------|--|--|--|

|                       | AMR - supplies                                 |      |      |                     |      |  |  |  |

| VBATT                 | Battery voltage                                | -16  | -    | 42                  | V    |  |  |  |

| VDDIO                 | I/O voltage                                    | -0.3 | -    | 20                  | V    |  |  |  |

| V <sub>BATT(LD)</sub> | Supply voltage in load dump                    |      | -    | 42                  | V    |  |  |  |

| V <sub>BATT(SC)</sub> | Supply voltage in short circuit (single pulse) |      | -    | 28                  | V    |  |  |  |

| V <sub>DS0</sub>      | Voltage at power transistor OUT0               | -0.3 | -    | V <sub>DS(CL)</sub> | V    |  |  |  |

| V <sub>DS7</sub>      | Voltage at power transistor OUT7               | -0.3 | -    | V <sub>DS(CL)</sub> | V    |  |  |  |

| V <sub>OUT07S</sub>   | Power transistor source voltage OUT07          | -0.3 | -    | 0.3                 | V    |  |  |  |

| Symbol              | Description                           | Min.                      | Тур. | Max.                | Unit |

|---------------------|---------------------------------------|---------------------------|------|---------------------|------|

| V <sub>OUT0D</sub>  | Power transistor drain voltage OUT0   | - 1 <sup>(1)</sup>        | -    | 42                  | V    |

| V <sub>OUT7D</sub>  | Power transistor drain voltage OUT7   | <b>- 1</b> <sup>(1)</sup> | -    | 42                  | V    |

| V <sub>DS1</sub>    | Voltage at power transistor OUT1      | -0.3                      | -    | V <sub>DS(CL)</sub> | V    |

| V <sub>DS2</sub>    | Voltage at power transistor OUT2      | -0.3                      | -    | V <sub>DS(CL)</sub> | V    |

| V <sub>OUT12S</sub> | Power transistor source voltage OUT12 | -0.3                      | -    | 0.3                 | V    |

| V <sub>OUT1D</sub>  | Power transistor drain voltage OUT1   | <b>- 1</b> <sup>(1)</sup> | -    | 42                  | V    |

| V <sub>OUT2D</sub>  | Power transistor drain voltage OUT2   | <b>- 1</b> <sup>(1)</sup> | -    | 42                  | V    |

| V <sub>DS3</sub>    | Voltage at power transistor OUT3      | -0.3                      | -    | V <sub>DS(CL)</sub> | V    |

| V <sub>DS4</sub>    | Voltage at power transistor OUT4      | -0.3                      | -    | V <sub>DS(CL)</sub> | V    |

| V <sub>OUT34S</sub> | Power transistor source voltage OUT34 | -0.3                      | -    | 0.3                 | V    |

| V <sub>OUT3D</sub>  | Power transistor drain voltage OUT3   | - 1 <sup>(1)</sup>        | -    | 42                  | V    |

| V <sub>OUT4D</sub>  | Power transistor drain voltage OUT4   | - 1 <sup>(1)</sup>        | -    | 42                  | V    |

| V <sub>DS5</sub>    | Voltage at power transistor OUT5      | -0.3                      | -    | V <sub>DS(CL)</sub> | V    |

| V <sub>DS6</sub>    | Voltage at power transistor OUT6      | -0.3                      | -    | V <sub>DS(CL)</sub> | V    |

| V <sub>OUT56S</sub> | Power transistor source voltage OUT56 | -0.3                      | -    | 0.3                 | V    |

| V <sub>OUT5D</sub>  | Power transistor drain voltage OUT5   | - 1 <sup>(1)</sup>        | -    | 42                  | V    |

| V <sub>OUT6D</sub>  | Power transistor drain voltage OUT6   | - 1 <sup>(1)</sup>        | -    | 42                  | V    |

|                     | IDLE pin                              |                           |      |                     | 1    |

| V <sub>IDLE</sub>   | Voltage at IDLE pin                   | -0.3                      | -    | 20                  | V    |

|                     | IN0,1 pins                            |                           |      |                     | 1    |

| V <sub>IN0</sub>    | Voltage at input pins IN0             | -0.3                      | -    | 20                  | V    |

| V <sub>IN1</sub>    | Voltage at input pins IN1             | -0.3                      | -    | VDDIO + 0.3         | V    |

|                     | DIS, NRES pins                        |                           |      |                     |      |

| V <sub>DIS</sub>    | Voltage at DIS pin                    | -0.3                      | -    | 20                  | V    |

| V <sub>RES</sub>    | Voltage at RES pin                    | -0.3                      | -    | 20                  | V    |

|                     | SPI pins–SI, NCS, SCLI                | ۲                         |      |                     |      |

| V <sub>SI</sub>     | Voltage at SI pin                     | -0.3                      | -    | 20                  | V    |

| V <sub>NCS</sub>    | Voltage at NCS pin                    | -0.3                      | -    | 20                  | V    |

| V <sub>CLK</sub>    | Voltage at CLK pin                    | -0.3                      | -    | 20                  | V    |

| V <sub>SO</sub>     | Voltage at serial output pin SO       | -0.3                      | -    | VDDIO + 0.3         | V    |

1. Case of short to GND with GND shift or ISOPULSE condition1.

### Table 5. ESD requirements

| ltem                             | Test condition                           | Min.        | Max.      | Unit |

|----------------------------------|------------------------------------------|-------------|-----------|------|

| All pins                         | НВМ                                      | -2          | 2         | kV   |

| All pins                         | CDM (values for corner pins in brackets) | -500/(-750) | 500/(750) | V    |

| Pins to connector <sup>(1)</sup> | НВМ                                      | -4          | 4         | kV   |

1. All pins are connected to GND.

# 4.3 Temperature ranges and thermal data

#### Table 6. Temperature ranges

| Symbol            | Description                              | Min. | Max. | Unit |

|-------------------|------------------------------------------|------|------|------|

| T <sub>A</sub>    | Operating temperature (ECU environment)  | -40  | 125  | °C   |

| TJ                | Operating junction temperature           | -40  | 150  | °C   |

| T <sub>stg</sub>  | Storage temperature                      | -55  | 150  | °C   |

| T <sub>ot</sub>   | Thermal shut-down temperature            | 175  | 200  | °C   |

| O <sub>Thys</sub> | Thermal shut-down temperature hysteresis | 5    | 15   | °C   |

### Table 7. Thermal data

| Symb             | ool | Parameter                                                                    | Тур. | Unit |

|------------------|-----|------------------------------------------------------------------------------|------|------|

| R <sub>thJ</sub> | IA  | Thermal resistance, junction-to-ambient–TFQFN24 $\ensuremath{package}^{(1)}$ | 42   | °C/W |

1. With 2s2p PCB thermally enhanced.

# 5 Input/output

# 5.1 Control pins

The device has three pins (IN0, IN1 and IDLE) to check directly the device without using SPI.

# 5.2 Input pins (IN0, IN1)

The L9800 has two input pins, IN0 and IN1, by default IN0 is connected to channel 2, IN1 is connected to channel 3. It is possible through programming MAP\_IN0 and MAP\_IN1 (input mapping registers) to link different channels to each input IN0 or IN1 with priority assigned to MAP\_IN0. If for example, both mapping registers are written to control the same channel, it follows the IN0 pin. The Figure 23 describes how the actuation of the channels is managed. The channels are driven by the signals that are the OR combination between PWM\_SPI\_register status, PWM generators (PWM generator output mapping status), IN0 and IN1. The STA\_0 (status register) shows the logic level of the input pins. See Section 7: Power stages for further details.

The logic level of the input pins can be monitored via the STA\_0 register. In the STA\_0 register, it is also possible to monitor the status of DIS and NRES pins. The input status monitor is operative also when the device is in limphome mode. If one of the input pins is set to "high" and the IDLE pin is set to "low", the device switches into limphome mode and activates the channel mapped by default to the input pins.

## 5.3 Reset pin

The NRES pin is the reset input for the device. As default, the state of the NRES pin is masked by the logic. The user must send a specific SPI frame (setting NRES\_EN or NRES\_N\_EN bit on the CFG\_0 register) to force the logic to take into account the state of the NRES pin. The function uses the inverse logic, if the NRES pin is low, the device is held in an internal reset state, all output channels are disabled, and all registers are reset to their default values. An internal pull-down holds the NRES pin asserted in case of an open pin.

Both NRES\_EN and NRES\_N\_EN are intended to enable/disable the NRES pin.

- When the NRES\_EN bit is 1 the NRES pin is enabled; in this case, a reset event on the NRES pin puts the registers in the default conditions, and the NRES pin in this case is disabled.

- When the NRES\_N\_EN is set to 1, the NRES pin is enabled, but the reset event puts the registers in default conditions while the NRES pin remains enabled.

## 5.4 DIS pin

The DIS pin is used to enable/disable the output stages. As default, the DIS pin is masked by the logic. The user needs to send a specific SPI frame (setting the DIS\_EN bit on the CFG\_0 register) to force the logic to take into account the state of the DIS pin:

- When the DIS pin is high, all channels are disabled if the pin is not masked. An internal pull-up holds the DIS pin asserted in case of an open pin.

- When the DIS pin is set low, all channels are enabled based on their configuration settings. The status of the DIS pin can be monitored reading the STA\_0 register.

The DIS pin can be connected to a general purpose output pin of the microcontroller or to an alternative safety circuit.

# 5.5 IDLE pin

The device enters in sleep state through IDLE pin when it is set to "low" together with INO and IN1. Instead if IDLE pin is in "low" state and one of the two inputs are in "high" state the device is brought in limp-home mode.

To ensure a correct transition IDLE pin should be set at least for a time duration of  $t_{\text{IDLEFLT}_max}$ .

Setting the IDLE pin to "low", with both INO and IN1 also at "low" value, has the following consequences:

- The SPI registers are reset to default value if IN0 and In1 are set to "low".

- To decrease the current consumption the voltage detection circuits on VDDIO and VBATT are disabled, if both IN0 and IN1 are set to "low". Instead if one of the two inputs is set to "high", the core is enabled with channel 2 and channel 3 driving circuits.

- No SPI communication is kept, the SO pin remains in "HighZ" even if NCS pin is active and the SPI communication is not allowed.

# 5.6 Electrical parameters

3V < VBATT < 18 V, 3 V < VDDIO < 5.5 V, T  $_{\rm J}$  = -40 °C to 150 °C, unless otherwise noticed.

| Symbol               | Description                                 | Test condition                        | Min. | Nom. | Max. | Unit |

|----------------------|---------------------------------------------|---------------------------------------|------|------|------|------|

| V <sub>IDLE(L)</sub> | L-input level                               |                                       |      | -    | 0.8  | V    |

| V <sub>IDLE(H)</sub> | H-input level                               |                                       | 2.0  | -    |      | V    |

| R <sub>IDLE</sub>    | Input pull-down resistor at IDLE pin        | VDDIO = 5 V, V <sub>DIS</sub> = 2 V   | 50   | -    | 180  | kΩ   |

|                      | Input pins I                                | N0 and IN1                            |      |      |      |      |

| V <sub>IN(L)</sub>   | L-input level                               |                                       |      | -    | 0.8  | V    |

| V <sub>IN(H)</sub>   | H-input level                               |                                       | 2.0  | -    |      | V    |

| R <sub>IN</sub>      | Input pull-down resistor at IN0 and IN1 pin | VDDIO = 5 V, V <sub>IN</sub> = 2 V    | 50   | -    | 180  | kΩ   |

|                      | Input pi                                    | n NRES                                |      |      |      |      |

| V <sub>NRES(L)</sub> | L-input level                               |                                       |      | -    | 0.8  | V    |

| V <sub>NRES(H)</sub> | H-input level                               |                                       | 2.0  | -    |      | V    |

| R <sub>NRES</sub>    | Input pull-down resistor at NRES pin        | VDDIO = 5 V, V <sub>NRES</sub> = 2 V  | 50   | -    | 180  | kΩ   |

|                      | Input r                                     | oin DIS                               |      |      |      |      |

| V <sub>DIS(L)</sub>  | L-input level                               |                                       |      | -    | 0.8  | V    |

| V <sub>DIS(H)</sub>  | H-input level                               |                                       | 2.0  | -    |      | V    |

| R <sub>DIS</sub>     | Input pull-up resistor at DIS pin           | VDDIO = 5 V, V <sub>DIS</sub> = 0.8 V | 35   | -    | 100  | kΩ   |

### Table 8. Digital input/output electrical performance

# 6 Power supply

The L9800 is fed by two supply voltages:

- VBATT (general supply for analog and digital part)

- VDDIO (supply for digital output buffers)

The VBATT supply line is connected to a battery feed and used for the driving circuitry of the power stages. VBATT and VDDIO supply voltages have an undervoltage detection circuit, which prevents the activation of the associated function in case the measured voltage is below the undervoltage threshold.

An undervoltage on the VBATT supply voltage prevents the activation of the power stages. All channels are disabled, and are enabled again as soon as VBATT exits from the undervoltage condition.

An undervoltage on the VDDIO supply prevents any SPI communication. SPI read/write registers are reset to default values.

The device drains all the needed current from the highest supply among the two.

| Condition                     | VDDIO ≤ VDDIO <sub>(UV)</sub>        | VDDIO > VDDIO <sub>(UV)</sub>                                     |

|-------------------------------|--------------------------------------|-------------------------------------------------------------------|

|                               | Channels cannot be controlled        | Channels can be controlled only if the VS_UV_MASK bit is set to 1 |

| VBATT ≤ VBATT <sub>(UV)</sub> | SPI registers reset                  | SPI registers available                                           |

|                               | SPI communication not available      | SPI communication available                                       |

|                               | Limp-home mode not available         | Limp-home mode available (channels are off)                       |

|                               | Channels cannot be controlled by SPI | Channels can be switched on and off                               |

| $VBATT > VBATT_{(UV)}$        | SPI registers reset                  | SPI registers available                                           |

|                               | SPI communication not available      | SPI communication available                                       |

#### Table 9. Supply ranges

# 6.1 Operating modes

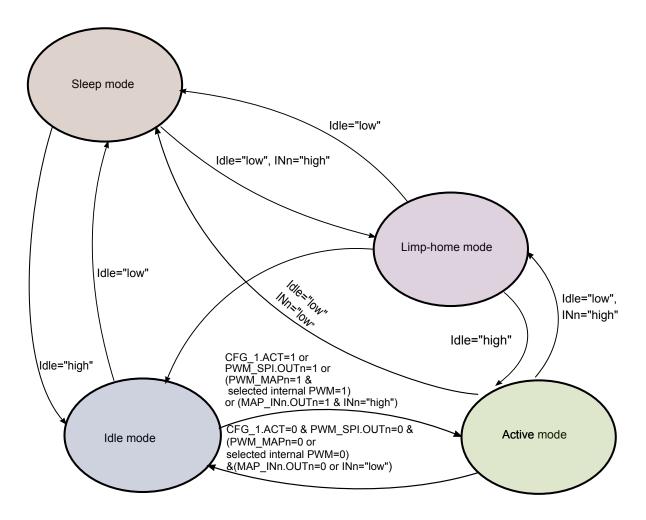

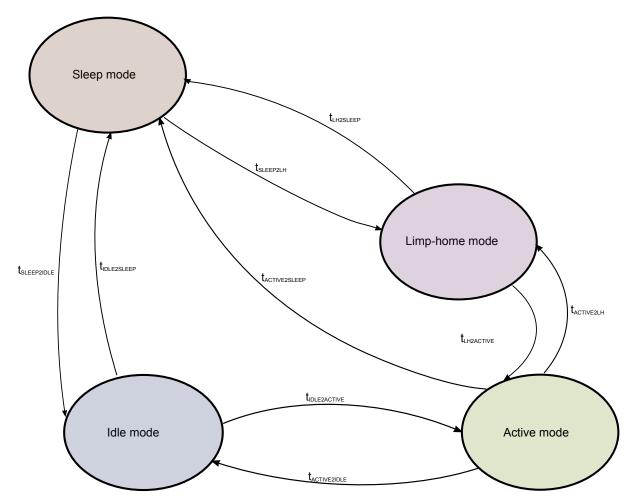

The L9800 has four operative states:

- Sleep mode

- Idle mode

- Active mode

- Limp-home mode

The transition between operation modes is determined according to the following levels and states:

- Logic level at IDLE pin

- Logic level at INn pins

- PWM\_SPI.OUTn bits state

- CFG\_1.ACT bit state

- MAP\_PWM.OUTn and PWM\_SEL.OUTn bits state

The state diagram including the possible transitions is shown in the Figure 4. The behavior of the device as well as some parameters may change depending on its operation mode. Furthermore, due to the undervoltage detection circuitry, which monitors VBATT and VDDIO supply voltages, some changes within the same operation mode can be seen accordingly.

In the case of VBATT < VBATT(UV\_L) and IDLE = IN0 = IN1 = high channel outputs are disabled.

The operation mode of the device can be observed by:

- Status of output channels

- Status of SPI registers

- Current consumption at VBATT pin (I<sub>VBATT</sub>)

The default operation mode to switch on the loads is active mode. If the device is not in active mode and a request to switch on one or more outputs occurs (via SPI or via input pins) it switches into active or limp-home mode, according to IDLE pin status. Due to the time needed for such transitions, output turn-on time  $t_{ON}$  is extended due to the mode transition latency.

The state diagram is described in the Figure 4. It is valid if the digital NPOR is '1'. In the case of POR='0' transitions from active to idle and from limp-home to sleep do not ensure switch off behavior with functional timings, but the switch off times extended to t<sub>OFF\_POR</sub>. An NPOR condition is registered in clear on the read NPOR bit of the STA 1 register.

In the case of condition IDLE='0' and INn='0' (corresponding to the transition from active to sleep) the device moves in sleep mode. The transition ACTIVE2SLEEP is not effective if at least one channel is on (only when SPI and PWM drive the channels). In order to turn off a channel before the transition from active to sleep, the bit CFG\_0. ACTIVE TO SLEEP DIS SWR shall be set to 1.

The Table 10 shows the correlation between device operation modes, VBATT and VDDIO supply voltages, and the state of the most important functions (channels operativity, SPI communication, and SPI registers).

| Function          | Undervoltage co             | ndition on VBATT            | VBATT not in                | Operating modes             |                 |

|-------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------|

| Function          | VDDIO ≤ VDDIO <sub>UV</sub> | VDDIO > VDDIO <sub>UV</sub> | VDDIO ≤ VDDIO <sub>UV</sub> | VDDIO > VDDIO <sub>UV</sub> | Operating modes |

|                   | u                           | u                           | u                           | u                           | Sleep           |

| Channels          | u                           | u                           | u                           | u                           | Idle            |

| Channels          | u                           | u <sup>(1)</sup>            | a <sup>(2)</sup>            | а                           | Active          |

|                   | u                           | u <sup>(3)</sup>            | a <sup>(2)</sup>            | a <sup>(2)</sup>            | Limp-home       |

|                   | u                           | u                           | u                           | u                           | Sleep           |

| SPI communication | u                           | а                           | u                           | а                           | Idle            |

| SPI communication | u                           | а                           | u                           | а                           | Active          |

|                   | u                           | <b>a</b> <sup>(4)</sup>     | u                           | <b>a</b> <sup>(4)</sup>     | Limp-home       |

|                   | r                           | r                           | r                           | r                           | Sleep           |

| SPI registers     | r                           | а                           | r                           | а                           | Idle            |

|                   | r                           | а                           | r                           | а                           | Active          |

|                   | r                           | <b>a</b> <sup>(4)</sup>     | r                           | а                           | Limp-home       |

#### Table 10. Supply ranges and operative modes

1. Available in case VS\_UV\_MASK bit is set to 1.

- 2. IN pins only.

- 3. Only OUT2 and OUT3 available in case VS\_UV\_MASK bit is set to 1.

- 4. Read only.

#### Where:

- "a" stands for available

- "u" stands for unavailable

- "r" stands for reset

#### 6.1.1 Power-up

The power-up condition is satisfied if, at least, one of the supply voltages (VBATT or VDDIO) is applied to the device and the INn or IDLE pins are set to "high".

In case of both VBATT and VDDIO device pins connected to external sources, the VBATT voltage must be included in its supply voltage range for normal operations (VBATT > 6 V).

In case of only the VBATT device pin connected to an external source, the VBATT voltage must be included in its supply voltage range for normal operations (VBATT > 6 V).

All the possible power-up scenarios are described below:

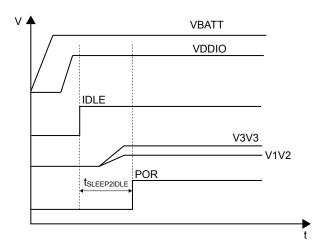

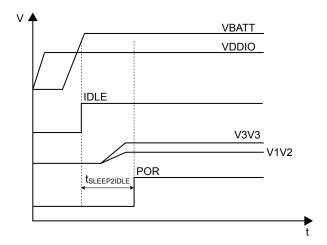

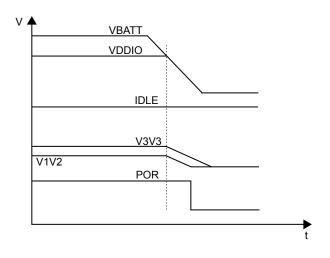

#### Figure 5. Scenario 1 power-up

**Scenario 1**: power-up by VBATT with VDDIO present in sleep to idle transition. Both VBATT and VDDIO are applied in their operative range (6 V to 18 V and 3 V to 5.5 V respectively). IDLE is set to high and the POR signal is released after  $t_{SLEEP2IDLE}$  (about 10 µs).

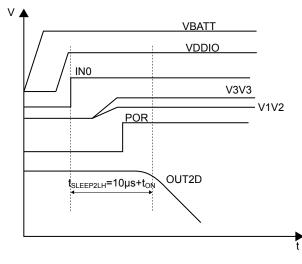

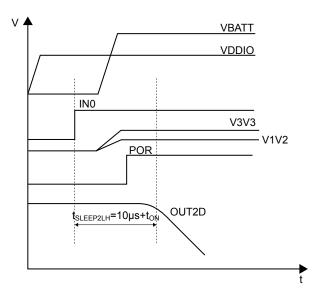

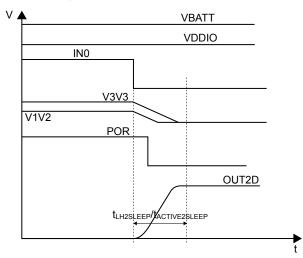

#### Figure 6. Scenario 2 power-up

**Scenario 2**: power-up by VBATT with VDDIO present in sleep to limp-home transition. Both VBATT and VDDIO are applied in their operative range (6 V to 18 V and 3 V to 5.5 V respectively). IN0 (or IN1) is set to high; the POR signal is released after 10  $\mu$ s and OUTD2 reaches 90% of VBATT in t<sub>ON</sub> time.

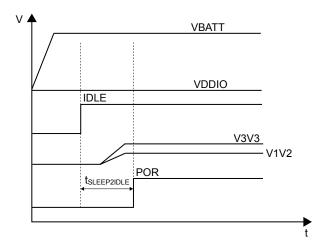

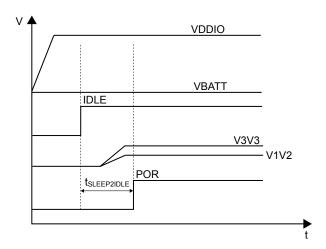

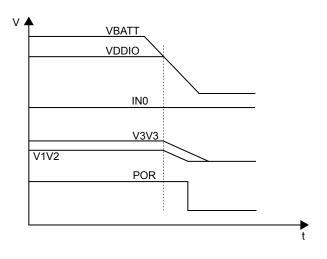

#### Figure 7. Scenario 3 power-up

**Scenario 3**: power-up by VBATT without VDDIO (0 V) in sleep to idle transition. VBATT is applied in its operative range (6 V to 18 V). IDLE is set to high and the POR signal is released after  $t_{SLEEP2IDLE}$  (about 10 µs). SPI communication is not available and registers are reset.

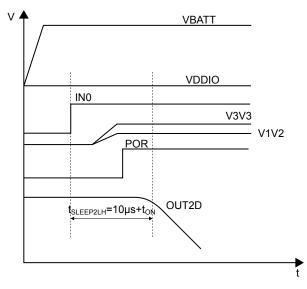

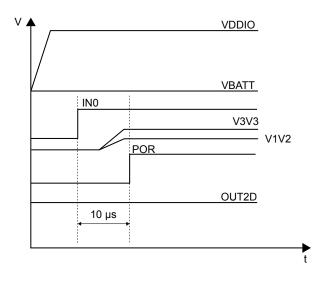

#### Figure 8. Scenario 4 power-up

**Scenario 4**: power-up by VBATT without VDDIO (0 V) in sleep to limp-home transition. VBATT is applied in its operative range (6 V to 18 V). IN0 (or IN1) is set to high; the POR signal is released after about 10  $\mu$ s and OUT2D reaches 90% of VBATT in t<sub>ON</sub> time. SPI communication is not available and registers are reset.

#### Figure 9. Scenario 5 power-up

**Scenario 5**: power-up by VDDIO with VBATT present in sleep to idle transition. Both VBATT and VDDIO are applied in their operative range (6 V to 18 V and 3 V to 5.5 V respectively). IDLE is set to high and the POR signal is released after  $t_{SLEEP2IDLE}$ .

#### Figure 10. Scenario 6 power-up

**Scenario 6**: power-up by VDDIO with VBATT present in sleep to limp-home transition. Both VBATT and VDDIO are applied in their operative range (6 V to 18 V and 3 V to 5.5 V respectively). IN0 (or IN1) is set to high; the POR signal is released after about 10  $\mu$ s and DRAIN OUT2 reaches 90% of VBATT in t<sub>ON</sub> time.

#### Figure 11. Scenario 7 power-up

**Scenario 7**: power-up by VDDIO without VBATT (0 V) in sleep to idle transition. VDDIO is applied in its operative range (3 V to 5.5 V). IDLE is set to high and the POR signal is released in  $t_{SLEEP2IDLE}$  (about 10 µs).

#### Figure 12. Scenario 8 power-up

**Scenario 8**: power-up by VDDIO without VBATT (0 V) in sleep to limp-home transition. VDDIO is applied in its operative range (3 V to 5.5 V). IN0 (or IN1) is set to high; the POR signal is released after 10  $\mu$ s but OUT2D does not turn on.

#### 6.1.2 Sleep mode

In sleep mode, the outputs of L9800 are OFF and the SPI registers are reset to default values. The current consumption is reduced to the  $I_{VDDIO(SLEEP)}$  and  $I_{VBATT(SLEEP)}$ . Refer to the parameters  $I_{VDDIO(SLEEP)}$  and  $I_{VBATT(SLEEP)}$  in the Table 11. Power supply.

#### 6.1.3 Idle mode

In idle mode, the current consumption of the device reaches the parameters  $I_{VDDIO(IDLE)}$  and  $I_{VBATT(IDLE)}$ . The on diagnosis functions are available only in read mode. During idle mode the output channels are disabled. The SPI communication is properly working, when the VDDIO is present. In idle mode DIAG\_OVC\_OVT bits are not clearable.

#### 6.1.4 Active mode

The active mode is needed when there are loads to drive. Voltage levels of VDDIO and VBATT influence the behavior as described at the beginning of Section 6: Power supply. The current consumption is described through these two parameters:  $I_{VDDIO(ACTIVE)}$  and  $I_{VBATT(ACTIVE)}$ . In case CFG\_1.ACT is set to "1", the device enters in active mode and remains in this state independently of the status of input pins, internal PWM generators, and PWM\_SPI.OUTn bits.

If CFG\_1.ACT is set to "0", the device comes back to idle mode as soon as all inputs pins are set to "low", PWM\_SPI.OUTn bits are set to "0" and in case of turn off command by PWM generators if properly configured.

If CFG\_1.ACT is set to "1", the device remains in active mode independently of the status of input pins, PWM\_SPI.OUTn register and PWM generators registers status. An undervoltage condition on VDDIO supply brings the device into idle mode if IN0 and IN1 are set to "low". If CFG\_1.ACT is set to "0", the registers MAP\_IN0, MAP\_IN1 (together with the input pins) and MAP\_PWM (together with the related PWM duty cycle) have to be correctly configured to switch to active mode.

#### 6.1.5 Limp-home mode

The L9800 is brought into limp-home mode when one of the two input pins is asserted (this means the enabling of the channel connected to it) and also the idle pin is set to "low". The SPI communication is possible only in readonly mode (SPI registers can be read but cannot be written). If the application is used in limp-home mode, in IDLE and ACTIVE the channels 2 and 3 cannot be used in BIM mode.

More in detail:

- MODE bits are set to "01B" (limp-home mode).

- Overload and overtemperature diagnostics on channel 2 and 3 are available and the related DIAG\_OVC\_OVT bits can be read.

- DIAG\_OPL\_OFF and DIAG\_SHG bits, referred to diagnostics executed during a previous active phase, can be read via SPI request.

During the transition from limp-home mode to sleep, the complete set of L9800 registers is not accessible for writing until it remains in the limp-home state and is set to their default values.

Refer to Section 6.1: Operating modes for a detailed description of supply voltage conditions required to switch on channels 2 and 3 during limp-home, the other channels are kept off.

#### 6.1.6 Power supply transition

The time to turn on a channel is defined as  $t_{ON}$  both in active and limp-home mode. In all other cases, the transition time is reported as shown in Figure 13.

#### 6.1.7 Reset

The following four conditions reset the SPI register (r/w) to the default value:

- 1. VDDIO is not present or below the minimum value of VDDIO(UV)

- 2. IDLE pin is set to "low" with both INn "low"

- 3. A reset command (CFG\_1.RST set to "1") is executed

- 4. NRES pin asserted

DIAG\_OVC\_OVT bits are not cleared by a reset command (for functional safety).

STA\_1.VDDIO\_UV and STA\_1.VBATT\_UV bits are not cleared by a reset command (for functional safety). In particular, all channels are switched OFF (if there are no input pin set to "high") and the input mapping configuration is reset.

## 6.1.8 Undervoltage on VBATT

If the device is operative and the supply voltage drops below  $VBATT_{(UV_L)}$ , the logic sets the bit  $STA_1.VBATT_UV$  to "1". As soon as the supply voltage VBATT is above  $VBATT_{(UV_H)}$ , the bit  $STA_1.VBATT_UV$  is set back to "0" after the first clear on read.

Undervoltage condition on VBATT may influence the status of the channels according to VS\_UV\_MASK bit status, as described in the Table 18.

#### 6.1.9 Low operating power-on VDDIO

When the VDDIO supply voltage drops in the range indicated by  $VDDIO_{(UV)}$ , the bit STA\_1.VDDIO\_UV is set to "1". This is valid if the digital NPOR is '1'. For all conditions that generate an NPOR = 0, a dedicated clear on read STA\_1. NPOR bit is set. As soon as VDDIO overcomes the minimum of the voltage operative threshold  $VDDIO_{(UV_{RECOVERY})}$  the bit STA\_1.VDDIO\_UV is set to "0" after the first clear on read.

One of the following conditions generates the NPOR condition (reset of the whole internal logic):

- 1. General internal supply failure (internal 3.3 V supply in UV or bandgap reference not correct)

- 2. VDDIO < VDDIO<sub>(UV)</sub> AND IN1 = 0 AND IN0 = 0

#### 6.1.10 Power-down

The power-down condition is satisfied if both supply voltages undergo 3 V or, if at least one of them is applied to the device in its operative range, the INn and IDLE pins are all set to "low". If one or more channels are switched on before power-down, it is necessary to assert a reset to ensure a correct turn-off timing. All possible power-down scenarios are described here below:

#### Figure 14. Scenario 1 power-down

**Scenario 1**: power-down with both supplies dropping together under 3 V. Although IDLE is high internal supply reference and  $v_{bg}$  drop; POR is set to zero. IN0 = IN1 = 0 V.

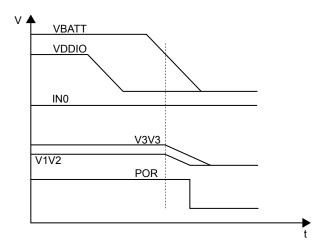

#### Figure 15. Scenario 2 power-down

**Scenario 2**: power-down with both supplies dropping together under 3 V. Although IN0 is high internal supply reference and  $v_{bg}$  drop; POR is set to zero. IDLE = IN1 = 0 V.

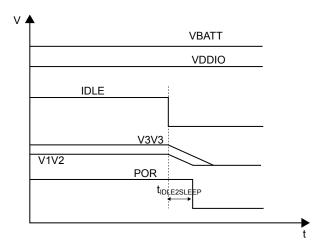

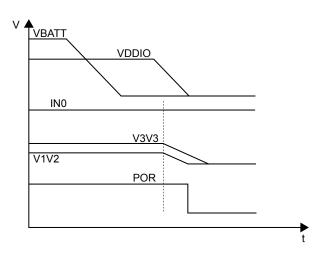

#### Figure 16. Scenario 3 power-down

**Scenario 3**: idle to sleep transition with VDDIO and VBATT in their operative range (at least one of them). IDLE is set to low, V3V3 supply reference and  $v_{bg}$  drop, and POR is set to zero by  $t_{IDLE2SLEEP}$  of about 10 µs. IN0 = IN1 = 0 V.

Figure 17. Scenario 4 power-down

**Scenario 4**: limp to sleep transition (IDLE=0) and active to sleep transition (IDLE = 1  $\rightarrow$  0) with VDDIO and VBATT in their operative range (at least one of them). IN0 is set to low, V3V3 supply reference and v<sub>bg</sub>, POR goes down to zero and the corresponding channel is switched off within 150 µs, IN1 can be already 0 or can follow IN0 behavior.

#### Figure 18. Scenario 5 power-down

**Scenario 5**: power-down with VBATT ping down after VDDIO. When even VBATT undergoes 2 V, although IN0 is still high, internal supply reference and  $v_{bg}$ ; POR is set to zero. IDLE = IN1 = 0 V.

#### Figure 19. Scenario 6 power-down

**Scenario 6**: power-down with VDDIO ping down after VBATT. When even VDDIO undergoes 3 V, although IN0 is still high, internal supply reference and  $v_{bg}$ ; POR is set to zero, IDLE = IN1 = 0 V. As for scenario 5, the same condition happens if, instead of IN0, one of the other pins is high or two of them or all of them.

# 6.2 Electrical parameters

3 V < VBATT < 18 V, 3 V < VDDIO < 5.5 V, T<sub>J</sub> = -40 °C to 150 °C, unless otherwise noticed.

| Symbol                                        | Description                                                                                                                                   | Comment                                                                                                                                                                 | Min. | Nom. | Max. | Unit  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                               |                                                                                                                                               | VBATT pin                                                                                                                                                               |      |      |      |       |

| VBATT <sub>(UV_L)</sub>                       | Analog supply<br>undervoltage low<br>threshold                                                                                                |                                                                                                                                                                         | 2.65 | 2.8  | 3    | V     |

| VBATT <sub>(UV_H)</sub>                       | Analog supply<br>undervoltage high<br>threshold                                                                                               |                                                                                                                                                                         | 2.7  | 2.85 | 3.1  | V     |

| dVBATT/dt <sub>pwrup</sub>                    | Battery slew rate during<br>power-up (VBATT from<br>10% to 90%)                                                                               |                                                                                                                                                                         | 0.5  |      |      | V/min |

| dVBATT/dt <sub>pwrup</sub>                    | Battery slew rate during<br>power-up (VBATT from<br>10% to 90%)                                                                               |                                                                                                                                                                         |      |      | 2    | V/µs  |

| 1                                             | Current consumption                                                                                                                           | V <sub>IDLE</sub> = 0 V, V <sub>INn</sub> = 0 V,<br>VDDIO = 5 V, T <sub>J</sub> ≤ 85 °C                                                                                 |      |      | 1    | μA    |

| IVBATT(SLEEP)                                 | from VBATT in sleep mode                                                                                                                      | V <sub>IDLE</sub> =0 V, V <sub>INn</sub> = 0 V,<br>VDDIO = 5 V, 85 °C ≤ T <sub>J</sub> ≤ 150 °C                                                                         |      |      | 14   | μΑ    |

| I <sub>VBATT</sub> (IDLE)                     | Analog supply current consumption in idle mode                                                                                                | $V_{IDLE} = 5 V, V_{INn} = 0 V,$<br>$VDDIO = 5 V, f_{SCLK} = 0 MHz,$<br>$CFG_1.ACT = 0_B,$<br>$PWM\_SPI.OUTn = 0_B,$<br>$DIAG\_OFF\_EN.OUTn = 0_B$                      |      |      | 2.2  | mA    |

| l <sub>VBATT</sub> (IDLE) T <sub>J</sub> high | Analog supply current consumption in idle mode for $T_J$ high                                                                                 | $V_{IDLE} = 5 V, V_{INn} = 0 V,$<br>$VDDIO = 5 V, f_{SCLK} = 0 MHz,$<br>$CFG_1.ACT = 0_B,$<br>$PWM\_SPI.OUTn = 0_B,$<br>$DIAG\_OFF\_EN.OUTn = 0_B, T_J > 100 °C$        |      |      | 2.3  | mA    |

| IVBATT(IDLE_COR)                              | Analog supply current<br>consumption in idle<br>mode from VBATT pin<br>when VBATT is lower<br>than VDDIO (the device<br>is supplied by VDDIO) | $V_{IDLE} = 5V, V_{INn} = 0 V,$<br>$VDDIO = 5 V, f_{SCLK} = 0 MHz,$<br>$CFG_1.ACT = 0_B,$<br>$PWM\_SPI.OUTn = 0_B,$<br>$DIAG\_OFF\_EN.OUTn = 0_B,$<br>VBATT = VDDIO-1 V | -0.1 |      | 0.1  | mA    |

| IVBATT(ACTIVE)                                | Analog supply current<br>consumption in active<br>mode - channels OFF                                                                         | $V_{IDLE} = 5 V, V_{INn} = 0 V,$<br>$VDDIO = 5 V, f_{SCLK} = 0 MHz,$<br>$CFG_1.ACT = 1_B,$<br>$PWM\_SPI.OUTn = 0_B,$<br>$DIAG\_OFF\_EN.OUTn = 0_B$                      |      |      | 4.3  | mA    |

#### Table 11. Power supply

L9800 Power supply

| Symbol                       | Description                                                         | Comment                                          | Min. | Nom. | Max. | Unit  |

|------------------------------|---------------------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

|                              | Analog supply current                                               | $V_{IDLE}$ = 5 V, $V_{INn}$ =0 V,                |      |      |      |       |

|                              | consumption in active                                               | VDDIO = 5 V, f <sub>SCLK</sub> = 0 MHz,          |      |      |      |       |

| IVBATT(ACTIVE_COR)           | mode - channels OFF<br>from VBATT pin when                          | $CFG_1.ACT = 1_B,$                               | -0.1 |      | 0.1  | mA    |

| VBATI(ACTIVE_COR)            | VBATT is lower than                                                 | $PWM\_SPI.OUTn=0_B,$                             |      |      |      |       |

|                              | VDDIO (the device is<br>supplied by VDDIO)                          | $DIAG_OFF_EN.OUTn = 0_B$ ,                       |      |      |      |       |

|                              |                                                                     | VBATT=VDDIO - 1 V                                |      |      |      |       |

| T <sub>VBATTUVFLT</sub>      | VBATT undervoltage filter                                           | Covered by SCAN                                  | 9    | 14   | 19   | μs    |

|                              |                                                                     | VDDIO pin                                        |      |      |      |       |

| VDDIO(OP)                    | VDDIO supply operating voltage range                                | $f_{SCLK}$ = 8 MHz, design info                  | 3.0  |      | 5.5  | V     |

| VDDIO <sub>(UV)</sub>        | Undervoltage shut down threshold                                    | MISO from "low" to high-Z                        | 2.65 | 2.8  | 3    | V     |

| VDDIO(UV_RECOVERY)           | Analog supply threshold<br>for recovery after<br>VDDIO undervoltage | MISO from "low" to high-Z                        | 2.7  | 2.85 | 3.1  | V     |

| dVDDIO/dt <sub>pwrup</sub>   | Supply slew rate during<br>power-up (VDDIO from<br>10% to 90%)      |                                                  |      |      | 2    | V/µs  |

|                              | VDDIO supply current in sleep mode                                  | V <sub>IDLE</sub> = 0 V, V <sub>INn</sub> = 0 V, |      |      |      |       |

|                              |                                                                     | VDDIO = 5 V, T <sub>J</sub> ≤ 85 °C              |      |      | 1    |       |

| IVDDIO(SLEEP)                |                                                                     | $V_{IDLE} = 0 V, V_{INn} = 0 V,$                 |      |      |      | μA    |

|                              |                                                                     | VDDIO = 5 V, T <sub>J</sub> = 150 °C             |      |      | 2    |       |

|                              |                                                                     | $V_{IDLE} = 5 V, V_{INn} = 0 V,$                 |      |      |      |       |

|                              |                                                                     | VDDIO = 5 V, $f_{SCLK}$ = 0 MHz,                 |      |      |      |       |

| IVDDIO(IDLE)                 | VDDIO supply current in                                             | $CFG_1.ACT = 0_B,$                               |      |      | 1.2  | mA    |

| (IDLE)                       | idle mode                                                           | $PWM\_SPI.OUTn = 0_B,$                           |      |      | 1.2  | III/A |

|                              |                                                                     | $DIAG_OFF_EN.OUTn = 0_B$                         |      |      |      |       |

|                              |                                                                     | $V_{IDLE} = 5 V, V_{INn} = 0 V,$                 |      |      |      |       |

|                              |                                                                     |                                                  |      |      |      |       |

| L                            | VDDIO supply current in                                             | VDDIO = 5 V, $f_{SCLK}$ = 0 MHz,                 |      |      |      |       |

| $I_{VDDIO}(IDLE) T_{J}$ high | idle mode for $T_J$ high                                            | $CFG_1.ACT = 0_B,$                               |      |      |      |       |

|                              |                                                                     | $PWM\_SPI.OUTn = 0_B,$                           |      |      |      |       |

|                              |                                                                     | DIAG_OFF_EN.OUTn = 0 <sub>B</sub>                |      |      |      |       |

|                              |                                                                     | $V_{IDLE} = 5 V, V_{INn} = 0 V,$                 |      |      |      |       |

|                              | VDDIO supply current in idle mode from VDDIO                        | VDDIO = 5 V, f <sub>SCLK</sub> = 0 MHz,          |      |      |      |       |

| IVDDIO(IDLE)                 | pin when VBATT is                                                   | $CFG_1.ACT = 0_B,$                               |      |      | 2.2  | mA    |

|                              | lower than VDDIO (the device is supplied by                         | $PWM\_SPI.OUTn = 0_B,$                           |      |      |      |       |

|                              | VDDIO)                                                              | $DIAG_OFF_EN.OUTn = 0_B$ ,                       |      |      |      |       |

|                              |                                                                     | VBATT = VDDIO - 1 V                              |      |      |      |       |

|                              | VDDIO supply current in                                             | $V_{IDLE}$ = 5 V, $V_{INn}$ = 0 V,               |      |      |      |       |

|                              | active mode-channels                                                | VDDIO = 5 V, f <sub>SCLK</sub> = 0 MHz,          |      |      |      |       |

| IVDDIO(ACTIVE)               | OFF from VDDIO pin when VBATT is lower                              | CFG_1.ACT = 1 <sub>B</sub> ,                     |      |      | 4.2  | mA    |

|                              | than VDDIO (the device                                              | $PWM\_SPI.OUTn = 0_B,$                           |      |      |      |       |

|                              | is supplied by VDDIO)                                               | $DIAG_OFF_EN.OUTn = 0_B,$                        |      |      |      |       |

| Symbol                    | Description                                                   | Comment                                                                        | Min. | Nom.     | Max.                  | Uni |

|---------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------|------|----------|-----------------------|-----|

|                           |                                                               | VBATT = VDDIO - 1 V                                                            |      |          |                       |     |

|                           | Logic supply current in                                       | V <sub>IDLE</sub> = 5 V, V <sub>INn</sub> = 0 V,                               |      |          |                       |     |

|                           | active mode–channels<br>OFF from VDDIO pin                    | VDDIO = 5 V, f <sub>SCLK</sub> = 0 MHz,                                        |      |          |                       | mA  |

| VDDIO(ACTIVE_COR)         | when VBATT is higher                                          | $CFG_1.ACT = 1_B, PWM_SPI.OUTn = 0_B,$                                         |      |          | 1.2                   |     |

|                           | than VDDIO (the device is supplied by VDDIO)                  | DIAG_OFF_EN.OUTn = 0 <sub>B</sub>                                              |      |          |                       |     |

| T <sub>VDDIOUVFLT</sub>   | VDDIO undervoltage filter                                     | Covered by SCAN                                                                | 9    | 14       | 19                    | μs  |

|                           |                                                               | Timings                                                                        |      |          |                       |     |

| t <sub>IDLEFLT</sub>      | Idle filter time                                              | Covered by SCAN                                                                | 4.9  | 7        | 10                    | μs  |

| t <sub>SLEEP2IDLE</sub>   | Sleep to idle delay                                           | Covered by SCAN                                                                |      |          | 120                   | μs  |

| t <sub>IDLE2SLEEP</sub>   | Idle to sleep delay                                           | From IDLE pin to sleep external pull-down MISO to GND required covered by SCAN |      |          | 10                    | μs  |

|                           |                                                               | From INn or NCS pins to MODE = $11_B$ ,                                        |      |          | 4                     | μs  |

| <sup>t</sup> IDLE2ACTIVE  | Idle to active delay                                          | covered by SCAN                                                                |      |          | 1                     |     |

| +                         | Active to idle delay                                          | From INn or NCS pins to MODE = $10_B$ ,                                        |      |          | 150                   |     |

| <sup>t</sup> ACTIVE2IDLE  |                                                               | covered by SCAN                                                                |      |          |                       |     |

| t                         | Sleep to limp-home delay                                      | From INn pins to $V_{DS}$ = 10% VBATT,                                         |      |          | 120 + t <sub>ON</sub> |     |

| tsleep2lh                 |                                                               | covered by SCAN                                                                |      |          | 120 + ION             | μs  |

|                           |                                                               | From INn pins to MODE = $00_B$ ,                                               |      |          |                       |     |

| t <sub>LH2SLEEP</sub>     | Limp-home to sleep delay                                      | external pull-down MISO to GND required,                                       |      | toff_por |                       | μs  |

|                           | ,                                                             | covered by SCAN                                                                |      |          |                       |     |

| t <sub>LH2ACTIVE</sub>    | Limp-home to active                                           | From IDLE pin to MODE = $11_B$                                                 |      | 20       |                       | μs  |

| LHZACTIVE                 | delay                                                         | covered by SCAN                                                                |      |          | 20                    | μο  |

| t <sub>ACTIVE2LH</sub>    | Active to limp-home                                           | From IDLE pin to MODE = $01_B$ ,                                               |      | 20       |                       | μs  |

| ACTIVE2LH                 | delay                                                         | covered by SCAN                                                                |      |          | 20                    | μο  |

|                           |                                                               | From IDLE pin to MODE = $00_B$ ,                                               |      |          |                       |     |

| t <sub>ACTIVE2SLEEP</sub> | Active to sleep delay                                         | External pull-down MISO to GND required,                                       |      |          | $t_{OFF\_POR}$        | μs  |

|                           |                                                               | Covered by SCAN                                                                |      |          |                       |     |

| toff_por                  | Channel switch off time<br>with passive pull-down<br>(NPOR=0) | From NPOR = 0 V to V <sub>DS</sub> = 90% VBATT                                 |      |          | 150                   | μs  |

Note:

All the digital filtering times reported in Table 11 are to be considered without spread spectrum.

# 7 Power stages

The device is an 8-channel low-side relay switch. The power stages are made by N-channel Power MOSFET transistors.

The source of the power transistors must be directly connected to the GND pin potential. An unwanted OV detection may happen when a different voltage is applied.

# 7.1 Operating modes

The R<sub>DS(ON)</sub> (on-state resistance) depends on the T<sub>J</sub> (junction temperature) and on the supply voltage.

#### 7.1.1 Switching resistive loads

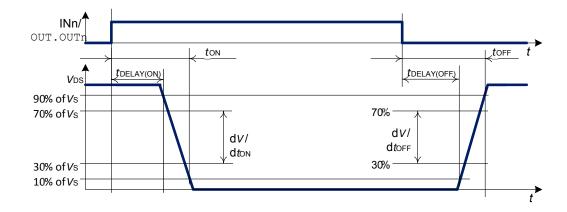

In the case of resistive loads switching, refer to the following switching times and slew rates.

#### Figure 20. Switching resistive load

#### 7.1.2 Inductive output clamp

The inductance still drives the current the voltage across the power switch increases until reaching  $V_{DS(CL)}$  in case of switching off inductive loads. The voltage clamping is necessary to prevent device destruction and protects the device in all operative modes. The maximum allowed load inductance is limited by the max energy. The clamping structure preserves the device in all the operating states: sleep, idle, active, and limp-home (see the Figure 21).

#### Figure 21. Output clamp concept

#### 7.1.3 Maximum load inductance

The maximum energy, which is converted into heat, is limited by the thermal design of the component. The  $E_{AR}$  value provided in Features assumes that all channels can dissipate the same energy when the inductances connected to the outputs are demagnetized at the same time.

### 7.2 Bulb inrush mode

Although the device is optimized for relays and LED, it may be necessary to use one or more of the outputs to drive small lamps (typically 2 W) or electronic loads with a high input capacitor. In such operative conditions at the switch on, an inrush current may appear, reaching the overload current threshold, which latches the channel off.

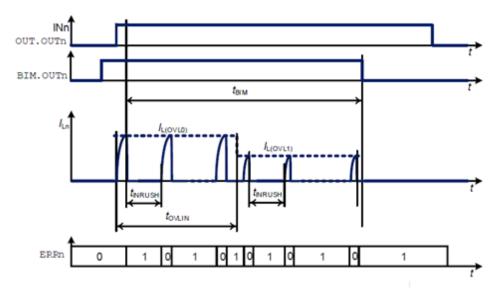

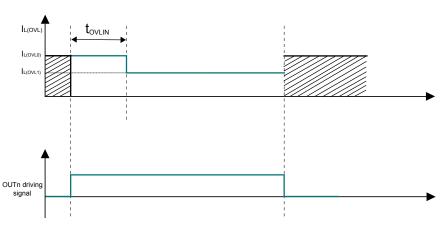

In normal operation the device waits until the microcontroller sends an SPI command to clear the latches (register DIAG\_OVC\_OVT) allowing the channel to turn on again. Usually this delay is too long to transfer enough energy to the load. If the corresponding bit BIM.OUTn is set to "1", in case the channel reaches the overload current threshold and latches off, it restarts automatically after a time t<sub>INRUSH</sub>, allowing the load to go out of the inrush phase. A time diagram is shown in the Figure 22.

The channel configured with the BIM option can be either driven by an SPI command, PWM command (internal generator) or INn parallel input. Once programmed to "1" via SPI, the BIM.OUTn bits are set back to "0" at the end of BIM time( $t_{BIM}$ ), unless a reset condition occurs (VDDIO<sub>(UV)</sub>, hardware, or software reset): an eventual switch off of the channel commanded by the user has no impact on BIM.OUTn configuration.

When BIM.OUTn are set to "1", eventual overcurrent conditions flag DIAG\_OVC\_OVT.OUTn bit, but the affected channels will not be permanently switched OFF (automatic restart after  $T_{INRUSH}$ ). Once asserted, the eventual SPI attempt to clear DIAG\_OVC\_OVT.OUTn is ignored, until the BIM counter is expired. To resume the normal behavior when the BIM counter is expired, the DIAG\_OVC\_OVT.OUTn should be cleared. If OVT condition happens before OVC condition, the flag is set and the channel is turned off but it could be turned on again by clearing register DIAG\_OVC\_OVT.OUTn

An internal timer set the bit BIM.OUTn back to "0" after 40 ms (parameter  $t_{BIM}$ ) starting from the first OVC event latched to prevent an excessive thermal stress to the channel, especially in case of short circuit at the output. Another countermeasure against overheating is that, in case the load current is higher than  $I_{L(OVL0)}$  or  $I_{L(OVL1)}$ , the overloaded channel is immediately switched OFF, without waiting for digital filter time  $t_{OFF(OVL)}$  expiration. The overload threshold is  $I_{L(OVL0)}$  between first channel switch on and  $t_{OVLIN}$  (in BIM mode  $t_{OVLIN}$  is not reset every time the channel is switched off by overcurrent);  $I_{L(OVL1)}$  from  $t_{OVLIN}$  expiration to the end of bulb inrush mode. The device allows a per-channel selection of bulb inrush mode (BIM) in order to be fully flexible without any additional reliability risk.

Figure 22. Bulb mode

### 7.3 PWM generator

The device has two independent PWM generators, which are defined as "PWM GEN" and "PWM LED" below. The two PWM generators can be associated to one or more channels. It is possible to configure it with various frequencies and duty cycle. For both refer to the same base frequency f<sub>INT</sub> (8 MHz typ.) even if two separate pre-scalers can be defined.

#### 7.3.1 Automatic PWM generator

The device has one independent automatic PWM generator that can be assigned to one or more channels and can be programmed with different duty cycle and frequency. The PWM frequency is obtained by dividing the internal clock base frequency  $f_{INT}$  and can be set using CFG\_1.PWM\_DIV\_GEN bits and adjusted through CFG\_2.FR\_ADJ bits as described in the Table 12.

#### Table 12. Coefficient overview

| CFG_2.FR_ADJ    | Absolute delta to f <sub>INT</sub> divider |

|-----------------|--------------------------------------------|

| 00 <sub>B</sub> | 0%                                         |

| 01 <sub>B</sub> | -13%                                       |

| 10 <sub>B</sub> | +18%                                       |

| 11 <sub>B</sub> | 0%                                         |

To configure the PWM generator, the user can set the following parameters:

Duty cycle (bits PWM\_GEN\_DC.DUTY\_CYCLE) 8 bits are available to achieve 0.39% duty cycle resolution. When the microcontroller programs a new duty cycle, the PWM generator waits until the previous cycle is completed before using the new duty cycle (this happens also when the duty cycle is 100%) - the new duty cycle is taken with the next PWM cycle, while the new duty cycle is immediately taken if the previous DC was 0%)

The maximum duty cycle achievable is 100% (PWM\_GEN\_DC.DUTY\_CYCLE set to "11111111B").

2. Frequency (bits CFG\_1.PWM\_DIV\_GEN)

Using 2 bits it is possible to select the divider for  $f_{\text{INT}}$  to achieve the needed duty cycle:

- 00B = PWM frequency is 122.5 Hz

- 01B = PWM frequency is 245.1 Hz

- 10B = PWM frequency is 490.2 Hz

- 11B = PWM frequency is 980.4 Hz

- 3. Mapping registers (PWM\_SEL and PWM\_MAP)

To correctly use the PWM generator:

- Configure the channel output control and mapping register (PWM\_SEL and PWM\_MAP).

- Write the duty cycle control register (PWM\_GEN\_DC) to enable the PWM generation.

#### Figure 23. PWM generator

(\*) In case IN0 and IN1 are mapped to the same channel, IN0 has a higher priority with respect to IN1.

#### 7.3.2 Automatic PWM LED generator

Device has one independent automatic PWM LED generator. This can be assigned to one or more channels, and can be programmed with a different duty cycle and frequency. The PWM frequency is obtained by dividing the internal clock base frequency  $f_{INT}$  and can be set using CFG\_2.PWM\_DIV\_LED bits and adjusted through CFG\_2.FR\_ADJ bits as described in the Table 13.

#### Table 13. Coefficient overview

| CFG_2.FR_ADJ Absolute delta to f <sub>INT</sub> divider |      |

|---------------------------------------------------------|------|

| 00 <sub>B</sub>                                         | 0%   |

| 01 <sub>B</sub>                                         | -13% |

| 10 <sub>B</sub>                                         | +18% |

| 11 <sub>B</sub>                                         | 0%   |

Four parameters can be set:

Duty cycle (bits PWM\_LED\_DC.DUTY\_CYCLE) 8 bits are available to achieve 0.39% duty cycle resolution. When the microcontroller programs a new duty cycle, the PWM LED generator waits until the previous cycle is completed before using the new duty cycle (this happens also when the duty cycle is 100%) - the new duty cycle is taken with the next PWM cycle, while the new duty cycle is immediately taken if the previous DC was 0%).

Maximum duty cycle achievable is 100% (PWM\_LED\_DC.DUTY\_CYCLE set to "1111111B")

- Frequency (bits CFG\_2.PWM\_DIV\_LED)

Using 2 bits it is possible to select the divider for f<sub>INT</sub> to achieve the needed duty cycle:

- 00B = PWM frequency is 122.5 Hz

- 01B = PWM frequency is 245.1 Hz

- 10B = PWM frequency is 490.2 Hz

- 11B = PWM frequency is 980.4 Hz

- 3. Mapping registers (PWM\_SEL and PWM\_MAP)

To correctly use the PWM LED generator:

- Configure the channel output control and mapping register (PWM\_SEL and PWM\_MAP).

- Write the duty cycle control register (PWM\_LED\_DC) to enable the PWM LED generation.

# 7.4 Electrical parameters

3 V < VBATT < 18 V, 3 V < VDDIO < 5.5 V, T  $_{\rm J}$  = -40 °C to 150 °C, unless otherwise noticed.

| Symbol                  | Description                                                                                     | Test condition                                                                                           | Min. | Тур. | Max. | Unit |

|-------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

|                         |                                                                                                 | Power stage                                                                                              |      |      |      |      |

| Proven                  | On-state resistance                                                                             | T <sub>J</sub> = 25 °C                                                                                   |      | 0.77 |      | Ω    |

| R <sub>DS(ON)</sub>     |                                                                                                 | T <sub>J</sub> = 150 °C, I <sub>L</sub> = 100 mA                                                         |      |      | 1.7  | Ω    |

| I <sub>L(NOM)</sub>     | Nominal load current (all channels active)                                                      | $T_J \le 150$ °C, design info                                                                            |      | 260  | 500  | mA   |

| I <sub>L(EAR)</sub>     | Load current for maximum energy dissipation–repetitive (all channels active)                    | $T_J \le 150^{\circ}C$ , design info                                                                     |      | 220  |      | mA   |

| $V_{LS_{DS(CL)}}$       | Drain to source output clamping voltage                                                         | I <sub>L</sub> = 10mA                                                                                    | 45   | 47   | 49   | V    |

|                         |                                                                                                 | V <sub>BATT</sub> = 0 V, V <sub>DDIO</sub> = 0 V,                                                        |      |      |      |      |

| I <sub>L(OFF)_</sub> LS | Output leakage current (each channel) T <sub>J</sub><br>= 150 °C                                | $V_{SOURCE}$ = 0 V, $V_{DS}$ = 28 V (with at least another channel's $V_{DS}$ = 29 V), $T_J$ up to 150°C | -4   | 0    | 4    | μA   |

| E <sub>AR</sub>         | Maximum energy dissipation repetitive pulses - 2*I <sub>L(EAR)</sub> (two channels in parallel) | $T_{J(0)}$ = 85 °C, $I_{L(0)}$ = 2* $I_{L(EAR)}$ , 2*10 <sup>6</sup> cycles                              |      |      | 15   | mJ   |

| E <sub>AS</sub>         | Maximum energy dissipation single pulse                                                         | T = 25 °C, I <sub>L</sub> = 2 * 200 mA                                                                   |      |      | 50   | mJ   |

| ⊢AS                     | Maximum energy dissipation single pulse                                                         | T = 150 °C, I <sub>L</sub> = 400 mA                                                                      |      |      | 25   | mJ   |

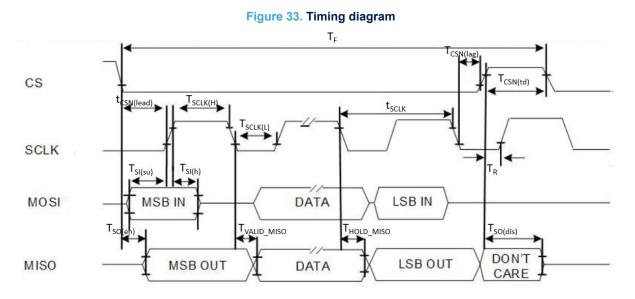

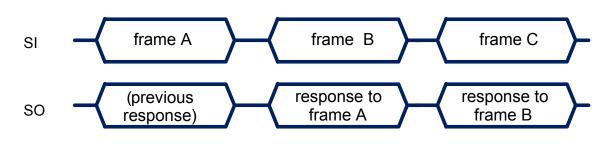

| E <sub>AR</sub>         | Maximum energy dissipation repetitive pulses - $I_{L(\text{EAR})}$                              | T = 85 °C, 2*10 <sup>6</sup> cycles                                                                      |      |      | 10   | mJ   |