Click here to ask an associate for production status of specific part numbers.

### 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### **General Description**

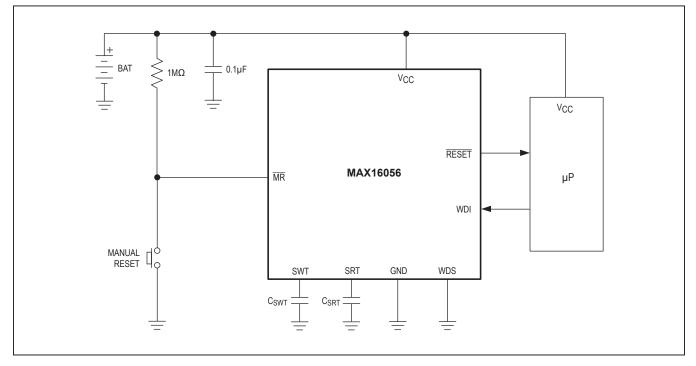

The MAX16056–MAX16059 are ultra-low-current 125nA (typ) microprocessor ( $\mu$ P) supervisory circuits that monitor a single system supply voltage. These devices assert an active-low reset signal whenever the V<sub>CC</sub> supply voltage drops below the factory-trimmed reset threshold, manual reset is pulled low, or the watchdog timer runs out (MAX16056/MAX16058). The reset output remains asserted for an adjustable reset timeout period after V<sub>CC</sub> rises above the reset threshold. Factory-trimmed reset threshold voltages are offered from 1.575V to 4.625V in approximately 100mV increments (see Table 1).

These devices feature adjustable reset and watchdog timeout using external capacitors. The MAX16056/ MAX16058 contain a watchdog timer with a watchdog select input (WDS) that multiplies the watchdog timeout period by 128. The MAX16057/MAX16059 do not have the watchdog feature.

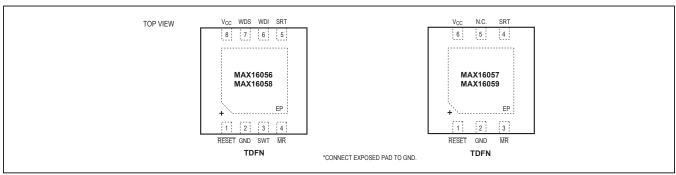

The MAX16056–MAX16059 are available in either pushpull or open-drain output-type configurations (see the *Ordering Information*). These devices are fully specified over the -40°C to +125°C automotive temperature range. The MAX16056/MAX16058 are available in an 8-pin TDFN package, and the MAX16057/MAX16059 are available in a 6-pin TDFN package.

#### **Applications**

- Portable/Battery-Powered Equipment

- PDAs/Cell Phones

- MP3 Players/Pagers

- Glucose Monitors/Patient Monitors

- Metering/HVAC

#### **Pin Configurations**

#### **Benefits and Features**

- Reduced Power Requirements

- Ultra-Low 125nA (typ) Supply Current

- 1.1V to 5.5V Operating Supply Range

- Configurable Circuit Enables Flexible Designs

- Factory-Set Reset Threshold Options from 1.575V to 4.625V in Approximately 100mV Increments

MAX16056–MAX16059

- Capacitor-Adjustable Reset Timeout

- Capacitor-Adjustable Watchdog Timeout (MAX16056/MAX16058)

- Watchdog Timer Capacitor Open Detect Function

- Optional Watchdog Disable Function (MAX16056/ MAX16058)

- Manual-Reset Input

- Push-Pull or Open-Drain RESET Output Options

- Integrated Features Increases System Robustness

- · Power-Supply Transient Immunity

- Guaranteed RESET Valid for VCC ≥ 1.1V

- Saves Board Space

- 3mm x 3mm TDFN Package

- Enables Functional Safety at System Level

<u>Typical Operating Circuit</u> and <u>Ordering Information</u> appear at end of data sheet.

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND0.3V to +6V                              |

|----------------------------------------------------------------|

| SRT, SWT, WDS, MR, WDI, to GND0.3V to (V <sub>CC</sub> + 0.3V) |

| RESET (Push-Pull) to GND0.3V to (V <sub>CC</sub> + 0.3V)       |

| RESET (Open-Drain) to GND0.3V to +6V                           |

| Input Current (all pins)±20mA                                  |

| Output Current (RESET)±20mA                                    |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)          |

| 6-Pin TDFN (derate 23.8mW/°C above +70°C)1905mW                |

| 8-Pin TDFN (derate 24.4mW/°C above +70°C)1951mW                |

| Operating Temperature Range       | -40°C to +125°C |

|-----------------------------------|-----------------|

| Storage Temperature Range         | -65°C to +150°C |

| Junction Temperature              | +150°C          |

| Lead Temperature (soldering, 10s) | +300°C          |

| Soldering Temperature (reflow)    | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Package Thermal Characteristics (Note 1)

6 TDFN

8 TDFN

- **Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="http://www.analog.com/thermal-tutorial">www.analog.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(V<sub>CC</sub> = 1.2V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                       | SYMBOL            | CONDITI                                                                                    | ONS                                                         | MIN                       | TYP | MAX                       | UNITS |

|---------------------------------|-------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------|-----|---------------------------|-------|

| Cumply Voltore                  |                   | $T_A = 0^{\circ}C$ to +125°C                                                               |                                                             | 1.1                       |     | 5.5                       | v     |

| Supply Voltage                  | V <sub>CC</sub>   | $T_A = -40^{\circ}C$ to $0^{\circ}C$                                                       |                                                             | 1.2                       |     | 5.5                       |       |

|                                 |                   |                                                                                            | V <sub>CC</sub> = 5.0V, T <sub>A</sub> =<br>-40°C to +85°C  |                           | 142 | 210                       |       |

|                                 |                   |                                                                                            | V <sub>CC</sub> = 3.3V, T <sub>A</sub> =<br>-40°C to +85°C  |                           | 132 | 185                       |       |

| Supply Current                  |                   | V <sub>CC</sub> > V <sub>TH</sub> + 150mV,<br>no load, reset output<br>deasserted (Note 3) | V <sub>CC</sub> = 1.8V, T <sub>A</sub> =<br>-40°C to +85°C  |                           | 125 | 175                       | nA    |

|                                 | ICC               |                                                                                            | V <sub>CC</sub> = 5.0V, T <sub>A</sub> =<br>-40°C to +125°C |                           | 142 | 430                       |       |

|                                 |                   |                                                                                            | V <sub>CC</sub> = 3.3V, T <sub>A</sub> =<br>-40°C to +125°C |                           | 132 | 415                       |       |

|                                 |                   |                                                                                            | V <sub>CC</sub> = 1.8V, T <sub>A</sub> =<br>-40°C to +125°C |                           | 125 | 400                       |       |

|                                 |                   | V <sub>CC</sub> < V <sub>TH</sub> , no load, rese                                          | et output asserted                                          |                           | 7   | 15                        | μA    |

| V <sub>CC</sub> Reset Threshold |                   |                                                                                            | T <sub>A</sub> = +25°C                                      | V <sub>TH</sub> -<br>1.5% |     | V <sub>TH</sub> +<br>1.5% | V     |

|                                 | V <sub>TH</sub>   | V <sub>CC</sub> falling (see Table 1)                                                      | T <sub>A</sub> = -40°C to<br>+125°C                         | V <sub>TH</sub> -<br>2.5% |     | V <sub>TH</sub> +<br>2.5% |       |

| Hysteresis                      | V <sub>HYST</sub> | V <sub>CC</sub> rising                                                                     |                                                             |                           | 0.5 |                           | %     |

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### **Electrical Characteristics (continued)**

(V<sub>CC</sub> = 1.2V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                   | SYMBOL             | CONDITI                                                                                           | ONS                                                     | MIN                      | TYP   | MAX                      | UNITS |

|---------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------|-------|--------------------------|-------|

| V <sub>CC</sub> to Reset Delay              | t <sub>RD</sub>    | V <sub>CC</sub> falling from (V <sub>TH</sub> + 100mV) to<br>(V <sub>TH</sub> - 100mV) at 10mV/μs |                                                         |                          | 80    |                          | μs    |

| Reset Timeout Period                        | t <sub>RP</sub>    | C <sub>SRT</sub> = 2700pF (Note 4)                                                                |                                                         | 10.5                     | 14.18 | 17.0                     | ms    |

| SRT Ramp Curren <b>t</b>                    |                    | V <sub>SRT</sub> = 0V to V <sub>RAMP1</sub> ,                                                     | T <sub>A</sub> = -40°C to<br>+125°C                     | 197                      | 240   | 282                      | μĄ    |

|                                             | IRAMP1             | V <sub>CC</sub> = 1.6V to 5V                                                                      | T <sub>A</sub> = +25°C                                  | 210                      | 240   | 270                      | nA    |

| SRT Ramp Threshold                          | V <sub>RAMP1</sub> | $V_{CC}$ = 1.6V to 5V ( $V_{RAN}$                                                                 | <sub>IP</sub> rising)                                   | 1.173                    | 1.235 | 1.297                    | V     |

| Watahdag Timagut Clask Dariad               | <b>t</b>           | T <sub>A</sub> = +25°C                                                                            |                                                         | 5                        | 6.4   | 8                        | ma    |

| Watchdog Timeout Clock Period               | <sup>t</sup> WDPER | T <sub>A</sub> = -40°C to +125°C                                                                  |                                                         | 3.5                      | 6.4   | 9.5                      | ms    |

| SWT Ramp Current                            |                    | $V_{SWT} = 0V$ to $V_{RAMP2}$ ,                                                                   | T <sub>A</sub> = -40°C to<br>+125°C                     | 197                      | 240   | 282                      | nΔ    |

|                                             | IRAMP2             | V <sub>CC</sub> = 1.6V to 5V                                                                      | T <sub>A</sub> = +25°C                                  | 210                      | 240   | 270                      | - nA  |

| SWT Ramp Threshold                          | V <sub>RAMP2</sub> | $V_{CC}$ = 1.6V to 5V ( $V_{RAN}$                                                                 | <sub>IP2</sub> rising)                                  | 1.173                    | 1.235 | 1.297                    | V     |

|                                             |                    | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub> = 50µA                                                  |                                                         |                          |       | 0.3                      |       |

|                                             | V <sub>OL</sub>    | $V_{CC} \ge 2.7V$ , $I_{SINK} = 1.2mA$                                                            |                                                         |                          |       | 0.3                      |       |

|                                             |                    | $V_{CC} \ge 4.5V$ , $I_{SINK} = 3.2mA$                                                            |                                                         |                          |       | 0.4                      |       |

| RESET Output Voltage                        | V <sub>OH</sub>    | MAX16056/MAX16057                                                                                 | V <sub>CC</sub> ≥ 1.8V,<br>I <sub>SOURCE</sub> = 200µA  | 0.8 x<br>V <sub>CC</sub> |       |                          | V     |

|                                             |                    |                                                                                                   | V <sub>CC</sub> ≥ 2.25V,<br>I <sub>SOURCE</sub> = 500µA | 0.8 x<br>V <sub>CC</sub> |       |                          | _     |

|                                             |                    |                                                                                                   | V <sub>CC</sub> ≥ 4.5V,<br>I <sub>SOURCE</sub> = 800µA  | 0.8 x<br>V <sub>CC</sub> |       |                          |       |

| RESET Output-Leakage Current,<br>Open Drain | I <sub>LKG</sub>   | V <sub>CC</sub> > V <sub>TH</sub> , reset not as<br>5.5V (MAX16058/MAX16                          |                                                         |                          |       | 1.0                      | μA    |

|                                             | VIH                |                                                                                                   |                                                         | 0.7 x<br>V <sub>CC</sub> |       |                          |       |

| Input-Logic Levels                          | VIL                |                                                                                                   |                                                         |                          |       | 0.3 x<br>V <sub>CC</sub> | V     |

| MR Minimum Pulse Width                      | t <sub>MPW</sub>   |                                                                                                   |                                                         | 1                        |       |                          | μs    |

| MR Glitch Rejection                         |                    |                                                                                                   |                                                         |                          | 200   |                          | ns    |

| MR-to-RESET Delay                           | t <sub>MRD</sub>   |                                                                                                   |                                                         |                          | 250   |                          | ns    |

| WDI Minimum Pulse Width                     |                    | (Note 5)                                                                                          |                                                         | 150                      |       |                          | ns    |

| Input Leakage Current                       |                    | MR, WDI, WDS is conne                                                                             | cted to GND or V <sub>CC</sub>                          | -100                     |       | +100                     | nA    |

Note 2: Devices are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature limits are guaranteed by design.

**Note 3:** WDI input period is 1s with  $t_{RISE}$  and  $t_{FALL} < 50$ ns.

Note 4: Worst case of SRT ramp current and voltage is used to guarantee minimum and maximum limits.

Note 5: Guaranteed by design, not production tested.

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

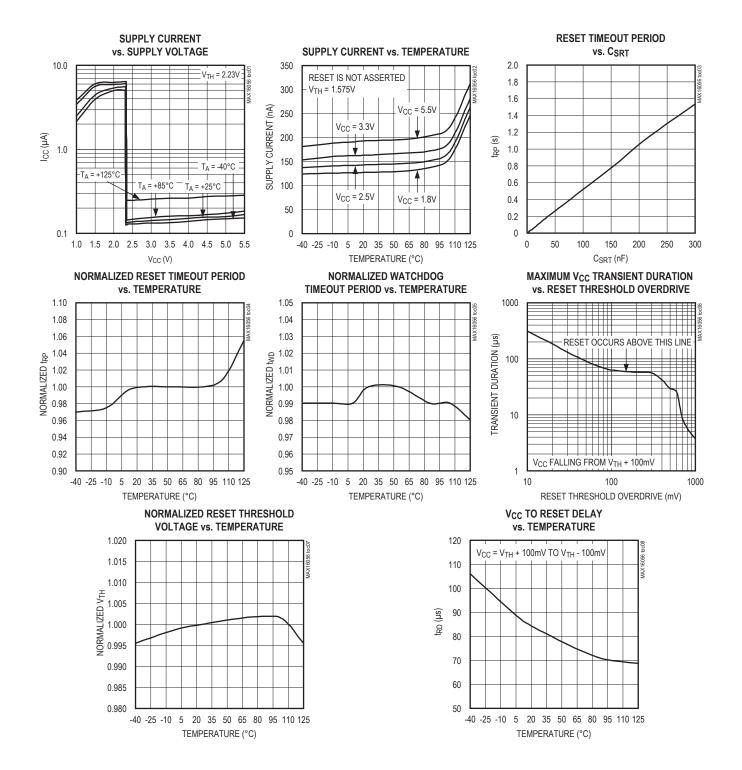

#### **Typical Operating Characteristics**

(V<sub>CC</sub> = 2.5V,  $T_A$  = +25°C, unless otherwise noted.)

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

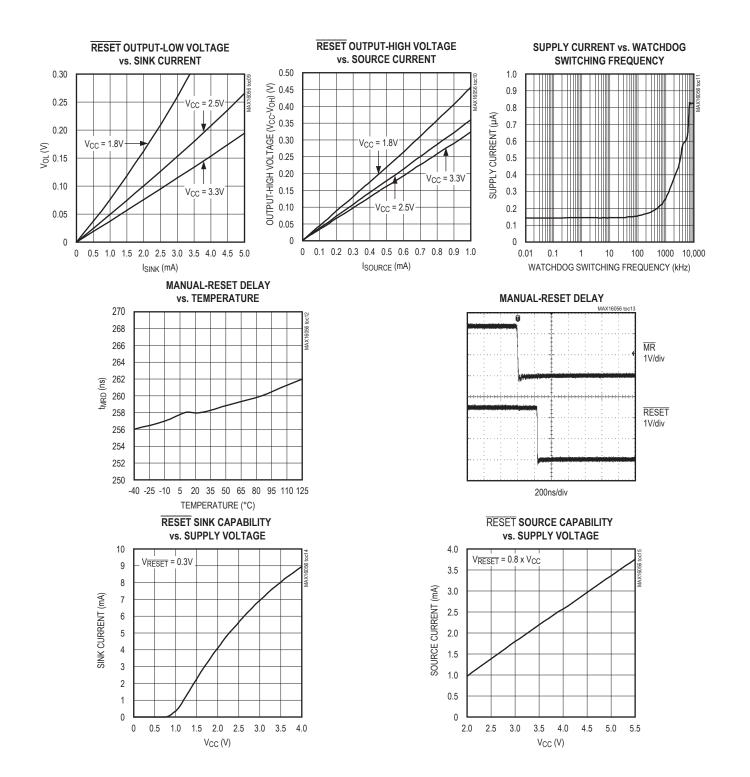

#### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 2.5V,  $T_A$  = +25°C, unless otherwise noted.)

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

# **Pin Description**

| Р                     | IN                    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16056/<br>MAX16058 | MAX16057/<br>MAX16059 | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                     | 1                     | RESET | Push-Pull or Open-Drain Reset Output. RESET asserts whenever V <sub>CC</sub> drops below the selected reset threshold voltage (V <sub>TH</sub> ) or manual reset is pulled low. RESET remains low for the reset timeout period after all reset conditions are deasserted, and then goes high. The watchdog timer triggers a reset pulse (t <sub>RP</sub> ) whenever a watchdog fault occurs (MAX16056/MAX16058).                                                                                                                                                                                         |

| 2                     | 2                     | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3                     | _                     | SWT   | Watchdog Timeout Input. Connect a capacitor between SWT and GND to set the basic watchdog timeout period (t <sub>WD</sub> ). Determine the period by the formula t <sub>WD</sub> = Floor[C <sub>SWT</sub> x $5.15 \times 10^{6}/6.4$ ms] x $6.4$ ms + $3.2$ ms (Note 6) with t <sub>WD</sub> in seconds and C <sub>SWT</sub> in Farads, or use Table 2. Extend the basic watchdog timeout period by using the WDS input. Connect SWT to ground to disable the watchdog timer function. The recommended value of the capacitor is between 2275pF and $0.54\mu$ F to have a valid watchdog timeout period. |

| 4                     | 3                     | MR    | Manual-Reset Input. Drive $\overline{\text{MR}}$ low to manually reset the device. $\overline{\text{RESET}}$ remains asserted for the reset timeout period after $\overline{\text{MR}}$ is released. There is no internal pullup on $\overline{\text{MR}}$ . $\overline{\text{MR}}$ must not be left unconnected. Connect $\overline{\text{MR}}$ to V <sub>CC</sub> if not used.                                                                                                                                                                                                                         |

| 5                     | 4                     | SRT   | Reset Timeout Input. Connect a capacitor from SRT to GND to select the reset timeout period. Determine the period as follows: $t_{RP} = 5.15 \times 10^6 \times C_{SRT}$ with $t_{RP}$ in seconds and $C_{SRT}$ in Farads, or use Table 2. The recommended value of the capacitor is between 39pF and 4.7µF.                                                                                                                                                                                                                                                                                             |

| 6                     | _                     | WDI   | Watchdog Input. A falling transition must occur on WDI within the selected watchdog timeout period or a reset pulse occurs. The watchdog timer clears when a falling transition occurs on WDI or whenever RESET is asserted. Connect SWT to ground to disable the watchdog timer function.                                                                                                                                                                                                                                                                                                               |

| 7                     |                       | WDS   | Watchdog Select Input. WDS selects the watchdog timeout mode. Connect WDS to ground to select normal mode. The watchdog timeout period is $t_{WD}$ . Connect WDS to $V_{CC}$ to select extended mode, Extended watchdog timeout period is calculated by the equation, extended $t_{WD}$ = Floor [C <sub>SWT</sub> x 5.15 x 10 <sup>-6</sup> /6.4ms] x 128 x 6.4ms + 3.2ms. A change in the state of WDS clears the watchdog timer.                                                                                                                                                                       |

| 8                     | 6                     | Vcc   | Supply Voltage. V <sub>CC</sub> is the power-supply input and the input for fixed-threshold V <sub>CC</sub> monitor. For noisy systems, bypass V <sub>CC</sub> with a 0.1 $\mu$ F capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                      |

| _                     | 5                     | N.C.  | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _                     |                       | EP    | Exposed Pad. Connect EP to GND or leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Note 6: Floor: take the preceding Integer value.

#### **Detailed Description**

The MAX16056–MAX16059 are ultra-low-current 125nA (typ)  $\mu$ P supervisory circuits that monitor a single system supply voltage. These devices assert an active-low reset signal whenever the V<sub>CC</sub> supply voltage drops below the factory-trimmed reset threshold, manual reset is pulled low, or the watchdog timer runs out (MAX16056/MAX16058). The reset output remains asserted for an adjustable reset timeout period after V<sub>CC</sub> rises above the reset threshold. The reset and watchdog delay periods are adjustable using external capacitors.

#### **RESET** Output

The MAX16056–MAX16059  $\mu P$  supervisory circuits assert a reset to prevent code-execution errors during power-up, power-down, and brownout conditions. The reset output is guaranteed to be valid for V<sub>CC</sub> down to 1.1V.

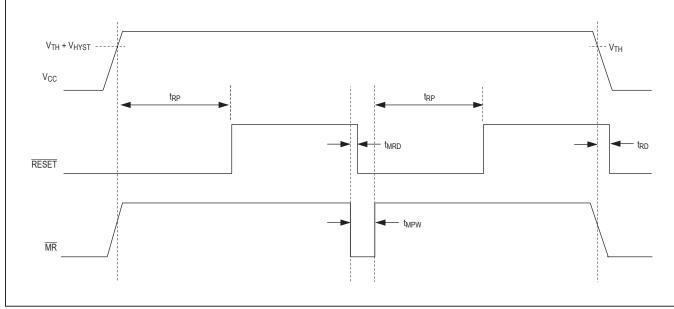

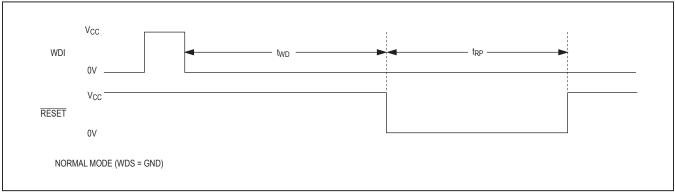

When  $V_{CC}$  falls below the reset threshold, the RESET output asserts low. Once  $V_{CC}$  exceeds the reset threshold plus the hysteresis, an internal timer keeps the RESET output asserted for the capacitor-adjusted reset timeout period (t<sub>RP</sub>), then after this interval the RESET output deasserts (Figure 1). The reset function features immunity to power-supply voltage transients.

#### Manual-Reset Input (MR)

Many  $\mu$ P-based products require manual-reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. The MAX16056–MAX16059 feature an MR input. A logic-low on MR asserts a reset. RESET remains asserted while MR is low and for the timeout period (t<sub>RP</sub>)after MR returns high. Connect MR to V<sub>CC</sub> if unused. MR can be driven with CMOS logic levels or with open-drain/collector outputs (with a pullup resistor). Connect a normally open momentary switch from MR to GND and a resistor from MR to V<sub>CC</sub> to implement a manual-reset function; external debounce circuitry is not required. If MR is driven by long cables or the device is used in a noisy environment, connect a 0.1µF capacitor from MR to GND to provide additional noise immunity.

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### Watchdog Timer

The MAX16056/MAX16058's watchdog timer circuitry monitors the  $\mu$ P's activity. If the  $\mu$ P does not toggle (high to low) the watchdog input (WDI) within the capacitor-adjustable watchdog timeout period (t<sub>WD</sub>), RESET asserts for the reset timeout period (t<sub>RP</sub>). The internal watchdog timer is cleared by: 1) any event that asserts RESET, 2) a falling transition at WDI (that can detect pulses as short as 150ns), or 3) a transition (high to low or low to high) at WDS. While RESET is asserted, the watchdog timer remains cleared and does not count. As soon as RESET deasserts, the watchdog timer resumes counting.

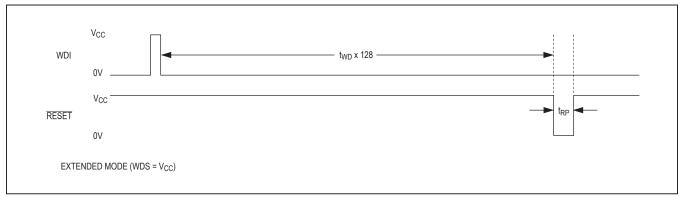

There are two modes of watchdog operation, normal mode and extended mode. In normal mode (Figure 2), the watchdog timeout period is determined by the value of the capacitor connected between SWT and ground. In extended mode (Figure 3), the watchdog timeout period is multiplied by 128. For example, in extended mode, a  $0.33\mu$ F capacitor gives a watchdog timeout period of 217s (Table 2). To disable the watchdog timer function, connect SWT to ground.

When V<sub>CC</sub> ramps above V<sub>TH</sub> + V<sub>HYST</sub>, the value of the external SWT capacitor is sampled after  $\overline{\text{RESET}}$  goes high. When sampling is finished, the capacitor value is stored in the device and is used to set watchdog timeout. If  $\overline{\text{RESET}}$  goes low before sampling is finished, the device interrupts sampling, and sampling is restarted when  $\overline{\text{RESET}}$  goes high again.

If the external SWT capacitor is less than 470pF, the sampling result sets the watchdog timeout to zero. This causes the watchdog to assert  $\overline{\text{RESET}}$  continuously after sampling is finished. If a PCB manufacturing defect caused the connection to  $C_{SWT}$  to be broken, the capacitance is very low and  $\overline{\text{RESET}}$  is continuously asserted. If the external SWT capacitor is greater than  $0.47\mu\text{F}$ , the sampling result sets the watchdog timeout to be infinite, disabling the watchdog function.

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

Figure 1. RESET Timing Relationship

Figure 2. Watchdog Timing Diagram, Normal Mode (WDS = GND)

Figure 3. Watchdog Timing Diagram, Extended Mode (WDS = V<sub>CC</sub>)

#### **Applications Information**

#### **Selecting the Reset Timeout Capacitor**

The reset timeout period is adjustable to accommodate a variety of  $\mu$ P applications. To adjust the reset timeout period (t<sub>RP</sub>), connect a capacitor (C<sub>SRT</sub>) between SRT and ground. The reset timeout capacitor is calculated as follows:

$C_{SRT} = t_{RP}/(5.15 \times 10^6)$

with  $t_{RP}$  in seconds and  $C_{SRT}$  in Farads.

C<sub>SRT</sub> must be a low-leakage (< 10nA) type capacitor. A ceramic capacitor with low temperature coefficient dielectric (i.e., X7R) is recommended.

#### **Selecting Watchdog Timeout Capacitor**

The watchdog timeout period is adjustable to accommodate a variety of  $\mu$ P applications. With this feature, the watchdog timeout can be optimized for software execution. The programmer can determine how often the watchdog time should be serviced. Adjust the watchdog timeout period (t<sub>WD</sub>) by connecting a capacitor (C<sub>SWT</sub>) between SWT and GND. For normal mode operation, calculate the watchdog timeout as follows:

$t_{WD}$  = Floor [C<sub>SWT</sub> x 5.15 x 10<sup>6</sup>/6.4ms] x 6.4ms + 3.2ms For extended mode of operation,

Extended  $t_{WD}$  = Floor [C<sub>SWT</sub> x 5.15 x 10<sup>6</sup>/6.4ms] x 128 x 6.4ms + 3.2ms

with  $t_{WD}$  in seconds and  $C_{SWT}$  in Farads.

(Floor: take the preceding Integer value) (Figures 2 and 3)

The maximum  $t_{WD}$  is 296s. If the capacitor sets  $t_{WD}$  greater than the 296s,  $t_{WD}$  = infinite and the watchdog timer is disabled.

C<sub>SWT</sub> must be a low-leakage (< 10nA) type capacitor. A ceramic capacitor with low temperature coefficient dielectric (i.e., X7R) is recommended.

#### Watchdog Timeout Accuracy

The watchdog timeout period is affected by the SWT ramp current ( $I_{RAMP2}$ ) accuracy, the SWT ramp threshold ( $V_{RAMP2}$ ), and the watchdog timeout clock period ( $t_{WDPER}$ ). In the equation above, the constant 5.15 x 10<sup>6</sup> is equal to  $V_{RAMP2}/I_{RAMP2}$ , and 6.4ms equals the watchdog timeout clock period. Calculate the timeout accuracy by substituting the minimum, typical, and maximum values into the equation.

twDMIN = Floor [C<sub>SWT</sub> x (V<sub>RAMP2\_Min</sub>/I<sub>RAMP2\_Max</sub>)/ twDPER\_Min] x twDPER\_Min + [twDPER\_Min/2]

### 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

- t<sub>WDNOM</sub> = Floor [C<sub>SWT</sub> x (V<sub>RAMP2\_Nom</sub>/I<sub>RAMP2\_Nom</sub>)/ t<sub>WDPER\_Nom</sub>] x t<sub>WDPER\_Nom</sub> + [t<sub>WDPER\_Nom</sub>/2]

- t<sub>WDMAX</sub> = Floor [C<sub>SWT</sub> x (V<sub>RAMP2\_Max</sub>/I<sub>RAMP2\_Min</sub>)/ tWDPER\_Max] x tWDPER\_Max + [tWDPER\_Max/2]

t<sub>WDEXT</sub> = Floor [C<sub>SWT</sub> x (V<sub>RAMP2\_Nom</sub>/I<sub>RAMP2\_Nom</sub>)/ t<sub>WDPER\_Nom</sub>] x 128 x t<sub>WDPER\_Nom</sub> + [t<sub>WDPER\_Nom</sub>/2] For example, if C<sub>SWT</sub> = 100nF:

t<sub>WDMIN</sub> = Floor [100 x 10<sup>-9</sup> x 1.173/(282 x 10<sup>-9</sup>)/3.5ms] x 3.5ms + 0.5 x 3.5ms = 414.75ms

$t_{WDNOM}$  = Floor [100 x 10<sup>-9</sup> x 1.235/(240 x 10<sup>-9</sup>)/6.4ms] x 6.4ms + 0.5 x 6.4ms = 515.2ms

t<sub>WDMAX</sub> = Floor [100 x 10<sup>-9</sup> x 1.297/(197 x 10<sup>-9</sup>)/9.5ms] x 9.5ms + 0.5 x 9.5ms = 660.25ms

t<sub>WDEXT</sub> = Floor [100 x 10<sup>-9</sup> x 1.235/(240 x 10<sup>-9</sup>)/6.4ms] x 128 x 6.4ms + 0.5 x 6.4ms = 65.539s

#### **Transient Immunity**

For applications with higher slew rates on  $V_{CC}$  during power-up, additional bypass capacitance may be required.

The MAX16056–MAX16059 are relatively immune to short-duration supply voltage transients, or glitches on V<sub>CC</sub>. The Maximum V<sub>CC</sub> Transient Duration vs. Reset Threshold Overdrive graph in the *Typical Operating Characteristics* shows this transient immunity. The area below the curve of the graph is the region where these devices typically do not generate a reset pulse. This graph was generated using a falling pulse applied to V<sub>CC</sub>, starting 100mV above the actual reset threshold (V<sub>TH</sub>), and ending below this threshold (reset threshold overdrive). As the magnitude of the transient increases, the maximum allowable pulse width decreases. Typically, a 100mV V<sub>CC</sub> transient duration of 40µs or less does not cause a reset.

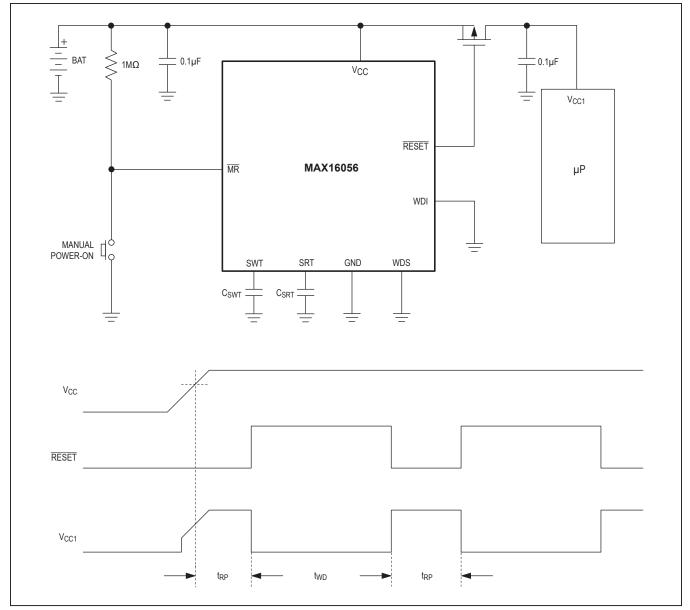

#### Using the MAX16056–MAX16059 for Reducing System Power Consumption

Using the RESET output to control an external p-channel MOSFET to control the on-time of a power supply can result in lower system power consumption in systems that can be regularly put to sleep. By tying the WDI input to ground, the RESET output becomes a low-frequency clock output. When RESET is low, the MOSFET is turned on and power is applied to the system. When RESET is high, the MOSFET is turned off and no power is consumed by the system. This effectively reduces the shutdown current of the system to zero (Figure 4).

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

Figure 4. Using MAX16056–MAX16059 to Reduce System Power Consumption

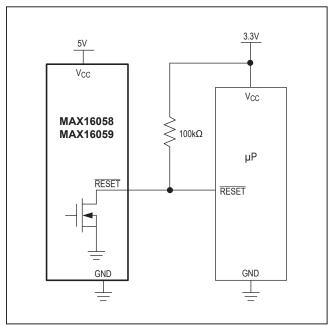

# Interfacing to Other Voltages for Logic Compatibility

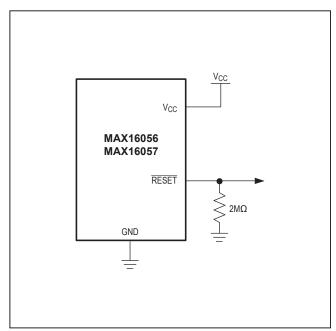

The open-drain  $\overline{\text{RESET}}$  output can be used to interface to a  $\mu P$  with other logic levels. The open-drain output is connected to a voltage from 0 to 5.5V, as shown in Figure 5. Generally, the pullup resistor connected to  $\overline{\text{RESET}}$  connects to the supply voltage that is being monitored at the device's  $V_{CC}$  input. However, some systems use the open-drain output to level-shift from the supervisor's monitored supply to another supply voltage. As the supervisor's  $V_{CC}$  decreases, so does the device's ability to sink current at  $\overline{\text{RESET}}$ .

Figure 5. Interfacing with Other Voltage Levels

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### Ensuring a Valid RESET Down to V<sub>CC</sub> = 0V (Push-Pull RESET)

When  $V_{CC}$  falls below 1.1V, the current-sinking capability of RESET decreases drastically. The high-impedance CMOS logic inputs connected to RESET can drift to undetermined voltages. This presents no problems in most applications, since most µPs and other circuitry do not operate with V<sub>CC</sub> below 1.1V. In those applications where RESET must be valid down to 0V, add a pulldown resistor between the MAX16056/MAX16057 push-pull RESET output and GND. The resistor sinks any stray leakage currents, holding RESET low (Figure 6). Choose a pulldown resistor that accommodates leakages, such that RESET is not significantly loaded and is capable of pulling to GND. The external pulldown cannot be used with the open-drain RESET output of the MAX16058/MAX16059.

Figure 6. Ensuring  $\overline{\text{RESET}}$  Valid to  $V_{CC}$  = GND

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### Table 1. Threshold Suffix Guide

| SUFFIX |       | V <sub>CC</sub> THRESHOLD FALLING (V) |       |

|--------|-------|---------------------------------------|-------|

|        | MIN   | ТҮР                                   | MAX   |

| 46     | 4.509 | 4.625                                 | 4.741 |

| 45     | 4.388 | 4.500                                 | 4.613 |

| 44     | 4.266 | 4.375                                 | 4.484 |

| 43     | 4.193 | 4.300                                 | 4.408 |

| 42     | 4.095 | 4.200                                 | 4.305 |

| 41     | 3.998 | 4.100                                 | 4.203 |

| 40     | 3.900 | 4.000                                 | 4.100 |

| 39     | 3.802 | 3.900                                 | 3.998 |

| 38     | 3.705 | 3.800                                 | 3.895 |

| 37     | 3.608 | 3.700                                 | 3.793 |

| 36     | 3.510 | 3.600                                 | 3.690 |

| 35     | 3.413 | 3.500                                 | 3.588 |

| 34     | 3.315 | 3.400                                 | 3.485 |

| 33     | 3.218 | 3.300                                 | 3.383 |

| 32     | 3.120 | 3.200                                 | 3.280 |

| 31     | 2.998 | 3.075                                 | 3.152 |

| 30     | 2.925 | 3.000                                 | 3.075 |

| 29     | 2.852 | 2.925                                 | 2.998 |

| 28     | 2.730 | 2.800                                 | 2.870 |

| 27     | 2.633 | 2.700                                 | 2.768 |

| 26     | 2.559 | 2.625                                 | 2.691 |

| 25     | 2.438 | 2.500                                 | 2.563 |

| 24     | 2.340 | 2.400                                 | 2.460 |

| 23     | 2.255 | 2.313                                 | 2.371 |

| 225    | 2.180 | 2.235                                 | 2.290 |

| 22     | 2.133 | 2.188                                 | 2.243 |

| 21     | 2.048 | 2.100                                 | 2.153 |

| 20     | 1.950 | 2.000                                 | 2.050 |

| 19     | 1.853 | 1.900                                 | 1.948 |

| 18     | 1.755 | 1.800                                 | 1.845 |

| 17     | 1.623 | 1.665                                 | 1.707 |

| 16     | 1.536 | 1.575                                 | 1.614 |

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

### Table 2. Capacitor Selection Guide

| CAPACITANCE (pF) | t <sub>RP</sub> (ms) | t <sub>WD</sub> (ms) | t <sub>WD</sub> x 128 (ms) |  |

|------------------|----------------------|----------------------|----------------------------|--|

| 39               |                      |                      | ·                          |  |

| 47               |                      |                      |                            |  |

| 56               |                      |                      |                            |  |

| 68               |                      |                      |                            |  |

| 82               |                      |                      |                            |  |

| 100              |                      |                      |                            |  |

| 120              |                      |                      | 0                          |  |

| 150              |                      | (no capacitor        | is connected)              |  |

| 180              |                      |                      |                            |  |

| 220              |                      |                      |                            |  |

| 270              |                      |                      |                            |  |

| 330              | Not recommended      |                      |                            |  |

| 390              |                      |                      |                            |  |

| 470              |                      |                      |                            |  |

| 560              |                      |                      |                            |  |

| 680              |                      |                      |                            |  |

| 820              |                      |                      |                            |  |

| 1000             |                      | Indeterminate        | Indeterminate              |  |

| 1200             |                      | (0, 9.6, or 16)      | (0, 1228.8, or 1636)       |  |

| 1500             |                      |                      |                            |  |

| 1800             |                      |                      |                            |  |

| 2200             |                      |                      |                            |  |

| 2700             | 14.18                | 16                   | 1641                       |  |

| 3300             | 16.99                | 16                   | 1641                       |  |

| 3900             | 20.1                 | 22.4                 | 2460                       |  |

| 4700             | 24.21                | 22.4                 | 2460                       |  |

| 5600             | 28.84                | 28.8                 | 3280                       |  |

| 6800             | 35.00                | 35.2                 | 4099                       |  |

| 8200             | 42.23                | 41.6                 | 4918                       |  |

| 10,000           | 51.5                 | 54.4                 | 6556                       |  |

| 12,000           | 61.8                 | 60.8                 | 7376                       |  |

| 15,000           | 77.25                | 80                   | 9833                       |  |

| 18,000           | 92.7                 | 92.8                 | 11,472                     |  |

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### Table 2. Capacitor Selection Guide (continued)

| CAPACITANCE (pF) | t <sub>RP</sub> (ms) | t <sub>WD</sub> (ms)                                        | t <sub>WD</sub> x 128 (ms) |

|------------------|----------------------|-------------------------------------------------------------|----------------------------|

| 22,000           | 113.3                | 112                                                         | 13,929                     |

| 27,000           | 139.05               | 137.6                                                       | 17,206                     |

| 33,000           | 169.95               | 169.6                                                       | 21,302                     |

| 39,000           | 200.85               | 201.6                                                       | 25,398                     |

| 47,000           | 242.05               | 240                                                         | 30,313                     |

| 56,000           | 288.4                | 291.2                                                       | 36,867                     |

| 68,000           | 350.2                | 348.8                                                       | 44,240                     |

| 82,000           | 422.3                | 419.2                                                       | 53,251                     |

| 100,000          | 515                  | 515.2                                                       | 65,539                     |

| 120,000          | 618                  | 617.6                                                       | 78,646                     |

| 150,000          | 772.5                | 771.2                                                       | 98,307                     |

| 180,000          | 927                  | 924.8                                                       | 117,968                    |

| 220,000          | 1133                 | 1129.6                                                      | 144,182                    |

| 270,000          | 1390.5               | 1392                                                        | 177,769                    |

| 330,000          | 1699.5               | 1699.2                                                      | 217,091                    |

| 390,000          | 2008.5               | 2006.4                                                      | 256,412                    |

| 470,000          | 2420.5               | 2416                                                        | 308,841                    |

| 680,000          | 3502                 |                                                             |                            |

| 820,000          | 4223                 |                                                             |                            |

| 1,000,000        | 5150                 | Indeterminate<br>(may be infinite and watchdog is disabled) |                            |

| 1,500,000        | 7725                 |                                                             |                            |

| 2,200,000        | 11,330               |                                                             |                            |

| 3,300,000        | 16,995               | Ir                                                          | nfinite                    |

| 4,700,000        | 24,205               | (watchdo                                                    | g is disabled)             |

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### **Table 3. Standard Versions**

| PART           | TOP MARK |

|----------------|----------|

| MAX16056ATA17+ | ВКΖ      |

| MAX16056ATA23+ | BLA      |

| MAX16056ATA26+ | BLB      |

| MAX16056ATA29+ | BLC      |

| MAX16056ATA31+ | BLD      |

| MAX16056ATA46+ | BLE      |

| MAX16057ATT17+ | ATQ      |

| MAX16057ATT23+ | ATR      |

| MAX16057ATT26+ | ATS      |

| MAX16057ATT29+ | ATT      |

| MAX16057ATT31+ | ATU      |

| MAX16057ATT46+ | ATV      |

| MAX16058ATA16+ | BLF      |

| MAX16058ATA22+ | BLG      |

| MAX16058ATA26+ | BLH      |

| MAX16058ATA29+ | BLI      |

| MAX16058ATA31+ | BLJ      |

| MAX16058ATA44+ | BLK      |

| MAX16059ATT16+ | ATW      |

| MAX16059ATT22+ | ATX      |

| MAX16059ATT26+ | ATY      |

| MAX16059ATT29+ | ATZ      |

| MAX16059ATT31+ | AUA      |

| MAX16059ATT44+ | AUB      |

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

### **Typical Operating Circuit**

#### **Chip Information**

PROCESS: BICMOS

#### **Ordering Information**

| PART          | PIN-       | RESET      | WATCH-    |

|---------------|------------|------------|-----------|

| FARI          | PACKAGE    | OUTPUT     | DOG TIMER |

| MAX16056ATA+T | 8 TDFN-EP* | Push-Pull  | Yes       |

| MAX16057ATT+T | 6 TDFN-EP* | Push-Pull  | No        |

| MAX16058ATA+T | 8 TDFN-EP* | Open-Drain | Yes       |

| MAX16059ATT+T | 6 TDFN-EP* | Open-Drain | No        |

**Note:** All devices are specified over the -40°C to +125°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

\*EP = Exposed pad.

"\_\_" represents the two number suffix needed when ordering the reset threshold voltage value (see Table 1).

Standard versions and their package top marks are shown in Table 3 at the end of data sheet.

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.analog.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 6 TDFN-EP       | T633-2          | <u>21-0137</u> | <u>90-0058</u>      |

| 8 TDFN-EP       | T833-2          | <u>21-0137</u> | <u>90-0059</u>      |

# 125nA nanoPower Supervisory Circuits with Capacitor-Adjustable Reset and Watchdog Timeouts

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                               | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------|------------------|

| 0                  | 6/09             | Initial release                                                           | —                |

| 1                  | 6/10             | Updated Absolute Maximum Ratings, Electrical Characteristics, and Table 3 | 2, 3, 15         |

| 2                  | 4/13             | Removed Automotive Infotainment from Applications sections                | 1                |

| 3                  | 5/14             | Changed top mark in Table 3 for MAX16057ATT31+ and MAX16057ATT46+         | 15               |

| 4                  | 4/15             | Revised Benefits and Features section                                     | 1                |

| 5                  | 3/17             | Updated title to include "nanoPower"                                      | 1–17             |

| 6                  | 5/21             | Updated Pin Description and Applications Information section              | 6, 9             |

| 7                  | 10/24            | Updated Benefits and Features section                                     | 1                |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. All Analog Devices products contained herein are subject to release and availability.