# Self Protected High Side Driver with Temperature Shutdown and Current Limit

The NCV8461 is a fully protected High–Side driver that can be used to switch a wide variety of loads, such as bulbs, solenoids and other activators. The device is internally protected from an overload condition by an active current limit and thermal shutdown. A diagnostic output reports OFF state open load conditions as well as thermal shutdown.

#### **Features**

- Short Circuit Protection

- Thermal Shutdown with Automatic Restart

- CMOS (3 V / 5 V) Compatible Control Input

- Off State Open Load Detection

- Open Drain Diagnostic Output

- Overvoltage Protection

- Undervoltage Shutdown

- Loss of Ground and Loss of V<sub>D</sub> Protection

- ESD Protection

- Reverse Battery Protection (with external resistor)

- Very Low Standby Current

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- This is a Pb-Free Device

#### **Typical Applications**

- Switch a Variety of Resistive, Inductive and Capacitive Loads

- Can Replace Electromechanical Relays and Discrete Circuits

- Automotive / Industrial

#### **FEATURE SUMMARY**

| Overvoltage Protection               | V <sub>OV</sub>  | 41     | V  |

|--------------------------------------|------------------|--------|----|

| $R_{DSon}$ (max) $T_J = 25^{\circ}C$ | R <sub>ON</sub>  | 350    | mΩ |

| Output Current Limit (typ)           | I <sub>lim</sub> | 1.2    | Α  |

| Operating Voltage Range              | $V_{OP}$         | 5 – 34 | V  |

#### ON Semiconductor®

www.onsemi.com

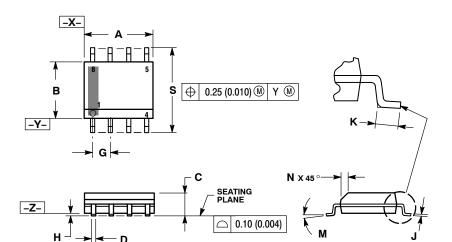

SOIC-8 CASE 751 STYLE 11

#### MARKING DIAGRAM

NCV8461 = Specific Device Code

A = Assembly Location

Y = Year

WW = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

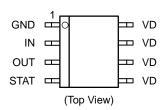

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| NCV8461DR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

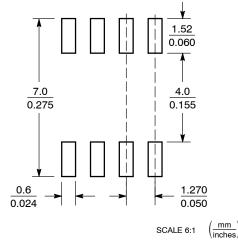

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

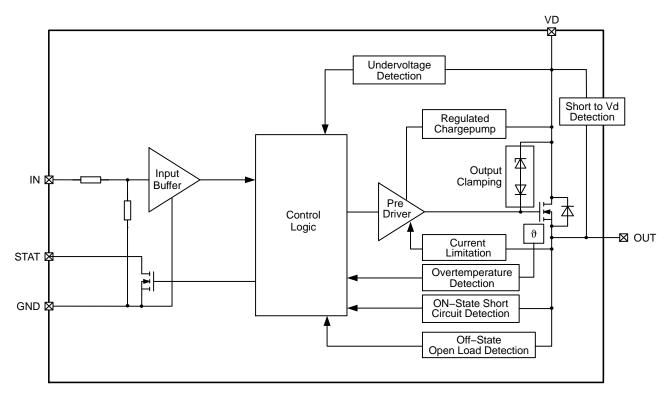

Figure 1. Block Diagram

#### **SO8 PACKAGE PIN DESCRIPTION**

| Pin# | Symbol  | Description       |  |

|------|---------|-------------------|--|

| 1    | GND     | Ground            |  |

| 2    | IN      | Logic Level Input |  |

| 3    | OUT     | Output            |  |

| 4    | STAT    | Status Output     |  |

| 5    | $V_{D}$ | Supply Voltage    |  |

| 6    | $V_{D}$ | Supply Voltage    |  |

| 7    | $V_{D}$ | Supply Voltage    |  |

| 8    | $V_{D}$ | Supply Voltage    |  |

**Table 1. MAXIMUM RATINGS**

|                                                                                                                                     |                      | \          | /alue              |                |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|--------------------|----------------|

| Rating                                                                                                                              | Symbol               | Min        | Max                | Unit           |

| DC Supply Voltage (Note 1)                                                                                                          | $V_{D}$              | -16        | 40                 | V              |

| Peak Transient Input Voltage (Note 1)<br>(Load Dump 38 V, V <sub>D</sub> = 14 V, ISO7637–2 pulse5)                                  | V <sub>peak</sub>    |            | 52                 | V              |

| Input Voltage                                                                                                                       | V <sub>in</sub>      | -10        | 16                 | V              |

| Input Current                                                                                                                       | l <sub>in</sub>      | <b>-</b> 5 | 5                  | mA             |

| Output Current (Note 1)                                                                                                             | l <sub>out</sub>     | _          | Internally Limited | А              |

| Status Current                                                                                                                      | I <sub>status</sub>  | -5         | 5                  | mA             |

| Power Dissipation Tc = 25°C (Note 1)                                                                                                | P <sub>tot</sub>     |            | 1.5                | W              |

| Electrostatic Discharge (Note 1) (HBM Model 100 pF / 1500 $\Omega$ ) Input All Other Pins                                           |                      | ±1.5<br>±5 |                    | DC<br>kV<br>kV |

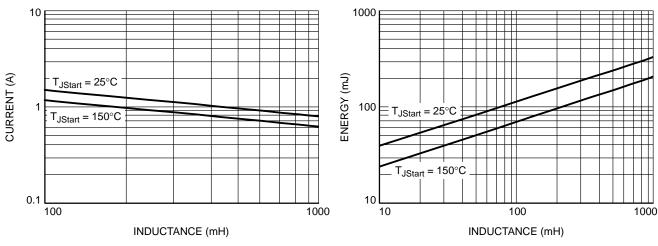

| Single Pulse Inductive Load Switching Energy (Note 1) $V_D = 13.5 \text{ V}; I_L = 0.5 \text{ A}, T_{Jstart} = 150^{\circ}\text{C}$ | E <sub>AS</sub>      | -          | 300                | mJ             |

| Operating Junction Temperature                                                                                                      | TJ                   | -40        | +150               | °C             |

| Storage Temperature                                                                                                                 | T <sub>storage</sub> | -55        | +150               | °C             |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

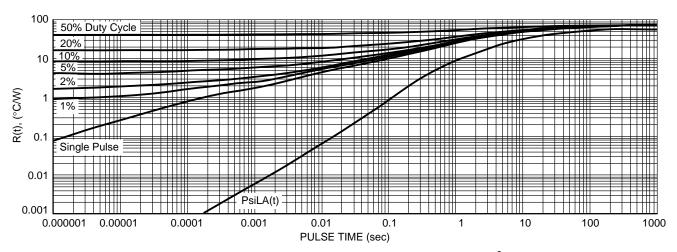

#### **Table 2. THERMAL RESISTANCE RATINGS**

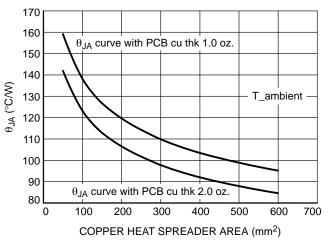

| Parameter                                                                                                         | Symbol                                 | Max. Value | Units |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|-------|

| Thermal Resistance (Note 2) Junction-to-Soldering Point Junction-to-Ambient (6 cm square pad size, FR-4, 2 oz Cu) | R <sub>thJS</sub><br>R <sub>thJA</sub> | 31<br>84   | °C/W  |

<sup>2.</sup> Reverse Output current has to be limited by the load to stay within absolute maximum ratings and thermal performance. See spec table and page 6 for further reverse battery information.

<sup>1.</sup> Not subjected to production testing

$\textbf{Table 3. ELECTRICAL CHARACTERISTICS} \ (V_D = 13.5 \ V; -40^{\circ}C < T_J < 150^{\circ}C \ unless \ otherwise \ specified)$

|                                                |                                      |                                                                                                                                              | Value     |            |            |          |

|------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|------------|----------|

| Rating                                         | Symbol                               | Conditions                                                                                                                                   | Min       | Тур        | Max        | Unit     |

| Operating Supply Voltage                       | $V_D$                                |                                                                                                                                              | 5         | -          | 34         | V        |

| Undervoltage Shutdown                          | V <sub>UV</sub>                      |                                                                                                                                              |           |            | 5          | V        |

| Undervoltage Restart                           | V <sub>UV_Res</sub>                  |                                                                                                                                              |           |            | 5.5        | V        |

| Overvoltage Protection                         | V <sub>OV</sub>                      | I <sub>D</sub> = 4 mA                                                                                                                        | 41        |            |            | V        |

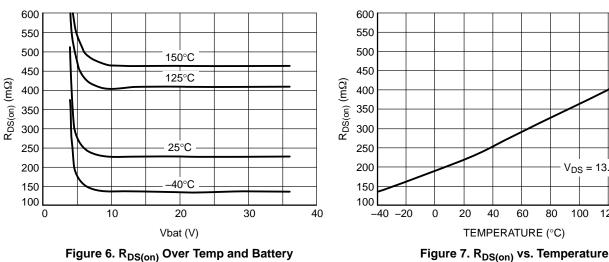

| On Resistance                                  | R <sub>ON</sub>                      | $I_{out}$ = 0.3 A; 6 V < V <sub>D</sub> < 40 V, T <sub>J</sub> = 25°C $I_{out}$ = 0.3 A; 6 V < V <sub>D</sub> < 40 V, T <sub>J</sub> = 150°C |           | 250<br>450 | 350<br>700 | mΩ       |

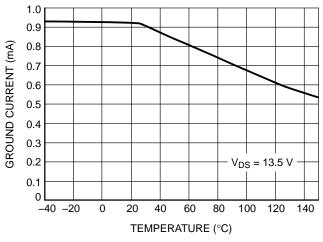

| Standby Current                                | I <sub>D</sub>                       | Off State, $V_{in} = V_{out} = 0 \text{ V}$<br>On State; $V_{in} = 5 \text{ V}$ , $I_{out} = 0 \text{ A}$                                    |           | 13<br>1    | 35<br>1.7  | μA<br>mA |

| Output Leakage Current                         | I <sub>L(off)</sub>                  |                                                                                                                                              |           |            | 12         | μΑ       |

| INPUT CHARACTERISTICS                          |                                      |                                                                                                                                              |           |            |            |          |

| Input Voltage – Low                            | $V_{in\_low}$                        |                                                                                                                                              |           |            | 0.8        | V        |

| Input Voltage – High                           | $V_{in\_high}$                       |                                                                                                                                              | 2.2       |            |            | V        |

| Input Hysteresis Voltage                       | $V_{hyst}$                           |                                                                                                                                              | 1         | 0.3        |            | V        |

| Off State Input Current                        | I <sub>in_OFF</sub>                  | V <sub>in</sub> = 0.7 V                                                                                                                      | 1         |            | 10         | μΑ       |

| On State Input Current                         | I <sub>in_ON</sub>                   | V <sub>in</sub> = 5.0 V                                                                                                                      | 1         |            | 10         | μΑ       |

| Input Resistance (Note 3)                      | R <sub>I</sub>                       |                                                                                                                                              | 1.5       | 3.5        |            | ΚΩ       |

| Input Clamp Voltage                            | V <sub>in_cl</sub>                   | I <sub>in</sub> = 1 mA<br>I <sub>in</sub> = -1 mA                                                                                            | 14<br>–18 | 16<br>–16  | 18<br>–14  | V        |

| SWITCHING CHARACTERISTICS                      | S                                    |                                                                                                                                              |           |            |            |          |

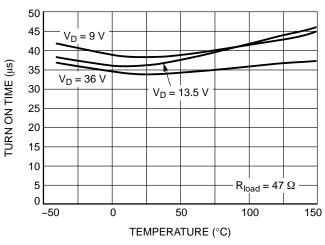

| Turn-On Delay Time                             | t <sub>d_on</sub>                    | to 90% $V_{out}$ , $R_L = 47 \Omega$                                                                                                         |           |            | 140        | μs       |

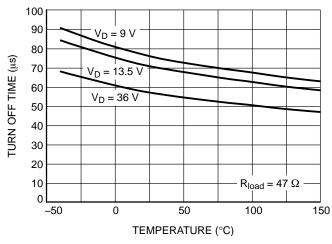

| Turn-Off Delay Time                            | t <sub>d_off</sub>                   | to 10% $V_{out}$ , $R_L = 47 \Omega$                                                                                                         |           |            | 170        | μs       |

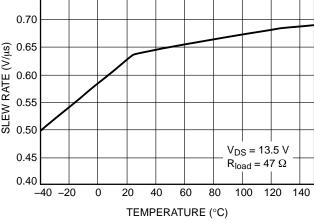

| Slew Rate On                                   | dV <sub>out</sub> /dt <sub>on</sub>  | 10% to 30% Vout, $R_L$ = 47 $\Omega$                                                                                                         |           |            | 2          | V/μs     |

| Slew Rate Off                                  | dV <sub>out</sub> /dt <sub>off</sub> | 70% to 40% Vout, $R_L$ = 47 $\Omega$                                                                                                         |           |            | 2          | V / μs   |

| REVERSE BATTERY (Note 3)                       |                                      |                                                                                                                                              |           |            |            |          |

| Reverse Battery                                | -V <sub>D</sub>                      | Requires a 150 $\Omega$<br>Resistor in GND Connection                                                                                        |           |            | 32         | V        |

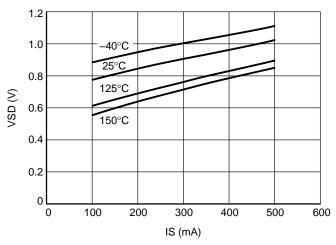

| Forward Voltage                                | $V_{F}$                              | $T_J = 150^{\circ}C$ , $I_S = 200 \text{ mA}$                                                                                                |           | 0.6        |            | V        |

| STATUS PIN CHARACTERISTIC                      | S                                    |                                                                                                                                              |           |            |            |          |

| Status Output Voltage Low                      | V <sub>stat_low</sub>                | $I_{stat}$ = 1.6 mA, $T_J$ = -40°C to 25°C $I_{stat}$ = 1.6 mA, $T_J$ = 150°C (Note 3)                                                       |           |            | 0.4<br>0.6 | V        |

| Status Leakage Current                         | I <sub>stat_leakage</sub>            | V <sub>stat</sub> = 5 V                                                                                                                      | 1         |            | 10         | μΑ       |

| Status Invalid Time After Positive Input Slope | T <sub>d(STAT)</sub>                 |                                                                                                                                              |           | 300        | 700        | μS       |

| Status Clamp Voltage                           | V <sub>stat_cl</sub>                 | $I_{\text{stat}} = 1 \text{ mA}$ $I_{\text{stat}} = -1 \text{ mA}$                                                                           |           | 10<br>-1.4 |            | V        |

| PROTECTION FUNCTIONS (Note                     | e 4)                                 |                                                                                                                                              | 1         |            |            |          |

| Temperature Shutdown (Note 3)                  | T <sub>SD</sub>                      |                                                                                                                                              | 150       | 175        | 200        | °C       |

| Temperature Shutdown Hysteresis (Note 3)       | T <sub>SD_hyst</sub>                 |                                                                                                                                              |           | 10         |            | °C       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Not subjected to production testing

To ensure long term reliability under heavy overload or short circuit conditions, protection and related diagnostic signals must be used together with a proper hardware/software strategy. If the devices operates under abnormal conditions this hardware/software solutions must limit the duration and number of activation cycles. AEC Q100-12 results available upon request.

Table 3. ELECTRICAL CHARACTERISTICS (V<sub>D</sub> = 13.5 V; -40°C < T<sub>J</sub> < 150°C unless otherwise specified)

|                                           |                      |                                                                                                                                   | Value Min Typ Max      |                        |       |    |

|-------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|-------|----|

| Rating                                    | Symbol               | Conditions                                                                                                                        |                        |                        | Max U |    |

| PROTECTION FUNCTIONS (Note                | : 4)                 |                                                                                                                                   |                        |                        |       |    |

| Output Current Limit Initial<br>Peak      | I <sub>lim</sub>     | $T_J = -40^{\circ}\text{C}, \ V_D = 20 \ \text{V (Note 3)}$<br>$T_J = 25^{\circ}\text{C}$<br>$T_J = 150^{\circ}\text{C (Note 3)}$ | 0.7                    | 1.2                    | 2     | А  |

| Repetitive Short Circuit Current<br>Limit | I <sub>lim(SC)</sub> | $T_J = T_{Jt}$ (Note 3)                                                                                                           |                        | 1                      |       | Α  |

| Switch Off Output Clamp Voltage           | V <sub>clamp</sub>   | $I_D = 4 \text{ mA}, V_{in} = 0 \text{ V}$                                                                                        | V <sub>D</sub> –<br>41 | V <sub>D</sub> –<br>47 |       | V  |

| DIAGNOSTICS CHARACTERIST                  | ics                  |                                                                                                                                   |                        |                        |       |    |

| Short Circuit Detection Voltage           | V <sub>OUT(SC)</sub> |                                                                                                                                   |                        | 2.8                    |       | V  |

| Openload Off State Detection<br>Threshold | V <sub>OL</sub>      | V <sub>in</sub> = 0 V                                                                                                             | 1.5                    |                        | 3.5   | V  |

| Openload Detection Current                | I <sub>L(OL)</sub>   |                                                                                                                                   |                        | 5                      |       | μΑ |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Not subjected to production testing

**Table 4. STATUS PIN TRUTH TABLE**

| Conditions                          | Input | Output | Status |

|-------------------------------------|-------|--------|--------|

| Normal Operation                    | L     | L      | Н      |

|                                     | Н     | Н      | Н      |

| Short Circuit to GND                | L     | L      | Н      |

|                                     | Н     | L*     | L      |

| Short to V <sub>D (OFF State)</sub> | L     | Н      | L      |

|                                     | Н     | Н      | Н      |

| Current Limitation                  | L     | L      | Н      |

|                                     | Н     | H**    | Н      |

| Overtemperature                     | L     | L      | Н      |

|                                     | Н     | L      | L      |

| OFF State Open Load                 | L     | Н      | L      |

|                                     | Н     | Н      | Н      |

<sup>4.</sup> To ensure long term reliability under heavy overload or short circuit conditions, protection and related diagnostic signals must be used together with a proper hardware/software strategy. If the devices operates under abnormal conditions this hardware/software solutions must limit the duration and number of activation cycles. AEC Q100–12 results available upon request.

<sup>\*</sup> Output = "L"; V<sub>OUT</sub> < 2 V typ. \*\* Output = "H"; V<sub>OUT</sub> > 2 V typ.

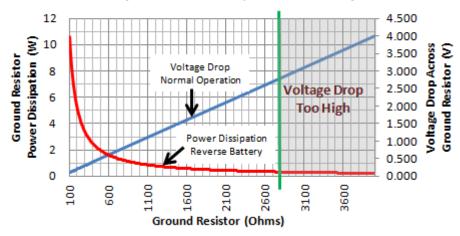

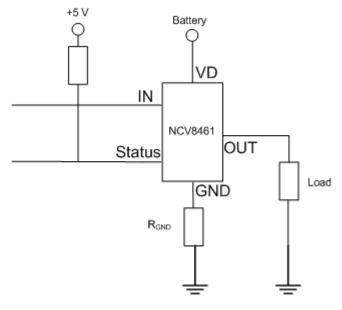

#### REVERSE BATTERY PROTECTION

The NCV8461 provides reverse battery protection up to 32 V. This protection requires a Resistor in the GND path. The recommended GND resistor is 150  $\Omega$ , but a variety of resistor values can be chosen for this purpose. The graph below shows the considerations and constraints for selection of the GND resistor. Figure 2 shows the power dissipation in the GND resistor during a 32 V reverse battery event on the left axis, while the right axis shows the voltage drop

across the GND resistor while in normal operation. The far right side of the graph is grayed out to indicate that the voltage drop across the resistor is too high, and the part will not be able to turn on with a standard 5 V on the input pin. Selection of the optimal GND resistor requires balancing the power dissipation considerations while in a reverse battery event, with the turn on capability of the input signal during normal operation.

# NCV8461 Reverse Battery Considerations Normal Operation Vin = 5 V, Reverse Battery = 32 V

Figure 2. Reverse Battery Considerations

Figure 3. Reverse Battery Protection Circuit

#### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Maximum Single Pulse Switch Off **Current vs. Inductance**

Figure 5. Maximum Single Pulse Switch Off **Energy vs. Inductance**

$V_{DS} = 13.5 \text{ V}$

140

100 120

80

$V_{DS} = 13.5 \text{ V}$

$R_{load} = 47 \Omega$

100

120

140

Figure 6. R<sub>DS(on)</sub> Over Temp and Battery

0.80

0.75

0.70

0.65 0.60 0.55

0.50

0.45

0.40

-40 -20

0

20

SLEW RATE (V/µs)

0.75 0.70 SLEW RATE (V/µs) 0.50 0.50 0.50  $V_{DS} = 13.5 V$ 0.45  $R_{load} = 47 \Omega$

TEMPERATURE (°C) Figure 8. Slew Rate On vs. Temperature

40

60

80

Figure 9. Slew Rate Off vs. Temperature

#### TYPICAL PERFORMANCE CHARACTERISTICS

2.0 1.8 1.6 1.4 CURRENT (A) 1.2 1.0 0.8 0.6  $V_{DS} = 13.5 \text{ V}$ 0.4 0.2 0 80 -20 0 20 40 60 100 120 140 -40 TEMPERATURE (°C)

Figure 10. On State Ground Current vs. Temp

Figure 11. Current Limit vs. Temperature

Figure 12. Body Diode

Figure 13. Turn On Time vs. Temperature

Figure 14. Turn Off Time vs. Temperature

Figure 15. Junction-to-Ambient Thermal Resistance vs. Copper Area

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 16. Junction to Ambient Transient Thermal Impedance (600 mm<sup>2</sup> Copper Area)

# **ISO 7637-2:2011 (E) PULSE TEST RESULTS**

| ISO 7637-2:2011(E) | Test Severity Levels, 13.5 V System  Delays and |      | # of Pulses or Test | Pulse / Burst Rep. |        |  |

|--------------------|-------------------------------------------------|------|---------------------|--------------------|--------|--|

| Test Pulse         | III                                             | IV   | Impedance           | Time               | Time   |  |

| 1                  | -112                                            | -150 | 2 ms, 10 Ω          | 500 pulses         | 0.5 s  |  |

| 2a                 | +55                                             | +112 | 0.05 ms, 2 $\Omega$ | 500 pulses         | 0.5 s  |  |

| 3a                 | -165                                            | -220 | 0.1 μs, 50 Ω        | 1 h                | 100 ms |  |

| 3b                 | +112                                            | +150 | 0.1 μs, 50 Ω        | 1 h                | 100 ms |  |

| ISO 7637-2:2011(E) | Test Results |    |  |

|--------------------|--------------|----|--|

| Test Pulse         | III          | IV |  |

| 1                  | С            | С  |  |

| 2a                 | С            | Е  |  |

| 3a                 | С            | С  |  |

| 3b                 | С            | С  |  |

| Class | Functional Status                                                                                                                                               |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| С     | One or more functions of a device do not perform as designed during exposure but return automatically to normal operation after exposure is removed.            |  |  |  |  |

| Е     | One or more functions of a device do not perform as designed during and after exposure and cannot be returned to proper operation without replacing the device. |  |  |  |  |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

XS

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 4.80        | 5.00  | 0.189     | 0.197 |

| В   | 3.80        | 4.00  | 0.150     | 0.157 |

| C   | 1.35        | 1.75  | 0.053     | 0.069 |

| D   | 0.33        | 0.51  | 0.013     | 0.020 |

| G   | 1.27        | 7 BSC | 0.050 BSC |       |

| Н   | 0.10        | 0.25  | 0.004     | 0.010 |

| J   | 0.19        | 0.25  | 0.007     | 0.010 |

| K   | 0.40        | 1.27  | 0.016     | 0.050 |

| М   | 0 °         | 8 °   | 0 °       | 8 °   |

| N   | 0.25        | 0.50  | 0.010     | 0.020 |

| S   | 5.80        | 6.20  | 0.228     | 0.244 |

## **SOLDERING FOOTPRINT\***

0.25 (0.010) M Z Y S

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot = Year = Work Week W

= Pb-Free Package

XXXXXX XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### SOIC-8 NB CASE 751-07 ISSUE AK

#### **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | 7. BASE, #1 8. EMITTER, #1  STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                        | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8:<br>PIN 1. COLLECTOR, DIE #1<br>2. BASE, #1<br>3. BASE, #2                                                                                                       |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                  |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15:  PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON              | STYLE 16:  PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                    |

| 5. RXE 6. VEE 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6            | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V MON 6. VBULK 7. VBULK 8. VIN                                                                         |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                          |

| DOCUMENT NUMBER: | 98ASB42564B | Printed versions are uncontrolled except when accessed directly from the Document Repository.  Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                | PAGE 2 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales