# Si3406x Family Data Sheet

## Fully-Integrated IEEE 802.3-Compliant POE+ PD Interface and High-Efficiency Switching Regulators with Sleep, Wake, and LED Drive

The Si3406x family integrates all power management and control functions required in a Power-over-Ethernet Plus (PoE+) powered device (PD) application. These devices convert the high voltage supplied over the 10/100/1000BASE-T Ethernet connection to a regulated, low-voltage output supply. The optimized architecture of this device family minimizes the solution footprint and external BOM cost and enables the use of low-cost external components while maintaining high performance. The Si3406x family integrates the required diode bridges and transient surge suppressor, thus enabling direct connection of the IC to the Ethernet RJ-45 connector. The switching power FET and all associated functions are also integrated. The integrated, current mode controlled switching regulator supports isolated or non-isolated flyback and buck converter topologies. The switching frequency for the regulator is tunable with a simple external resistor value to help avoid unwanted harmonics for better emissions control. A synchronous driver is provided to optionally drive a secondary side FET to improve efficiency of power conversion. Connection to the PSE switch is maintained during sleep by an optional automated maintain-power-signature (MPS) signal.

These devices fully support the IEEE 802.3at specification for the cases of single or two event classification. Standard external resistors provide the proper IEEE 802.3 signatures for the detection function and programming of the classification mode, and internal startup circuits ensure well-controlled soft-start initial operation of both the hotswap switch and the voltage regulator.

The Si34061 and Si34062 add main transformer bias winding support for ultra-high-efficiency operation.

The Si34062 includes support for sleep modes with wake function, as well as LED drive capability. These features can be utilized to minimize standby current, control sleep and wake states, and provide application status information using an LED.

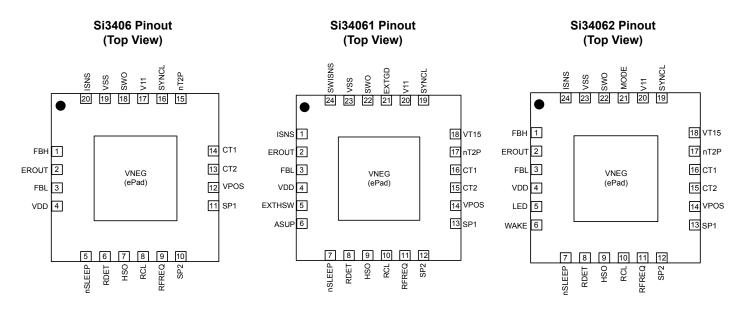

The Si3406 is available in a low-profile, 20-pin, 5 x 5 mm QFN package, and the Si34061 and Si34062 are available in low-profile, 24-pin, 5 x 5 mm QFN packages.

## KEY FEATURES

- Type 1 (PoE) or Type 2 (PoE+) power

- Full IEEE 802.3at compliance

- Synchronous secondary FET driver

- Current mode dc-dc converter

- Tunable switching frequency

- · Auxiliary transformer winding support

- Auxiliary wall adapter support (12 V to 57 V)

Internal hotswap and switching FET bypass

- support

- Automated maintain-power-signature (MPS) support

- Sleep mode augmented with wake pin, mode control, and LED driver

- 120 V Absolute Max voltage performance

- Extended -40 to +85 °C temperature

- Compact ROHS-compliant 5 mm x 5 mm QFN Package

#### APPLICATIONS

- · Voice over IP telephones

- · Wireless access points

- Security and surveillance IP cameras

- · Lighting luminaires

- · Point-of-sale terminals

- Internet appliances

- Network devices

## 1. Ordering Guide

| Ordering Part Number <sup>1</sup> | Package                 | Temperature Range (Ambient) | Applications                                           |  |

|-----------------------------------|-------------------------|-----------------------------|--------------------------------------------------------|--|

| Si3406-A-GM                       | 5 x 5 mm 20-QFN         | –40 to 85 °C Extended       | All Purposes                                           |  |

| 313400-A-GIVI                     | Pb-free, RoHS-compliant |                             |                                                        |  |

| 0:04004 A OM                      | 5 x 5 mm 24-QFN         |                             | Any high-power, high-efficiency                        |  |

| Si34061-A-GM                      | Pb-free, RoHS-compliant | –40 to 85 °C Extended       | uses, such as Wireless Access<br>Points and IP Cameras |  |

| Si34062-A-GM                      | 5 x 5 mm 24-QFN         | -40 to 85 °C Extended       | IP Phones with manual sleep                            |  |

| 5154002-A-GM                      | Pb-free, RoHS-compliant |                             | mode                                                   |  |

## Table 1.1. Si3406x Ordering Guide

1. Add an "R" to the end of the part number for tape and reel option (e.g., Si3406-A-GMR, Si34061-A-GMR, or Si34062-A-GMR).

## **Table of Contents**

| 1. | Ordering Guide                                                                                                       | • | . 2 |

|----|----------------------------------------------------------------------------------------------------------------------|---|-----|

| 2. | System Overview                                                                                                      |   | . 4 |

|    | 2.1 Block Diagrams.                                                                                                  |   | . 4 |

|    | 2.2 Power over Ethernet (PoE) Line-Side Interface                                                                    |   |     |

|    | 2.2.1 Surge Protection                                                                                               |   |     |

|    | 2.2.2 Telephony Protection                                                                                           |   |     |

|    | 2.3 Hotswap Switch                                                                                                   |   |     |

|    | 2.4 HSSW State Machine                                                                                               |   |     |

|    | 2.4.1 External HSSW FET Driver                                                                                       |   | . 7 |

|    | 2.5 DC to DC Converter                                                                                               |   |     |

|    | 2.5.1 Average Current Sensing, Overcurrent, Low-Current Detection, and Output Short Protection 2.5.2 Sync FET Driver |   |     |

|    | 2.5.2 Sync PET Driver                                                                                                |   |     |

|    | 2.7 Regulators                                                                                                       |   |     |

|    | 2.8 Sleep Mode                                                                                                       |   |     |

|    | 2.9 Special Sleep Mode                                                                                               |   |     |

|    | 2.10 External Wall Adapter Support                                                                                   |   |     |

| 2  | Application Examples                                                                                                 |   |     |

|    |                                                                                                                      |   |     |

|    | Electrical Specifications                                                                                            |   |     |

| 5. | Pin Descriptions                                                                                                     |   |     |

|    | 5.1 Detailed Pin Descriptions                                                                                        | • | .21 |

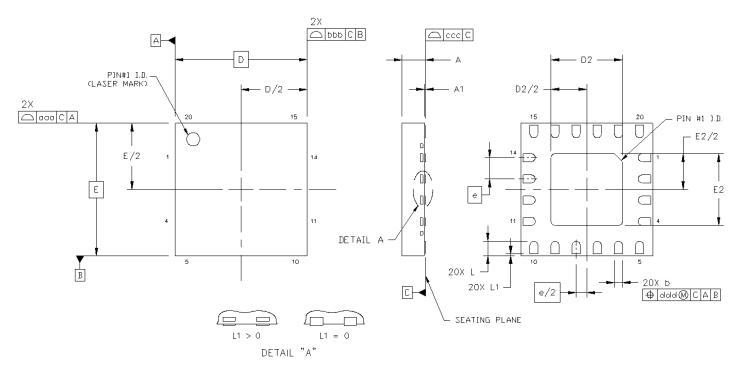

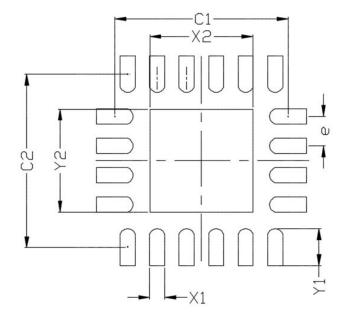

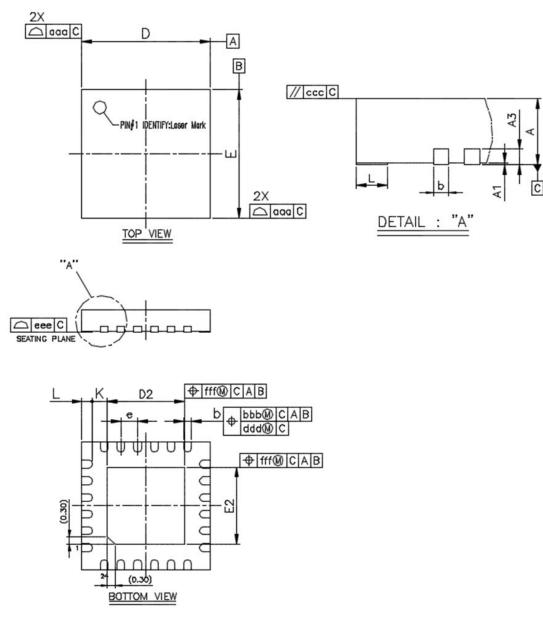

| 6. | Packaging                                                                                                            | • | 26  |

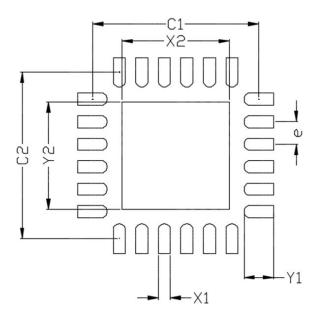

|    | 6.1 Package Outline: Si3406                                                                                          | • | .26 |

|    | 6.2 Land Pattern: Si3406                                                                                             |   | .28 |

|    | 6.3 Package Outline: Si34061/62                                                                                      |   | .29 |

|    | 6.4 Land Pattern: Si34061/62                                                                                         |   | .31 |

| 7. | Top Markings                                                                                                         |   | 32  |

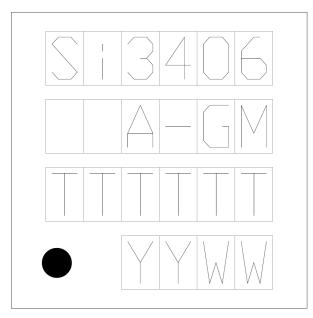

|    | 7.1 Si3406 Top Marking                                                                                               |   | .32 |

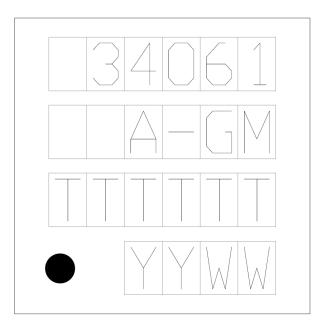

|    | 7.2 Si34061 Top Marking                                                                                              |   | .33 |

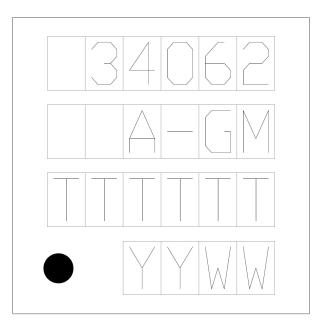

|    | 7.3 Si34062 Top Marking                                                                                              |   | .34 |

| 8. | Revision History                                                                                                     |   | 35  |

Si3406x Family Data Sheet • System Overview

## 2. System Overview

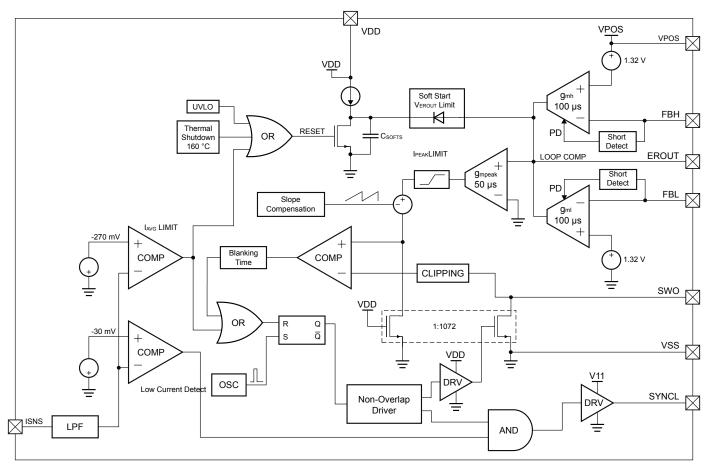

The following Block Diagrams will give the designer a sense for the internal arrangement of functional blocks, plus their relationships to external pins. The Block Diagrams are followed by a description of the features of these integrated circuits.

## 2.1 Block Diagrams

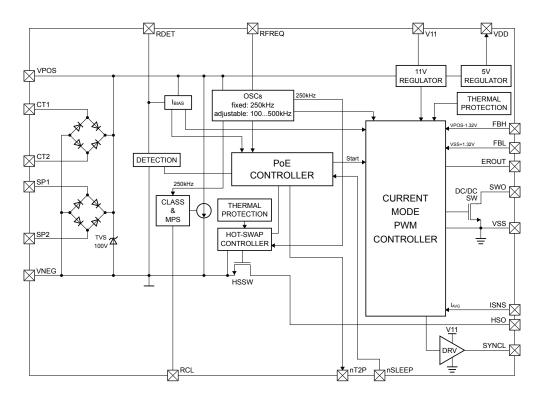

Figure 2.1. Si3406 Block Diagram

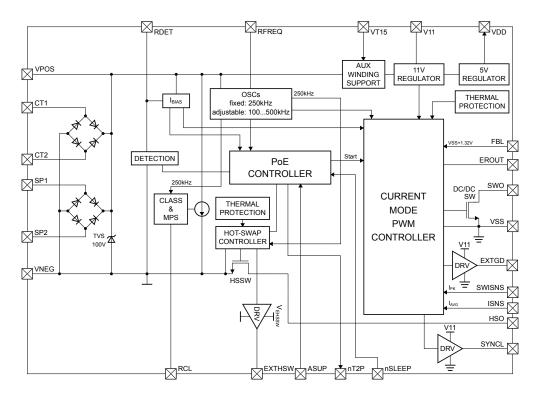

Figure 2.2. Si34061 Block Diagram

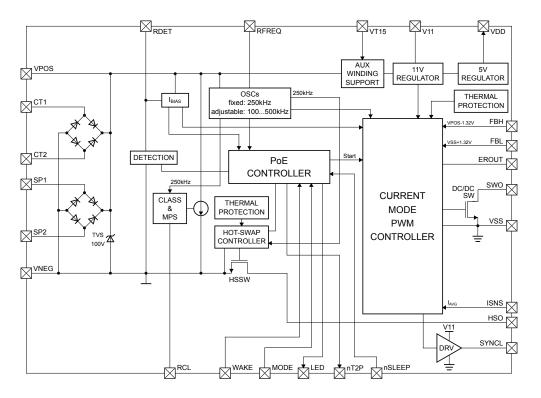

Figure 2.3. Si34062 Block Diagram

## 2.2 Power over Ethernet (PoE) Line-Side Interface

The PoE line interface consists of diode bridges, internal surge protection, and the protocol interface support for detection and classification.

Internal diode bridge maximum current is given by the specification,  $I_{RECT}$ . For Class 1 and Class 2 applications, the internal diode bridge can be used. For Class 3 and Class 4, an external diode bridge needs to be installed.

The external bridge should be connected in parallel to the internal bridge and the designer must ensure that the internal bridge will not conduct significant current by using low-voltage-drop external diodes. For higher efficiency, Schottky diodes are recommended.

Instead of a diode bridge, a Mosfet based bridge can be used as well to further improve the overall efficiency.

The chip features active protection against surge transients and accidentally applied telephony voltages.

#### 2.2.1 Surge Protection

The surge protection circuit is activated if the VPOS-VNEG voltage exceeds V<sub>PROT</sub> and the hotswap switch is off (dc-dc is not powered). If the hotswap switch is on, the surge power is sunk in the dc-dc input capacitance.

The internal surge protection can be overridden with an external TVS if higher than specified surge conditions need be tolerated. The external surge device must be connected between VPOS an VNEG in parallel to the internal one; therefore, the designer must ensure that the external surge protection will activate prior to the internal surge protection.

## 2.2.2 Telephony Protection

The Si3406x provides protection against telephony ringing voltage. The telephony ringing is much longer than the surge pulse but it has less energy, therefore, the Si3406x has a switch parallel with the supply (between VPOS and VNEG). When the protection circuit is activated, it turns ON the protection switch; the ringing energy then dissipates on this switch and ringing generator resistance (> 400  $\Omega$ ).

## 2.2.3 Detection and Classification

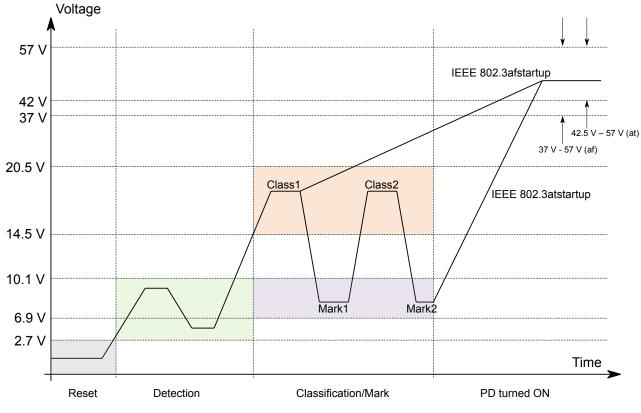

When the Si3406x is connected via Ethernet cable to a PSE-enabled Ethernet switch, it must provide a characteristic resistance (~25  $k\Omega$ ) to the PSE in a given voltage range (2.7–10.1 V). This is called detection. After the PSE detects the PD, the PSE increases the voltage above the classification threshold 14.5 V. Then, the PD provides the classification current to inform the PSE about its required power class (Class 1, 2, 3, or 4). Type 1 PSEs will recognize the Class 4 PD as Class 0, providing 15.4 W to the PD. Therefore, the optimal Class 4 PD application is designed with two power modes: Low-Power mode (for Type 1 PSE) and High-Power mode (for Type 2 PSE). Type 2 PSEs have additional voltage steps before switching on the PD. After an initial classification voltage pulse, the Type 2 PSE reduces the voltage below the mark threshold level (10 V). At that point, the PD should provide a non-valid detection resistance. Then, the PSE raises a voltage up again to the Class event range (Class 2). Last, before turning ON the dc-dc, the PSE reduces the voltage again (Mark2). This sequence is recognized by the si3406x, and it pulls down its nT2P pin to inform the application about the higher available power; otherwise, the application will need to operate in a reduced power consumption state (Type 1) if the PSE is incapable of delivering Class 4 power.

Figure 2.4. Powered Device Voltages

## 2.3 Hotswap Switch

The hotswap switch is a high-voltage device that separates the PoE inerface from the dc-dc converter domain. The internal hotswap switch (HSSW) is turned on (conducting) when the PoE interface voltage goes above  $V_{UVLO_R}$ . It provides limited inrush current until the dc-dc side capacitor is charged. The hotswap switch turns off (open) if voltage on the HSSW switch (HSO-VNEG) is greater than  $V_{HSSW OFF}$ .

In overload, the hotswap switch goes into current-limiting mode with a current limit of  $I_{OVL}$ . It will turn back ON after  $T_{WAITHSSW}$  elapses and the dc-dc input capacitor is recharged, meaning the HSO-VNEG voltage is less than  $V_{HSSW}$  ON.

The hotswap switch (if it is in the on state and conducting) can detect if the current is lower than I<sub>MPSth</sub>. If automatic sleep mode is enabled, the chip turns on MPS pulse generation, which ensures that the PSE will not disconnect.

With the Si34061, an external hotswap switch can be used to improve efficiency and reduce thermal stress in high current applications. For Class 3 applications, using an external hotswap switch is recommended; for Class 4, it is mandatory because the internal hotswap switch otherwise generates significant heat. When an external hotswap switch is used, intelligent switch control ensures that inrush current limiting and automatic MPS request of the internal switch are still supported.

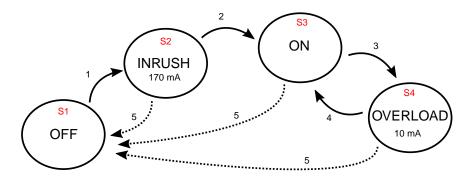

#### 2.4 HSSW State Machine

The HSSW operates as simple 4-state state machine:

Figure 2.5. Hotswap Switch 4-State Machine

## **OFF State**

HSSW turn-on is controlled by UVLO, the undervoltage lockout feature. When UVLO is engaged, the HSSW is OFF. In this state, the HSSW is in idle mode, VNEG and HSO pins are disconnected. In normal operation, a complete detect/classification procedure precedes the HSSW turn-on, and the control of this sequence is implemented in the state machine logic of the chip.

#### **INRUSH State**

After the controller enables the HSSW, the block starts operation in the INRUSH state. In this state the switch itself is not directly turned on, but operating in a closed-loop current limit mode to avoid high current peaks during the charging of the input capacitor of the dc-dc converter.

If the V<sub>HSSW</sub> voltage drops below 380 mV (meaning the bypass cap is 99% charged), the HSSW will change state to ON either in Type1 classification immediately, or in Type2 classification if the HSSW has been in the INRUSH state for at least 80 ms.

## **ON State**

In ON state, the HSSW switch is completely turned on. The HSSW circuit continuously monitors  $V_{HSSW}$ . HSSW will change to OVERLOAD state if  $V_{HSSW}$  voltage increases over 3.5 V for at least 140  $\mu$ s.

#### **OVERLOAD State**

In OVERLOAD state the HSSW operates in closed-loop low current limit mode. If the V<sub>HSSW</sub> voltage drops below 380 mV again, and the HSSW has been in the OVERLOAD state for at least 80 ms, the HSSW will change back to the ON state.

## 2.4.1 External HSSW FET Driver

An external HSSW FET may be used to improve thermal operation of an Si34061 at very high power loading levels (the top end of Class 4).

With the Si34061, the chip automatically detects if the EXTHSW pin is connected to VNEG or to a FET gate at startup. If the external hotswap FET driver will not be used, the EXTHSW pin must be tied to VNEG.

For further information on using an external HSSW FET, please refer to "AN1130: Using the Si3406/Si34061/Si34062 PoE+ and Si3404 PoE PD Controller In Isolated and Non-Isolated Designs".

## 2.5 DC to DC Converter

The dc-dc converter is current-controlled for easier compensation and more robust protection of circuit magnetics. The controller has the following features:

- · High- and low-side error amplifier (supports Buck and Flyback topologies).

- <1 Ω internal switching FET</li>

- · Driver for optional synchronous rectification

- Overcurrent detection

- · Low current detection

- · Cycle skipping at low current and short circuit conditions

- Optional external switching FET driver (Si34061)

- · Automatic non-overlap control

Figure 2.6. Si3406x DC-DC Converter Block Diagram

When the internal switching FET is used with the converter, internal peak current detection is employed. When the EXTGD pin and an external FET are used with Si34061, an external current sense resistor is used to measure the peak current connected to the SWISNS pin. Changing that resistor allows the application to set the converter maximum peak current to protect the magnetic components (like the transformer) from saturation.

Feedback to the dc-dc converter can be provided in three ways:

- High side, referenced to VPOS, connected to FBH pin (Buck converter)

- · Low side, referenced to VSS, connected to FBL pin (nonisolated Flyback)

- · Directly to EROUT pin by a voltage to current converter (isolated Flyback)

The EROUT pin provides current output (if FBL or FBH is used) and voltage input. Also, the loop compensation impedance is connected to EROUT. The active voltage range is V<sub>EROUT</sub>, which is proportional to the converter peak current.

The converter startup is not configurable; soft start is accomplished by internal circuitry. Soft start time is T<sub>SOFTSTART</sub>. The intelligent soft start circuit dynamically adjusts the soft start time depending on the connected load.

## 2.5.1 Average Current Sensing, Overcurrent, Low-Current Detection, and Output Short Protection

The application average current is sensed by an external resistor ( $R_{SENSE}$ ) connected between VSS and ISNS. Overcurrent is detected and triggered when the voltage on the sense resistor exceeds  $V_{ISNS_OVC}$ . Sizing the resistor allows the designer to set the overcurrent limit according to application needs. When overcurrent is triggered, the dc-dc controller goes into reset until the overcurrent resolves. When the overcurrent is no longer present, the controller starts up again with softstart.

This external sense resistor is also used to detect a low current situation. When the voltage on the sense resistor goes below  $V_{ISNS\_LC}$ , the dc-dc controller disables the sync FET and the external hotswap switch, allowing very low current consumption—the internal hotswap switch then measures the chip current internally. If the average current is lower than the PoE maintain power signature (MPS) limit, and if automatic sleep mode is enabled (using the NSLEEP pin), the chip turns on the MPS generation. See the sleep mode section for further detail.

The Si3406x integrates output short protection. When the output is shorted, the average input current remains in the normal operating range. If the controller detects a high EROUT signal for more than 1 ms, it resets the dc-dc controller, and a new startup cycle with soft-start turn ON follows.

## 2.5.2 Sync FET Driver

With the Si3406x family, an optional synchronous rectifying FET may be used in place of an output rectifier diode for improved power conversion efficiency.

A gate driver is provided for this purpose. The synchronous rectifying FET driver is enabled by default in Si3406x configurations, but, if a synchronous FET is not used in the design, the SYNCL pin must not be connected (do not connect SYNCL to any power or ground rail). The synchronous rectifying FET driver is disabled only when the dc-dc converter measures low average current (meaning lower than  $V_{ISNS LC}$  on ISNS). This ensures low sleep mode current consumption.

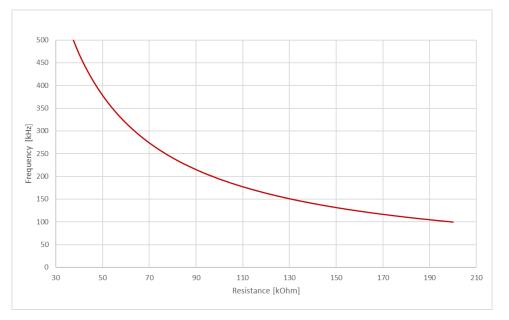

## 2.6 Tunable Oscillator

The dc-dc frequency can be fixed to 250 kHz or tunable by an external resistor.

The tuning resistor must be connected between the  $R_{FREQ}$  pin and VPOS. If  $R_{FREQ}$  is shorted to VPOS, the fixed frequency oscillator will provide the clock,  $F_{OSCINT}$ , to the dc-dc converter; otherwise, the resistor will determine the frequency as shown in the curve below.

Figure 2.7. R<sub>FREQ</sub> Frequency Selector Diagram

## 2.7 Regulators

The chip provides a 5 V output to power LEDs or optocouplers. This is a closed-loop regulator, which ensures accurate output voltage. The 5 V regulator is supplied by an internal 11 V open loop regulator, which also provides power for the external FET gate drivers. The 11 V regulator is supplied by a coarse regulator, which is also open-loop. With the Si34061 and Si34062, the VT15 pin can be used to supply this regulator from an optional auxiliary transformer winding. The advantage of doing so is additional power saving since the external FET drivers' current is not generated from the PoE 50 V but, rather, from a transformer-provided 12–16.5 V. The application must be designed to ensure that the absolute maximum rating voltage for the VT15 pin is not exceeded.

## 2.8 Sleep Mode

The Si3406 and Si34061 have automatic (consumption-based) and non-automatic sleep modes. When SLEEPb is tied to ground, the automatic sleep mode is enabled, meaning that if the current consumption is lower than  $I_{MPSth}$ , the chip will automatically generate MPS pulses from the PSE. If SLEEPb is tied to VDD, then it will not generate MPS pulses, and the PSE will disconnect if total application current consumption drops below 5–10 mA.

For non-automatic sleep mode, tie SLEEPb high at initial startup (right after the hotswap switch turns on). The chip turns OFF automatic mode, but pulling SLEEPb low will force MPS generation as long as the pin is held low. Using this mode, the designer can control MPS generation. For details on MPS generation connection, please refer to "AN1130: Using the Si3406/Si34061/Si34062 PoE+ and Si3404 PoE PD Controller In Isolated and Non-Isolated Designs".

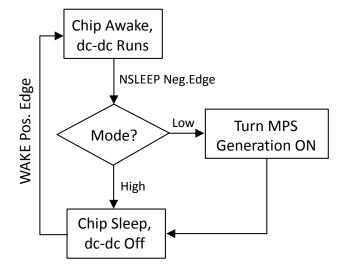

## 2.9 Special Sleep Mode

In the Si34062, a special sleep mode is available which includes LED, WAKE, and MODE pin support. The LED pin drives a light emitting diode to (for example) illuminate a button on the primary side of the application. The WAKE pin triggers wakeup, and the MODE button controls if MPS generation is enabled in sleep. In the Si34062 case, nSLEEP is used to initiate sleep.

The sleep mode is initiated by a negative transition on nSLEEP. It is latched at that negative transition event together with MODE, so their status is kept until wakeup even if the input changes on these pins due to the secondary side losing power. MPS generation is enabled if MODE = 0 at the nSLEEP transition. The following figure shows the Si34062 sleep mode behavior.

Figure 2.8. Si34062 Special Sleep Mode Behavior

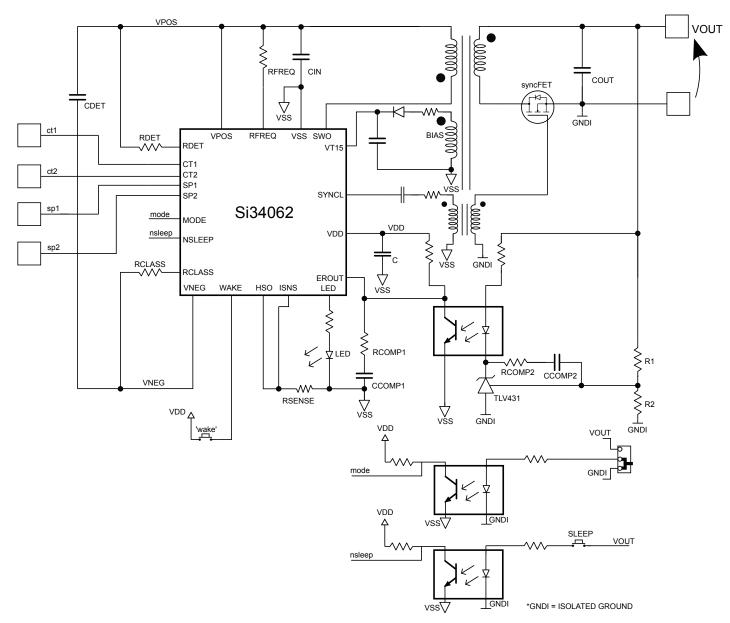

Refer to Figure 3.3 Si34062 Isolated Flyback Application Diagram on page 13, which shows the connectivity for the Si34062 with the special sleep mode.

For details on special sleep mode, please refer to "AN1130: Using the Si3406/Si34061/Si34062 PoE+ and Si3404 PoE PD Controller In Isolated and Non-Isolated Designs".

## 2.10 External Wall Adapter Support

The Si3406x supports using a wide voltage range of external wall adapters as a primary or secondary supply. The controller is able to provide a stable output voltage with PoE input voltage from the PSE, or with low voltage (12 V) in ASUP mode from the wall adapter. However, if the transformer was designed and optimized for PoE voltages, then the same transformer will not be able to provide high power to the application from a low-voltage adapter (12 V). To ensure operation from both PoE input and wall adapter in the full power range, a high-voltage adapter is recommended.

For details on options and supported modes of adapter connection, please refer to "AN1130: Using the Si3406/Si34061/Si34062 PoE+ and Si3404 PoE PD Controller In Isolated and Non-Isolated Designs".

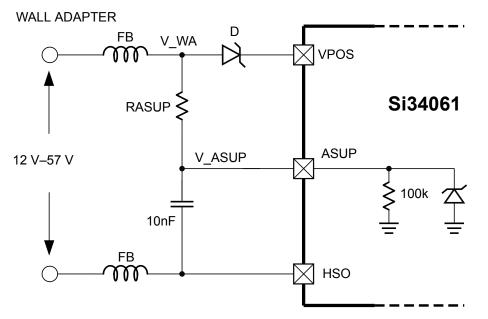

Figure 2.9. Auxiliary Wall Adapter Connection Example

## 3. Application Examples

The following diagrams demonstrate the ease of use and straightforward BOM of the Si3406x Powered Device ICs. Detailed reference designs are available in Evaluation KIT User Guides. Also refer to "AN1130: Using the Si3406/Si34061/Si34062 PoE+ and Si3404 PoE PD Controller In Isolated and Non-Isolated Designs".

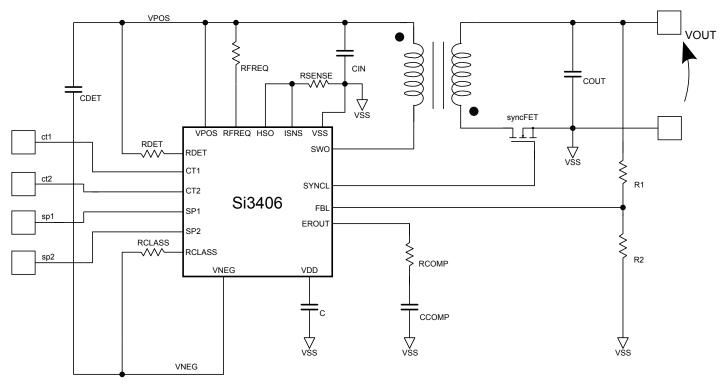

Figure 3.1. Si3406 Non-Isolated Flyback Application Diagram

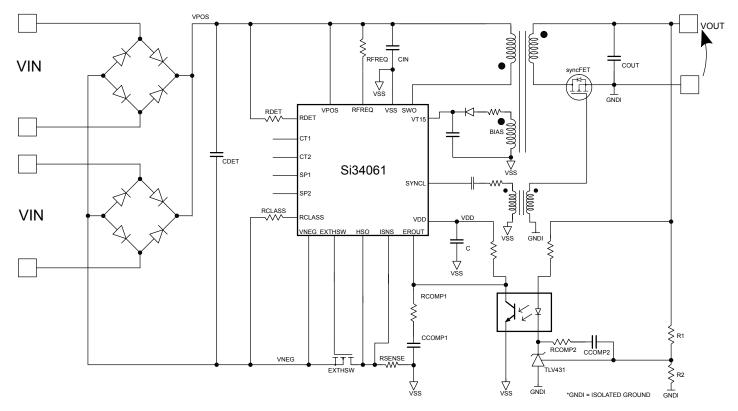

Figure 3.2. Si34061 Isolated Flyback Application Diagram

Figure 3.3. Si34062 Isolated Flyback Application Diagram

## 4. Electrical Specifications

| Туре                    | Description                                                                                                                                | Min  | Мах | Units |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|

|                         | CT1-CT2 or SP1-SP2                                                                                                                         | -100 | 100 | V     |

|                         | VNEG-VSS, VPOS-VNEG, HSO <sup>2</sup> , RDET <sup>3</sup>                                                                                  | -0.7 | 100 | V     |

|                         | SWO-VSS                                                                                                                                    | -0.7 | 120 | V     |

|                         | ISNS, SWISNS                                                                                                                               | -1   | 1   | V     |

| Voltage                 | Low Voltage pins: FBH <sup>3</sup> , EROUT, FBL,<br>NSLEEP, RCL <sup>2</sup> , RFREQ <sup>3</sup> , ASUP <sup>3</sup> , WAKE,<br>MODE, LED | -0.7 | 6   | V     |

|                         | Mid Voltage pins: SYNCL,VT15, EXTGD,<br>EXTHSW                                                                                             | -0.7 | 18  | V     |

|                         | Other Mid Voltage pin: V11                                                                                                                 | -0.7 | 12  | V     |

| Peak Current            | CT1, CT2, SP1, SP2, VPOS <sup>4</sup>                                                                                                      | -5   | 5   | A     |

| DC Current <sup>5</sup> | CT1, CT2, SP1, SP2                                                                                                                         | -0.2 | 0.2 | А     |

|                         | Storage Temperature                                                                                                                        | -65  | 150 | °C    |

| Temperature             | Ambient Operating Temperature                                                                                                              | -40  | 85  | °C    |

|                         | Junction Tempertature                                                                                                                      |      | 150 | °C    |

## Table 4.1. Absolute Maximum Ratings<sup>1</sup>

## Note:

1. Unless otherwise noted, all voltages referenced to VSS. Permanent device damage may occur if the maximum ratings are exceeded. Functional operation should be restricted to those conditions specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may adversely affect device reliability.

2. Voltage referenced to VNEG.

3. Voltage referenced to VPOS.

4. The Si340x provides internal protection from certain transient surge voltages on these pins. Refer to AN1130: Si3404/06x PoE-PD Controller Design Guide for further details.

5. Higher dc current is possible in the application, but only utilizing external bridge diodes. Refer to reference design documentation and AN1130: Si3404/06x PoE-PD Controller Design Guide for further details.

| Symbol               | Parameter (Condition)                                                                                        | Min  | Тур  | Max  | Unit |

|----------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>PORT</sub>    | CT1 – CT2  or  SP1 – SP2                                                                                     | 2.7  | _    | 57   | V    |

| V <sub>HV_OP</sub>   | VNEG-VSS, VNEG-HSO, VPOS-<br>VSS, VPOS-VNEG                                                                  | 1.5  | _    | 57   | V    |

| $V_{LV_{OP}}$        | VPOS referred low voltage pins:<br>RFREQ, RDET, FBH                                                          | -5.5 | _    | 0    | V    |

| V <sub>LV_OP</sub>   | VSS referred low voltage pins: VDD,<br>FBL, EROUT, ASUP, nSLEEP, nT2P,<br>ASUP, WAKE, MODE, LED <sup>1</sup> | 0    | _    | 5.5  | V    |

| V <sub>ISNS_OP</sub> | VSS referred current sensing pins:<br>ISNS, SWISNS                                                           | -0.5 | _    | 0.5  | V    |

| V <sub>LV_OP</sub>   | VNEG referred low voltage pins:<br>RCL                                                                       | 0    | _    | 5.5  | V    |

| V <sub>MV_OP</sub>   | VSS referred medium voltage pins<br>SYNCL, EXTGD, EXTHSW                                                     | 0    | _    | 13   | V    |

| V <sub>MV_VT15</sub> | VSS referred medium voltage pin<br>VT15 <sup>2</sup>                                                         | 12   | 14.5 | 16.5 | V    |

| I <sub>RECT</sub>    | On chip rectifier current on CT1,<br>CT2, SP1, SP2—steady state <sup>3</sup>                                 | _    | _    | 176  | mA   |

| V <sub>RECT</sub>    | On chip rectifier voltage @ 200 mA,<br>2 diodes                                                              | _    | 1.8  | _    | V    |

| I <sub>RECT_PK</sub> | Peak rectifier current Max 75 ms 5%<br>Duty Cycle <sup>4</sup>                                               | _    | _    | 231  | mA   |

| I <sub>AVG</sub>     | Allowable continuous current on SWO, VSS, HSO, VNEG                                                          | _    | _    | 600  | mA   |

| I <sub>MAX</sub>     | Maximum current on HSO, VNEG,<br>VPOS Max 75 ms 5% Duty Cycle                                                | _    | _    | 683  | mA   |

## Table 4.2. Recommended Operating Conditions

Note:

1. For all digital inputs (MODE, NSLEEP, WAKE, ASUP) Voh low to high transition voltage max is 3.7 V; Vol high to low voltage min is 1.6 V.

2. V<sub>MV\_VT15</sub> is relevant for Si34061 and Si34062 only when an external auxiliary winding from the primary side of the transformer is being used to improve power conversion efficiency. This can be left undriven, in which case an internal regulator will be used.

3. For Class 3 and above operation, use external diode bridge rectifiers to bypass the internal input diode bridge rectifiers.

4. The IEEE 802.3at specification allows for higher peak current for transients.

## Table 4.3. Electrical Characteristics

Excluding detection and classification and unless otherwise noted,  $37 \text{ V} < \text{VPOS} - \text{VNEG} \le 57 \text{ V}$ ; junction temperature = -40 to +125 °C; typical specs are measured at 25 °C. All voltages are with respect to VSS unless otherwise noted.

| Symbol                 | Parameter (Condition)                                | Min   | Тур      | Max   | Unit |

|------------------------|------------------------------------------------------|-------|----------|-------|------|

| PoE PROTOCO            | DL                                                   |       | 1        |       |      |

| Detection              |                                                      |       |          |       |      |

|                        | Signature Range (at V <sub>PORT</sub> )              | 2.7   | _        | 10.1  | V    |

| V <sub>DET</sub>       | Signature Resistance (at V <sub>PORT</sub> )         | 23.75 | _        | 26.25 | kΩ   |

| Classification         |                                                      |       |          |       |      |

| V <sub>RESET</sub>     | Classification Reset (at V <sub>PORT</sub> )         | 0     |          | 2.81  | V    |

|                        | Classification ON threshold (at V <sub>PORT</sub> )  | _     | _        | 14.5  | V    |

| V <sub>CLASS</sub>     | Classification OFF threshold (at V <sub>PORT</sub> ) | 20.5  |          | _     | V    |

|                        | Class 0 (R <sub>CLASS</sub> > 681 Ω)                 | 0     | _        | 4     | mA   |

|                        | Class 1 (R <sub>CLASS</sub> = 140 Ω @ 1%)            | 9     | _        | 12    | mA   |

| I <sub>PortCLASS</sub> | Class 2 (R <sub>CLASS</sub> = 75 Ω @ 1%)             | 17    | _        | 20    | mA   |

|                        | Class 3 (R <sub>CLASS</sub> = 48.7 Ω @ 1%)           | 26    | _        | 30    | mA   |

|                        | Class 4 (R <sub>CLASS</sub> = 33.2 Ω @ 1 %)          | 36    | _        | 44    | mA   |

| Type 2 Classifi        | cation                                               |       | <u> </u> |       |      |

| V <sub>MARK</sub>      | Mark event voltage (at V <sub>PORT</sub> )           | 6.9   | _        | 10.1  | V    |

| I <sub>MARK</sub>      | Mark event current                                   | 0.25  | _        | 4     | mA   |

| Power On and           | UVLO                                                 |       |          |       |      |

| V <sub>UVLO_R</sub>    | Hotswap closed and converter on                      | 34    | 37       | 40    | V    |

| V <sub>UVLO_F</sub>    | Hotswap open and converter off                       | 30    | 32       | 34    | V    |

| V <sub>UVLO_HYST</sub> | O_HYST                                               |       | 4.5      | 6     | V    |

| Thermal Chara          | icteristics                                          |       |          |       |      |

| T <sub>SHD</sub>       | Thermal shutdown                                     | _     | 160      | _     | °C   |

| T <sub>HYST</sub>      | Thermal shutdown hysteresis                          | _     | 20       | _     | °C   |

| On-Chip Trans          | ient Voltage Suppression/Protection                  |       | 1        | 1     |      |

| V <sub>PROT</sub>      | TVS protection activation voltage (VPOS-<br>VNEG)    | 100   | _        | _     | V    |

| Hotswap Swite          | h                                                    |       |          |       |      |

| l <sub>inrush</sub>    | Inrush current                                       | 100   | 170      | 200   | mA   |

| IMAXHSSW               | Maximum continuous operating current                 | _     | _        | 600   | mA   |

| V <sub>HSSW_ON</sub>   | Switch ON voltage                                    | _     | 380      | _     | mV   |

| V <sub>HSSW_OFF</sub>  | Switch OFF voltage, HSSW goes to overload cycle      | _     | 3.5      | _     | V    |

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com

207028A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice • November 25, 2022 16

| Symbol                 | Parameter (Condition)                                                       | Min   | Тур  | Мах   | Unit |

|------------------------|-----------------------------------------------------------------------------|-------|------|-------|------|

| I <sub>OVL</sub>       | Switch current limit in OVERLOAD State                                      | _     | 10.5 | _     | mA   |

| I <sub>MPSth</sub>     | MPS signal request current level threshold                                  | 14    | 20   | 26    | mA   |

| I <sub>EXT_DRV</sub>   | External hotswap driver peak current on<br>EXTHSW pin                       | _     | _    | 10    | mA   |

| V <sub>EXT_DRV</sub>   | External hotswap driver voltage on EXTHSW pin                               | 9     | 11   | 13    | V    |

| T <sub>WAITHSSW</sub>  | Wait time in OVERLOAD and type 2 inrush                                     | 80    | 96   | 116   | ms   |

| R <sub>ONHSSW</sub>    | Internal hotswap drain-source resistance while<br>ON                        | 0.65  | 1.5  | 2.9   | Ω    |

| DC-DC                  |                                                                             |       |      |       |      |

| ISWOPEAK               | Peak current limit of internal FET (SWO pin)                                | 2.1   | _    | 2.7   | A    |

| V <sub>EXTGD</sub>     | External FET driver voltage (EXTGD pin)                                     | 9     | 11   | 13    | V    |

| I <sub>EXTGD</sub>     | External FET driver peak current (EXTGD pin)                                | _     | _    | 500   | mA   |

| F <sub>OSCINT</sub>    | Using internal Oscillator                                                   | 215   | 250  | 290   | kHz  |

| <b>F</b>               | Using external Oscillator,<br>RFREQ = 215 k $\Omega$                        | 75    | 95   | 115   | kHz  |

| FOSCEXT                | Using external Oscillator,<br>RFREQ = 39 k $\Omega$                         | 420   | 470  | 520   | kHz  |

| DUC                    | Output duty cycle of PWM                                                    | _     | _    | 75    | %    |

| V <sub>DCDCUVLO</sub>  | DCDC UVLO level (Minimum adapter voltage-<br>ASUP mode)                     | 10.75 | 11.3 | 11.85 | V    |

| V <sub>FBREF</sub>     | FBH (referenced to VPOS) and FBL (refer-<br>enced to VSS) reference voltage | 1.28  | 1.32 | 1.36  | V    |

| V <sub>EROUT</sub>     | Operating voltage range of error input                                      | 1     | _    | 4     | V    |

| T <sub>HICCUP</sub>    | Output short protection if EROUT is max                                     | _     | 1    | _     | ms   |

| V <sub>ISNS_OVC</sub>  | Overcurrent limit voltage on ISNS (ref. to VSS)                             | -305  | -270 | -255  | mV   |

| V <sub>ISNS_LC</sub>   | Low current limit voltage on ISNS (ref. to VSS)                             | -45   | -30  | -15   | mV   |

| V <sub>SWISNSMAX</sub> | External FET peak current sense                                             | _     | 240  | _     | mV   |

| T <sub>SOFTSTART</sub> | Startup time <sup>1</sup>                                                   | _     | 15   | _     | ms   |

| R <sub>ONDCDC</sub>    | Internal DCDC switching FET drain-source re-<br>sistance while ON           | _     | 0.9  | 1.2   | Ω    |

| Regulators             |                                                                             |       |      |       |      |

| VT15                   | Override internal regulator with transformer winding                        | 12.5  | _    | 16.5  | V    |

| VDD                    | 5 V regulated output                                                        | 4.9   | 5.2  | 5.5   | V    |

| VDD <sub>ILIM</sub>    | DC current limit of VDD                                                     | 9.7   | 11.2 | _     | mA   |

| C <sub>REG</sub>       | Filter capacitor on VDD and V11                                             | 82    | 100  | 220   | nF   |

| IMAXLED                | LED pin max current, reduces VDD <sub>ILIM</sub>                            | _     | 5    | _     | mA   |

| I <sub>MAXDO</sub>     | Digital output max current (NT2P), reduces<br>VDD <sub>ILIM</sub>           | 2     | 2.5  |       | mA   |

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com 207028A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice • November 25, 2022 17

## Si3406x Family Data Sheet • Electrical Specifications

|                                             | DC-DC max power internal FET<br>Total chip power<br>erating current (V <sub>PORT</sub> 57 V; 250 kHz) |   | 0.2<br>0.5<br>3 | 0.9 | W<br>W<br>mA |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|---|-----------------|-----|--------------|

| P <sub>MAX</sub><br>I <sub>PortOP</sub> Ope | Total chip power                                                                                      |   | 0.5             | _   | W            |

| I <sub>PortOP</sub> Ope                     |                                                                                                       |   |                 | 5   |              |

|                                             | erating current (V <sub>PORT</sub> 57 V; 250 kHz)                                                     | _ | 3               | 5   | mA           |

| Package Thermal Char                        |                                                                                                       |   |                 |     |              |

| •                                           | acteristics <sup>2</sup>                                                                              |   |                 |     |              |

| θ <sub>JA</sub>                             | QFN20                                                                                                 | _ | 44              | _   | C°/W         |

| θ <sub>JA</sub>                             | QFN24                                                                                                 | _ | 38.5            | _   | C°/W         |

## 5. Pin Descriptions

Table 5.1. Pin Descriptions

| '06<br>Pins | '061<br>Pins | '062<br>Pins | Name   | Ref  | Dir. | Vrange  | Description                                                                        |

|-------------|--------------|--------------|--------|------|------|---------|------------------------------------------------------------------------------------|

|             | 24           |              | SWISNS | VSS  | I    | 0–1     | External FET peak current sense resistor voltage input                             |

| 20          | 1            | 24           | ISNS   | VSS  | I    | -1–0    | Chip average current sense resistor input                                          |

| 1           |              | 1            | FBH    | VPOS | I    | 0–5.5   | High side (VPOS referred) dc-dc feedback (Buck converter)                          |

| 2           | 2            | 2            | EROUT  | VSS  | IO   | 0–5.5   | Error amplifier current output, compensation impedance input                       |

| 3           | 3            | 3            | FBL    | VSS  | I    | 0–5.5   | Low side (VSS referenced) dc-dc feedback (Flyback converter)                       |

| 4           | 4            | 4            | VDD    | VSS  | 0    | 0–5.5   | 5 V regulator output                                                               |

|             |              | 5            | LED    | VSS  | 0    | 0–5.5   | Output to drive sleep LED                                                          |

|             | 5            |              | EXTHSW | VNEG | 0    | 0–11    | External hotswap switch drive                                                      |

|             |              | 6            | WAKE   | VSS  | I    | 0–5.5   | Wakeup from sleep mode                                                             |

|             | 6            |              | ASUP   | VSS  | I    | 0–5.5   | AUX auxiliary adapter present                                                      |

| 5           | 7            | 7            | nSLEEP | VSS  | I    | 0–5.5   | Sleep, with pull-up, driven by open drain                                          |

| 6           | 8            | 8            | RDET   | VPOS | IO   | 0–100   | Detection resistor                                                                 |

| 7           | 9            | 9            | HSO    | VNEG | IO   | 0–100   | Hotswap switch output                                                              |

| 8           | 10           | 10           | RCL    | VNEG | IO   | 0–5.5   | Classification resistor                                                            |

| 9           | 11           | 11           | RFREQ  | VPOS | IO   | 0–5.5   | Oscillator frequency tuning resistor, tie to VPOS to select de-<br>fault frequency |

| 10          | 12           | 12           | SP2    | SP1  | I    | 0 - 100 | High-voltage supply input from spare pair; polarity-insensitive                    |

| 11          | 13           | 13           | SP1    | SP2  | I    | 0–100   | High-voltage supply input from spare pair; polarity-insensitive                    |

| 12          | 14           | 14           | VPOS   | —    | IO   | 0–100   | Rectified high-voltage supply positive rail                                        |

| 13          | 15           | 15           | CT2    | CT1  | I    | 0–100   | High-voltage supply input from main pair; polarity-insensitive                     |

| 14          | 16           | 16           | CT1    | CT2  | I    | 0 - 100 | High-voltage supply input from main pair; polarity-insensitive                     |

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com

207028A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice • November 25, 2022 19

Si3406x Family Data Sheet • Pin Descriptions

| '06<br>Pins | '061<br>Pins | '062<br>Pins | Name  | Ref | Dir. | Vrange | Description                                                                    |

|-------------|--------------|--------------|-------|-----|------|--------|--------------------------------------------------------------------------------|

| 15          | 17           | 17           | nT2P  | VSS | 0    | 0–5.5  | Type II classification was successful                                          |

|             | 18           | 18           | VT15  | VSS | I    | 0–16.5 | dc-dc transformer bias winding input                                           |

| 16          | 19           | 19           | SYNCL | VSS | 0    | 0–11   | Gate driver for synchronous rectification FET                                  |

| 17          | 20           | 20           | V11   | VSS | IO   | 0–11   | 11 V regulator output for filter cap.                                          |

|             | 21           |              | EXTGD | VSS | 0    | 0–11   | External FET gate drive.<br>When internal switching FET is in use, tie to VSS. |

|             |              | 21           | MODE  | VSS | I    | 0–5.5  | Controls MPS and LED switch behavior                                           |

| 18          | 22           | 22           | SWO   | VSS | 0    | 0–120  | Internal dc-dc switch output (NMOS drain)                                      |

| 19          | 23           | 23           | VSS   |     | IO   | 0      | dc-dc converter primary ground                                                 |

| ePad        | ePad         | ePad         | VNEG  |     | Ю    | 0      | Rectified high voltage supply ground                                           |

## 5.1 Detailed Pin Descriptions

| Pin Name | Detailed Description                                                                                                                                                                                                                                                      | Circuit Detail                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| SWISNS   | External dc-dc switching FET peak current sense resistor input. The max-<br>imum current of the switching FET should correspond to voltage V <sub>SWISN-</sub><br>SMAX·                                                                                                   | VDD<br>SWISNS<br>VSS<br>Rswisns                    |

| ISNS     | Average current sense resistor input. The resistor value will set the maxi-<br>mum allowed average current for the application. The overcurrent threshold<br>voltage V <sub>ISNS_OVC</sub> . Note that this pin voltage goes below VSS.                                   |                                                    |

| FBH      | High side dc-dc feedback input. Need to be tied to VPOS when not used.<br>See VFBREF.                                                                                                                                                                                     | VPOS<br>X<br>FBH<br>FBH                            |

| EROUT    | dc-dc converter error output; current out, voltage sense. Loop compensat-<br>ing impedance should be connected here.<br>I <sub>EROUT</sub> = (V <sub>FBH</sub> – V <sub>FBREF</sub> ) x 50 μA or<br>I <sub>EROUT</sub> = (V <sub>FBL</sub> – V <sub>FBREF</sub> ) x 50 μA | VDD<br>X EROUT<br>VDD<br>X EROUT<br>X VSS<br>X VSS |

| FBL      | Low side dc-dc feedback input. Need to be tied to VSS when not used. See $V_{FBREF}$                                                                                                                                                                                      | VDD<br>FBL<br>VSS                                  |

## Table 5.2. Circuit Equivalent and Description of Die Pads

| Pin Name | Detailed Description                                                                                                                                                                         | Circuit Detail                |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| VDD      | Regulated 5 V relative to VSS. There is no foldback characteristic, reaching VDD <sub>ILIM</sub> the output voltage decreases.<br>The regulator needs C <sub>REG</sub> external capacitance. |                               |

| LED      | LED driver output Max current is I <sub>MAXLED</sub>                                                                                                                                         |                               |

| WAKE     | Wake-up input pin for sleep mode, used only in Si34062.                                                                                                                                      | VDD<br>WAKE                   |

| ASUP     | Auxiliary supply adapter is present. Enables the operation of the dc-dc controller without PoE supply being present (used only in Si34061).                                                  | VDD<br>ASUP<br>VSS<br>VSS     |

| nSLEEP   | Sleep function input, see description in Sleep mode section.                                                                                                                                 | VDD<br>MINSLEEP<br>VSS<br>VSS |

| Pin Name             | Detailed Description                                                                                                                                                                                                                                                                          | Circuit Detail                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| RCL                  | Classification resistor input. For class 0 this pin can be left floating. Pin is active only at time of classification.                                                                                                                                                                       | RCL<br>T<br>VNEG<br>REXT           |

| RFREQ                | Used for adjusting the oscillator frequency.<br>The frequency is inversely proportional to the value of the connected resis-<br>tor.                                                                                                                                                          | VPOS                               |

| SP1, SP2<br>CT1, CT2 | Main power inputs, goes to diode bridge producing VPOS and VNEG. Can<br>be used up to Class 1 and Class 2. For higher power classes, external<br>bridge is required.                                                                                                                          | VPOS<br>CT1,CT2<br>SP1,SP2<br>VNEG |

| VPOS,<br>VNEG        | Main chip power output generated by the diode bridge. Note that VNEG (the ePad on the bottom of the chip) also provides thermal relief.                                                                                                                                                       | VPOS<br>CT1,CT2<br>SP1,SP2<br>VNEG |

| nT2P                 | Pin main function is digital output; it is low if Type 2 classification was successful and the application is allowed to draw class 4 current.<br>Output current is I <sub>MAXDO</sub> , but the load (e.g. an LED) should connected to VDD not VSS; otherwise, it can cause false operation. | VDD<br>VDD<br>A nT2P<br>VSS<br>VSS |

| Pin Name        | Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                      | Circuit Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSO             | Hotswap Switch Output. The switch shorts the VNEG and HSO pins, and includes several other functions. See hotswap switch section for details.                                                                                                                                                                                                                                                                                             | HSO<br>100V<br>VNEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| EXTGD,<br>SYNCL | EXTGD: Optional external switch driver of the dc-dc converter. When the internal switch is used this pin should be tied to VSS. This driver controls the external switch with 10 V logic level, relative to VSS.<br>SYNCL: Optional synchronous rectifier switch driver of the dc-dc converter. When not used the pin must be left floating. This driver controls the external synchronous switch with 10 V logic level, relative to VSS. | VCAS <sub>P</sub><br>VCAS <sub>P</sub><br>VCAS <sub>N</sub><br>VCAS <sub>N</sub> |

| EXTHSW          | Optional external hotswap switch driver output. The maximum current of the internal hotswap switch is I <sub>MAXHSSW</sub> , for higher currents an external NMOS FET should be used in parallel with the internal HSSW (VNEG-HSO). When EXTGD is not used the pin should be tied to VNEG. This driver controls the external switch with 10 V logic level, relative to VNEG.                                                              | 11V internal supply<br>46V<br>VCAS<br>46V<br>CAS<br>46V<br>46V<br>46V<br>46V<br>46V<br>46V<br>46V<br>46V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RDET            | The user has to tie the RDET resistor between this pin and VPOS. During detection, a high voltage switch pulls down RDET to VNEG. After detection, the reference block uses RDET as absolute chip current reference, forcing –750 mV relative to VPOS, creating 30 µA for the internal blocks.                                                                                                                                            | VPOS<br>100V<br>RDET<br>100V<br>VNEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Name     | Detailed Description                                                                                                                                                                                                                                                                                                                                                  | Circuit Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VT15,<br>V11 | VT15 is input for an optional 15 V supply generated by an auxiliary trans-<br>former bias winding. If the bias winding voltage is lower than VT15_MIN, the<br>internal 15 V coarse regulator will provide the current for the 11 V regulator.<br>The V11 pin is for filtering capacitor for the 11 V regulator. A capacitor of<br>value C <sub>REG</sub> is required. | ✓ VPOS<br>↓ VT15<br>↓ CT15<br>↓ CT1 |

| MODE         | MPS mode control, used in Si34062.                                                                                                                                                                                                                                                                                                                                    | VDD<br>MODE<br>VSS<br>VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SWO          | dc-dc converter switching transistor drain output, Vmax = 120 V.                                                                                                                                                                                                                                                                                                      | swo<br>Swo<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |