# **TFT DISPLAY SPECIFICATION**

WINSTAR Display Co.,Ltd. 華凌光電股份有限公司

WEB: <a href="https://www.winstar.com.tw">https://www.winstar.com.tw</a> E-mail: sales@winstar.com.tw

## **SPECIFICATION**

| CUSTOMER :                |                    | - |

|---------------------------|--------------------|---|

| MODULE NO.:               | WF35XSWACDNNO#     |   |

|                           |                    | - |

|                           |                    |   |

| APPROVED BY:              |                    |   |

| ( FOR CUSTOMER USE ONLY ) |                    |   |

|                           | PCB VERSION: DATA: |   |

| 葉虹蘭 | SALES BY | APPROVED BY | CHECKED BY | PREPARED BY |

|-----|----------|-------------|------------|-------------|

|     |          |             |            | 葉虹蘭         |

ISSUED DATE: 2023/07/12

TFT Display Inspection Specification: <a href="https://www.winstar.com.tw/technology/download.html">https://www.winstar.com.tw/technology/download.html</a>

Precaution in use of TFT module: <a href="https://www.winstar.com.tw/technology/download/declaration.html">https://www.winstar.com.tw/technology/download/declaration.html</a>

MODLE NO:

| REC     | ORDS OF REV | ISION               | DOC. FIRST ISSUE                |

|---------|-------------|---------------------|---------------------------------|

| VERSION | DATE        | REVISED<br>PAGE NO. | SUMMARY                         |

| 0       | 2021/07/30  |                     | First issue                     |

| A       | 2023/07/12  |                     | Remove Inspection Specification |

## **Contents**

- 1. Module Classification Information

- 2.Summary

- 3. General Specifications

- 4. Absolute Maximum Ratings

- 5. Electrical Characteristics

- 6.AC Characteristics

- 7. Communication Interface

- 8. Optical Characteristics

- 9.Interface

- 10.Block Diagram

- 11.Reliability

- 12.Contour Drawing

- 13.Other

## 1. Module Classification Information

S W C N 0 W F 35 X D N # 1 3 4 (5) 7 8 (11) (12) 13) 2 6 10

| ①   | Brand: WINSTA          | R DISPLAY     | COR                                       | PORAT    | ΓΙΟΝ  | 1     |        |                     |             |       |             |       |      |

|-----|------------------------|---------------|-------------------------------------------|----------|-------|-------|--------|---------------------|-------------|-------|-------------|-------|------|

| 2   | Display Type: F        | →TFT Type,    | J→Cι                                      | ıstom 7  | ΓFT   |       |        |                     |             |       |             |       |      |

| 3   | Display Size: 3.5" TFT |               |                                           |          |       |       |        |                     |             |       |             |       |      |

| 4   | Model serials no.      |               |                                           |          |       |       |        |                     |             |       |             |       |      |

| (5) | Backlight              | F→CCFL, V     | Vhite                                     |          |       |       | Т      | $\rightarrow$ L     | ED, White   | •     |             |       |      |

|     | Type:                  | S→LED, Hi     | LED, High Light White Z-Nichia LED, White |          |       |       |        |                     |             |       |             |       |      |

|     | LCD Polarize           | A→Transmi     | ssive,                                    | N.T, II  | PS T  | FT    | Q      | <b>2</b> →T         | ransmissiv  | ve, S | uper W.T,   | 12:00 | )    |

|     | Type/                  | C→Transmi     | ssive,                                    | N. T, 6  | :00   | ,     | R      | R→Ti                | ransmissiv  | e, S  | uper W.T,   | O-TF  | T    |

|     | Temperature            | F→Transmis    | -                                         | -        |       |       | V      | / <b>→</b> T        | ransmissiv  | ve, S | uper W.T,   | VA T  | FT   |

| 6   | range/ Gray            | I→Transmis    | sive, V                                   | W. T, 6: | :00   |       | V      | V→T                 | Transmissi  | ve, s | Super W.T,  | IPS ' | ΓFT  |

|     | Scale Inversion        | K→Transfle    | -                                         | -        |       |       | X      | <b>X</b> → <b>T</b> | ransmissiv  | ve, V | V.T, VA TF  | T     |      |

|     | Direction              | L→Transmis    | ssive,                                    | W.T,12   | 2:00  |       | Y      | / <b>→</b> T        | ransmissiv  | ve, V | V.T, IPS TI | T     |      |

|     |                        | N→Transmi     | ssive,                                    | Super    | W.T.  | 6:0   |        |                     |             |       | V.T, O-TFT  |       |      |

|     | A: TFT LCD             |               |                                           |          |       | 4     |        | . \                 |             |       | L BOAR      | D     |      |

|     | B: TFT+SCREV           |               |                                           |          |       | D     |        |                     | FT+ SCR     |       |             |       |      |

| 7   | C: TFT+ SCRE           |               |                                           |          | \ '   | ~     |        |                     | FT+D/V      |       |             |       |      |

|     | D: TFT+ SCREW          |               |                                           |          |       |       |        |                     |             |       |             | /V B  | OARD |

|     | E: TFT+ SCRE           | W HOLES +F    | POWE                                      | R BO     | DAR   | D     | J      | : TF                | FT+POWE     | ER E  | BD          |       |      |

|     | Resolution:            |               |                                           |          |       |       |        |                     |             | _     |             |       |      |

|     | A 128160 B             |               |                                           | 20240    | D     |       | 0234   | Е                   | 480272      | F     | 640480      |       |      |

| 8   | G 800480 H             |               |                                           | 20480    | J     |       | 0320   | K                   | 800600      | L     | 240400      |       |      |

|     | M 1024768 N            |               | _                                         | 80800    | Q     |       | 0800   | R                   | 640320      | S     | 480128      |       |      |

|     | T 800320 U             | 8001280       | V 17                                      | 76220    | W     |       | 30398  | + -                 | 1024250     | Y     | 1920720     |       |      |

|     | Z 800200 2             |               |                                           | 01280    | 4     | 192   | 01200  | 5                   | 1366768     | 6     | 1280320     |       |      |

| 9   | D: Digital L:          | LVDS M:N      | MIPI                                      |          |       |       |        |                     |             |       |             |       |      |

|     | Interface:             |               | _                                         | _        |       |       |        |                     |             |       | T           |       |      |

| 10  | N Without co           | ntrol board   | A                                         | 8Bit     |       | В     |        | 16E                 | Bit         | Н     | HDMI        |       |      |

|     | I I2C Interfa          | ce            | R                                         | RS23     | 2     | S     | SP     | I Inte              | erface      | U     | USB         |       |      |

|     | TS:                    |               |                                           |          |       |       |        |                     |             |       |             |       |      |

|     | N Without TS           |               | T                                         | Resist   | ive t | oucl  |        |                     |             |       | touch pane  |       |      |

| 11) | G Capacitive to        | ouch panel (G | G-G)                                      |          |       | С     | 1 Ca   | apac                | itive touch | par   | nel (G-F-F) | +OC   | A    |

|     | C2 Capacitive to       |               |                                           |          |       | G     | 1 Ca   | apac                | itive touch | n par | nel (G-G)+  | OCA   |      |

|     | G2 Capacitive to       | ouch panel (G | G-G)+C                                    | OCR      |       | E     | B C    | TP+0                | GG+USB      |       |             |       |      |

| 12  | Version: X:Ras         | pberry pi     |                                           |          |       |       |        |                     |             |       |             |       |      |

| 13  | Special Code           | #:Fit in w    | ith RC                                    | HS dir   | ecti  | ve re | gulati | ons                 |             |       |             |       |      |

|     |                        |               |                                           |          |       |       |        |                     |             |       |             |       |      |

## 2.Summary

TFT 3.5" is a IPS transmissive type color active matrix TFT liquid crystal display that use amorphous silicon TFT as switching devices. This module is a composed of a TFT\_LCD module, It is usually designed for industrial application and this module follows RoHs.

## **3.General Specifications**

| Item             | Dimension                         | Unit |

|------------------|-----------------------------------|------|

| Size             | 3.5                               | inch |

| Dot Matrix       | 320 x RGBx240(TFT)                | dots |

| Module dimension | 76.84(W) x 63.84(H) x 3.27(D)     | mm   |

| Active area      | 70.08 x 52.56                     | mm   |

| Dot pitch        | 0.073 x 0.219                     | mm   |

| LCD type         | TFT, normally black, Transmissive |      |

| View Direction   | Wide View                         |      |

| Driver IC        | ST7272A or equivalent             |      |

| Interface        | 24-bit RGB                        |      |

| Aspect Ratio     | 4:3                               |      |

| Backlight Type   | LED,Normally White                |      |

| With /Without TP | Without TP                        |      |

| Surface          | Glare                             |      |

<sup>\*</sup>Color tone slight changed by temperature and driving voltage.

## **4.Absolute Maximum Ratings**

| Item                  | Symbol | Min | Тур | Max | Unit |

|-----------------------|--------|-----|-----|-----|------|

| Operating Temperature | TOP    | -30 | _   | +85 | °C   |

| Storage Temperature   | TST    | -40 | _   | +85 | °C   |

Note: Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above

1. Temp.  $60^{\circ}\text{C}$ , 90% RH MAX. Temp.  $>60^{\circ}\text{C}$ , Absolute humidity shall be less than 90% RH at  $60^{\circ}\text{C}$

## **5.Electrical Characteristics**

#### 5.1. Operating conditions:

| Item                   | Symbol | Min | Тур | Max | Unit | Remark |

|------------------------|--------|-----|-----|-----|------|--------|

| Supply Voltage For LCM | VCC    | 3.0 | 3.3 | 3.6 | V    |        |

| Supply Current For LCM | ICC    | _   | 20  | 30  | mA   | Note 1 |

Note 1 : This value is test for VCC =3.3V , Ta=25  $^{\circ}$ C only

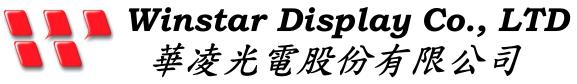

#### 5.2. LED driving conditions

| Parameter         | Symbol | Min. | Тур.   | Max. | Unit | Remark     |

|-------------------|--------|------|--------|------|------|------------|

| LED current       |        | -    | 40     | - (  | mA   |            |

| Power Consumption |        | 540  | 600    | 660  | mW   |            |

| LED voltage       | LED+   | 13.5 | 15     | 16.5 | V    | Note 1     |

| LED Life Time     |        | -    | 50,000 |      | Hr   | Note 2,3,4 |

Note 1 : There are 1 Groups LED

Note 2 : Ta = 25 °C

Note 3: Brightness to be decreased to 50% of the initial value

Note 4: The single LED lamp case

## **6.AC Characteristics**

#### 6.1. System Operation AC Characteristics

PVDD=VDDI= 3.3V, AGND= 0V, TA=25°C, Bare Chip

| ltem                         | Symbol | Min. | Тур.     | Max. | Unit | Conditions                                               |

|------------------------------|--------|------|----------|------|------|----------------------------------------------------------|

| VDD Power Source Slew Time   | TPOR   | -    | -        | 20   | ms   | From 0V to 99% VDD                                       |

| GRB Pulse Width              | tRSTW  | 10   | 50       | - 20 | us   | R=10Kohm, C=1uF                                          |

| SD Output Stable Time        | Tst    |      | <u>=</u> | 12   | us   | Output settled within<br>+20mV Loading =<br>6.8k+28.2pF. |

| GD Output Rise and Fall Time | Tgst   | _    | ū        | 6    | us   | Output settled (5%~95%),<br>Loading = 4.7k+29.8pF        |

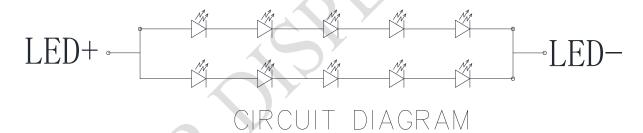

#### 6.2. System Bus Timing for I2C Interface

PVDD=VDD=VDDI= 3.3V, AGND= 0V, TA=25°C, Bare Chip

| ltem                                         | Symbol  | Min.     | Тур.            | Max.                     | Unit | Conditions |

|----------------------------------------------|---------|----------|-----------------|--------------------------|------|------------|

| SCL Clock Frequency                          | FSCL    | -        |                 | 400                      | KHz  |            |

| SCL Clock Low Period                         | TLOW    | 1300     | 2               | 31113<br>31 <u>11</u> 31 | ns   |            |

| SCL Clock High Period                        | THIGH   | 600      | ie.             | (H)                      | ns   |            |

| Signal Rise Time                             | Tr      | 20+0.1Cb | 5               | 300                      | ns   |            |

| Signal Fall Time                             | Tf      | 20+0.1Cb | 旨               | 300                      | ns   |            |

| Start Condition Setup Time                   | TSU;STA | 600      | \$ <del>7</del> | (15)                     | ns   |            |

| Start Condition Hold Time                    | THD;STA | 600      | 12              | (12)                     | ns   |            |

| Data Setup Time                              | TSU;DAT | 100      | -               | 1871                     | ns   |            |

| Data Hold Time                               | THD;DAT | 0        | 2               | 900                      | ns   |            |

| Setup Time for STOP Condition                | TSU;STO | 600      | 14              | (S#2)                    | ns   |            |

| Bus Free Time Between a STOP and START       | TBUF    | 100      | 12              | (2)                      | ns   |            |

| Capacitive load represented by each bus line |         | Cb       |                 | 400                      | pF   |            |

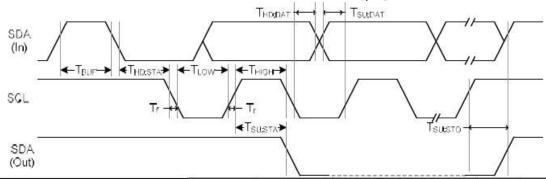

**6.3. System Bus Timing for 3-Wire SPI Interface** PVDD=VDD=VDDI= 3.3V, AGND= 0V, TA=25°C, Bare Chip

| Item                         | Symbol | Min. | Тур. | Max.           | Unit | Conditions |

|------------------------------|--------|------|------|----------------|------|------------|

| CS Input Setup Time          | Ts0    | 50   |      |                | ns   |            |

| Serial Data Input Setup Time | Ts1    | 50   | ¥    | 6 <b>4</b> 8   | ns   |            |

| CS Input Hold Time           | Th0    | 50   |      |                | ns   |            |

| Serial Data Input Hold Time  | Th1    | 50   | 9    | 528            | ns   |            |

| SCL Write Pulse High Width   | Twh1   | 50   | -    | 2000           | ns   |            |

| SCL Write Pulse Low Width    | Twl1   | 50   | 2    | 2000           | ns   |            |

| SCL Read Pulse High Width    | Trh1   | 300  |      | 2000           | ns   |            |

| SCL Read Pulse Low Width     | Trl1   | 300  |      | 2000           | ns   |            |

| CS Pulse High Width          | Tw2    | 400  | =    | \$ <b>=</b> \$ | ns   |            |

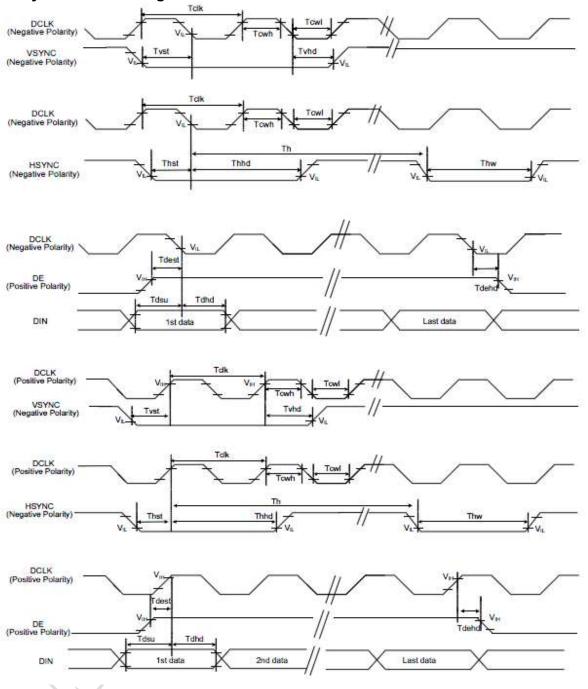

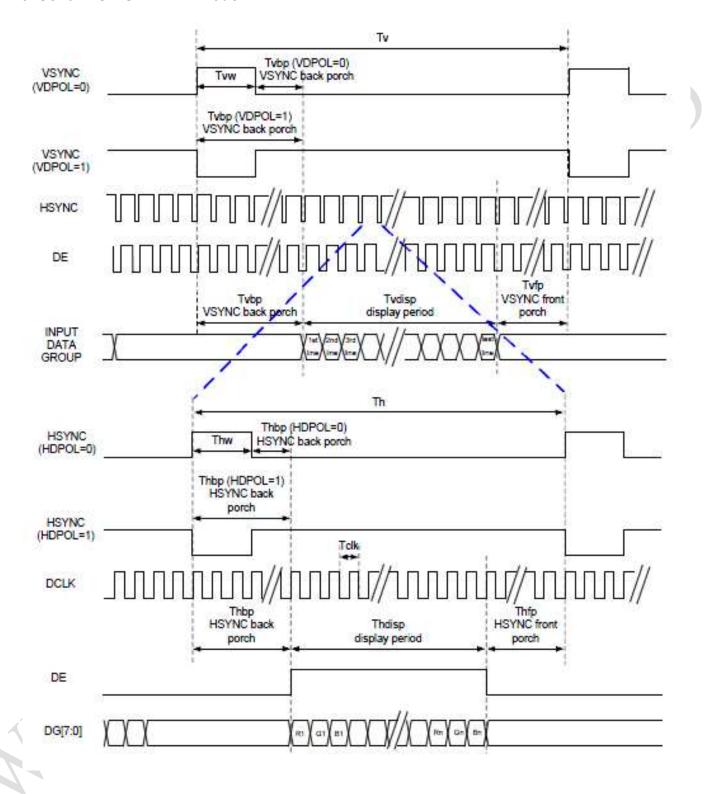

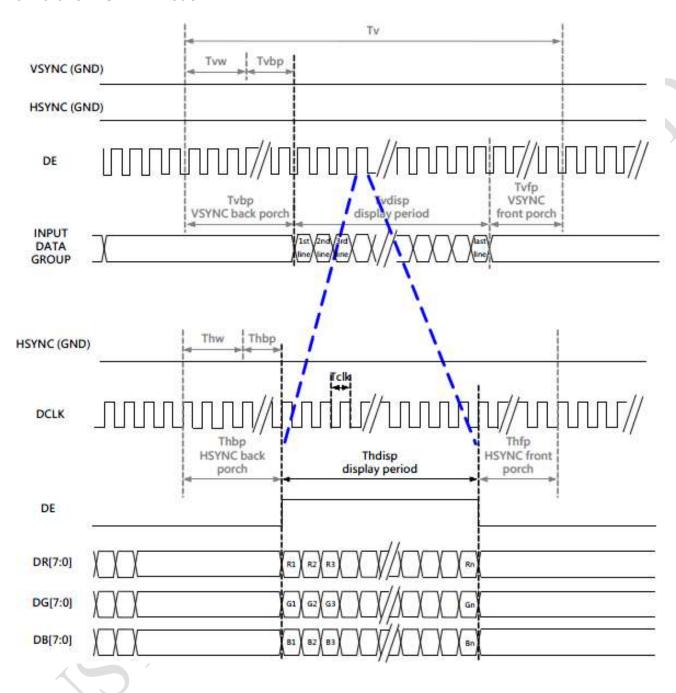

## 6.4. System Bus Timing for RGB Interface

| Item             | Symbol | Min. | Тур. | Max. | Unit | Conditions |

|------------------|--------|------|------|------|------|------------|

| CLK Pulse Duty   | Tclk   | 40   | 50   | 60   | %    |            |

| HSYNC Width      | Thw    | 2    | 100  | 2    | DCLK |            |

| VSYNC Setup Time | Tvst   | 12   | -    | 2    | ns   |            |

| VSYNC Hold Time  | Tvhd   | 12   | -    | -    | ns   |            |

| HSYNC Setup Time | Thst   | 12   | =    | . #  | ns   |            |

| HSYNC Hold Time  | Thhd   | 12   | -    |      | ns   |            |

| Data Setup Time  | Tdsu   | 12   | -    |      | ns   |            |

| Data Hold Time   | Tdhd   | 12   | 8    | · 20 | ns   |            |

| DE Setup Time    | Tdest  | 12   |      | 2    | ns   |            |

| DE Hold Time     | Tdehd  | 12   | 5    | 2    | ns   |            |

|                  |        |      |      | •    |      |            |

## 7. Communication Interface

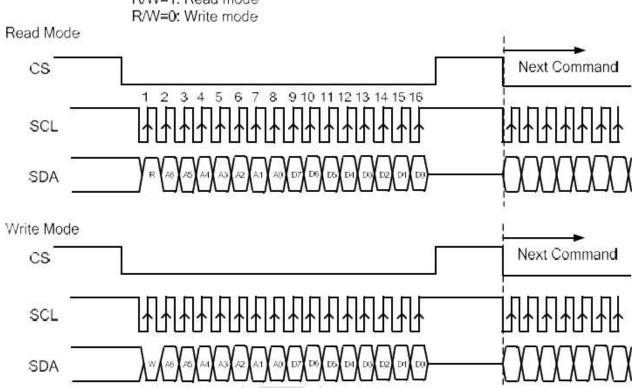

#### 7.1. 3-wire Serial Interface

R/W: Read/Write mode control bit.

R/W=1: Read mode R/W=0: Write mode

- a. Each serial command consists of 16 bits of data which is loaded one bit a time at the rising edge of serial clock SCL.

- b. Command loading operation starts from the falling edge of CS and is completed at the next rising edge of CS.

- c. The serial control block is operational after power on reset, but commands are established by the VSYNC signal. If command is transferred multiple times for the same register, the last command before the VSYNC signal is valid.

- d. If less than 16 bits of SCL are input while CS is low, the transferred data is ignored.

- e. If 16 bits or more of SCL are input while CS is low, the previous 16 bits of transferred data before then rising edge of CS pulse are valid data.

- f. Serial block operates with the SCL clock

- g. Serial data can be accepted in the power save mode.

- h. After power on reset or GRB reset, it is required 100ms delay to begin SPI communication.

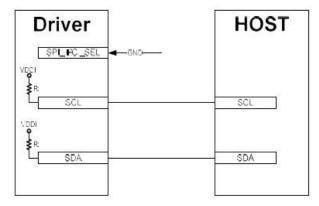

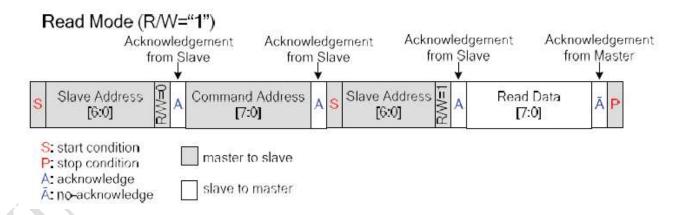

#### 7.2. I2C Interface

The I2C Interface is bi-directional two-line communication between different ICs or modules. The two lines are a Serial Data line (SDA) and a Serial Clock line (SCL). Both lines have built-in pull up resistor which drives SDA and SCL to high when the bus is not busy. Data transfer can be initiated only when the bus is not busy.

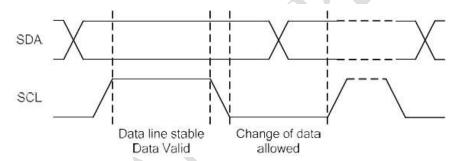

#### 1. Bit Transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse because changes of SDA line at this time will be interpreted as START or STOP. Bit transfer is illustrated as follows.

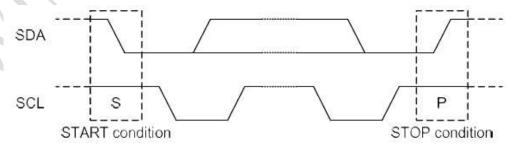

#### 2. START and STOP Conditions

Both SDA and SCL lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of SDA, while SCL is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of SDA while SCL is HIGH is defined as the STOP condition (P). The START and STOP conditions are illustrated as follows.

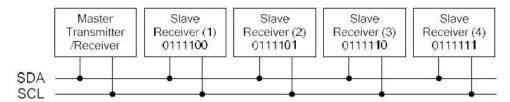

#### 3. System Configuration

The system configuration is illustrated above and some word-definitions are explained below:

- a. Transmitter: the device which sends the data to the bus.

- b. Receiver: the device which receives the data from the bus.

- c. Master: the device which initiates a transfer generates clock signals and terminates a transfer.

- d. Slave: the device which is addressed by a master.

- e. Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message.

- f. Arbitration: the procedure to ensure that, if more than one master tries to control the bus simultaneously, only one is allowed to do so and the message is not corrupted.

- g. Synchronization: procedure to synchronize the clock signals of two or more devices.

#### 4.Acknowledgment

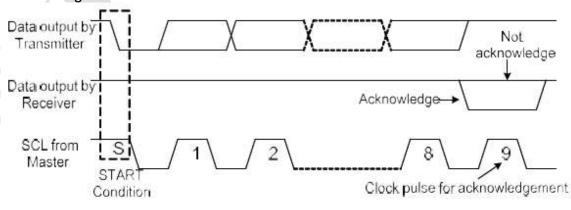

Each byte of eight bits is followed by an acknowledge-bit. The acknowledge-bit is a HIGH signal put on SDA by the transmitter during the time when the master generates an extra acknowledge-related clock pulse. A slave receiver which is addressed must generate an acknowledge-bit after the reception of each byte. A master receiver must also generate an acknowledge-bit after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge-clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledgerelated clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end-of-data to the slave transmitter by not generating an acknowledge-bit on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STOP condition. Acknowledgement on the I2C Interface is illustrated as follows.

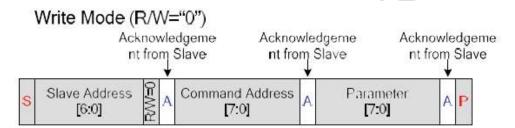

#### 5. I2C Interface Protocol

The driver supports command/data write to addressed slaves on the bus. Before any data is transmitted on the I2C Interface, the device which should respond is addressed first. The default slave address is 0111100b and the three times I2C address could be OTP programing.

The sequence is initiated with a START condition (S) from the I2C Interface master, which is followed by the slave address. All slaves with the corresponding address acknowledge in parallel, all the others will ignore the I2C Interface transfer. After acknowledgement, one or more command or data words are followed and define the status of the addressed slaves.

Only the addressed slave makes the acknowledgement after each byte. At the end of the transmission the bus master issues a STOP condition (P). If no acknowledge is generated by the master after a byte, the driver stops transferring data to the master. The register write/read transference sequence are described as follows.

#### 7.3. RGB Interface

## 1.Pin Assignment for RGB Interface

| Pin                      |           | F     | Parallel RG | В     | Serial RGB |       |       |  |

|--------------------------|-----------|-------|-------------|-------|------------|-------|-------|--|

|                          |           | 888   | 666         | 565   | 888        | 666   | 565   |  |

| 11011110                 | SYNC Mode | VSYNC | VSYNC       | VSYNC | VSYNC      | VSYNC | VSYNC |  |

| VSYNC                    | DE Mode   | х     | х           | X     | х          | х     | х     |  |

| HOVANO                   | SYNC Mode | HSYNC | HSYNC       | HSYNC | HSYNC      | HSYNC | HSYNC |  |

| HSYNC                    | DE Mode   | x     | x           | X     | x          | x     | X     |  |

| DE.                      | SYNC Mode | х     | x           | x     | X          | X     | x     |  |

| DE                       | DE Mode   | DE    | DE          | DE    | DE         | DE    | DE    |  |

|                          | CLK       | CLK   | CLK         | CLK   | CLK        | CLK   | CLK   |  |

|                          | DR0       | R0    | X           | X     | X          | X     | X     |  |

|                          | DR1       | R1    | x           | X     | x          | X     | X     |  |

|                          | DR2       | R2    | R0          | X     | X          | X     | x     |  |

|                          | DR3       | R3    | R1          | R0    | x          | x     | x     |  |

|                          | DR4       | R4    | R2          | R1    | х          | X     | x     |  |

|                          | DR5       | R5    | R3          | R2    | X          | X     | X     |  |

|                          | DR6       | R6    | R4          | R3    | X          | X     | X     |  |

|                          | DR7       | R7    | R5          | R4    | x          | X     | x     |  |

|                          | DG0       | G0    | х           | х     | D0         | x     | x     |  |

|                          | DG1       | G1    | x           | X     | D1         | x     | x     |  |

|                          | DG2       | G2    | G0          | G0    | D2         | D0    | D0    |  |

|                          | DG3       | G3    | G1          | G1    | D3         | D1    | D1    |  |

|                          | DG4       | G4    | G2          | G2    | D4         | D2    | D2    |  |

|                          | DG5       | G5    | G3          | G3    | D5         | D3    | D3    |  |

|                          | DG6       | G6    | G4          | G4    | D6         | D4    | D4    |  |

|                          | DG7       | G7    | G5          | G5    | D7         | D5    | D5    |  |

|                          | DB0       | В0    | х           | x     | х          | x     | x     |  |

|                          | DB1       | B1    | x           | x     | x          | X     | X     |  |

| DB2<br>DB3<br>DB4<br>DB5 |           | B2    | В0          | X     | x          | X     | X     |  |

|                          |           | В3    | B1          | В0    | x          | x     | x     |  |

|                          |           | B4    | B2          | B1    | x          | x     | x     |  |

|                          |           | B5    | B3          | B2    | X          | ×     | x     |  |

|                          | DB6       | B6    | B4          | B3    | x          | x     | X     |  |

|                          | DB7       | B7    | B5          | B4    | X          | X     | X     |  |

| RGB Mode Selection Table | DCLK  | HSYNC | VSYNC | DE    |

|--------------------------|-------|-------|-------|-------|

| SYNC - DE Mode           | Input | Input | Input | Input |

| SYNC Mode                | Input | Input | Input | GND   |

| DE Mode                  | Input | GND   | GND   | Input |

Note: "Input" means these signals are driven by host side

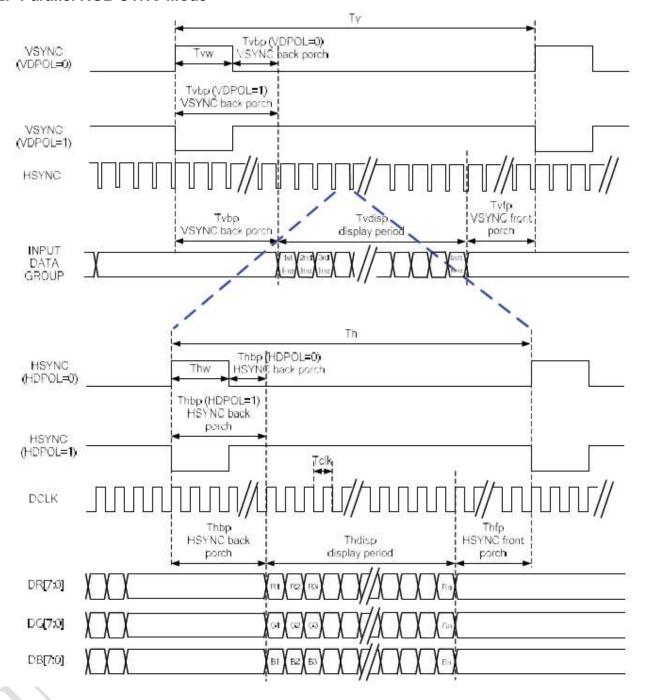

#### 2. Parallel RGB SYNC Mode

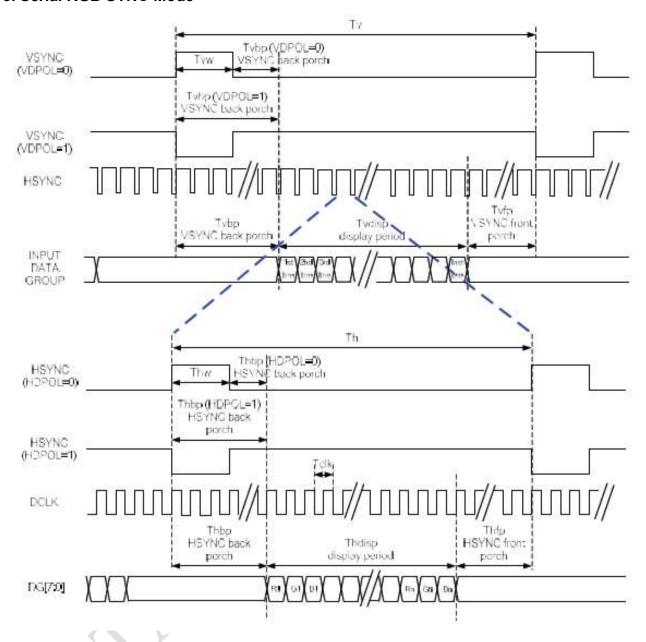

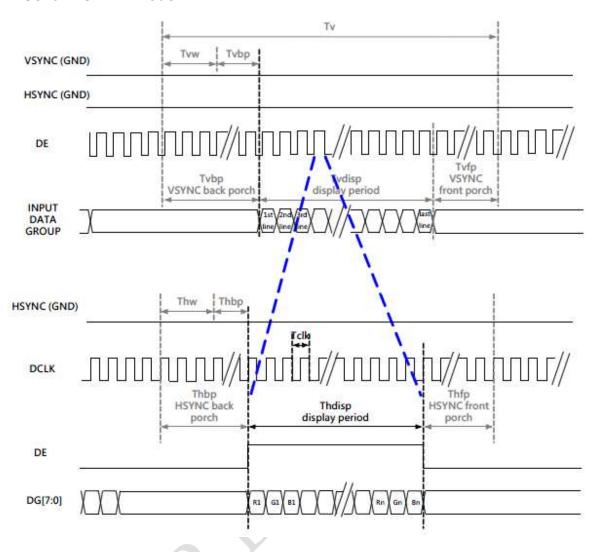

#### 3. Serial RGB SYNC Mode

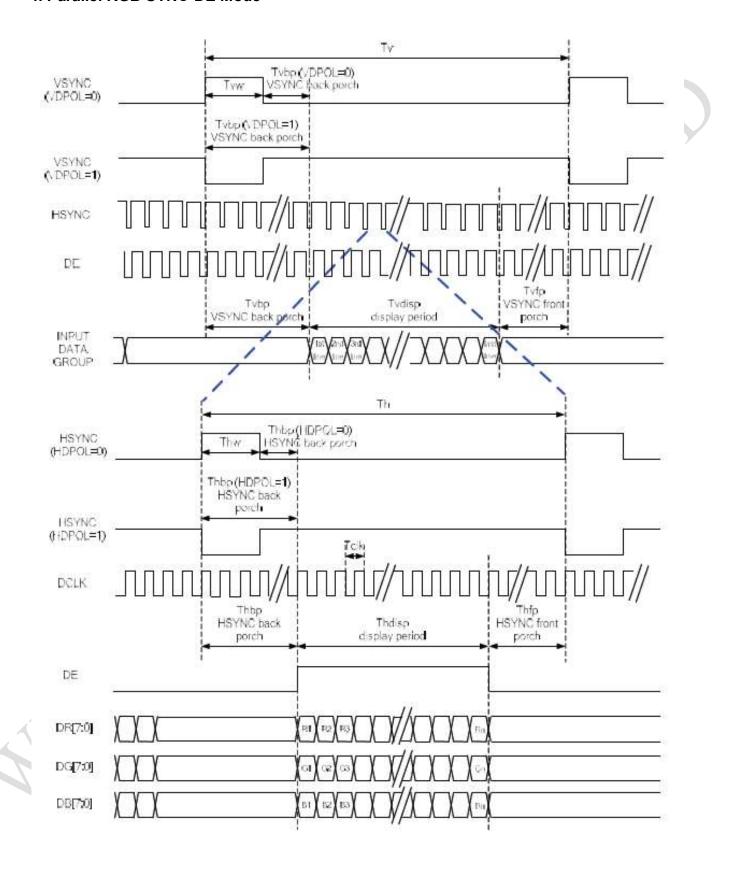

#### 4. Parallel RGB SYNC-DE Mode

#### 5. Serial RGB SYNC-DE Mode

#### 6. Parallel RGB DE Mode

#### 7. Serial RGB DE Mode

### 8. Parallel RGB Input Timing Table

Parallel 24-bit RGB Input Timing (PVDD=VDDI= 3.3V, AGND= 0V, TA=25 C)

|       |                | Parallel 2 | 24-bit R | GB Inpu | t Timing | Table Table |                                                                               |

|-------|----------------|------------|----------|---------|----------|-------------|-------------------------------------------------------------------------------|

|       | Item           | Symbol     | Min.     | Тур.    | Max.     | Unit        | Note                                                                          |

| DCL   | K Frequency    | Fclk       | 5        | 6       | 8        | MHz         |                                                                               |

| DC    | LK Period      | Tclk       | 125      | 167     | 200      | ns          |                                                                               |

| 11000 | Period Time    | Th         | 325      | 371     | 438      | DCLK        |                                                                               |

|       | Display Period | Thdisp     |          | 320     |          | DCLK        |                                                                               |

| HSYNC | Back Porch     | Thbp       | 3        | 43      | 43       | DCLK        | SYNC mode back porch control by H_BLANKING[7:0] setting Thbp= H_BLANKING[7:0] |

|       | Front Porch    | Thfp       | 2        | 8       | 75       | DCLK        |                                                                               |

|       | Pulse Width    | Thw        | 2        | 4       | 43       | DCLK        | č.                                                                            |

|       | Period Time    | Tv         | 244      | 260     | 289      | HSYNC       |                                                                               |

|       | Display Period | Tvdisp     |          | 240     |          | HSYNC       |                                                                               |

| VSYNC | Back Porch     | Tvbp       | 2        | 12      | 12       | HSYNC       | SYNC mode back porch control by V_BLANKING[7:0] setting Tvbp= V_BLANKING[7:0] |

|       | Front Porch    | Tvfp       | 2        | 8       | 37       | HSYNC       |                                                                               |

|       | Pulse Width    | Tvw        | 2        | 4       | 12       | HSYNC       |                                                                               |

Note: It is necessary to keep Tvbp =12 and Thbp =43 in sync mode. DE mode is unnecessary to keep it.

### 9. Serial RGB Input Timing Table

Serial 8-bit RGB Input Timing (PVDD=VDDI= 3.3V, AGND= 0V, TA=25 C)

|       |                | Serial 8 | bit RGE | Input 1 | iming 1 | Table |                                                                                    |

|-------|----------------|----------|---------|---------|---------|-------|------------------------------------------------------------------------------------|

|       | Item           | Symbol   | Min.    | Тур.    | Max.    | Unit  | Remark                                                                             |

| DCL   | Frequency      | Fclk     | 15      | 18      | 21      | MHz   |                                                                                    |

| DC    | LK Period      | Tclk     | 47      | 55      | 66      | ns    |                                                                                    |

|       | Period Time    | Th       | 965     | 1011    | 1078    | DCLK  |                                                                                    |

|       | Display Period | Thdisp   |         | 960     |         | DCLK  |                                                                                    |

| HSYNC | Back Porch     | Thbp     | 3       | 43      | 43      | DCLK  | SYNC mode back porch contro<br>by H_BLANKING[7:0] setting<br>Thbp= H_BLANKING[7:0] |

|       | Front Porch    | Thfp     | 2       | 8       | 75      | DCLK  |                                                                                    |

|       | Pulse Width    | Thw      | 2       | 4       | 43      | DCLK  |                                                                                    |

|       | Period Time    | Tv       | 244     | 260     | 289     | HSYNC |                                                                                    |

|       | Display Period | Tvdisp   |         | 240     |         | HSYNC |                                                                                    |

| VSYNC | Back Porch     | Tvbp     | 2       | 12      | 12      | HSYNC | SYNC mode back porch control by V_BLANKING[7:0] setting Tvbp= V_BLANKING[7:0]      |

|       | Front Porch    | Tvfp     | 2       | 8       | 37      | HSYNC |                                                                                    |

|       | Pulse Width    | Tvw      | 2       | 4       | 12      | HSYNC |                                                                                    |

Note: It is necessary to keep Tvbp =12 and Thbp =43 in sync mode. DE mode is unnecessary to keep it.

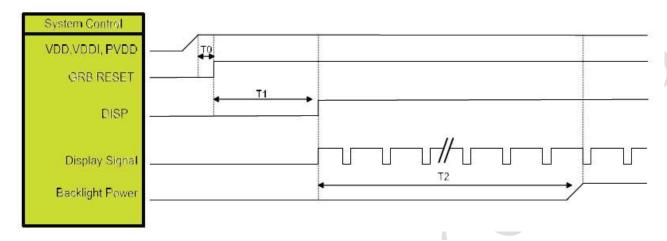

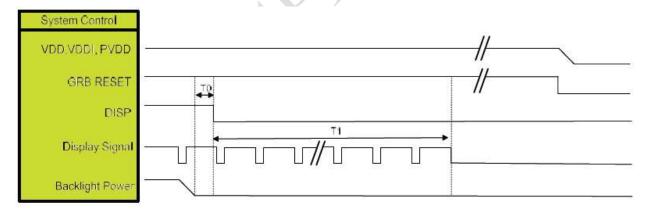

#### 7.4. POWER ON/OFF SEQUENCE

#### 1. Power On Sequence

| Symbol | Description                                 | Min. Time | Unit |

|--------|---------------------------------------------|-----------|------|

| T0     | System power stability to GRB RESET signal  | 0         | ms   |

| T1     | GRB RESET= "High" to DISP="High"            | 10        | ms   |

| T2     | Display Signal output to Backlight Power on | 250       | ms   |

Note: Display signal: DCLK; VSYNC; HSYNC; DE; DR[7:0]; DG[7:0]; DB[7:0]

### 2. Power Off Sequence

| Symbol | Description                                          | Min. Time | Unit |

|--------|------------------------------------------------------|-----------|------|

| T0     | Backlight Power off to DISP="Low"                    | 5         | ms   |

| T1     | DISP="Low" to IC internal voltage discharge complete | 80        | ms   |

Note: Display signal: DCLK; VSYNC; HSYNC; DE; DR[7:0]; DG[7:0]; DB[7:0]

## **8.Optical Characteristics**

| Item               |         | Symbol | Condition.                 | Min  | Тур. | Max. | Unit | Remark            |

|--------------------|---------|--------|----------------------------|------|------|------|------|-------------------|

| Response tim       | е       | Tr+ Tf | θ=0° \ Ф=0°                | -    | 30   | 40   | ms   | Note 3            |

| Contrast ratio     | )       | CR     | At optimized viewing angle | 640  | 800  | -    | -    | Note 4            |

| Color Chromoticity | \\/bito | Wx     | θ=0° \ Φ=0                 | 0.26 | 0.31 | 0.36 | - <  | Note              |

| Color Chromaticity | White   | Wy     | $\theta = 0  \Phi = 0$     | 0.30 | 0.35 | 0.40 | 4    | 2,6,7             |

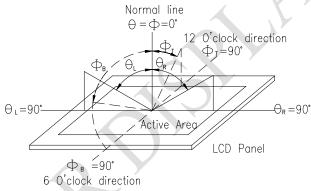

|                    | Hor.    | ΘR     | CR 10                      | 70   | 80   | -    | Deg. | Note 1            |

| Viewing angle      | ПОІ.    | ΘL     |                            | 70   | 80   | -    |      |                   |

| Viewing angle      | Ver.    | ΦТ     |                            | 70   | 80   | -    |      |                   |

|                    |         | ФВ     |                            | 70   | 80   |      |      |                   |

| Brightness         |         | -      | -                          | 1000 | L    | ) -  | cd/m | Center of display |

| Uniformity         |         | (U)    | -                          | 75   | -    | -    | %    | Note 5            |

Ta=25±2°C, IL=40mA

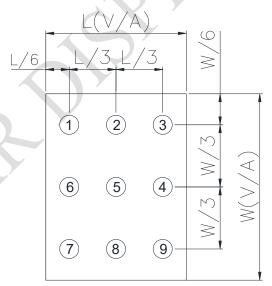

Note 1: Definition of viewing angle range

Fig. 8.1. Definition of viewing angle

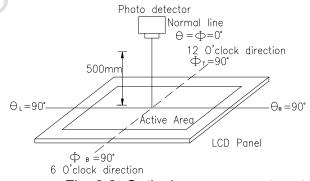

Note 2: Test equipment setup:

After stabilizing and leaving the panel alone at a driven temperature for 10 minutes, the measurement should be executed. Measurement should be executed in a stable, windless, and dark room. Optical specifications are measured by Topcon BM-7orBM-5 luminance meter 1.0° field of view at a distance of 50cm and normal direction.

Fig. 8.2. Optical measurement system setup

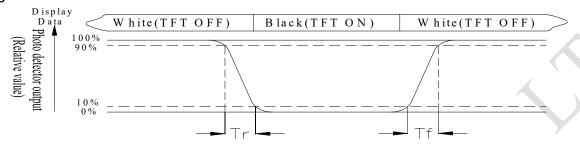

#### Note 3: Definition of Response time:

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time, Tr, is the time between photo detector output intensity changed from 90%to 10%. And fall time, Tf, is the time between photo detector output intensity changed from 10%to 90%

Note 4: Definition of contrast ratio:

The contrast ratio is defined as the following expression.

#### Note 5: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (reference the picture in below). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax x100%

L = Active area length

W = Active area width

Fig8.3. Definition of uniformity

Note 6: Definition of color chromaticity (CIE 1931) Color coordinates measured at the center point of LCD

Note 7: Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

# 9.Interface 9.1. LCM PIN Definition

| Pin | Symbol          | Function                        | Remark   |

|-----|-----------------|---------------------------------|----------|

| 1   | LED-            | Power for LED backlight cathode |          |

| 2   | LED-            | Power for LED backlight cathode |          |

| 3   | LED+            | Power for LED backlight anode   |          |

| 4   | LED+            | Power for LED backlight anode   | \ \ \ '  |

| 5   | NC(YU)          | No connect                      | <b>Y</b> |

| 6   | NC(XL)          | No connect                      |          |

| 7   | NC(SPI_IIC_SEL) | No connect                      |          |

| 8   | /RESET          | Hardware reset                  |          |

| 9   | NC(CS)          | No connect                      |          |

| 10  | NC(SDA)         | No connect                      |          |

| 11  | NC(SCL)         | No connect                      |          |

| 12  | В0              | Data bus                        |          |

| 13  | B1              | Data bus                        |          |

| 14  | B2              | Data bus                        |          |

| 15  | В3              | Data bus                        |          |

| 16  | B4              | Data bus                        |          |

| 17  | B5              | Data bus                        |          |

| 18  | B6              | Data bus                        |          |

| 19  | В7              | Data bus                        |          |

| 20  | G0              | Data bus                        |          |

| 21  | G1              | Data bus                        |          |

| 22  | G2              | Data bus                        |          |

| 23  | G3              | Data bus                        |          |

| 24  | G4              | Data bus                        |          |

| 25  | G5              | Data bus                        |          |

| 26  | G6              | Data bus                        |          |

| 27  | G7              | Data bus                        |          |

| 28  | R0              | Data bus                        |          |

| 29  | R1              | Data bus                        |          |

| 30  | R2              | Data bus                        |          |

| -  |               |                                                              |

|----|---------------|--------------------------------------------------------------|

| 31 | R3            | Data bus                                                     |

| 32 | R4            | Data bus                                                     |

| 33 | R5            | Data bus                                                     |

| 34 | R6            | Data bus                                                     |

| 35 | R7            | Data bus                                                     |

| 36 | HSYNC         | Horizontal sync signal, default is negative polarity.        |

| 37 | VSYNC         | Vertical sync signal, default is negative polarity.          |

| 38 | DCLK          | Dot-clock signal and oscillator source                       |

| 39 | NC(HDIR)      | No connect                                                   |

| 40 | NC(VDIR)      | No connect                                                   |

| 41 | VCC           | Power Supply                                                 |

| 42 | VCC           | Power Supply                                                 |

| 43 | NC(YD)        | No connect                                                   |

| 44 | NC(XR)        | No connect                                                   |

| 45 | NC(PARA_SERI) | No connect                                                   |

| 46 | NC(BIST_EN)   | No connect                                                   |

| 47 | NC(ENPROG)    | No connect                                                   |

| 48 | NC            | No connect                                                   |

| 49 | NC            | No connect                                                   |

| 50 | NC            | No connect                                                   |

| 51 | NC(DISP)      | No connect                                                   |

| 52 | DE            | Data input enable. Display access is enabled when DE is "H". |

| 53 | GND           | Ground                                                       |

| 54 | GND           | Ground                                                       |

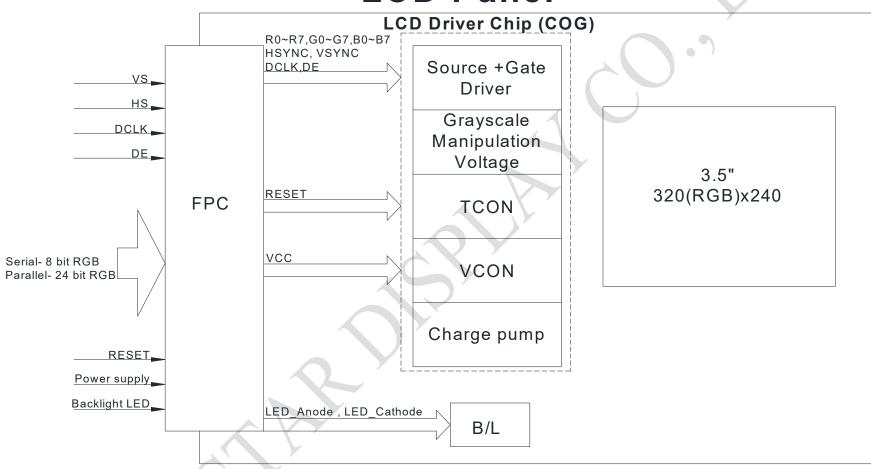

## **10.Block Diagram**

## **LCD Panel**

## 11.Reliability

Content of Reliability Test (Super Wide temperature, -30°C~85°C)

| Environmental Tes                                         | Environmental Test                                                                                                                          |                                                                                                                             |       |  |  |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| Test Item                                                 | Content of Test                                                                                                                             | Test Condition                                                                                                              | Note  |  |  |  |  |  |

| High Temperature<br>storage<br>Low Temperature<br>storage | Endurance test applying the high storage temperature for a long time.  Endurance test applying the low storage temperature for a long time. | 85°C<br>200hrs<br>-40°C<br>200hrs                                                                                           | 2 1,2 |  |  |  |  |  |

| High Temperature<br>Operation                             | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.                      | 85°C<br>200hrs                                                                                                              |       |  |  |  |  |  |

| Low Temperature<br>Operation                              | Endurance test applying the electric stress under low temperature for a long time.                                                          | -30°C<br>200hrs                                                                                                             | 1     |  |  |  |  |  |

| High Temperature/<br>Humidity storage                     | The module should be allowed to stand at 60°C,90%RH max                                                                                     | 60°C,90%RH<br>96hrs                                                                                                         | 1,2   |  |  |  |  |  |

| Thermal shock resistance                                  | The sample should be allowed stand the following 10 cycles of operation  -30°C 25°C 85°C  30min 5min 30min 1 cycle                          | -30°C/85°C<br>10 cycles                                                                                                     |       |  |  |  |  |  |

| Vibration test                                            | Endurance test applying the vibration during transportation and using.                                                                      | Total fixed amplitude: 1.5mm Vibration Frequency: 10~55Hz One cycle 60 seconds to 3 directions of X,Y,Z for Each 15 minutes | 3     |  |  |  |  |  |

| Static electricity test                                   | Endurance test applying the electric stress to the terminal.                                                                                | VS=±600V(contact),<br>±800v(air),<br>RS=330Ω<br>CS=150pF<br>10 times                                                        |       |  |  |  |  |  |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal

Temperature and humidity after remove from the test chamber.

Note3: The packing have to including into the vibration testing.

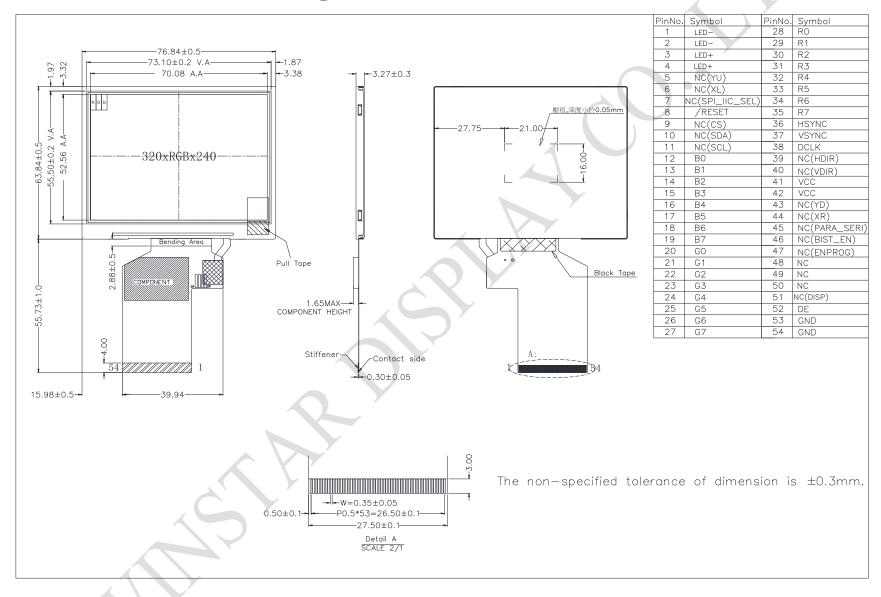

## **12.Contour Drawing**

## instar LCM Sample Estimate Feedback Sheet

| 0 | dule       | Number:                    |              | Pag           | e: 1 |

|---|------------|----------------------------|--------------|---------------|------|

| 1 | ` <u>P</u> | anel Specification :       |              |               |      |

|   | 1.         | Panel Type:                | □ Pass       | □ NG ,        |      |

|   | 2.         | View Direction:            | □ Pass       | □ NG ,        |      |

|   | 3.         | Numbers of Dots:           | □ Pass       | □ NG ,        |      |

|   | 4.         | View Area:                 | □ Pass       | □ NG ,        |      |

|   | 5.         | Active Area:               | □ Pass       | □ NG ,        |      |

|   | 6.         | Operating                  | □ Pass       | □ NG ,        |      |

|   | 7.         | Storage Temperature :      | □ Pass       | □ NG ,        |      |

|   | 8.         | Others:                    |              |               |      |

| 2 | ? <u> </u> | echanical                  |              |               |      |

|   | 1.         | PCB Size:                  | □ Pass       | □ NG ,        |      |

|   | 2.         | Frame Size :               | □ Pass       | □ NG ,        |      |

|   | 3.         | Material of Frame:         | □ Pass       | □ NG ,        |      |

|   | 4.         | Connector Position:        | □ Pass       | □ NG ,        |      |

|   | 5.         | Fix Hole Position:         | □ Pass       | □ NG ,        |      |

|   | 6.         | Backlight Position:        | □ Pass       | □ NG ,        |      |

|   | 7.         | Thickness of PCB:          | □ Pass       | □ NG ,        |      |

|   | 8.         | Height of Frame to         | □ Pass       | □ NG ,        |      |

|   | 9.         | Height of Module:          | □ Pass       | □ NG ,        |      |

|   | 10.        | Others:                    | □ Pass       | □ NG ,        |      |

| 3 | \ <u>R</u> | elative Hole Size :        |              |               |      |

|   | 1.         | Pitch of Connector:        | □ Pass       | □ NG ,        |      |

|   | 2.         | Hole size of Connector:    | □ Pass       | □ NG ,        |      |

|   | 3.         | Mounting Hole size :       | □ Pass       | □ NG ,        |      |

|   | 4.         | Mounting Hole Type:        | □ Pass       | □ NG ,        |      |

|   | 5.         | Others:                    | □ Pass       | □ NG ,        |      |

| 4 | ٠ <u>B</u> | acklight Specification :   |              |               |      |

|   | 1.         | B/L Type:                  | □ Pass       | □ NG ,        |      |

|   | 2.         | B/L Color:                 | □ Pass       | □ NG ,        |      |

|   | 3.         | B/L Driving Voltage (Refer | ence for LED | □ Pass □ NG , |      |

|   | 4.         | B/L Driving Current :      | □ Pass       | □ NG ,        |      |

|   | 5.         | Brightness of B/L:         | □ Pass       | □ NG ,        |      |

|   | 6.         | B/L Solder Method:         | □ Pass       | □ NG ,        |      |

|   | 7.         | Others:                    | □ Pass       | □ NG ,        |      |

|   |            |                            |              |               |      |

## >> Go to page 2 <<

| Winstar Module Number :        |              | Page: 2          |

|--------------------------------|--------------|------------------|

| 5 · Electronic Characteristics | s of Module: |                  |

| 1. Input Voltage :             | □ Pass       | □ NG ,           |

| 2. Supply Current:             | □ Pass       | □ NG ,           |

| 3. Driving Voltage for LCD:    | □ Pass       | □ NG ,           |

| 4. Contrast for LCD :          | □ Pass       | □ NG ,           |

| 5. B/L Driving Method:         | □ Pass       | □ NG ,           |

| 6. Negative Voltage Output :   | □ Pass       | □ NG ,           |

| 7. Interface Function:         | □ Pass       | □ NG ,           |

| 8. LCD Uniformity:             | □ Pass       | □ NG ,           |

| 9. ESD test:                   | □ Pass       | □ NG ,           |

| 10. Others:                    | □ Pass       | □ NG ,           |

| 6 · <u>Summary</u> :           |              |                  |

| Sales signature :              |              |                  |

| Customer Signature :           |              | <u>Date: / /</u> |