# **Video Frame Buffer IP**

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents    |                                         | 3          |

|-------------|-----------------------------------------|------------|

| Acronyms i  | n This Document                         | 5          |

| 1. Introd   | uction                                  | 6          |

| 1.1.        | Overview of the IP                      | 6          |

| 1.2.        | Quick Facts                             | 6          |

| 1.3.        | Features                                | 6          |

|             | Licensing and Ordering Information      |            |

| 1.4.1.      |                                         |            |

| 1.5.        | Naming Conventions                      |            |

| 1.5.1.      | Nomenclature                            |            |

| 1.5.2.      | Signal Names                            | 7          |

| 1.5.3.      | Host                                    |            |

| 1.5.4.      | Attribute                               | 7          |

| 1.6.        | Minimum Device Requirements             |            |

|             | onal Description                        |            |

|             | IP Architecture Overview                |            |

|             | Frame Rate Conversion                   |            |

|             | Dynamic Parameter Updating              |            |

|             | Memory Bandwidth and Size               |            |

|             | Clocking                                |            |

| 2.5.1.      | Video Input/Output Timing               |            |

| 2.5.2.      | Video Frame Timing                      |            |

| 2.5.3.      | Memory Interface Timing                 |            |

| 2.5.4.      | Dynamic Parameter Updating              |            |

| 2.5.5.      | Clocking and Reset Overview             |            |

| 2.5.6.      | Clock Domains and Clock Domain Crossing |            |

|             | User Interfaces                         |            |

| 2.6.1.      | Video Input/Output                      |            |

| 2.6.2.      | Memory Interface                        |            |

| 2.6.3.      | Parameter Register Read/Write Interface |            |

| 2.6.4.      | Unified Video Streaming Interface       |            |

| _           | ameter Description                      |            |

|             | Description                             |            |

| _           | er Description                          |            |

| Ŭ           | ning with the IP                        |            |

| U           | Generation and Synthesis                |            |

|             | Constraining the IP                     |            |

|             | Running Functional Simulation           |            |

|             |                                         |            |

| _           | ging                                    |            |

| _           | n Considerations                        |            |

|             | A. Resource Utilization                 |            |

|             | upport Assistance                       |            |

| Pevision Hi |                                         | 39<br>//10 |

|             |                                         |            |

## **Figures**

| Figure 2.1. Video Frame Buffer IP Core Functional Diagram                             | 8  |

|---------------------------------------------------------------------------------------|----|

| Figure 2.2. Video Frame Buffer IP Core I/O                                            |    |

| Figure 2.3. Timing Diagram of the RGB Serial Processing (8-bit Pixel)                 | 10 |

| Figure 2.4. Timing Diagram of the RGB Parallel Processing (8-bit Pixel)               |    |

| Figure 2.5. Timing Diagram of the YCbCr 4:2:2 Serial Processing (8-bit Pixel)         | 11 |

| Figure 2.6. Timing Diagram of the YCbCr 4:2:2 Parallel Processing (8-bit Pixel)       | 11 |

| Figure 2.7. dout_enable_i Control Timing                                              | 12 |

| Figure 2.8. Output Frame Rate Same as Input Frame Rate                                | 12 |

| Figure 2.9. Output Frame Rate is Twice the Input Frame Rate                           | 12 |

| Figure 2.10. Frame Dropping when Frame Rate Conversion = 1                            | 13 |

| Figure 2.11. Timing Diagram for Memory Write Operation                                | 13 |

| Figure 2.12. Timing Diagram for Memory Read Operation                                 | 13 |

| Figure 2.13. Timing Diagram for Dynamic Parameter Updating (Parameter Bus Width = 32) | 14 |

| Figure 2.14. Clock Domains and Clock Domain Crossing Diagram                          |    |

| Figure 2.15. UVSI Tx and Rx Signals Example Waveform                                  | 17 |

| Figure 2.16. RGB with 10 BPC                                                          | 17 |

| Figure 2.17. YCbCr422 with 10 BPC                                                     | 17 |

| Figure 2.18. YCbCr444 with 10 BPC                                                     | 18 |

| Figure 2.19. Single Color with 12 BPC                                                 | 18 |

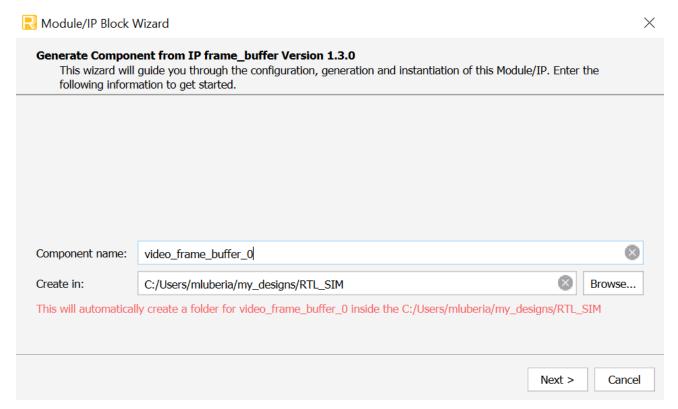

| Figure 6.1. Module/IP Block Wizard                                                    | 30 |

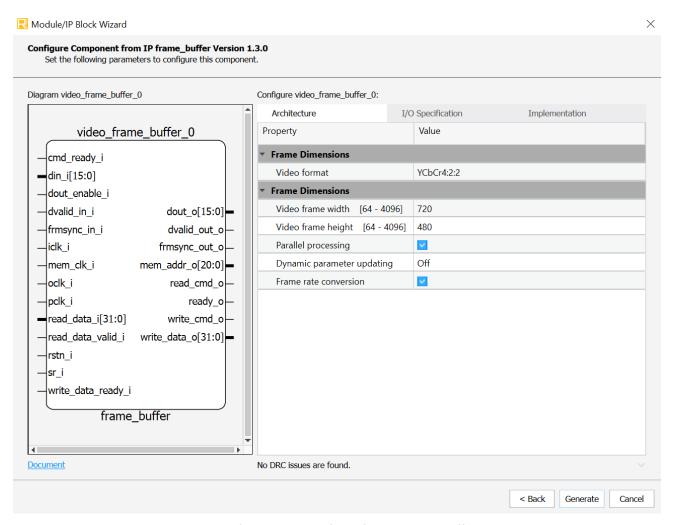

| Figure 6.2. Configure User Interface of Video Frame Buffer IP Core                    | 31 |

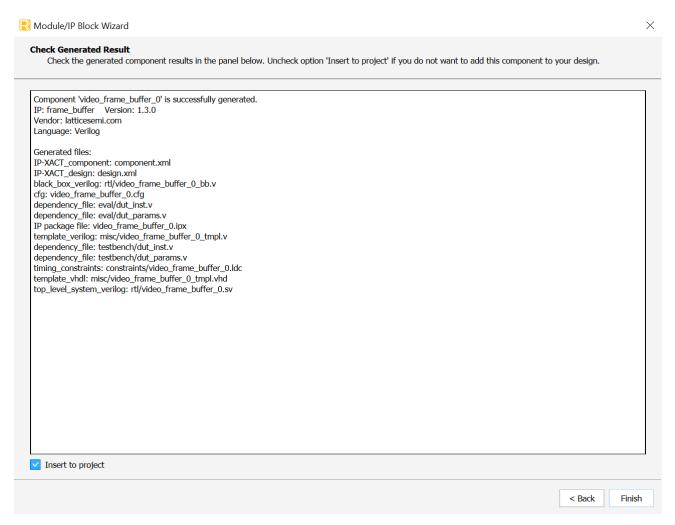

| Figure 6.3. Check Generating Result                                                   | 32 |

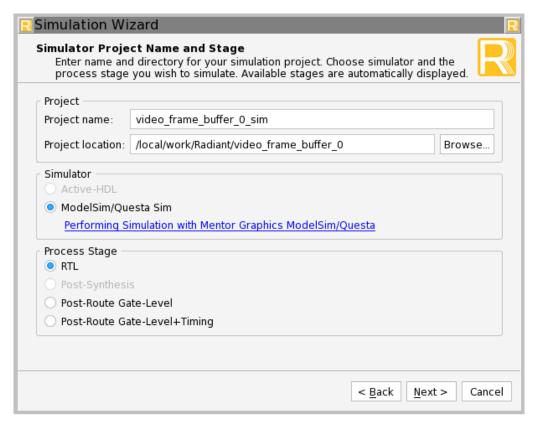

| Figure 6.4. Simulation Wizard                                                         | 33 |

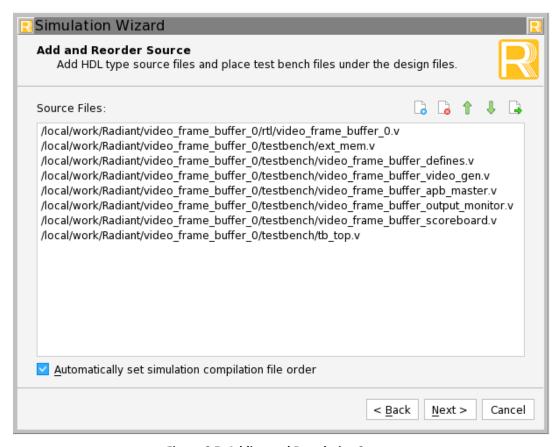

| Figure 6.5. Adding and Reordering Source                                              | 34 |

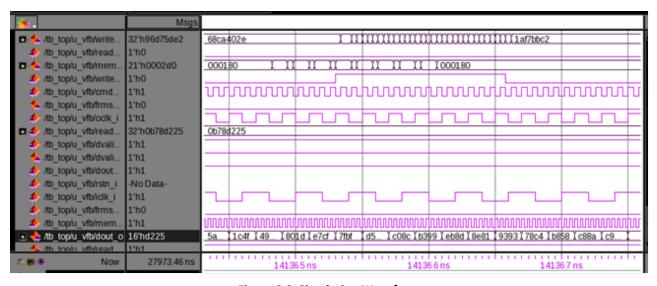

| Figure 6.6. Simulation Waveform                                                       | 34 |

|                                                                                       |    |

| Tables                                                                                |    |

| Table 1.1. Quick Facts                                                                | 6  |

| Table 1.2. Ordering Part Number                                                       |    |

| Table 2.1. User Interfaces and Supported Protocols                                    |    |

| Table 3.1. Attributes Table                                                           |    |

| Table 4.1. Video Frame Buffer IP Core Signal Description                              |    |

| Table 5.1. General Configuration Registers                                            |    |

| Table 5.2. FRMWIDTH Register (Address 0x0000)                                         |    |

| Table 5.3. FRMHEIGHT Register (Address 0x0004)                                        |    |

| Table 5.4. UPDATE Register (Address 0x000C)                                           |    |

| Table 5.5. FRM_RESYNC Register (Address 0x0010)                                       |    |

| Table 5.6. FRAME_CONV_STATUS Register (Address 0x0014)                                |    |

| Table 6.1. Generated File List                                                        |    |

| Table A.1. Resource Utilization for the LAV-AT-G70-1LFG1156I Device                   |    |

| Table A.2. Resource Utilization for the LFCPNX-100-7LFG672C Device                    |    |

5

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                                |

|---------|-------------------------------------------|

| AMBA    | Advanced Microcontroller Bus Architecture |

| AXI     | Advanced eXtensible Interface             |

| CPU     | Central Processing Unit                   |

| DDR     | Double Data Rate                          |

| EBR     | Embedded Block RAM                        |

| FIFO    | First In First Out                        |

| FPGA    | Field Programmable Gate Array             |

| RAM     | Random Access Memory                      |

| RTL     | Register Transfer Level                   |

| UVSI    | Unified Video Streaming Interface         |

## 1. Introduction

#### 1.1. Overview of the IP

The Video Frame Buffer IP Core buffers video data in external memory to be displayed on output devices such as computer monitors, projectors, and others. The Video Frame Buffer IP Core supports image sizes up to 4K x 4K with YCbCr 4:2:2, 4:4:4 and RGB video formats. The IP supports dynamic parameter updating through the AXI4-Lite interface or native parameter bus interface, which can be configured to operate on a different clock from the IP. Simple frame rate conversion is employed to support different input and output frame rates.

#### 1.2. Quick Facts

Table 1.1 presents a summary of the Video Frame Buffer IP Core.

**Table 1.1. Quick Facts**

| IP Requirements            | Supported FPGA Families | CrossLink™-NX, Certus™-NX, CertusPro™-NX, Lattice Avant™                                 |  |  |

|----------------------------|-------------------------|------------------------------------------------------------------------------------------|--|--|

| Resource Utilization       | Targeted Devices        | LIFCL-40, LIFCL-17, LFD2NX-40, LFD2NX-17, LFCPNX-100, LAV-AT-E70, LAV-AT-G70, LAV-AT-X70 |  |  |

|                            | Resources               | See the Resource Utilization section                                                     |  |  |

|                            | Lattice Implementation  | IP Core v1.x.x – Lattice Radiant software 2024.1 or later                                |  |  |

|                            | Conthacts               | Lattice Synthesis Engine                                                                 |  |  |

| <b>Design Tool Support</b> | Synthesis               | Synopsys® Synplify Pro® for Lattice                                                      |  |  |

|                            | Simulation              | For a list of supported simulators, see the Lattice Radiant software user guide.         |  |  |

#### 1.3. Features

The key features of Video Frame Buffer IP Core include:

- Supports single color, YCbCr 4:2:2, YcbCr 4:4:4, and RGB video formats

- Supports input and output resolutions of  $64 \times 64$  to  $4 \times 4$  k pixels

- Supports serial and parallel pixel processing

- Supports frame rate conversion

- Supports dynamic parameter update of frame size

- Supports configurable parameter bus clock

- Supports configurable memory bus width and base address

- · Supports configurable memory burst length and burst count

- Configurable internal FIFO type and depth

- Supports 8, 10, 12, or 16-bit color depth per plane

- Supports optional AXI4-Lite interface for register access

- Supports optional AXI4 interface for memory interface

- Supports optional Unified Video Streaming Interface (UVSI)

## 1.4. Licensing and Ordering Information

An IP specific license string is required to enable full use of the Video Frame Buffer IP in a complete, top-level design.

The IP can be fully evaluated through functional simulation and implementation (synthesis, map, place and route) without an IP license string. This IP supports Lattice's IP hardware evaluation capabilities. You can create versions of the IP to operate in hardware for a limited time (approximately four hours) without requiring an IP license string. A license string is required to enable timing simulation and to generate a bitstream file that does not include the hardware evaluation timeout limitation. It may also be used to evaluate the core in hardware in user-defined designs.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPLIG-02137-1 3

7

The hardware evaluation capability may be enabled and disabled in the Strategy dialog box. This setting is enabled by default. To change this setting, go to **Project > Active Strategy > LSE/Synplify Pro Settings**.

For more information about pricing and availability of the Video Frame Buffer IP, contact your local Lattice Sales Office.

### 1.4.1. Ordering Part Number

**Table 1.2. Ordering Part Number**

| Device Family   | P                     | Part Number          |  |  |  |

|-----------------|-----------------------|----------------------|--|--|--|

|                 | Single Machine Annual | Multi-Site Perpetual |  |  |  |

| Lattice Avant-E | VFB-AVE-US            | VFB-AVE-UT           |  |  |  |

| Lattice Avant-G | VFB-AVG-US            | VFB-AVG-UT           |  |  |  |

| Lattice Avant-X | VFB-AVX-US            | VFB-AVX-UT           |  |  |  |

| CrossLink-NX    | VFB-CNX-US            | VFB-CNX-UT           |  |  |  |

| Certus-NX       | VFB-CTNX-US           | VFB-CTNX-UT          |  |  |  |

| CertusPro-NX    | VFB-CPNX-US           | VFB-CPNX-UT          |  |  |  |

## 1.5. Naming Conventions

#### 1.5.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.5.2. Signal Names

Signal Names that end with:

- \_n are active low

- \_*i* are input signals

- \_o are output signals

- \_io are bi-directional input/output signals

#### 1.5.3. Host

The logic unit inside the FPGA interacts with the Video Frame Buffer IP Core.

#### 1.5.4. Attribute

The names of attributes in this document are formatted in title case and italicized (Attribute Name).

## 1.6. Minimum Device Requirements

Refer to the Resource Utilization section.

## 2. Functional Description

#### 2.1. IP Architecture Overview

The Video Frame Buffer IP Core receives input video data, stores it in the external memory and outputs it based on the timing controlled by the dout\_enable\_i or axis\_vid\_tready\_i signal. The IP stores data into memory in different width format as required by the application. The IP also provides synchronization of data across different clock domains and different format domains.

The IP provides a simple parameter bus for dynamic frame size updating. It also implements a flexible memory interface which can be connected to Lattice memory controller IP cores.

An optional AMBA bus interface is also provided — AXI4-Lite for parameter bus, Unified Video Streaming Interface for video interface, and AXI4 for memory controller interface.

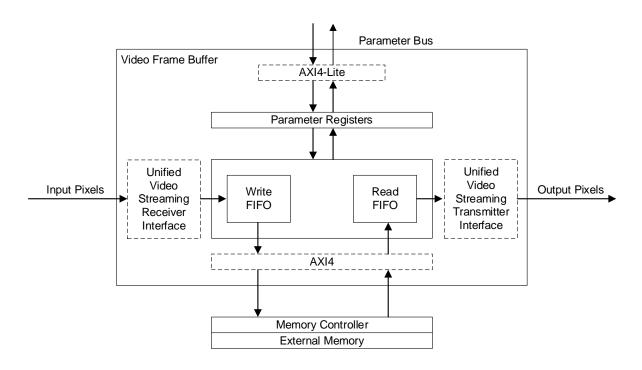

Figure 2.1. Video Frame Buffer IP Core Functional Diagram

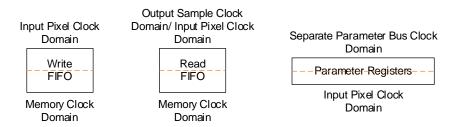

The IP supports continuous data streams from and to external interfaces in different clock domains using asynchronous Write and Read FIFOs. Input pixels are packed and stored into the asynchronous double clock Write FIFO first. The pixels are then sent to an external memory controller to be written to the memory. After an entire video frame has been stored in the external memory, frame reading starts. The pixels read from external memory are stored in the asynchronous Read FIFO and transferred to output interface clock domain. After unpacking, pixels are output from the Video Frame Buffer IP Core. In the video frame buffer, several clock sources are involved. The memory interface operates on a separate memory clock. When frame rate conversion is enabled, there are two clocks in the video data path: input pixel sample clock and output pixel sample clock. When frame rate conversion is disabled, the video data path operates at input pixel sample clock rate. The parameter bus runs on a separate parameter bus clock.

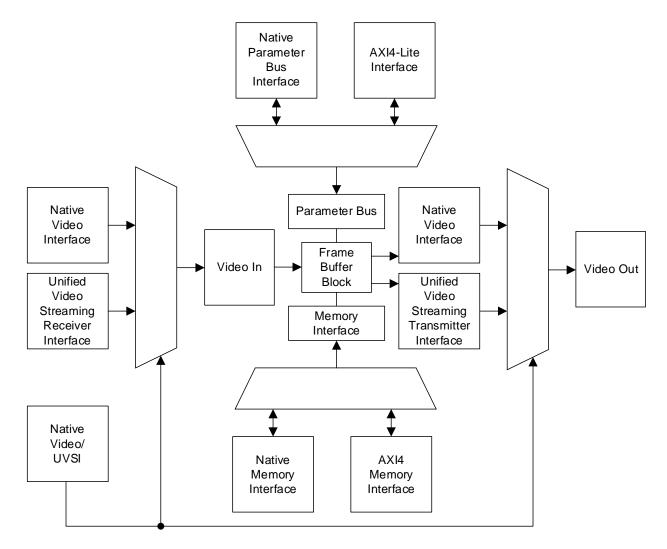

Figure 2.2. Video Frame Buffer IP Core I/O

#### 2.2. Frame Rate Conversion

The Video Frame Buffer IP Core provides a simple frame rate conversion. When frame rate conversion is enabled, the IP output data path runs at the output pixel clock rate. The output frame rate is controlled by the output pixel sample clock and dout\_enable\_i or axis\_vid\_tready\_i signal. When dout\_enable\_i or axis\_vid\_tready\_i signal is high, the IP outputs pixels continuously. When there is no new video frame, the IP outputs the last frame repeatedly. When frame rate conversion is ON, the IP requires to store 2 frames first before the IP begins to output frames. When frame rate conversion is disabled, the IP output data path runs on the input pixel sample clock. The output frame is generated directly from the input video stream. If there is no new input video frame, the IP stops generating output data.

## 2.3. Dynamic Parameter Updating

The Video Frame Buffer IP Core provides AXI4-Lite parameter bus and native parameter bus ports for internal parameter update at run time. The parameters are double-buffered to avoid adverse effect to the IP when they are changed. The new values are buffered and transferred to the working registers when the IP is ready to accept a new configuration. The UPDATE register is used to indicate when the new values are consumed and when the buffers can accept new data.

When AXI4-lite is enabled, dynamic parameter updating is allowed through control and status registers. Table 5.1 shows the registers for configuration of the IP.

All the parameter registers (Frame Height and Frame Width) can be written to only when the UPDATE register bit is 0. When the UPDATE bit is set to 1, the parameters FRMWIDTH and FRMHEIGHT take effect when the frmsync\_in\_i or axis\_vid\_tuser[0] signal is active, indicating a new input frame is arriving. After updating the internal parameters, the IP resets the UPDATE bit to indicate that the parameter registers are now empty and can take on new values.

### 2.4. Memory Bandwidth and Size

The Video Frame Buffer IP Core stores and retrieves pixels to and from the external memory using memory burst write and read commands. When DDR2 memory is used for external memory, one burst operation with the number of bits equals (burst\_length × burst\_count / 2) × memory\_data\_width bit, cannot exceed the size of a single video line. A single video line is transferred through multiple burst write/read transactions internally.

When frame rate conversion is inactive, the Video Frame Buffer IP Core needs a two-frame memory storage space; when frame rate conversion is active, a three-frame storage space is required. The total external memory size the IP requires can be viewed on the Video frame buffer IP user interface.

The required memory bandwidth is input pixel data rate plus output pixel data rate.

For example, for parallel 8-bit YCbCr 4:2:2 pixels, if the input pixel sample clock is 74.25 MHz and output pixel sample clock is 148.5 MHz, the required bandwidth is  $2 \times 8 \times (74.25 + 148.5) = 3564$  bit  $\times$  MHz. If the memory data width is 32, the required memory clock is (3564 / 32) = 111.375 MHz.

### 2.5. Clocking

#### 2.5.1. Video Input/Output Timing

The Video Frame Buffer IP Core supports single color, YCbCr 4:2:2, YCbCr 4:4:4, or RGB video format.

For YCbCr 4:4:4 or RGB video format in Native Video, the three planes are interleaved for serial processing and combined on the din\_i and dout\_o ports for parallel processing.

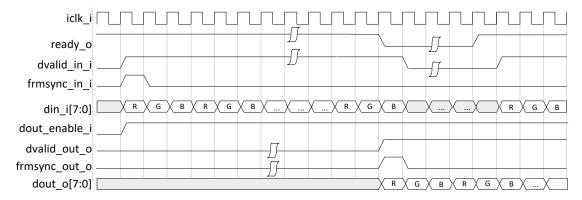

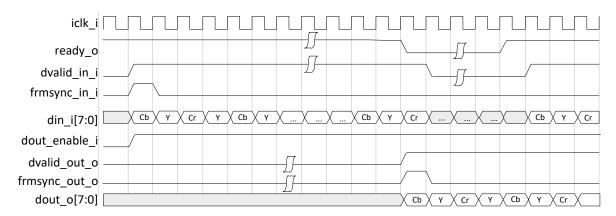

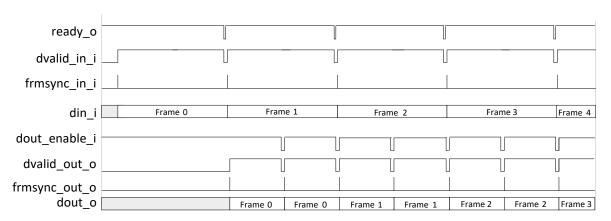

Figure 2.3. Timing Diagram of the RGB Serial Processing (8-bit Pixel)

Figure 2.4. Timing Diagram of the RGB Parallel Processing (8-bit Pixel)

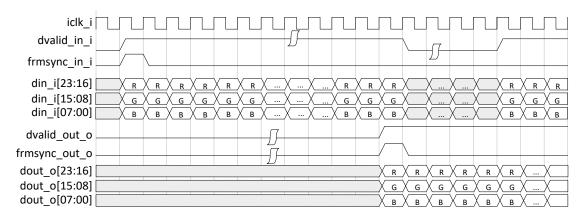

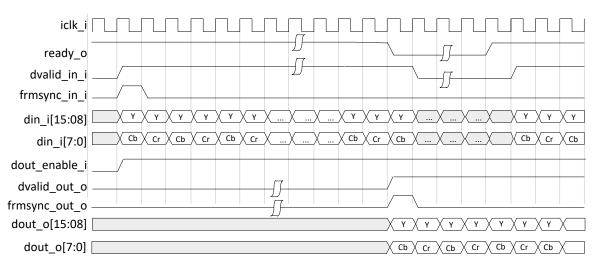

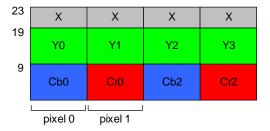

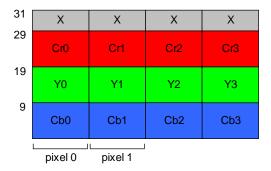

For YCbCr 4:2:2 video serial processing, the input and output sequence is Cb, Y, Cr, Y, .... For parallel processing, the Y plane occupies the upper bits of the din\_i and dout\_o ports, and the Cb and Cr planes the lower bits. Cb and Cr planes are interleaved in the lower half, and Cb comes before Cr.

Figure 2.5. Timing Diagram of the YCbCr 4:2:2 Serial Processing (8-bit Pixel)

Figure 2.6. Timing Diagram of the YCbCr 4:2:2 Parallel Processing (8-bit Pixel)

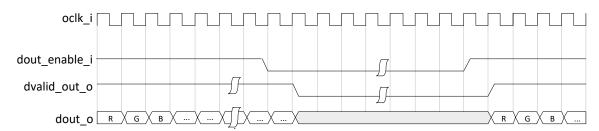

When dout\_enable\_i is de-asserted, the IP stops outputting data. Similarly, when dout\_enable\_i is asserted, the IP begins outputting data. The assertion and de-assertion of dout\_enable\_i can be used to generate a horizontal blank and a vertical blank depending on the output video format.

Figure 2.7. dout\_enable\_i Control Timing

#### 2.5.2. Video Frame Timing

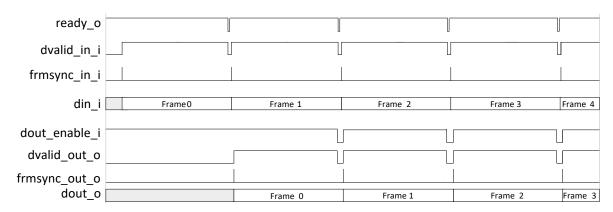

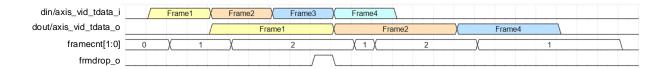

The following diagram shows the frame timing when frame rate conversion is disabled. After accepting one input frame, the IP starts generating frames. The output frame is driven by the input frame. When a new input frame arrives before the current output frame is finished, the current output frame is dropped and a new output frame starts. After the last input frame, the video frame buffer stops generating output frames. For details, refer to the Design Considerations section.

Figure 2.8. Output Frame Rate Same as Input Frame Rate

The following diagram shows the frame timing when the output frame rate is twice the input frame rate. Output frames run on a separate output pixel clock. The output frame rate is determined by the output pixel clock and dout\_enable\_i or axis\_vid\_tready\_i signal. The IP generates output frames based on the oldest pending input frames. When a new input frame is received, the IP pushes out the oldest frame and exports the second oldest frame. When there is no new frame input, the IP exports the stored frames and then keeps exporting the last frame repeatedly. When the external memory is fully occupied by the unconsumed frames where there is no more space for new frames, the IP overwrites the latest input frame.

Figure 2.9. Output Frame Rate is Twice the Input Frame Rate

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

13

The following diagram shows the frame timing when the output frame rate is two times slower than the input frame rate. The Video Frame Buffer can store at most 2 frames at a time. The IP accepts only a new frame when the IP is complete writing at least one of the stored frames to the external memory, or when the IP is not holding any frames. When a new frame is sent to the IP when the output clock is slower and the IP is still holding 2 frames, the new frame is dropped.

Figure 2.10. Frame Dropping when Frame Rate Conversion = 1

#### 2.5.3. Memory Interface Timing

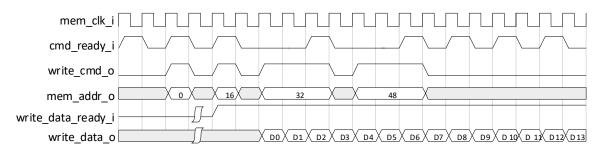

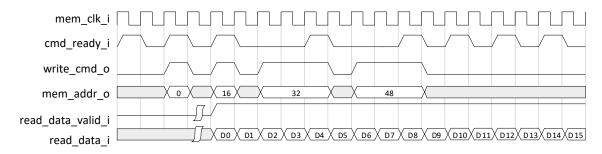

When the internal write FIFO is half full, the IP triggers memory write operation cycles. The memory write operation continues until the write FIFO is empty. Write FIFO width is the same as the data bus width which is set from the GUI. Data is stored to the write FIFO during the positive edge of the input pixel clock and read with the memory clock.

Figure 2.11. Timing Diagram for Memory Write Operation

When the internal read FIFO is less than half full, and there is no ongoing write operation, the memory read burst operation starts. Read burst operation continues until the read FIFO is half full.

The memory write and read operations are in bursts. The memory write and read operations switch at the end of the burst cycle.

Figure 2.12. Timing Diagram for Memory Read Operation

The AXI4 Memory interface write operation is triggered whenever the Write FIFO holds any data. The memory write operation continues until the write FIFO is empty.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-IPUG-02137-1.3

#### 2.5.4. Dynamic Parameter Updating

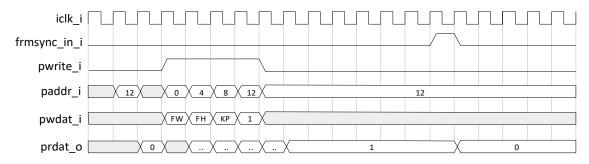

In the following diagram, FW and FH are the video frame width and height.

The parameter bus can be configured to operate on a separate clock. By default, the bus operates at the input pixel clock rate. The parameter registers are writable only when the UPDATE register is 0. When the UPDATE register bit is set to 1, the IP updates the internal parameter registers with the new values at the next active frmsync\_in\_i or axis vid tuser i[0] and reset the UPDATE register bit.

Figure 2.13. Timing Diagram for Dynamic Parameter Updating (Parameter Bus Width = 32)

#### 2.5.5. Clocking and Reset Overview

The IP contains 2 resets — one active low asynchronous reset and an active high synchronous reset. The synchronous reset takes effect on the positive edge of the input pixel clock domain for signals in this clock domain. For signals in other clock domains, the synchronous reset takes effect at the third positive edge of the corresponding clock after two positive edges of the input pixel clock. The IP uses iclk\_i and mem\_clk\_i for all configurations while output sample clock (oclk\_i) is used only when frame rate conversion is on and is used to sample the read FIFO. The pclk\_i clock input is a separate parameter bus clock used for dynamic parameter.

#### 2.5.6. Clock Domains and Clock Domain Crossing

The following diagram shows the clock domain crossings of the IP when separate bus parameter clock is used. The read clock for the Read FIFO can either be from iclk\_i or oclk\_i clock domain. If the frame rate conversion option is turned on, the read clock for the Read FIFO is from the ock\_i clock domain. The entire IP is controlled by the active low asynchronous reset and the active high synchronous reset.

Figure 2.14. Clock Domains and Clock Domain Crossing Diagram

#### 2.6. User Interfaces

Table 2.1. User Interfaces and Supported Protocols

| User Interface   | Supported Protocols                               | Description                                                                                                                                                                                                              |  |

|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Video interface  | Native video<br>Unified Video Streaming Interface | Video interface can either be set to Native Video which is described in the Video Input/Output section or through Unified Video Streaming Interface which is described in the Unified Video Streaming Interface section. |  |

| Memory interface | Native memory                                     | Memory interface can either be set to Native Memory                                                                                                                                                                      |  |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| User Interface             | Supported Protocols               | Description                                                                                                                                                                                                                                                                                                                     |

|----------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | AXI4                              | which is described in the Memory Interface section or through AXI4. For details, refer to the AMBA AXI protocol specification in the Arm Developer web page.                                                                                                                                                                    |

| Dynamic parameter updating | Native parameter bus<br>AXI4-Lite | When using dynamic parameter updating, the control and status registers can be written and read through either the Native Parameter Bus as described in the Parameter Register Read/Write Interface section or through AXI4-Lite. For details, refer to the AMBA AXI-Lite protocol specification in the Arm Developer web page. |

#### 2.6.1. Video Input/Output

The Video Frame Buffer IP Core uses a simple handshaking method to pass pixel data into and out of the IP. The IP asserts the ready output when the IP is ready to receive data. When the driving module has data to pass to the video frame buffer, the module asserts the IP dvalid\_in\_i port and at the same time placing the input video data on the din\_i port. The frmsync\_in\_i input is driven to a 1 during the clock cycle when the very first active pixel is placed on the din\_i bus.

Similarly, dvalid\_out\_o is active when valid output pixels are available on dout\_o, and frmsync\_out\_o marks the first pixel in an output frame.

The input signal dout\_enable\_i enables the IP to generate output pixels. When dout\_enable\_i is low (inactive), the IP stops generating output pixels.

#### 2.6.2. Memory Interface

The Video Frame Buffer IP Core implements a flexible memory interface which operates on a separate clock from the main core.

When connecting to DDR2 memory controller, the burst length and burst count of video frame buffer have the same values as the DDR2 memory controller. When connecting to DDR3 memory controller, the burst length of video frame buffer has the same value with DDR3 memory controller, while the burst count of video frame buffer is half as that of DDR3 memory controller.

The video frame buffer assumes a memory byte addressing scheme. When connecting the memory controller, the address connection adjusts according to the DDR memory data width.

Assuming the DDR2 and DDR3 memory has 27 bits address width, the address connection can be as follows:

```

ddr_addr = {1'b0,mem_addr_o[25:0]}; // for 8-bit DDR memory only

ddr_addr = {2'b00,mem_addr_o[25:1]}; // for 16-bit DDR memory only

ddr_addr = {3'b000,mem_addr_o[25:2]}; // for 32-bit DDR memory only

The corresponding command is as follows:

```

```

ddr_cmd = (write_cmd_o) ? 4'b0010 : 4'b0001; // (write_cmd_o) ? WRITE : READ

ddr_cmd_valid = (write_cmd_o || read_cmd_o);

```

To get the best throughput (about 5% increase compared to normal connection), you must fine tune the combination of row, bank, or column address to get the best throughput.

To get maximum throughput on the memory bus (about 5% increase compared to normal connection), you need to steer clear of write-to-precharge, read-to-precharge, or precharge-to-active during row switching. You can access each bank in turn by using write or read with auto-precharge command to close current bank immediately after current burst write or read. To adopt this policy, you must fine tune the combination of Row, Bank, or Column address to get the best throughput.

For example, when DDR2 memory data width is 16, row size is 14, column size is 10, bank size is 8, burst length is 8, and burst count is 1, which means the memory controller user interface data width is 32, row address is 14 bits, column address is 10 bits, bank address is log2(bank size) = 3 bits and log2(burst length × burst count) = 3 bits. The memory controller address mapping inside the memory controller IP core is as follows:

```

ddr_addr = {row_addr[13:0], bank_addr[2:0], col_addr[9:0]}

```

To get the best throughput, first increase col\_addr[2:0] to utilize the burst operation, then increase bank\_addr[2:0], followed by col\_addr[9:3], and finally the row\_addr. The interface to the DDR2 and DDR3 memory is similar to:  $ddr_addr = \{2'b00, mem_addr_o[25:14], mem_addr_o[6:4], mem_addr_o[13:7], mem_addr_o[3:1]\};$

The corresponding command is as follows:

```

ddr_cmd = (write_cmd_o) ? 4'b0100 : 4'b0011; // (write_cmd_o) ? WRITEA : READA

```

As the memory controller user interface data width is 32, mem addr o[1:0] is always zero.

The IP arbitrates between memory write and read operations, ensuring only a write\_cmd\_o or a read\_cmd\_o is asserted at any given time.

Two clock cycles after the write\_data\_ready\_i is asserted, data becomes available on the write\_data\_o port. The parameter "Data\_rdy to Write Data Delay" of memory controller must be set to 2.

The cmd\_ready\_i can be asserted once every two clock cycles, and must have at least a one-cycle interval, which is consistent with the Lattice DDR Memory Controller IP cores.

When the IP is configured to use AXI4 as a memory interface, the AXI4 signals are exposed in the top-level ports instead of the memory interface. Refer to the AMBA AXI-Lite protocol specification in the Arm Developer web page for detailed information.

#### 2.6.3. Parameter Register Read/Write Interface

The parameter bus data width is configured based on the system CPU's data width.

When the IP is configured to use AXI4-Lite as register interface, the AXI4-Lite signals are exposed in the top-level ports instead of the parameter register interface. Refer to the AMBA AXI-Lite protocol specification in the Arm Developer web page for detailed information.

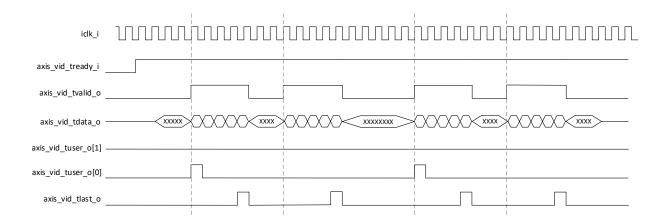

#### 2.6.4. Unified Video Streaming Interface

The Unified Video Streaming Interface is compliant with the AMBA AXI4-Stream Protocol Specification. This interface is only available when parallel processing is enabled. When Unified Video Streaming Receiver Interface is enabled, pixel data is received through the Unified Video Streaming Receiver Interface.

Refer to the AMBA AXI-stream protocol specification in the Arm Developer web page for detailed information.

The size of axis\_vid\_tdata\_i and axis\_vid\_tdata\_o depends on the value of TD\_WD and PPC, where PPC is the Pixel Per Clock – this IP can only support 1 PPC, and TD\_WD (axis\_vid\_tdata width) depends on the following attributes:

- BPP, Bits Per Pixel == CPP × BPC.

- CPP, Colors Per Pixel. Red, Green, and Blue for RGB. Luma, Blue minus Luma, and Red minus Luma for YCbCr. 3 is used for RGB and YCbCr 4:4:4, while 2 for YCbCr 4:2:2.

- BPC, Bits Per Color. Minimum width of each component is 8 -bits. This IP can support BPC of 8, 10, 12, and 16 bits.

The TD\_WD is calculated as  $ceil(BPP/8) \times 8$  which is the data width per pixel. The size of axis\_vid\_tdata\_i is calculated as TD\_WD × PPC.

Figure 2.15. UVSI Tx and Rx Signals Example Waveform

Figure 2.15 shows the waveform when UVSI is enabled. The valid pixels are accompanied by axis\_tvalid\_o and the transaction is valid when handshake with axis\_vid\_tready\_i is made. The waveform also shows the assertion of axis\_vid\_tuser\_o [0] at start of frame and axis\_vid\_tlast\_o for end of line. Horizontal blanking occurs after every line while vertical blanking occurs before every start of frame. For Video Frame Buffer, the axis\_vid\_tready\_o signal deasserts after last pixel of row is received or write FIFO is almost full (Write FIFO Depth – 3 if Memory Bus Width / Data Port Width (TD\_WD) <2 and Write FIFO Depth – 2 otherwise).

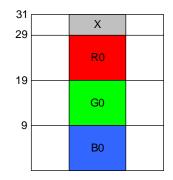

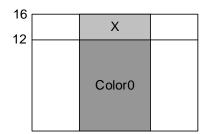

For axis\_vid\_tdata mapping, the video packet data is mapped across the TDATA bytes with the LSB of the first color component of the first pixel in bit 0. Byte align each pixel when mapping multiple pixels in parallel. When a pixel does not perfectly fill a given number of bytes, pad MSBs with don't care data. Refer to the following diagrams.

Figure 2.16. RGB with 10 BPC

Figure 2.17. YCbCr422 with 10 BPC

Figure 2.18. YCbCr444 with 10 BPC

Figure 2.19. Single Color with 12 BPC

## 3. IP Parameter Description

The configurable attributes of the Video Frame Buffer IP Core are shown in Table 3.1. You can configure the IP by setting the attributes accordingly in the IP Catalog Module/IP Wizard of the Lattice Radiant software. Wherever applicable, default values are in bold.

**Table 3.1. Attributes Table**

| Selectable Values                                | Description                                                                                                                                                                                                                                                                                        | Dependency on Other Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sciectable values                                | Description Dependency on other Attribute                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                                  |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Single color,  YCbCr4:2:2,  YCbCr4:4:4 or RGB    | Defines the format of video stream.                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 64–4096, <b>720</b>                              | Selects the video frame width which is the horizontal number of pixels. Only values from 64 to 4096 are allowed.                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 64–4096, <b>480</b>                              | Selects the video frame height which is the horizontal number of pixels. Only values from 64 to 4096 are allowed.                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Off, <b>On</b>                                   | Determines whether the IP processes video color planes in parallel.                                                                                                                                                                                                                                | Off when <i>Video format</i> is equal to Single color, editable otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| <b>Off</b> , AXI4-lite, Native<br>Parameter Bus  | Determines whether the IP supports parameters updating at runtime. Refer to the Dynamic parameter updating section for more information.  When dynamic parameter updating is enabled, the Max video frame width and Max video frame height specify the largest frame size the IP needs to support. | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Checked, Unchecked                               | Enables frame rate conversion. When enabled, the output video stream runs on a separate clock. Refer to the Frame Rate Conversion section for more information.                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| <b>Native video</b> , Unified<br>Video Streaming | Set to <i>Native Video</i> as described in the Video Input/Output section or through Unified Video Streaming Interface as described in the Unified Video Streaming Interface section.                                                                                                              | Unified Video Streaming is only available when Parallel processing is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                  |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                                  |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| <b>8</b> ,10,12,16                               | Sets the bit width of all color planes comprising the incoming pixel.                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                  |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 8,16, <b>32</b> ,64,128                          | Sets the data width of memory interface.                                                                                                                                                                                                                                                           | Selectable values are calculated based on <i>Video format</i> , <i>Parallel processing</i> , and <i>Input pixel width</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                  | YCbCr4:2:2, YCbCr4:4:4 or RGB  64–4096, 720  64–4096, 480  Off, On  Off, AXI4-lite, Native Parameter Bus  Checked, Unchecked  Native video, Unified Video Streaming  8,10,12,16                                                                                                                    | Single color, YCbCr4:2:2, YCbCr4:4:4 or RGB  Selects the video frame width which is the horizontal number of pixels. Only values from 64 to 4096 are allowed.  Selects the video frame height which is the horizontal number of pixels. Only values from 64 to 4096 are allowed.  Off, On  Determines whether the IP processes video color planes in parallel.  Determines whether the IP supports parameters updating at runtime. Refer to the Dynamic parameter updating senabled, the Max video frame width and Max video frame height specify the largest frame size the IP needs to support.  Checked, Unchecked  Checked, Unchecked  Checked, Unchecked  Native video, Unified Video Streaming Interface as described in the Video Streaming Interface section.  Sets the bit width of all color planes comprising the incoming pixel.  Sets the data width of memory |  |  |

| Attribute                                                                                                                                      | Selectable Values                                                                                             | Description                                                                                                                                                                               | Dependency on Other Attributes                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory base address                                                                                                                            | Memory address<br>width x00000000—<br>Memory address<br>width xFFFFFFF,<br>Memory address<br>width 'b00000000 | Sets the base address of the external memory space used. Value must be in binary format and must not exceed memory address width.                                                         | Base address must be aligned to axi_awsize_o and axi_arsize_o value.                                                                                                                                                                          |

| Memory address width                                                                                                                           | Output Value, 21                                                                                              | Specifies the address width of the memory interface. This is generated automatically by the user interface.                                                                               | Calculated based on <i>Memory size</i> needed.                                                                                                                                                                                                |

| Memory size needed                                                                                                                             | Output Value,<br>2073600                                                                                      | Specifies the size of the external memory space needed. This is generated automatically by the user interface.                                                                            | Calculated based on Video frame width, Video frame height, Frame rate conversion, Command burst count, DDR memory burst length, Memory bus width, and Input pixel width.                                                                      |

| Memory interface                                                                                                                               | Native memory, AXI4                                                                                           | Set to <i>Native Video</i> as described in the Memory Interface section or through <i>AXI4</i> . For details, refer to the AMBA AXI protocol specification in the Arm Developer web page. | _                                                                                                                                                                                                                                             |

| Miscellaneous ports                                                                                                                            | •                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                                                                                                               |

| Miscellaneous Signals                                                                                                                          | Checked, <b>Unchecked</b>                                                                                     | Enables the input frame re-sync flag, including frame drop and repeat flag when frame rate conversion is on.                                                                              | Only selectable when <i>Dynamic</i> Parameter Updating is off.                                                                                                                                                                                |

| Implementation                                                                                                                                 | -                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                                                                                                               |

| Read FIFO type                                                                                                                                 | EBR, Distributed                                                                                              | Selects EBR or Distributed RAM for<br>the internal read FIFO type of the<br>frame buffer module.                                                                                          | -                                                                                                                                                                                                                                             |

| Write FIFO type                                                                                                                                | EBR, Distributed                                                                                              | Selects EBR or Distributed RAM for<br>the internal write FIFO type of the<br>frame buffer module.                                                                                         | _                                                                                                                                                                                                                                             |

| Read FIFO depth                                                                                                                                | 32, <b>64</b> ,128,256,512                                                                                    | Selects the depth of the internal Read FIFO.                                                                                                                                              | Both Read and Write FIFO must be set to the same value. Selectable values are calculated based on video format, input pixel width, video frame width, video frame height, memory bus width, command burst count, and DDR memory burst length. |

| Selects the depth of the intern write FIFO.  Write FIFO depth 32,64,128,256,512  DDR memory burst length 2,4,8 Selects the burst length value. |                                                                                                               | Selects the depth of the internal write FIFO.                                                                                                                                             | Both Read and Write FIFO must be set to the same value. Selectable values are calculated based on video format, input pixel width, video frame width, video frame height, memory bus width, command burst count, and DDR memory burst length. |

|                                                                                                                                                |                                                                                                               |                                                                                                                                                                                           |                                                                                                                                                                                                                                               |

| Attribute           | Selectable Values | Description                                                           | Dependency on Other Attributes                                                                                                                                                  |

|---------------------|-------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command burst count | 1,2,4,8           | Selects the burst count value for working with the memory controller. | Selectable values are calculated based on <i>DDR memory burst length</i> . Only 2, 4, and 8 are available for burst length of 2, otherwise all selectable values are available. |

# 4. Signal Description

Table 4.1 lists the input and output signals for Video Frame Buffer IP Core.

Table 4.1. Video Frame Buffer IP Core Signal Description

| Port                                | 1/0 | Width                                                                                                                                                                                                                                                                                 | Clock Domain | Default | Description                                                                                                                                                                                               |

|-------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Reset                     | •   |                                                                                                                                                                                                                                                                                       | 1            | _       |                                                                                                                                                                                                           |

| rstn_i                              | In  | 1                                                                                                                                                                                                                                                                                     | _            | _       | Asynchronous active-low reset signal.                                                                                                                                                                     |

| iclk_i                              | In  | 1                                                                                                                                                                                                                                                                                     | iclk_i       | _       | Input pixel sample clock.                                                                                                                                                                                 |

| mem_clk_i                           | In  | 1                                                                                                                                                                                                                                                                                     | mem_clk_i    | _       | Memory write and read clock. This is also the clock source of the AXI4 interface.                                                                                                                         |

| pclk_i                              | In  | 1                                                                                                                                                                                                                                                                                     | pclk_i       | _       | Clock source for the AXI4-Lite and Parameter Bus Interface.                                                                                                                                               |

| oclk_i                              | In  | 1                                                                                                                                                                                                                                                                                     | oclk_i       | _       | Output sample clock, available when<br>Frame rate conversion is checked.                                                                                                                                  |

| sr_i                                | In  | 1                                                                                                                                                                                                                                                                                     | iclk_i       | _       | Active-high synchronous reset signal.                                                                                                                                                                     |

| Native Video Interface <sup>1</sup> |     |                                                                                                                                                                                                                                                                                       |              |         |                                                                                                                                                                                                           |

| frmsync_in_i                        | In  | 1                                                                                                                                                                                                                                                                                     | iclk_i       | _       | New input video frame indicator, active-high.                                                                                                                                                             |

| dvalid_in_i                         | In  | 1                                                                                                                                                                                                                                                                                     | iclk_i       | _       | Input video data valid signal, activehigh.                                                                                                                                                                |

| din_i                               | In  | When Video format = YCbCr4:2:2 and Parallel processing is checked, size is 2 × Input pixel width. When Video format = YCbCr4:4:4 or RGB and Parallel processing is checked, size is 3 × Input pixel width. When Parallel processing is unchecked, size is equal to Input pixel width. | iclk_i       | _       | Input video data in frame format.                                                                                                                                                                         |

| ready_o                             | Out | 1                                                                                                                                                                                                                                                                                     | iclk_i       | b0      | When high, indicating the Video Frame Buffer IP Core can accept more input data. The signal ready_o deasserts after last pixel of row is received or write FIFO is almost full (threshold) <sup>9</sup> . |

| dout_enable_i                       | In  | 1                                                                                                                                                                                                                                                                                     | iclk_i       | -       | Input from down-stream module to enable output data, active high.                                                                                                                                         |

| Port                    | 1/0          | Width                                                                                                                                                                                                                                                                                 | Clock Domain | Default                   | Description                                                                                      |