# Accelerometer M-A352AD10 Data Sheet

### Notice of the Document

NOTICE: PLEASE READ CAREFULLY BELOW BEFORE THE USE OF THIS DOCUMENT ©Seiko Epson Corporation 2022. The content of this document is subject to change without notice.

- 1. This document may not be copied, reproduced, or used for any other purposes, in whole or in part, without the consent of Seiko Epson Corporation("Epson").

- 2. Before purchasing or using Epson products, please contact with our sales representative for the latest information and be always sure to check the latest information published on Epson's official web sites and sources.

- 3. Information provided in this document such as application circuits, programs, usage, etc., are for reference purpose only. Please use the application circuits, programs, usage, etc. in the design of your equipment or systems at your own responsibility. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

- 4. Epson is committed to constantly improving quality and reliability, but semiconductor products in general are subject to malfunction and failure. In using Epson products, you shall be responsible for safe design in your products; your hardware, software and systems are designed enough to prevent any harm or damages to life, health or property even if any malfunction or failure might be caused by Epson products. In designing of your products with using Epson products, please be sure to check and comply with the latest information regarding Epson products (this document, specifications, data sheets, manuals, Epson's web site, etc.). When using the information included in the above materials such as product data, chart, technical contents, programs, algorithms and application circuit examples, you shall evaluate your products both in stand-alone basis and within your overall systems. You shall be solely responsible for deciding whether or not to adopt and use Epson products.

- 5. Epson has prepared this document and programs provided in this document carefully to be accurate and dependable, but Epson does not guarantee that the information and the programs are always accurate and complete. Epson assumes no responsibility for any damages which you incurred by due to misinformation in this document and the programs.

- 6. No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is allowed.

- 7. Epson products have been designed, developed and manufactured to be used in general electronic applications (office equipment, communications equipment, measuring instruments, home electronics, etc.) and applications individually listed in this document ("General Purpose"). Epson products are NOT intended for any use beyond the General Purpose that requires particular/higher quality or reliability in order to refrain from causing any malfunction or failure leading to harm to life, health or serious property damage or severe impact on society, including, but not limited to listed below. Therefore, you are advised to use Epson products only for the General Purpose. Should you desire to buy and use Epson products for the particular purpose other than the General Purpose, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any particular purpose.

[Particular purpose]

Space equipment (artificial satellites, rockets, etc.)

Transportation vehicles and their control equipment (automobiles, aircraft, trains, ships, etc.)

Medical equipment (other than applications individually listed in this document) / Relay equipment to be placed on sea floor Power station control equipment / Disaster or crime prevention equipment / Traffic control equipment / Financial equipment

Other applications requiring similar levels of reliability as the above

- 8. Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for developing military weapons of mass destruction, military purpose use, or any other military applications. If exporting Epson products or our associated technologies, you shall comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A (EAR) and other export-related laws and regulations in Japan and any other countries and follow the required procedures as provided by the relevant laws and regulations.

- 9. Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document.

- 10. Epson assumes no responsibility for any damages (whether direct or indirect) incurred by any third party that you assign, transfer, loan, etc., Epson products.

- 11. For more details or other concerns about this document, please contact our sales representative.

- 12. Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

2022.08

© Seiko Epson Corporation 2022, All rights reserved.

# **Table of Contents**

| 1. | G                 | eneral Description                                   | 1  |

|----|-------------------|------------------------------------------------------|----|

| 2. | Sr                | pecifications                                        | 2  |

| 2  | 1<br>2.1          | · Absolute Maximum Ratings                           |    |

| 2  | 2.2               | Recommended Operating Condition                      |    |

| 2  | 2.3               | Performance & Electrical Specifications              |    |

|    | 2.4               | Timing Specifications                                |    |

|    | 2.5               | Socket Pin Layout and Functions                      |    |

|    | _                 | lechanical Dimensions                                |    |

|    |                   |                                                      |    |

|    | 3.1               | Outline Dimensions                                   |    |

| 4. | _                 | ypical Performance Characteristics                   |    |

| 5. | Ва                | asic Operation                                       | 11 |

| 5  | 5.1               | Connection To Host                                   | 11 |

| 5  | 5.2               | Operation Mode                                       | 12 |

| 5  | 5.3               | Functional Block                                     | 13 |

| 5  | 5.4               | Data Output Timing                                   | 14 |

| 5  | 5.5               | Data Ready Signal                                    | 14 |

| 5  | 5.6               | Sampling Counter                                     | 15 |

| 5  | 5.7               | Self Test                                            | 15 |

| 5  | 5.8               | Threshold Detection of Accelerometer                 | 16 |

| 5  | 5.9               | External Trigger Input                               | 16 |

| 5  | 5.10              | Checksum                                             | 17 |

| 5  | 5.11              | Automatic Start (For UART Auto Sampling Only)        | 18 |

| 5  | 5.12              |                                                      |    |

| 5  | 5.13              | Tilt Output / Combination Output                     | 18 |

| 5  | 5.14              | ·                                                    |    |

| 5  | 5.15              |                                                      |    |

| 5  | 5.16              |                                                      |    |

|    |                   | FILTER                                               |    |

|    |                   | 17.1 FIR Kaiser Filter                               |    |

|    |                   | 17.2 User Defined FIR Filter                         |    |

|    |                   | 17.3 Notes For FIR Filter Usage                      |    |

|    |                   |                                                      |    |

| 6. | Di                | igital Interface                                     |    |

| 6  | 3.1               | SPI Interface                                        |    |

|    | 6.1               | 1.1 SPI Read Timing (Normal Mode)                    |    |

|    | -                 | 1.3 SPI Read Timing (Normal Mode)                    |    |

| 6  | 5.2               |                                                      |    |

|    | 6.2               |                                                      |    |

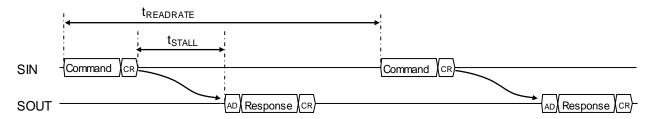

|    | -                 | 2.2 UART Read Timing (Burst Mode)                    |    |

|    |                   | 2.3 UART Write Timing                                |    |

| ,  | 6.2<br><b>3.3</b> | 2.4 UART Auto Sampling Operation  Data Packet Format |    |

|    | _                 |                                                      |    |

|    |                   | ser Registers                                        |    |

|    | '.1<br>· -        | BURST Register (Window 0)                            |    |

| 7  | <b>7.2</b>        | MODE_CTRL Register (Window 0)                        | 40 |

| 7.3         | B DIAG_STAT Register (Window 0)                           | 41             |

|-------------|-----------------------------------------------------------|----------------|

| 7.4         | 4 FLAG(ND/EA) Register (Window 0)                         | 42             |

| 7.5         | 5 COUNT Register (Window 0)                               | 43             |

| 7.6         | TEMP Register (Window 0)                                  | 44             |

| 7.7         | ,                                                         |                |

| 7.8         | ,                                                         |                |

| 7.9         | • ,                                                       |                |

| 7.1         | _ ,                                                       |                |

| 7.1         | _ ,                                                       |                |

| 7.1         |                                                           |                |

| 7.1         | _ , ,                                                     |                |

| 7.1         | _ ,                                                       |                |

|             | _ ,                                                       |                |

| 7.1         |                                                           |                |

| 7.1         | = ,                                                       |                |

| 7.1         |                                                           |                |

| 7.1         |                                                           |                |

| 7.1         | _                                                         |                |

| 7.2         |                                                           |                |

| 7.2         |                                                           |                |

|             | 22 YA_OFFSET Register (Window 1)                          |                |

|             | 23 ZA_OFFSET Register (Window 1)                          |                |

|             | 24 XA_ALARM Register (Window 1)                           |                |

|             | 25 YA_ALARM Register (Window 1)                           |                |

|             | 26 ZA_ALARM Register (Window 1)                           |                |

| 7.2         | PROD_ID Register (Window 1)                               | 58             |

| 7.2         | 28 VERSION Register (Window 1)                            | 58             |

| 7.2         | 29 SERIAL_NUM Register (Window 1)                         | 58             |

| 7.3         | 30 WIN_CTRL Register (Window 0,1)                         | 59             |

| 8. \$       | Sample Program Sequence                                   | 60             |

|             | SPI Sequence                                              | 00             |

| 8           | 8.1.1 Power-on Sequence (SPI)                             | 60             |

|             | 8.1.2 Register Read and Write (SPI)                       |                |

|             | 8.1.3 Sampling Data (SPI)                                 |                |

|             | 8.1.4 Selftest (SPI)                                      |                |

|             | 8.1.6 Software Reset (SPI)                                |                |

| 8           | 8.1.7 Flash Backup (SPI)                                  | 62             |

|             | 8.1.8 Flash Reset (SPI)                                   |                |

|             | 8.1.9 Filter Setting (SPI)                                |                |

|             | 8.1.10 User Defined FIR Filter Coefficients Setting (SPI) |                |

|             | 8.1.12 Reduced Noise Floor Condition Setting (SPI)        |                |

|             | 8.1.13 Bias Offset Setting (SPI)                          | 65             |

| 8           | 8.1.14 Alarm Threshold Setting (SPI)                      |                |

| 8.2         |                                                           | 67             |

|             | 8.2.1 Power-on Sequence (UART)                            |                |

| Ö           |                                                           | ر ب <i>ب</i>   |

|             | 8.2.2 Register Read and Write (UART)                      |                |

| 8           | 8.2.2 Register Read and Write (UART)                      | 67             |

| 8<br>8<br>8 | 8.2.3 Sampling Data (UART)                                | 67<br>68<br>69 |

|     | 8.2.7                | Flash Backup (UART)                                 | 69 |  |  |

|-----|----------------------|-----------------------------------------------------|----|--|--|

|     | 8.2.8                | Flash Reset (UART)                                  | 70 |  |  |

|     | 8.2.9                | Filter Setting (UART)                               |    |  |  |

|     | 8.2.10               | User Defined FIR Filter Coefficients Setting (UART) | 70 |  |  |

|     |                      | Sleep Sequence (UART)                               |    |  |  |

|     |                      | Reduced Noise Floor Codition Setting (UART)         |    |  |  |

|     | 8.2.13               | Bias Offset Setting (UART)                          | 72 |  |  |

|     | 8.2.14               | Alarm Threshold Setting (UART)                      | 72 |  |  |

|     | 8.2.15               | Auto Start (UART only)                              | 73 |  |  |

| 9.  | Handl                | ing Notes                                           | 74 |  |  |

| 9   | ).1 Caı              | utions for Use                                      | 74 |  |  |

| 9   | ).2 Caı              | utions for Storage                                  | 74 |  |  |

| 9   | .3 Oth               | ner Cautions                                        | 75 |  |  |

| 9   |                      | nited Warranty                                      |    |  |  |

| 10. | . Part N             | lumber / Ordering Info                              | 76 |  |  |

|     | 11. Evaluation Tools |                                                     |    |  |  |

|     |                      |                                                     |    |  |  |

| Re  | vision               | History                                             | 77 |  |  |

# 1. General Description

The M-A352 is a three axis digital output accelerometer featuring ultra-low noise, high stability, and low power consumption using fine processing technology of Quartz. Incorporating both high accuracy and durability, the versatile M-A352 is well suited to a wide-range of challenging applications such as SHM, seismic observation, condition monitoring for industrial equipment, and pose detection for industrial machinery (i.e. construction machinery/attachments, agricultural machinery/ implements, robots).

### **Features**

- Ultra-low noise : 0.2µG/√Hz typ.

- Selectable output format: Acceleration / Tilt Angle

- Selectable interface: SPI / UART

- Programmable low-pass digital filters

- · Low jitter external trigger function for synchronous sampling

- Solid metallic case (Aluminum, size : 48mm x 24mm x 16mm, weight: 25g)

# **Applications**

- Structural health monitor

- Seismic measurements

- Vibration control and stabilization

- Motion analysis and control

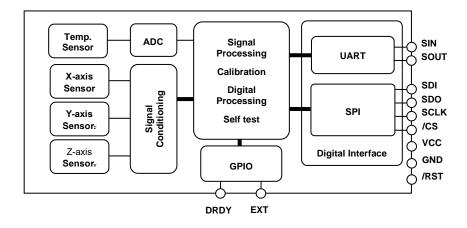

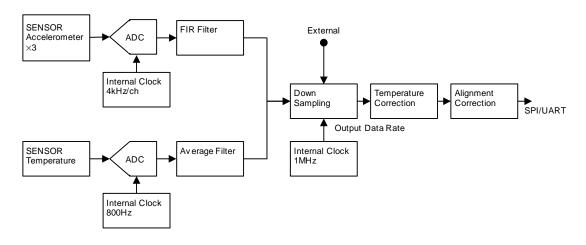

# **Functional Block Diagram**

Figure 1.1 Block Diagram

# 2. Specifications

# 2.1 Absolute Maximum Ratings

Table 2.1 Absolute Maximum Rating

| Parameter                        | Min  | Тур | Max     | Unit |

|----------------------------------|------|-----|---------|------|

| VCC to GND                       | -0.3 |     | 3.6     | V    |

| Digital Input Voltage to GND     | -0.3 |     | VCC+0.3 | V    |

| Digital Output Voltage to GND    | -0.3 |     | VCC+0.3 | V    |

| Storage Temperature Range        | -40  |     | 85      | °C   |

| Acceleration (Half-sine 0.2msec) |      |     | 1,000   | G    |

<sup>\*1</sup> Precautions concerning ESD.

Electrostatic discharge (ESD) may damage this product.

Please take appropriate measures against electrostatic discharge (ESD) when storing and handling this product.

Damage by electrostatic discharge (ESD) can cause very small performance deterioration, partial malfunction, or complete breakdown.

This is a high precision product and may not conform to specification even with very small performance degradation due to improper usage or handling.

# 2.2 Recommended Operating Condition

Table 2.2 Recommended Operating Conditions

| Parameter                     | Condition                                          | Min  | Тур | Max      | Unit |

|-------------------------------|----------------------------------------------------|------|-----|----------|------|

| VCC to GND                    |                                                    | 3.15 | 3.3 | 3.45     | V    |

| Digital Input Voltage to GND  |                                                    | GND  |     | VCC      | V    |

| Digital Output Voltage to GND |                                                    | -0.3 |     | VCC +0.3 | V    |

| Operating Temperature Range   |                                                    | -30  |     | 85       | °C   |

| Start up Time                 | Power-on to start output                           |      |     | 900      | ms.  |

|                               | Warm-up period for best performance.               |      | _   |          |      |

|                               | Bias stabilization against thermal shock = enable  |      | 5   |          | min. |

|                               | Warm-up period for best performance.               |      | 45  |          |      |

|                               | Bias stabilization against thermal shock = disable | 15   |     | min      |      |

2

# 2.3 Performance & Electrical Specifications

Table 2.3 Sensor Specification

Condition: T<sub>A</sub>=-30°C to +85°C, VCC=3.15V~3.45V, ≤±1G, Normal Operation Mode, unless otherwise noted.

| Parameter                                       | C=3.15V~3.45V, ≤±1G, Normal Opera<br>Test Conditions / Comments | Min      | Typ        | Max              | Unit                    |

|-------------------------------------------------|-----------------------------------------------------------------|----------|------------|------------------|-------------------------|

| ACCELERATION                                    | rest conditions / comments                                      | 141111   | 1,75       | WIGA             | TOTILE.                 |

| Sensitivity                                     |                                                                 |          |            |                  |                         |

| Output Range                                    | f = DC ~ 460Hz                                                  |          |            | ±15              | G                       |

| Scale Factor                                    | 2 <sup>-24</sup> G/LSB                                          |          | 0.06       |                  | μG/LSB                  |

| Sensitivity Error                               | 25°C, ≤ 1G                                                      |          | ±500       |                  | ×10 <sup>-6</sup> (ppm) |

| Nonlinearity                                    | ≤ 1G, Best fit straight line, RT                                |          | 2000       | ±0.03            | % of FS                 |

| Cross Axis Sensitivity                          | = 10, Bost in straight into, 111                                |          | ±0.2       | 0.00             | %                       |

| Misalignment                                    | 25°C                                                            |          | _0.2       | ±0.1             | Deg                     |

| Bias                                            |                                                                 |          |            |                  | 1209                    |

| Initial Error                                   | 25°C                                                            |          |            | ±2               | mG                      |

|                                                 | TA=25°C and VCC=3.3V for one                                    |          |            |                  |                         |

| Bias Repeatability                              | year after shipment                                             |          | 3          |                  | mG                      |

| Bias Temperature Error                          | 25°C                                                            |          |            | ±2               | mG                      |

| Temperature Sensitivity                         |                                                                 |          | ±0.1       |                  | mG/°C                   |

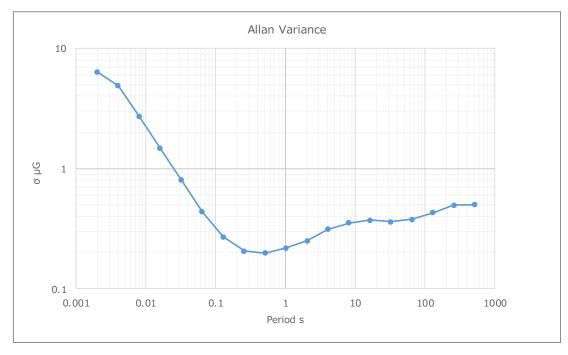

| Bias Instability                                | Allan variance, Average                                         |          | 0.2        |                  | μG                      |

| Velocity Random Walk                            | Average                                                         |          | 1.2E-4     |                  | (m/sec)/√hr             |

| Noise                                           |                                                                 |          |            |                  |                         |

| Noise Density                                   | 25°C, Avg, f = 0.5Hz ~ 6Hz                                      |          | 0.2        | 0.7              | μG/√Hz, rms             |

| Cantilever<br>Resonance Frequency <sup>*1</sup> | 25°C, VCC3.3V                                                   |          | 850        |                  | Hz                      |

| VRC                                             | at 50Hz, 25°C, VCC3.3V                                          |          |            | ±50              | μG/G <sup>2</sup>       |

| Frequency Property                              |                                                                 | •        |            |                  |                         |

| -6 dB Bandwidth                                 | User selectable                                                 | 9        |            | 460              | Hz                      |

| TILT ANGLE                                      |                                                                 |          |            |                  |                         |

| Sensitivity                                     |                                                                 |          |            |                  |                         |

| Dynamic Range                                   | f = DC ~ 460Hz                                                  |          |            | ±1.0472<br>(±60) | rad<br>(deg)            |

| Scale Factor                                    | 2 <sup>-29</sup> rad/LSB                                        |          | 0.002      | ,                | µrad/LSB                |

| Nonlinearity                                    | 25°C, ±45deg                                                    |          |            | ±0.03            | % of FS                 |

|                                                 |                                                                 |          |            | ±1.745           | mrad                    |

| Misalignment                                    | 25°C                                                            |          |            | $(\pm 0.1)$      | (deg)                   |

| Bias                                            |                                                                 |          |            |                  |                         |

| Piga Panastahilitu                              | TA=25°C and VCC=3.3V for one                                    |          | ±3         |                  | mrad                    |

| Bias Repeatability                              | year after shipment                                             |          | (±0.17)    |                  | (deg)                   |

| Bias Temperature Error                          | 25°C                                                            |          |            | ±2<br>(±0.11)    | mrad<br>(deg)           |

| Noise                                           |                                                                 | <u> </u> |            | (==:::)          | 1(409)                  |

| Noise Density                                   | 25°C, Avg, f = 0.5Hz ~ 6Hz                                      |          | 0.2        | 0.7              | µrad/√Hz, rms           |

| TEMPERATURE SENSOR                              | 1,                                                              |          |            |                  | 11                      |

| Output Range                                    |                                                                 | -30      |            | 85               | °C                      |

| Scale Factor *2                                 | Output=2634(0x0A4A) at 25°C                                     | 1        | -0.0037918 |                  | °C/LSB                  |

| RELIABILITY                                     | 11. F. 11. 21. (1.10. 1.11.) 41. 20                             |          |            |                  |                         |

| MTBF*3                                          | JIS-C5003 TA=25°C                                               | 87,600   |            |                  | hour                    |

| ·····                                           |                                                                 | 0.,000   | 1          |                  | · ·                     |

<sup>&</sup>lt;sup>\*1</sup> Please make sure that a vibration on this product around the resonance frequency does not exceed 100 mG. Please take an appropriate action (e.g. installing a damper mechanism) if it exceeds 100 mG.

<sup>&</sup>lt;sup>\*2</sup> This is a reference value used for the internal temperature correction, and is not guaranteed to accurately output the interior temperature.

$<sup>^{*3}</sup>$  The MTBF is an estimated value derived from the result of high temperature operation with a system requirement of TA=25 $^{\circ}$ C and a 60% reliability level.

Note) The values in the specifications are based on the data calibrated at the factory. The values may change according to the way the product is used.

Note) The Max/Min value is the maximum/minimum value of the design or factory shipment examination, unless otherwise specified. Note) The calibrated standard 1G gravitational acceleration value is 9.80665 m/s²

Table 2.4 Interface Specification

T<sub>A</sub>=25°C, VCC=3.3V, unless otherwise noted

| Table 2.4 Interface ope                    | I                                                                  | ĺ       | r e  | Terwise not | 1    |

|--------------------------------------------|--------------------------------------------------------------------|---------|------|-------------|------|

| Parameter                                  | Test Conditions                                                    | Min     | Тур  | Max         | Unit |

| LOGIC INPUTS*1                             |                                                                    |         |      |             |      |

| Positive Trigger Voltage                   | Schmitt                                                            | 1.37    |      | 2.29        | V    |

| Negative Trigger Voltage                   | Schmitt                                                            | 0.69    |      | 1.24        | V    |

| Hysteresis Voltage                         | Schmitt                                                            | 0.53    |      |             | V    |

| Input Current, li                          | VI=Vcc or GND                                                      |         | 0.5  |             | μΑ   |

| Input Capacitance, Ci                      |                                                                    |         | 2.5  |             | pF   |

| RST Low Pulse Width                        |                                                                    | 100     |      |             | ms   |

| Pull-up resistor                           |                                                                    |         | 220  |             | kΩ   |

| Ext.Trigger Input Width, tetw              |                                                                    | 1       |      |             | μs   |

| Ext.Trigger Input Cycle, tetc              |                                                                    | 1       |      | 20          | ms   |

| Ext.Trigger Jitter, t <sub>ETJ</sub>       | Ext.Trigger input to resampling's completion                       | 0       |      | 5           | μs   |

| Ext.Trigger Delay Time*3, t <sub>ETD</sub> | Ext.Trigger input to DRDY asserted Long-period filter is disable   |         |      | 740         | μs   |

| Internal Timer Delay Time*3, titD          | Internal Timer input to DRDY asserted Long Period Filter = disable |         |      | 430         | μs   |

| DIGITAL OUTPUTS <sup>*1</sup>              |                                                                    |         |      |             |      |

| Output High Voltage, VOH                   | ISOURCE=20µA                                                       | VCC-0.1 |      |             | V    |

| Output Low Voltage, VOL                    | ISINK=20µA                                                         |         |      | 0.1         | V    |

| FUNCTIONAL TIMES*2                         | Time until data is available                                       |         |      |             |      |

| Power-On Start-Up Time                     |                                                                    |         |      | 900         | ms   |

| Reset Recovery Time                        |                                                                    |         |      | 970         | ms   |

| Flash Backup Time                          |                                                                    |         |      | 310         | ms   |

| Flash Reset Time                           |                                                                    |         |      | 1900        | ms   |

| Self Test Time                             | ACC Test, TEMP Test, VDD Test                                      |         |      | 200         | ms   |

|                                            | Sensitivity Test / axis                                            |         | 10   | 40          | s    |

|                                            | Flash Test                                                         |         |      | 5           | ms   |

| Filter Setting Time                        | Built-In FIR Filter                                                |         |      | 4           | ms   |

| _                                          | User FIR Filter                                                    |         |      | 100         | ms   |

| User Filter Write Cycle, tuwc              |                                                                    |         |      | 7           | ms   |

| User Filter Read Cycle, turc               |                                                                    |         |      | 500         | us   |

| Sleep Wake-up Time, twakeUp                |                                                                    |         |      | 16          | ms   |

| OUTPUT DATA RATE                           |                                                                    | 50      |      | 1,000       | Sps  |

| Clock Accuracy                             |                                                                    |         |      | ±0.001      | %    |

| POWER SUPPLY                               | Operating voltage range, VCC                                       | 3.15    | 3.3  | 3.45        | V    |

| Power Supply Current                       | Standard noise floor condition,<br>200Sps, Average                 |         | 13.2 | 18.0        | mA   |

|                                            | Reduced noise floor condition,<br>200Sps, Average                  |         | 16.2 | 20.0        | mA   |

|                                            | Sleep mode                                                         |         | 1.3  | 2.0         | mA   |

| t.                                         |                                                                    | •       |      | <u> </u>    | •    |

Note) These parameters are not included in the factory test items but these characteristics are confirmed.

<sup>\*1)</sup> Digital I/O signal pins operate at 3.3V inside the unit. All digital I/O signal pins (except RST) can tolerate 5V input.

<sup>\*2)</sup> These specifications do not include the effect of temperature fluctuation and response time of the internal filter.

<sup>\*3)</sup> It is not included the group delay of the built-in filter.

# 2.4 Timing Specifications

T<sub>A</sub>=25°C, VCC=3.3V, unless otherwise noted

| Parameter      | Description                           | Min  | Тур | Max | Unit |

|----------------|---------------------------------------|------|-----|-----|------|

| NORMAL MODE    |                                       |      |     |     |      |

| fSCLK          |                                       | 0.01 |     | 2.0 | MHz  |

| tSTALL         | Stall period between data             | 20   |     |     | μs   |

| tWRITERATE     | Write rate                            | 40   |     |     | μs   |

| tREADRATE      | Read rate                             | 40   |     |     | μs   |

| BURST MODE     |                                       |      |     |     |      |

| fSCLK          |                                       | 0.01 |     | 2.0 | MHz  |

| tSTALL1        | Stall period between data             | 45   |     |     | μs   |

| tSTALL2        | Stall period between data             | 0    |     |     | μs   |

| tREADRATE2     | Read rate                             | 8    |     |     | μs   |

| COMMON         |                                       |      |     |     |      |

| tCS            | Chip select to clock edge             | 10   |     |     | ns   |

| tDAV           | SO valid after SCLK edge              |      |     | 80  | ns   |

| tDSU           | SI setup time before SCLK rising edge | 10   |     |     | ns   |

| tDHD           | SI hold time after SCLK rising edge   | 10   |     |     | ns   |

| tSCLKR, tSCLKF | SCLK rise/fall times                  |      |     | 20  | ns   |

| tDF, tDR       | SO rise/fall times                    |      |     | 20  | ns   |

| tSFS           | high after SCLK edge CS               | 80   |     |     | ns   |

Note) These parameters are not included in the factory test items but these characteristics are confirmed.

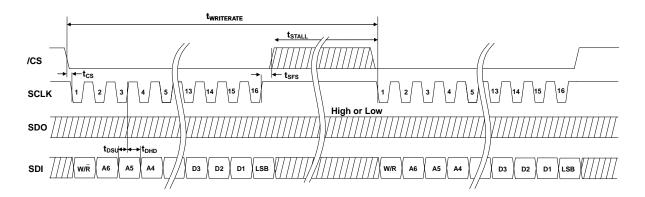

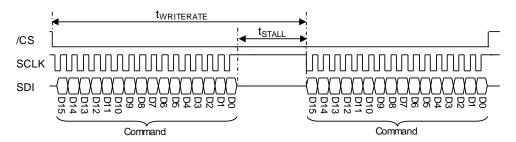

Figure 2.1 SPI Write Timing and Sequence

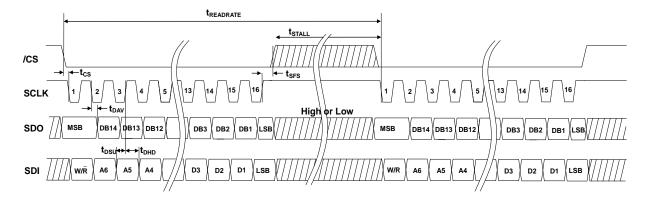

Figure 2.2 SPI Read Timing and Sequence

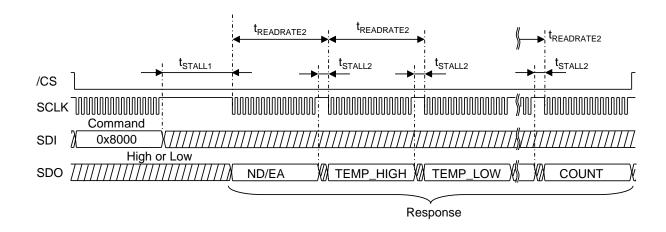

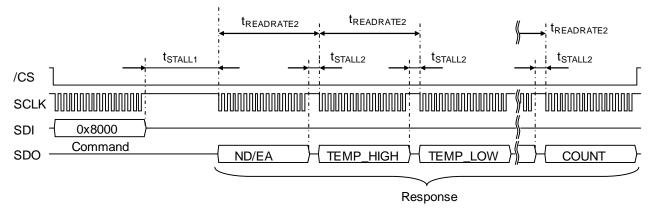

Figure 2.3 SPI Read Timing and Sequence (BURST MODE)

# Socket Pin Layout and Functions

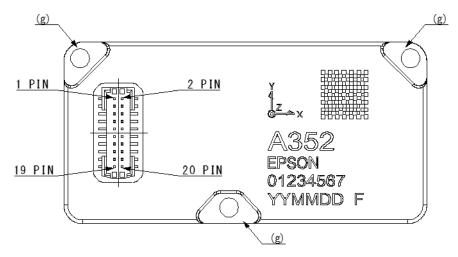

Figure 2.4 Socket Pin Assignment

Table 2.6 Pin Function Descriptions

| Pin No.     | Mnemonic | Type <sup>*1</sup> | Description                                               |

|-------------|----------|--------------------|-----------------------------------------------------------|

| 1           | SCLK     | I                  | SPI Serial Clock *2                                       |

| 2           | SDO      | 0                  | SPI Data Output *2                                        |

| 5           | SDI      | I                  | SPI Data Input *2                                         |

| 6           | /CS      | I                  | SPI Chip Select *2                                        |

| 7           | SOUT     | 0                  | UART Data Output *2                                       |

| 9           | SIN      | I                  | UART Data Input *2                                        |

| 13          | DRDY     | 0                  | Data Ready *3                                             |

| 14          | EXT      | I                  | External Trigger Input <sup>*4</sup> (Sleep Wakeup Input) |

| 16          | /RST     | I                  | Reset *5                                                  |

| 10,11,12    | VCC      | S                  | Power Supply 3.3V                                         |

| 3,4,8,15    | GND      | S                  | Ground <sup>*6</sup>                                      |

| 17,18,19,20 | NC       | N/A                | Do Not Connect                                            |

Note) All input pins are weak pull-up inside this product.

<sup>\*1)</sup> Pin Type I:Input, O:Output, I/O:Input/Output, S:Supply, N/A:Not Applicable \*2) Please connect either SPI or UART. Connecting both SPI and UART at the same time may cause malfunction. Please connect unused input pins to VCC via a resistor.

<sup>\*3)</sup> Please refer to DRDY\_ON of register: MSC\_CTRL [0x02 (W1)], bit [2] for pin function selection. \*4) Please refer to EXT\_SEL of register: MSC\_CTRL [0x02 (W1)], bit [6] for pin function selection.

<sup>\*5)</sup> When RST pin is not used, fix it to High (VCC) level via a resistor.

<sup>\*6)</sup> Please connect (g) Frame Ground to any GND pin (No.3, 4, 8, 15).

# 3. Mechanical Dimensions

# 3.1 Outline Dimensions

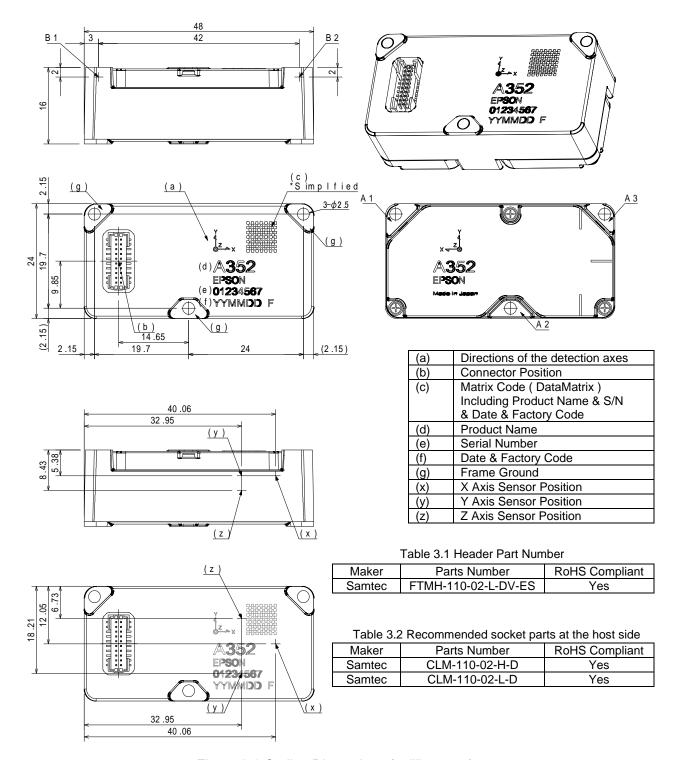

Figure 3.1 Outline Dimensions (millimeters)

<sup>\*1)</sup> This product is calibrated based on the surfaces A1, A2, A3, and B1, B2.

<sup>\*2)</sup> In order to demonstrate the performance of the product properly, please fix surfaces A1, A2, A3 to rugged parts with M2 screw.

<sup>\*3)</sup> When high connection reliability is required, please tighten this product together with the board on which the connector is mounted.

# 4. Typical Performance Characteristics

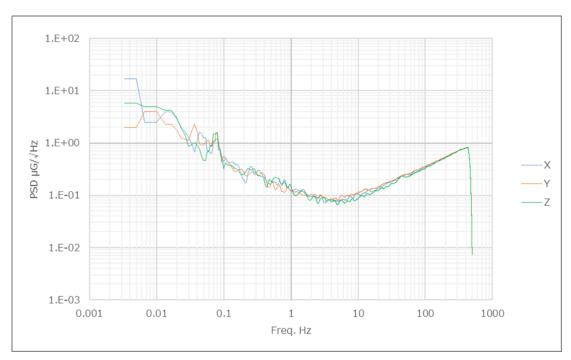

Figure 4.1 Noise Density Characteristic of Accelerometer (Standard Noise Floor Condition)

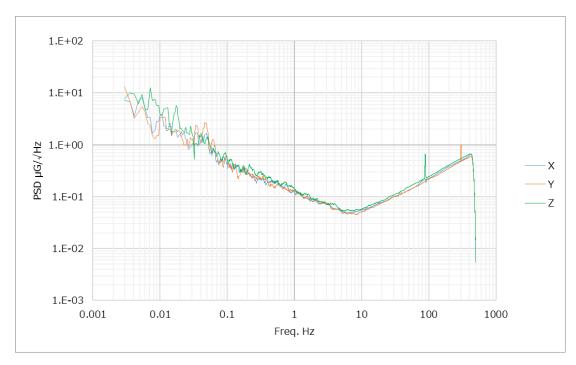

Figure 4.2 Noise Density Characteristic of Accelerometer (Reduced Noise Floor Condition)

Figure 4.3 Allan Variance Characteristic of Accelerometer(Standard Noise Floor Condition)

The above graph is a typical example of the product characteristics, and is not guaranteed by the specification.

# 5. Basic Operation

# 5.1 Connection To Host

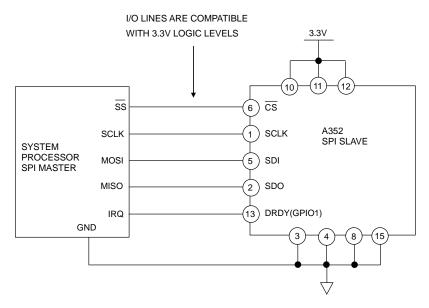

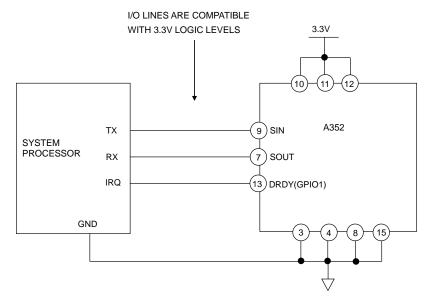

The device supports two types of serial interface:UART and SPI. Only one interface type should be selected and used at any given time (not both). The example wiring connection is provided below as a reference.

Figure 5.1 SPI Connection

Figure 5.2 UART Connection

The device performance may be affected by signal overshoot or undershoot of the host interface. Care must be taken minimize signal integrity issues when designing the electrical interface so that the noise level is reduced as much as possible to within the tolerance of the communication timing specification.

# 5.2 Operation Mode

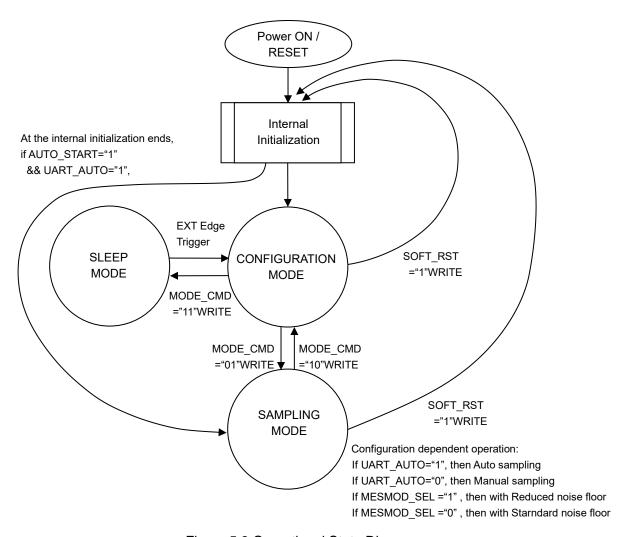

The following three operational modes are available in the device.

- (1) Configuration mode

- (2) Sampling mode

Sampling condition

- Manual sampling

- Auto sampling (UART Only)

- (3) Sleep mode

### Measurement condition

- Standard noise floor

- Reduced noise floor

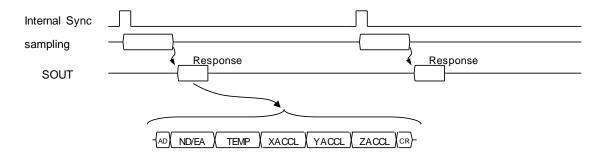

In the Sampling mode, the device can operate with a standard noise floor condition or a reduced noise floor condition. When Auto sampling is active, all sensor outputs are sent automatically at the programmed output data rate without the request from the Host (only available with a UART connection). These conditions can be switched between Manual sampling and Auto sampling by **UART\_AUTO**, and between a Standard noise floor and a Reduced noise floor by **MESMOD SEL** (see Figure 5.3).

Immediately after a hardware reset or power-on, internal initialization starts. During the internal initialization, all the register values and states of external pins are undefined. After the internal initialization is completed, the device goes into Configuration mode automatically, except for the UART version when AUTO\_START and UART\_AUTO sampling are both enabled (the device then goes into Sampling mode automatically). To change the operation mode, write to **MODE\_CMD** (MODE\_CTRL[0x02(W0)] bit[9:8]) (\*1) and make various changes to the sensor setting in Configuration mode (\*2). After configuration is completed, go to Sampling mode to read out the temperature and acceleration data. When shifting to the sleep mode, the internal circuit operation stops and the current consumption during standby can be reduced. The return time from sleep mode can be shorter than the initialization time from startup. The device can wake up from sleep mode by detecting an edge trigger on the EXT pin.

By executing software reset (Register: GLOB\_CMD [0x0A (W1)], write 1 to SOFT\_RST in bit [7]), internal initialization operation is executed regardless of the current operation mode and the system enters Configuration mode.

When the UART interface is used, writing to **UART\_AUTO** (UART\_CTRL[0x08(W1)] bit[0]) can switch between the Manual sampling and the Auto sampling<sup>(\*3)</sup>. When SPI interface is used, Manual sampling must be selected. Otherwise, the device does not work properly.

\*1) The following explains register notation used in this document.

For example, MODE\_CTRL[0x02(W0)] bit[9:8] refers to:

- MODE\_CTRL: Register Name

- [0x02(W0)] : First number is the Register Address, (W0) refers to Window Number "0"

- bit[9:8] : Bits from 9 to 8

- \*2) Make sure that the device is in Configuration mode when you write to the registers to configure operational settings. In Sampling mode, writing to registers is ignored **except** the following cases.

- Writing to MODE CMD (MODE CTRL[0x02(W0)] bit[9:8])

- Writing to SOFT\_RST (GLOB\_CMD[0x0A(W1)] bit[7])

- Writing to WINDOW\_ID (WIN\_CTRL[0x7E(W0/W1)] bit[7:0])

- \*3) While the device is with UART Auto sampling and sensor sampling is active, register read access is not supported. Otherwise, the sampling data transmitted with the UART Auto sampling will be corrupted by the response data from the register read.

Figure 5.3 Operational State Diagram

# 5.3 Functional Block

Figure 5.4 Functional Block Diagram

# 5.4 Data Output Timing

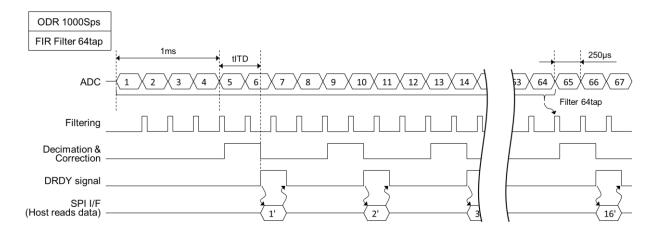

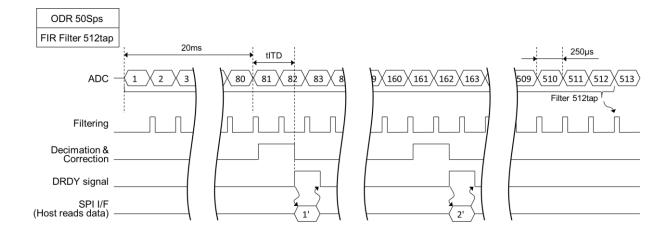

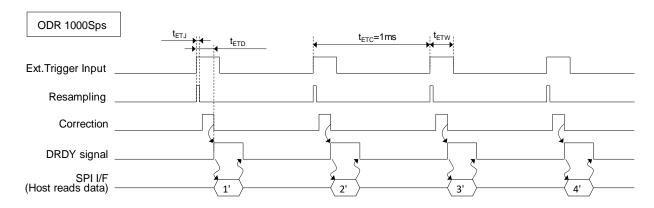

Figure 5.5 Data Output Timing - ODR 1,000 Sps

Figure 5.6 Data Output Timing - ODR 50 Sps

# 5.5 Data Ready Signal

The Data Ready Signal is asserted when one sampling cycle completes and registers are updated with new sensor values. When the sensor values are read out, the Data Ready signal becomes negated. With UART AUTO sampling enabled, the Data Ready signal becomes negated just before data is output.

The Data Ready Signal is output to the DRDY pin when the **DRDY\_ON** (MSC\_CTRL[0x02(W1)] bit[2]) is set to "1". The polarity of the signal can be changed by the **DRDY\_POL** of MSC\_CTRL[0x02(W1)] bit[1] register.

The Data Ready Signal is the logical sum of all the ND flags corresponding to each sensor value. If all the ND flags are disabled in the **ND\_EN** (SIG\_CTRL[0x00(W1)] bit[15,11:9]), the Data Ready will not be asserted. On the other hand, if all the sensor values enabled in the **ND\_EN** (SIG\_CTRL[0x00(W1)] bit[15,11:9]) are not read out, the Data Ready signal is kept asserted and never becomes negated.

Figure 5.7 Data Ready Signal Timing

# 5.6 Sampling Counter

By reading COUNT[0x0A(W0)] register, the counter value, which is incremented based on the sampling completion timing of the internal A/D converter, can be read. The count interval is 250usec/count and is based on the precision of the internal reference oscillator (crystal).

Additionally, during UART/SPI burst mode or with UART Auto sampling, the counter value can be included in the response format by setting the **COUNT\_OUT** (BURST\_CTRL[0x0C(W1)] bit[1]). For information about the response format, see 6.3 DATA PACKET FORMAT.

### 5.7 Self Test

This product has the following self test functions. For information about the execution time of the self test, see "Self Test Time" in Table 2.4 Interface Specifications.

### Acceleration Value

This self test function can be used to check whether the outputs of the accelerometer are within the pre-determined range and operating properly.

The test result is OK if the absolute value of the output as a three dimensional vector is within the gravitational acceleration(0.8G to 1.2G).

When performing the self test, make sure the device does not move during the test and the test is conducted in a place without vibration.

To use this function, execute **ACC\_TEST** of register: MSC\_CTRL[0x02(W1)] bit[10], check the **ACC\_ERR\_ALL** of register DIAG\_STAT[0x04(W0)] bit[1] for diagnostic result.

### Acceleration Sensitivity

This self test function can be used to determine whether the acceleration sensitivity error is within  $\pm$  2.5 %. It takes up to 40 sec (typ.10 sec) per axis for the diagnostic.

To use this function, execute **SENS\_TEST** of register: MSC\_CTRL[0x02(W1)],bit[14:12], check the **SENS\_ERR** of register DIAG STAT[0x04(W0)],bit[11:10] for diagnostic result.

Note) It may lead to a diagnostic result of "unable to be determined" or may result in an inaccurate diagnostic when there are sudden changes in vibration level during the execution or the vibration level is lower than the noise floor of this product (refer to Section 4 Typical Performance Characteristics).

### Temperature Value

Determine whether the temperature sensor is operating properly.

To use this function, execute **TEMP\_TEST** of register: MSC\_CTRL [0x02 (W1)], bit [9], check the **TEMP\_ERR** of register: DIAG\_STAT [0x04 (W0)], bit [9] for diagnostic result.

### Power Supply Voltage Level

Determine whether the power supply voltage is within 3.0V to 3.6V.

To use this function, execute **VDD\_TEST** of register: MSC\_CTRL[0x02(W1)],bit[8], check the **VDD\_ERR** of register: DIAG\_STAT[0x04(W0)],bit[8] for diagnostic result.

### Nonvolatile memory

Determine whether the Nonvolatile memory is operating properly by consistency test of data in nonvolatile memory.

To use this function, execute **FLASH\_TEST** of register: MSC\_CTRL[0x02(W1)],bit11], check the **FLASH\_ERR** of register: DIAG\_STAT[0x04(W0)],bit[2] for diagnostic result.

### 5.8 Threshold Detection of Accelerometer

When the acceleration value exceeds the preset threshold, an alarm is indicated. The threshold can be set for each 1G step within the range of 0 to 15 G upper limit and -15 G to 0 G lower limit. At the time of shipment, the upper limit + 15 G and the lower limit -15 G are set

The alarm threshold is set in the registers: XA\_ALARM [0x47 - 0x46 (W1)], YA\_ALARM [0x49 - 0x48 (W1)], ZA\_ALARM [0x4B - 0x4A (W1)] and the alarm indication is registered in FLAG [0x06 (W0)], displayed in \*ALARM\_ERR of bit [4: 2]. Reading \*ALARM\_ERR will reset the alarm display.

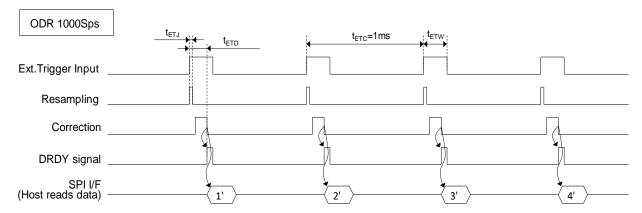

# 5.9 External Trigger Input

External Trigger Input function provides control of the sample data output timing by using an externally supplied input pulse signal to EXT pin. By enabling the **EXT\_SEL** (MSC\_CTRL[0x02(W1)] bit[6]), EXT pin can be used as External Trigger Input pin. The polarity of External Trigger Input (Positive Pulse / Negative Pulse) can be selected by **EXT\_POL** (MSC\_CTRL[0x02(W1)] bit[5]).

When this function is active, the operation is as follows:

For UART Auto Sampling:

When External Trigger Input pin is asserted, the latest sampling data is set to each register and sent to Host automatically.

For all other modes:

When External Trigger Input pin is asserted, the latest sampling data is set to each register and Data Ready signal is asserted. The Host should then read the sampling data synchronized with Data Ready signal.

Note) In case of External Trigger function usage please apply appropriate filter setting (**FILTER\_SEL**) depending on the External Trigger period. Inappropriate filter setting may affect sensor noise performance.

The External Trigger Input Timing requirements and timing diagrams are shown in Figure 5.8, and Figure 5.9.

Figure 5.8 External Trigger Input (Auto Sampling)

Figure 5.9 External Trigger Input (UART/SPI Manual Sampling)

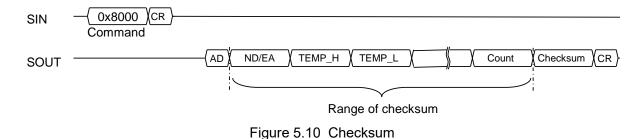

# 5.10 Checksum

A checksum can be appended to the response data during UART/SPI Burst mode or UART Auto sampling by enabling this function in **CHKSM\_OUT** (BURST\_CTRL [0x0C(W1)] bit 0).

The range of the data content for checksum is after the address byte (AD=0x80) of the response data (Figure 5.10). The checksum is calculated with a simple addition of the data content in units of 16-bit, and the resulting sum is truncated to 16-bits and appended as checksum just before delimiter byte (CR=0x0D).

# For example:

Because the sum is "611B4" for the response data stream of "FE01 C455 4000 0052 33C0 0043 7BC8 004A 2608 FD73 3AA0 FF75 4C30 1F53 8FD0 0600 0014", the checksum is "11B4":

**SEIKO EPSON CORPORATION**

# 5.11 Automatic Start (For UART Auto Sampling Only)

Automatic Start function is designed to be used in conjunction with the UART Auto sampling. When the power is supplied or the accelerometer is restart/reset, it allows the device to automatically enter Sampling mode after completing internal initialization. Please refer to Figure 5.3 for the state transition.

Follow the procedures below to enable the Automatic Start function:

- Write a "1" to both UART\_AUTO (bit [0]) and AUTO\_START (bit [1]) of UART\_CTRL [0x08(W1)].

- Store the current register settings to non-volatile memory by writing a "1" to FLASH\_BACKUP (GLOB\_CMD [0x0A(W1)] bit [3]). After completion of the FLASH\_BACKUP command, confirm the results by FLASH\_BU\_ERR (DIAG\_STAT [0x04(W0)] bit [0]).

- The Accelerometer will automatically enter Sampling Mode after the power supply is cycled, or a hardware reset, or a software reset command is executed.

Follow the procedures below to disable this function.

- After entering sampling mode with automatic start, write "01" to **MODE\_CMD** of register: MODE\_CTRL [0x02 (W0)], bit [9: 8] and enter the configuration mode

- Write "0" to AUTO\_START of register: UART\_CTRL [0x08 (W1)], bit [1].

- The subsequent steps are the same as above. Please store the register setting to nonvolatile memory and restart or reset the accelerometer.

### 5.12 Bias Offset

This function adjusts acceleration bias of X, Y, Z axis. The user specified offset is applied to the measured acceleration value before being sent out the serial interface.

Set the bias offset value to the registers: XA\_OFFSET [0x2F - 0x2C (W1)], YA\_OFFSET [0x33 - 0x30 (W1)], ZA\_OFFSET [0x37 - 0x34 (W1)]. The adjustment range is -15 G to +15 G. The data format is the same as the output format of register: ACCL [0x3A - 0x30 (W0)]. Both the X, Y, and Z axes are set to "0" when shipped.

# 5.13 Tilt Output / Combination Output

The device can be configured to output tilt angle by register setting. The tilt angle is calculated from the measured gravitational acceleration vector. The calculation formulas are as follows.

$$\theta = asinG[rad]$$

The device is configurable to select the measurement output type for each axis to be either acceleration or tilt angle. The measurement output type is selected with **OUTPUT\_SEL\_\*** of register: SIG\_CTRL [0x00 (W1)], bit [7: 5].

When both acceleration and tilt angle is outputting at the same time, set **OUTPUT\_SEL** to "Tilt angle" and read register: ACCL [0x3A - 0x30 (W0)] and register: TILT [0x46 - 0x3C (W0)] in normal mode.

### 5.14 Intermittent Measurement for Total Current Reduction

This explains how to realize intermittent measurement for reducing the device current consumption. The user can realize the intermittent measuremet by one of the methods below.

(1) Method of using a sleep mode

(2) Method of switching the device power directly on and off

Table 5.1 shows a summary of some essential items and characteristics.

Table 5.1 Summary of Intermittent Measurement Characteristics and Parameters

|                                | (1) Using sleep mode                               | (2) Device power on and off                                                                                                                                                                          |  |

|--------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Switching method               | Controlling a register and an EXT pin.             | Switching the M-A352 power directly on and off                                                                                                                                                       |  |

| Current consumption at standby | 1.3 mA (typ.)                                      | 0 mA                                                                                                                                                                                                 |  |

| Wakeup time                    | 16 msec (Max.)                                     | 900 msec (Max.)                                                                                                                                                                                      |  |

| Advantage                      | Short wakeup time from sleep mode to sampling mode | Minimum current consumption at standby (power off)                                                                                                                                                   |  |

| Disadvantage                   | -                                                  | Necessity for design considerations<br>to correctly handle floating device<br>interface pins, or unpowered pins<br>during standby mode (power off) and<br>transition current at wakeup (power<br>on) |  |

| Example of intended use        | Event-driven measurement                           | Occasional measurement and long standby (power off) time                                                                                                                                             |  |

Note) When returning to sampling mode, current consumption increases from a low level to the typical current at sampling mode. This causes an increase in internal heating of the device resulting in a transitional increase in temperature compensation errors.

Note) The extent of the errors depends on many variables such as standby time, environment conditions, etc, therefore, the user should evaluate carefully these effects when used for strict and high precision measurement scenarios.

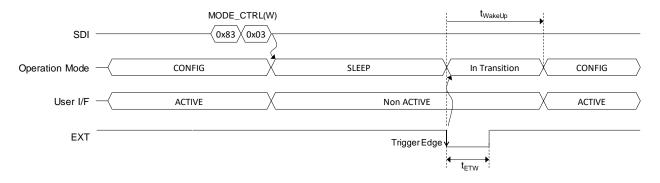

### Method of using sleep mode

The sleep mode function can be enabled by register setting. When shifting to sleep mode, internal circuit operation stops and current consumption during standby mode can be reduced to 1.3 mA (typ.). Wakeup time from sleep mode to sampling mode can be shorter than that from power on to start time (reduced from 900 msec to 16 msec).

Put the operation mode from configuration mode into sleep mode by writing "11" to **MODE\_CMD** (MODE\_CTRL[0x02(W0)], bit[9:8]). The device can wake up from sleep mode to configuration mode in Sleep Wake-up Time by detecting an edge trigger on the EXT pin. Timing sequence from configuration mode to sleep mode and vice versa are shown in Figure 5.11.

Figure 5.11 Timing Sequence from Configuration mode to Sleep mode and vice versa

# Method of switching the device power directly on and off

When the device power is directly switched on and off, the current consumption during standby mode can be 0 mA. Wakeup time from standby to sampling mode is exactly the same as that from power on to start time (900 msec). Please refer to "5.2 Operation Mode" for timing sequence from the power on to sampling mode.

Note) The communication interface pins shown in Table 2.6 will be un-powered during standby (the device power being off), and transition current will appear at wakeup time (device power on). The system interface to the device may need additional design considerations to mitigate the effects, i.e. an unpowered device input pin appears as a short circuit to GND to the host system or when the device is powered on before the system interface to these pins are driven (floating input).

### 5.15 Measurement with Reduced Noise Floor Condition

The device can be configured to output data with a Reduced noise floor condition by register setting. Check the noise density characteristics shown in Figures 4.1-4.2 for standard noise floor level and reduced noise floor level.

Note) If the setting for the noise floor condition is switched from the standard condition to the reduced condition, current consumption during sampling increases from 13.2 mA typ. to 16.2 mA typ.

Follow the procedures below to select a Reduced noise floor condition,

- Set MESMOD\_SEL (SIG\_CTRL[0x00(W1)], bit[4]) to "1: Enable".

- Store the current register settings to non-volatile memory by writing a "1" to **FLASH\_BACKUP** (GLOB\_CMD [0x0A(W1)], bit [3]). After completion of the **FLASH\_BACKUP** command, confirm the results by **FLASH\_BU\_ERR** (DIAG\_STAT [0x04(W0)], bit [0]) to be "0: No error".

- The Reduced noise floor condition will be applied after the power supply is cycled, or a hardware reset or a software reset command is executed. The status can be checked by **MESMOD \_STAT** (GLOB CMD[0x0A (W1)], bit[12]) to be "1: Reduced noise floor condition".

- Put the operation mode from configuration mode into sampling mode by writing "01" to MODE\_CMD (MODE\_CTRL[0x02(W0)], bit[9:8]) to start measurement with the Reduced noise floor condition.

Follow the procedures below to return to Standard noise floor.

- Set **MESMOD\_SEL** (SIG\_CTRL[0x00(W1)], bit[4]) to "0: Standard noise floor condition".

- The subsequent steps are the same as above. Please store the register setting to nonvolatile memory and restart or reset the device.

# 5.16 Bias Temperature Shock Compensation

The device is equipped with a bias stabilization function against thermal shock. The factory setting is set to "1: enable" for this function. When enabled, the time period for bias stabilization after power on is reduced, and the bias errors due to an environmental temperature change are reduced.

Note) This function when enabled may increase errors in estimation of inertial position when state estimation filters such as a Kalman filter are used for inertial navigation etc.

When data without bias temperature shock compensation is preferred, disable this function by setting **TEMP\_STABIL** (SIG CTRL[0x00(W1)], bit[2]) to "0: Disable".

### 5.17 FILTER

The device has a programmable internal FIR filter. The intermediate sensor signal at 4k sps is processed by the FIR filter and decimated according to the output timing and sent out the serial interface. The number of TAPs and a cutoff frequency can be set with the FILTER CTRL [0x06(W1)] register.

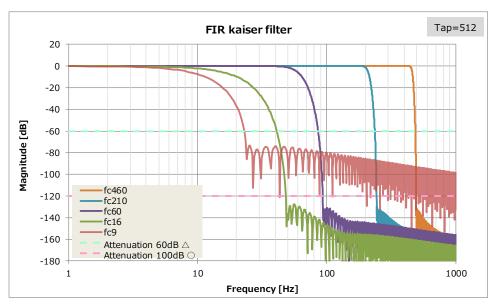

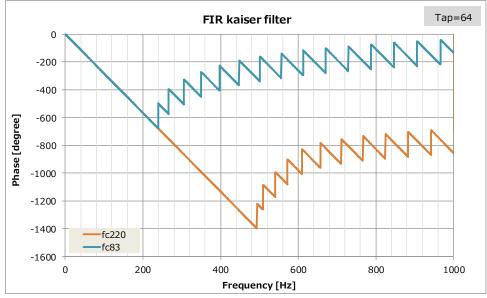

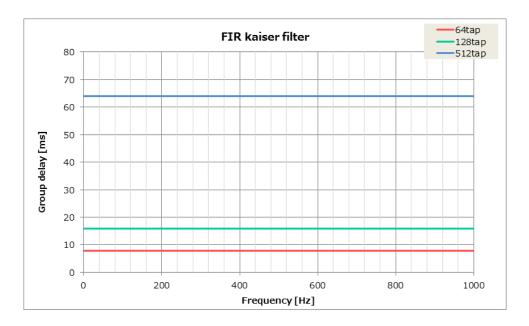

### 5.17.1 FIR Kaiser Filter

Filter parameters correspond to the Kaiser window parameters.

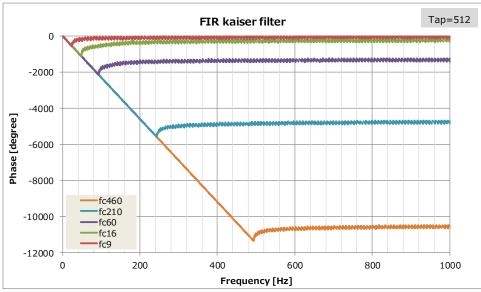

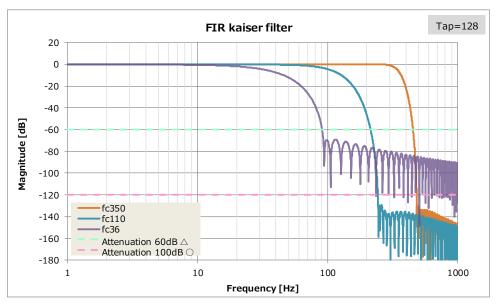

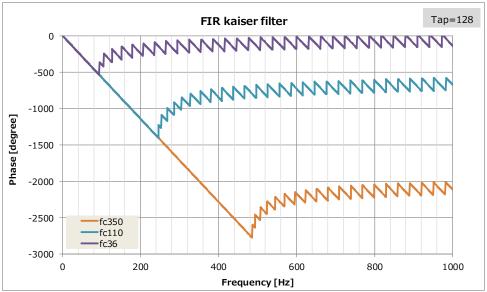

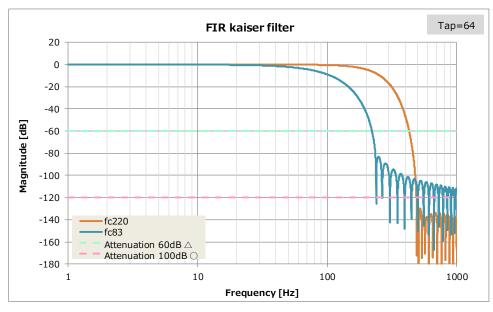

The number of TAPs can be set to 64, 128, or 512, and the cutoff frequency Fc can be selected according to the output sample rate. Figures 5.12 to 5.15 show the typical characteristic of the filters.

Figure 5.12 FIR Kaiser Filter Characteristic (512 taps)

Figure 5.13 FIR Kaiser Filter Characteristic (128 taps)

Figure 5.14 FIR Kaiser Filter Characteristic (64 taps)

Figure 5.14 FIR Kaiser Filter Characteristic – Group Delay

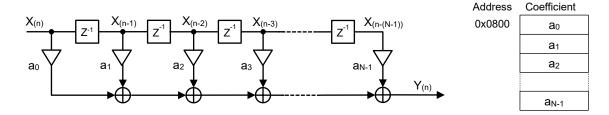

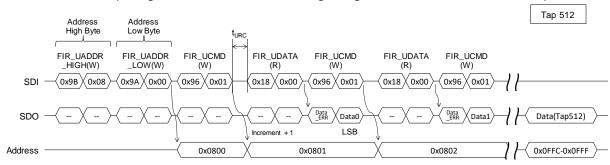

### 5.17.2 User Defined FIR Filter

The FIR filter can be arbitrarily defined by properly setting filter coefficients in the registers: FIR\_UCMD [0x16 (W1)], FIR\_UDATA [0x18 (W1)], FIR\_UADDR [0x1A (W1)], and set **FILTER\_SEL** of register: FILTER\_CTRL [0x06(W1)] to "user defined FIR filter".

Follow the procedures below to program the user defined FIR filter.

### Register Programming Preparation

Set the filter coefficient value using signed 32 bit fixed point number with decimal point after bit [31]. For example, if the coefficient value in decimal form is 0.2195378928, the corresponding filter coefficient value in signed 32 bit fixed point form is 0.2195378928\*2³¹≒0x1C19D153.

Table 5.2 shows the address ranges for the filter coefficients, and Figure 5.16 shows a N-tap FIR filter architecture and a coefficient memory map. The start address is common to each tap number and is at 0x0800. No specific values are set in memory at the factory shipment.

Table 5.2 User Defined FIR Filter Coefficient Address Ranges

| Тар | Coefficient Address Range |

|-----|---------------------------|

| 4   | 0x0800-0x080F             |

| 64  | 0x0800-0x08FF             |

| 128 | 0x0800-0x09FF             |

| 512 | 0x0800-0x0FFF             |

Figure 5.16 N-tap FIR Filter Architecture and Coefficient Memory Map

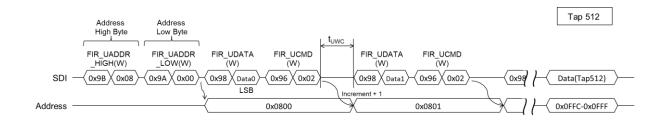

### Register Control (Write)

Set the filter coefficient address in register: FIR\_UADDR [0x1B, 0x1A (W1)] and set the filter coefficient value in **FIR\_UDATA** of register: FIR\_UDATA [0x18 (W1)].

Set **FIR\_UCMD** of register: FIR\_UCMD [0x16 (W1)], bit [1: 0] to write the coefficient value. Next coefficient value can be set after waiting until the **FIR\_UCMD** of registeris to be "00: execution complete"

After the byte has completed writing, the address is automatically incremented by 1, so continuous programming of coefficients are possible without requiring additional address settings.

For the coefficient value, set the upper byte to the upper address and the lower byte to the lower address. Figure 5.17 shows the write sequence.

Please specify the type of filter, TAP setting and cutoff frequency using **FILTER\_SEL** in register: FILTER\_CTRL[0x06 (W1)], bit [3:0]. When selecting the user defined FIR filter, the **FILTER\_SEL** register must reflect the filter coefficient data that are programmed in the device.

Figure 5.17 User Defined FIR Filter Coefficient Example Write Sequence (512 taps)

# Register Control (Read)

Set the filter coefficient address in register: FIR\_UADDR [0x1B, 0x1A (W1)] and read the coefficient value using **FIR\_UCMD** in register: FIR\_UCMD [0x16 (W1)], bit [1: 0]. Next coefficient value can be read after waiting until the FIR\_UCMD of registeris to be "00: execution complete"

The address is automatically incremented by 1, so continuous execution of read commands is possible without requiring additional address settings. Figure 5.18 shows the read sequence.

Figure 5.18 User Defined Filter Coefficient Read Sequence (512 taps)

### 5.17.3 Notes For FIR Filter Usage

# Transient response

As shown in Table 5.3, transient response data is generated according to the combination of the tap number and the data output rate when sampling is started.

In the case of internal timer trigger measurement, the acceleration value of register ACCL [0x3A - 0x30(W0)] is not updated during this period.

In the case of automatic measurement, the device starts outputting data after the transient response.

Table 5.3 Transient Response Data Based on Output Data Rate and Filter Tap

|          | 64 Taps | 128 Taps | 512 Taps |

|----------|---------|----------|----------|

| 1,000sps | 15      | 31       | 127      |

| 500sps   | 7       | 15       | 63       |

| 200sps   |         | 7        | 31       |

| 100sps   |         |          | 15       |

| 50sps    |         |          | 7        |

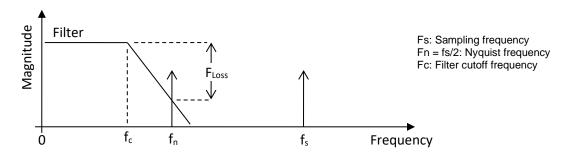

# Supported Settings For Output Rate and Filter Cutoff Frequency

The host must set the cutoff frequency of the FIR filter and the output rate in proper combination to avoid aliasing.

Figure 5.19 Anti-Aliasing Relationship Diagram

Table 5.4 Supported Settings For Output Rate and Filter Cutoff Frequency

|          |          |        |                | SMPL_CTRL Register(Internal Timer Trigger) |         |         |         |           |  |  |  |

|----------|----------|--------|----------------|--------------------------------------------|---------|---------|---------|-----------|--|--|--|

|          | Ton      |        |                |                                            |         |         |         |           |  |  |  |

|          | Тар      | Fc     | Group<br>delay | 50 Sps                                     | 100 Sps | 200 Sps | 500 Sps | 1,000 Sps |  |  |  |

| Ξ        |          | 460 Hz |                | -                                          | -       | -       | -       | OK        |  |  |  |

| FILTER   | 512 Taps | 210 Hz |                | -                                          | -       | -       | OK      | OK        |  |  |  |

|          |          | 60 Hz  | 63.875 ms      | -                                          | -       | OK*1    | OK      | OK        |  |  |  |

| CTRL     |          | 16 Hz  |                | -                                          | OK      | OK      | OK      | OK        |  |  |  |

| ~        |          | 9 Hz   |                | *                                          | *       | *       | *       | *         |  |  |  |

| Register | 400 -    | 350 Hz |                | -                                          | -       | -       | -       | OK        |  |  |  |

| iste     | 128 Taps | 110 Hz | 15.875 ms      | -                                          | -       | ı       | OK      | OK        |  |  |  |

|          |          | 36 Hz  |                | -                                          | -       | *       | *       | *         |  |  |  |

|          | 04 Tara  | 220 Hz | 7.875 ms       | -                                          | -       | -       |         | OK        |  |  |  |

|          | 64 Taps  | 83 Hz  | 7.0751115      | -                                          | -       | -       | *       | *         |  |  |  |

OK: F<sub>Loss</sub> < -120 dB Recommended setting

Note) These settings are valid when the user defined FIR filter function is used or the external trigger input function is active,

<sup>\* :</sup> F<sub>Loss</sub> < -60 dB Although a possible setting, some decrease in measurement quality due to aliasing

<sup>— :</sup> Fn < Fc Invalid setting. When using internal timer measurement, measurement data returns with error "0x64000000".

<sup>\*1)</sup> The factory setting is Tap: 512, Fc: 60 Hz, ODR: 200 Hz

# 5.17.4 Long-Term Filter (HPF, LPF)

In addition to the FIR filter, this product has a simple filter for long-term measurement. This filter consists of a moving average at an output data rate. The number of taps can be set to a power of 2 in the range 2 to 4096.

LPF is a two-stage configuration with the set number of taps.

HPF consists of a single-stage configuration with the set number of taps and subtracting the moving average from the original data.

When using a long-term filter, set **FILT\_EN** of register: LONGFILT\_CTRL [0x1C (W1)], bit [0] to "1: valid" and select "LPF" or "HPF" in bit [1] **FILT\_SEL**.

Set the number of taps to TAP\_SIZE of register: LONGFILT\_TAP [0x1E (W1)].

Please note that transient response data is generated according to the combination of the tap size and a kind of filters (HPF/LPF) when sampling is started. Numbers of the transient response data for long period filters are shown in Table 5.5.

Table 5.5 Numbers of Transient Response Data for Long Period Filters

|     | Number of Transient Response Data |

|-----|-----------------------------------|

| HPF | TAP Size                          |

| LPF | TAP Size * 2                      |

Note) The maximum output rate is limited to 500 Sps when long-term filter is used.

# 6. Digital Interface

This device has the following two external interfaces.

- (1) SPI interface

- (2) UART interface

The SPI interface and the UART interface have almost the same functions, except for Auto sampling function for the UART interface. No hardware pin configuration is necessary for SPI/UART selection since both interfaces are always active. Connect desired interface pins to SPI or UART interface.

Note) Connecting both SPI and UART at the same time is not supported and may result in malfunction of the device.

The registers inside the device are accessed via the SPI or UART interfaces.

In this document, data sent to the device is called a "Command" and data sent back in response to the command is called a "Response". There are two types of commands: write command and read command. The write command has no response. The write command always writes to the internal register in 8-bit words. The response to the read command, i.e. the data from the internal register, is always read in 16-bit words.

When reading from the registers, there is a burst mode in addition to the normal mode.

When the IMU output data rate is high (i.e. 1000sps), it may exceed the bandwidth of the host interface and cause the data transmission to be incorrect. In this case, the user must balance the transmission data rate and the bandwidth capability of the host interface.

Adjust the following settings accordingly to optimize the host interface bandwidth:

- For the UART, adjust the baud rate in **BAUD\_RATE** (UART\_CTRL [0x08(W1)] bit [9:8]).

- For the SPI, adjust the host side SPI clock frequency and SPI wait time.

Adjust the following settings accordingly to optimize the transmission data rate:

- The transmission data rate is affected by the data output rate setting in **DOUT\_RATE** (SMPL\_CTRL [0x04(W1)] bits [11:8]).

- The transmission data rate is also affected by the number of output bytes included in burst mode read transfer. The adjustment to the number of output bytes is in registers BURST\_CTRL [0x0C(W1)].

Several concrete examples for setting the transmission data rate and host interface bandwidth are shown below:

- (1) For UART Output:

- BAUD RATE ="01" of UART CTRL [0x08(W1)] bit [9,8]: 460800 baud

- UART AUTO ="1" of UART CTRL [0x08(W1)] bit [0]: UART Auto sampling

- **DOUT\_RATE** = "0100" of SMPL CTRL [0x04(W1)] bit [11:8]: 200Sps

- **BURST\_CTRL** [0x0C(W1)] = "0x4702": TEMP, Acceleration, and COUNT output

- (2) For SPI Output:

- SPI Interface Transmission Setting: f<sub>SCLK</sub>=1MHz and t<sub>STALL</sub>=24us for normal mode

- DOUT\_RATE = "0100" of SMPL\_CTRL [0x04(W1)] bit [11:8]: 200Sps

- BURST\_CTRL [0x0C(W1)]= "0x4702": TEMP, Acceleration, and COUNT output

### 6.1 SPI Interface

Table 6.1 shows the communication settings of SPI interface and Table 6.2 shows the SPI timing for normal mode.

Table 6.1 SPI Communication Settings

| Parameter   | Setting        |  |  |  |  |  |

|-------------|----------------|--|--|--|--|--|

| Mode        | Slave          |  |  |  |  |  |

| Word length | 16 bits        |  |  |  |  |  |

| Phase       | Rising edge    |  |  |  |  |  |

| Polarity    | Negative logic |  |  |  |  |  |

Table 6.2 SPI Timing (Normal Mode)

| Parameter             | Minimum | Maximum | Unit |

|-----------------------|---------|---------|------|

| f <sub>SCLK</sub>     | 0.01    | 2.0     | MHz  |

| t <sub>STALL</sub>    | 20      | -       | μs   |

| twriterate            | 40      | -       | μs   |

| t <sub>READRATE</sub> | 40      | -       | μs   |

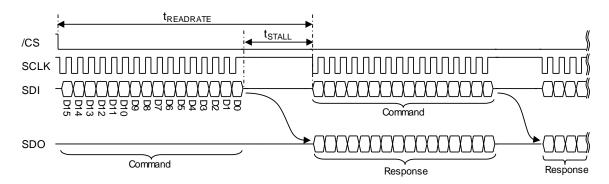

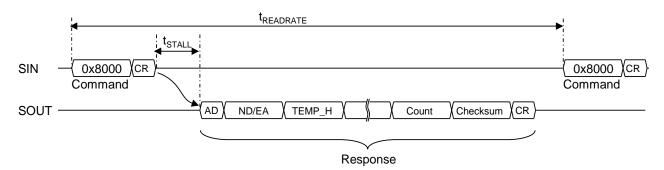

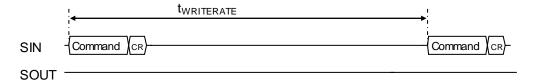

# 6.1.1 SPI Read Timing (Normal Mode)

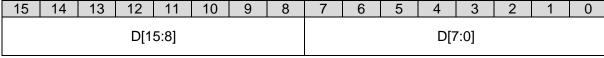

The response data to a read command, i.e. the data from the internal register, is always returned in 16-bit words. The SPI interface supports sending the next command during the same bus cycle as receiving a response to the read command (full-duplex).

Figure 6.1 SPI Read Timing (Normal Mode)

Table 6.3 Command Format (Read)

| 15 | 14 | 13 | 12 | 11     | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|--------|----|---|---|---|---|---|---|---|---|---|---|

| 0  |    |    |    | A[6:0] |    |   |   |   |   |   | X | X |   |   |   |

A [6:0] · · · Register address (even address)

XX · · · Don't Care

Table 6.4 Response Format (Read)

D[15:8] · · · Register read data (upper byte)

D[7:0] · · · Register read data (lower byte)

# **6.1.2 SPI Write Timing (Normal Mode)**

A write command to a register has no response. Unlike register reading, registers are written in 8-bit words.

Figure 6.2 SPI Write Timing (Normal Mode)

Table 6.5 Command Format (Write)

| 15 | 14 | 13 | 12 | 11     | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3         | 2 | 1 | 0 |

|----|----|----|----|--------|----|---|---|---|---|---|-----|-----------|---|---|---|

| 1  |    |    |    | A[6:0] |    |   |   |   |   |   | D[7 | · · / \ I |   |   |   |

A [6:0] · · · Register address (even or odd number)

D [7:0] · · · Register write data

# 6.1.3 SPI Read Timing (Burst Mode)

Burst mode access of read data is supported using a "Burst Read Command" by writing 0x00 in **BURST\_CMD** (BURST [0x00(W0)] bits[7:0]). In burst mode, ND flag/EA flag, temperature sensor value, 3-axis acceleration sensor value, etc. are consecutively sent as a response. The response format for the burst read output data is configured by register setting in BURST\_CTRL [0x0C(W1)]. Please refer to 6.3 Data Packet Format for the response format.

Table 6.6 SPI Timing (Burst Mode)

| Parameter              | Minimum | Maximum | Unit |

|------------------------|---------|---------|------|

| f <sub>SCLK</sub>      | 0.01    | 2.0     | MHz  |

| t <sub>STALL1</sub>    | 45      | -       | μs   |

| t <sub>STALL2</sub>    | 0       | -       | μs   |

| t <sub>READRATE2</sub> | 8       | -       | μs   |

Figure 6.3 SPI Read Timing (Burst Mode)

#### 6.2 UART Interface

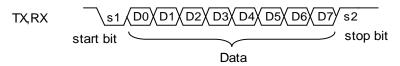

Table 6.7 shows the supported UART communication settings and Figure 6.4 shows the UART bit format. Please refer to **BAUD\_RATE** (UART\_CTRL [0x08(W1)] bit[9:8]) for changing the baud rate setting.

Table 6.7 UART Communication Settings

|               | <u> </u>                        |

|---------------|---------------------------------|

| Parameter     | Settings                        |

| Transfer rate | 115.2kbps/ 230.4kbps/ 460.8kbps |

| Start         | 1 bit                           |

| Data          | 8 bits                          |

| Stop          | 1 bit                           |

| Parity        | None                            |