## Si47xx Programming Guide

## 1. Introduction

This document provides an overview of the programming requirements for the Si4704/05/06/3x AM/FM/SW/LW receiver. The hardware control interface and software commands are detailed along with several examples of the required steps to configure the device for various modes of operation.

### 2. Overview

This family of products is programmed using commands and responses. To perform an action, the system controller writes a command byte and associated arguments, causing the device to execute the given command. The device will, in turn, provide a response depending on the type of command that was sent. Section "4. Commands and Responses" on page 5 and Section "5. Commands and Properties" on page 6 describe the procedures for using commands and responses and provide complete lists of commands, properties, and responses.

The device has a slave control interface that allows the system controller to send commands to and receive responses from the device using one of three serial protocols (or bus modes): 2-wire mode (I<sup>2</sup>C and SMBUS compatible), 3-wire mode, or SPI mode.

Section "6. Control Interface" on page 123 describes the control interface in detail.

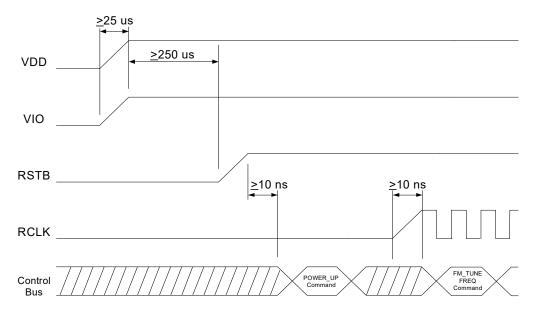

Section "7. Powerup" on page 131 describes options for the sequencing of VDD and VIO power supplies, selection of the desired bus mode, provision of the reference clock, RCLK, and sending of the POWER UP command.

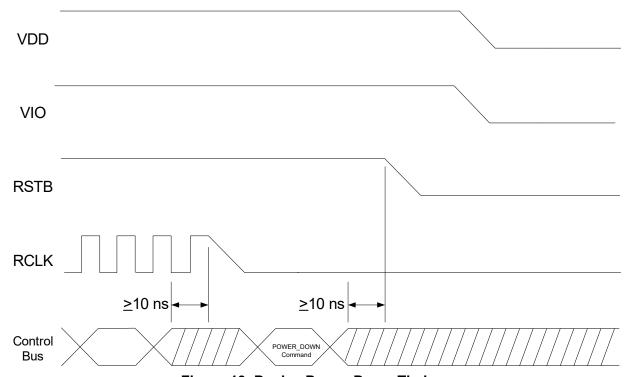

Section "8. Powerdown" on page 138 describes sending the POWER\_DOWN command and removing VDD and VIO power supplies as necessary.

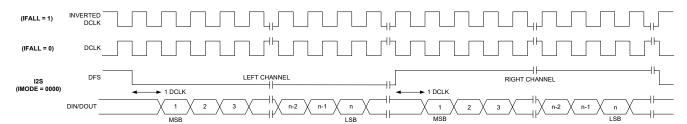

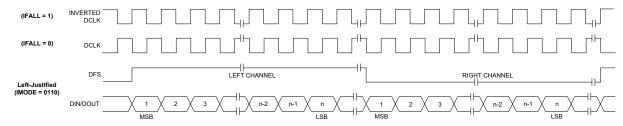

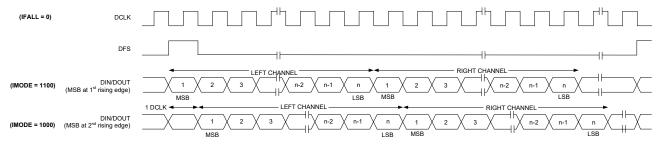

Section "9. Digital Audio Interface" on page 139 describes the digital audio format supported and how to operate the device in digital mode.

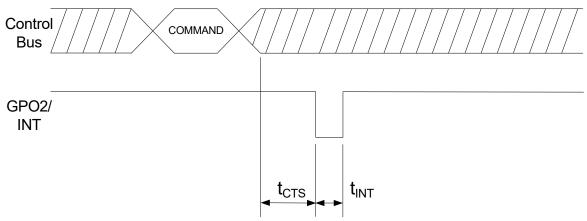

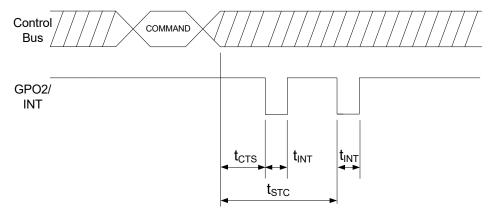

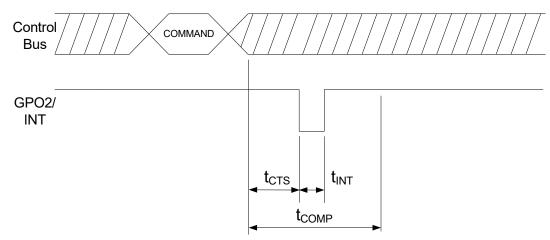

Section "10. Timing" on page 142 describes the CTS (Clear to Send) timing indicating when the command has been accepted and in most cases completed execution, and the STC (Seek/Tune Complete) timing indicating when the Seek/Tune commands have completed execution.

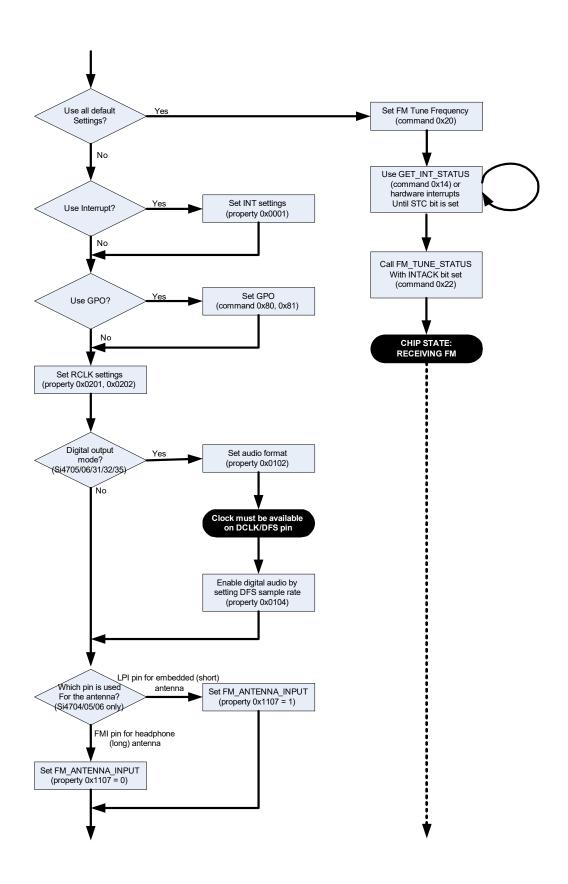

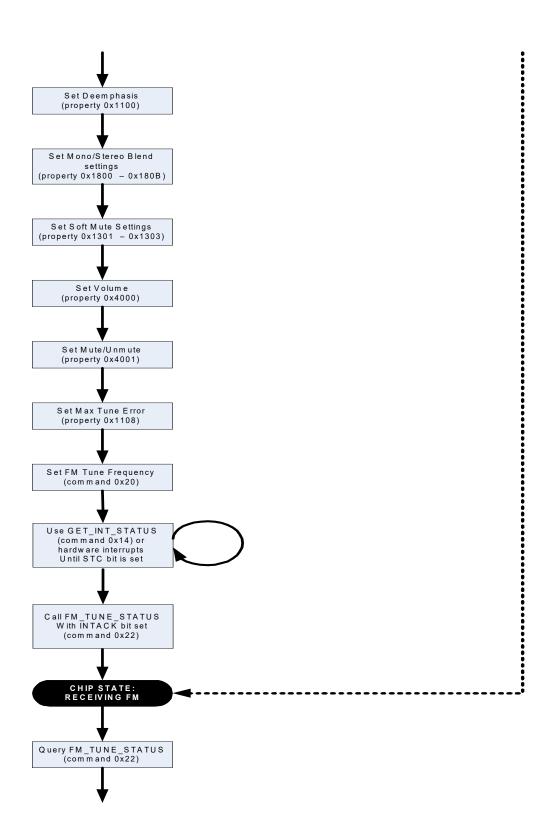

Section "11. Programming Examples" on page 146 provides flowcharts and step-by-step procedures for programming the device.

**Table 1. Product Family Function**

| Part<br>Number      | General Description           | FM Receiver | AM Receiver | SW/LW Receiver | RDS      | High Performance RDS | RPS | Digital Input | Digital Output | Embedded FM antenna | AEC-Q100 Qualified | Package Size (mm) |

|---------------------|-------------------------------|-------------|-------------|----------------|----------|----------------------|-----|---------------|----------------|---------------------|--------------------|-------------------|

| Si4702              | FM Receiver                   | <b>✓</b>    |             |                |          |                      |     |               |                | ш                   |                    | 3x3               |

| Si4703              | FM Receiver with RDS          | <b>✓</b>    |             |                | <b>✓</b> |                      |     |               |                |                     |                    | 3x3               |

| Si4704              | FM Receiver                   | ✓           |             |                |          |                      |     |               | Not e 1        | <b>✓</b>            |                    | 3x3               |

| Si4705              | FM Receiver with RDS          | ✓           |             |                | 1        | Note 2               |     |               | ✓              | <b>✓</b>            |                    | 3x3               |

| Si4706 <sup>3</sup> | High Performance RDS Receiver | ✓           |             |                | 1        | ✓                    |     |               | <b>✓</b>       | <b>√</b>            |                    | 3x3               |

| Si4708              | FM Receiver                   | ✓           |             |                |          |                      |     |               |                |                     |                    | 2.5x2.5           |

| Si4709              | FM Receiver with RDS          | ✓           |             |                | 1        |                      |     |               |                |                     |                    | 2.5x2.5           |

| Si4730              | AM/FM Receiver                | ✓           | ✓           |                |          |                      |     |               |                |                     |                    | 3x3               |

| Si4731              | AM/FM Receiver with RDS       | <b>✓</b>    | <b>√</b>    |                | <b>✓</b> | Note 2               |     |               | <b>√</b>       |                     |                    | 3x3               |

| Si4732 <sup>4</sup> | AM/SW/LW/FM Receiver with RDS | ✓           | <b>✓</b>    | ✓              | ✓        | ✓                    |     |               | <b>√</b>       |                     |                    | SOIC16            |

| Si4734              | AM/SW/LW/FM Receiver          | ✓           | <b>✓</b>    | ✓              |          |                      |     |               |                |                     |                    | 3x3               |

| Si4735              | AM/SW/LW/FM Receiver with RDS | ✓           | ✓           | <b>✓</b>       | ✓        | Note 2               |     |               | ✓              |                     |                    | 3x3               |

### Notes:

- 1. Digital Output is available in Si4704-D60 and later.

- 2. High Performance RDS is available in Si4705/31/35 and later, Si4732.

- 3. Si4706 is covered under NDA.

- **4.** Si4732-A10 has the same firmware FMRX component and AM\_SW\_LW RX component as that of Si4735-D60, so Si4732-A10 is considered as the most recent revision as D60, and the Si4735-D60 related descriptions in Appendix A and Appendix B also apply to Si4732-A10 if not specified.

# TABLE OF CONTENTS

| <u>Section</u>                                                                | <u>Page</u> |

|-------------------------------------------------------------------------------|-------------|

| 1. Introduction                                                               | 1           |

| 2. Overview                                                                   | 1           |

| 3. Terminology                                                                |             |

| 4. Commands and Responses                                                     | 5           |

| 5. Commands and Properties                                                    | 6           |

| 5.1. Commands and Properties for the FM/RDS Receiver (Si4704/05/06/3x)        | 6           |

| 5.2. Commands and Properties for the AM/SW/LW Receiver (Si4730/31/32/34/35) . | 68          |

| 5.3. Commands and Properties for the Stereo Audio ADC Mode (Si4704/05/30/31)  | 104         |

| 6. Control Interface                                                          | 123         |

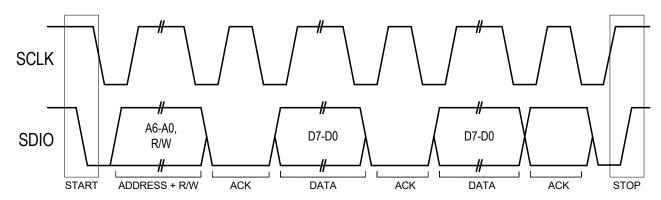

| 6.1. 2-Wire Control Interface Mode                                            | 123         |

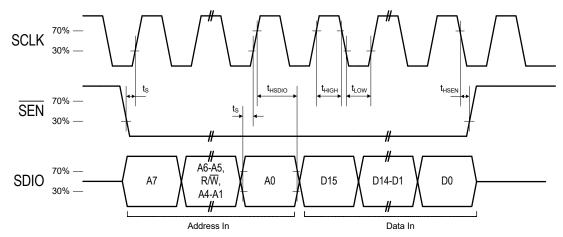

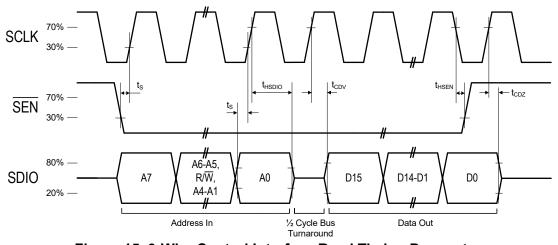

| 6.2. 3-Wire Control Interface Mode                                            | 126         |

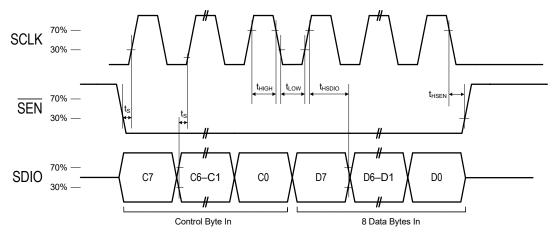

| 6.3. SPI Control Interface Mode                                               | 129         |

| 7. Powerup                                                                    | 131         |

| 7.1. Powerup from Device Memory                                               | 132         |

| 7.2. Powerup from a Component Patch                                           | 132         |

| 8. Powerdown                                                                  | 138         |

| 9. Digital Audio Interface                                                    | 139         |

| 10. Timing                                                                    | 142         |

| 11. Programming Examples                                                      | 146         |

| 11.1. Programming Example for the FM/RDS Receiver                             | 146         |

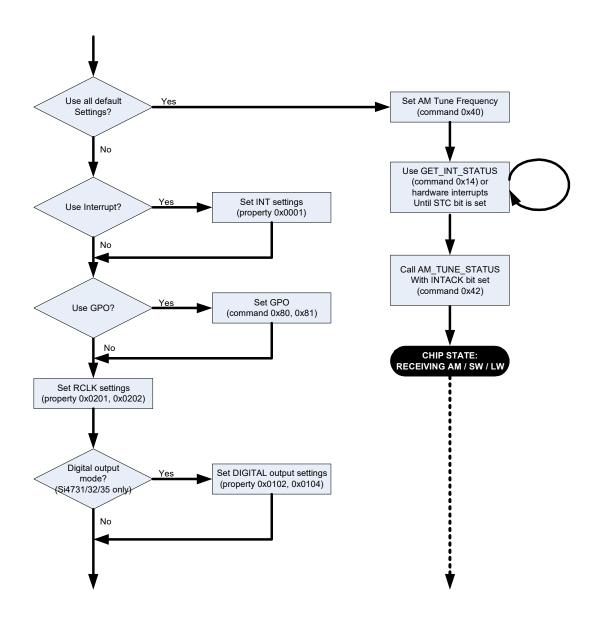

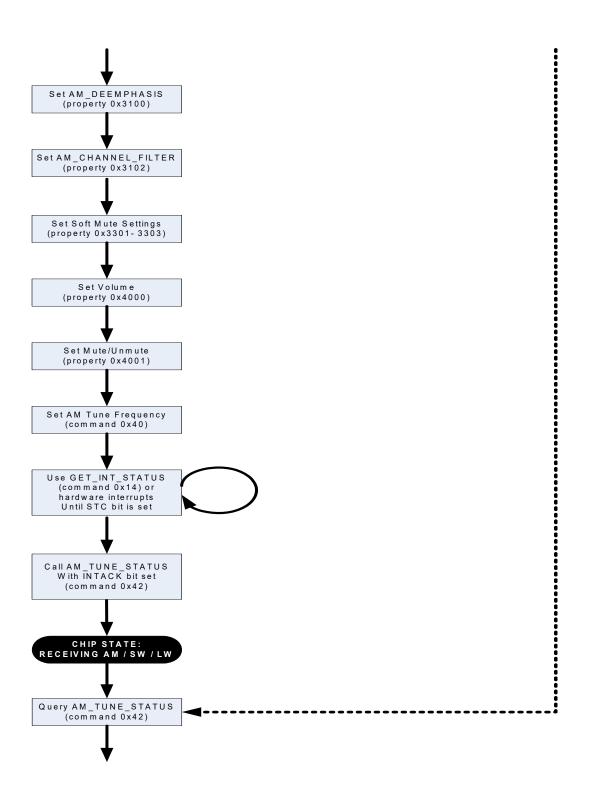

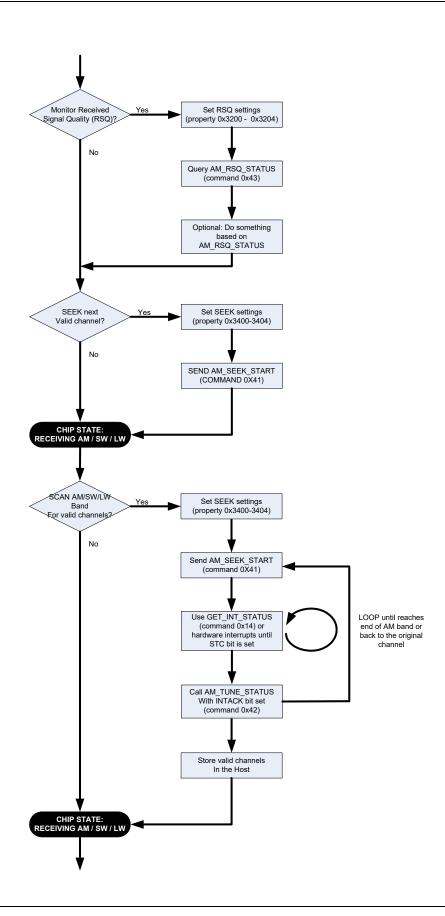

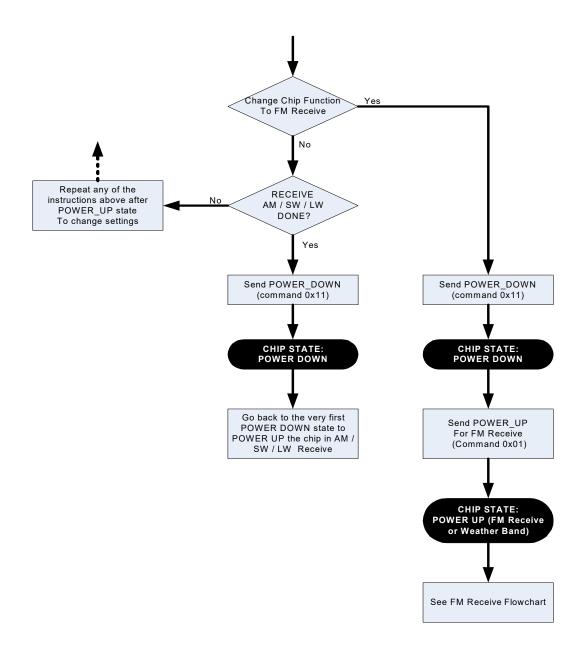

| 11.2. Programming Example for the AM/LW/SW Receiver                           |             |

| Document Change List                                                          | 178         |

# **AN332**

## 3. Terminology

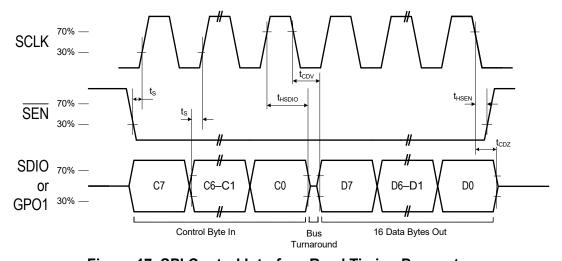

- SEN—Serial enable pin, active low; used as device select in 3-wire and SPI operation and address selection in 2-wire operation.

- SDIO—Serial data in/data out pin.

- SCLK—Serial clock pin.

- RST or RSTb—Reset pin, active low

- RCLK—External reference clock

- GPO—General purpose output

- CTS—Clear to send

- STC—Seek/Tune Complete

- NVM—Non-volatile internal device memory

- Device—Refers to the AM/FM/SW/LW Receiver

- System Controller—Refers to the system microcontroller

- CMD—Command byte

- COMMANDn—Command register (16-bit) in 3-Wire mode (n = 1 to 4)

- ARGn—Argument byte (n = 1 to 7)

- STATUS—Status byte

- RESPn—Response byte (n = 1 to 15)

- RESPONSEn—Response register (16-bit) in 3-Wire mode (n = 1 to 8)

## 4. Commands and Responses

Commands control actions, such as power up, power down, or tune to a frequency, and are one byte in size. Arguments are specific to a given command and are used to modify the command. For example, after the FM\_TUNE\_FREQ command, arguments are required to set the tune frequency. Arguments are one byte in size, and each command may require up to seven arguments. Responses provide the system controller status information and are returned after a command and its associated arguments are issued. All commands return a one byte status indicating interrupt state and clear-to-send the next command. Commands may return up to 15 additional response bytes. A complete list of commands is available in "5. Commands and Properties".

Table 2 shows an example of tuning to a frequency using the FM\_TUNE\_FREQ command. This command requires that a command and three arguments be sent and returns one status byte. The table is broken into three columns. The first column lists the action taking place: command (CMD), argument (ARG), status (STATUS), or response (RESP). The second column lists the data byte or bytes in hexadecimal that are being sent or received. An arrow preceding the data indicates data being sent from the device to the system controller. The third column describes the action.

| Action | Data  | Description                          |

|--------|-------|--------------------------------------|

| CMD    | 0x20  | FM_TUNE_FREQ                         |

| ARG1   | 0x00  |                                      |

| ARG2   | 0x27  | Set frequency to 101.1 MHz           |

| ARG3   | 0x7E  |                                      |

| ARG4   | 0x00  | Set antenna tuning capacitor to auto |

| STATUS | →0x80 | Reply Status. Clear-to-send high.    |

Table 2. Using the FM\_TUNE\_FREQ Command

Properties are special command arguments used to modify the default device operation and are generally configured immediately after power-up. An example of a property is REFCLK\_FREQ. A complete list of properties is available in Section "5. Commands and Properties".

Table 3 shows an example of setting the REFCLK frequency using the REFCLK\_FREQ property by sending the SET\_PROPERTY command and five argument bytes. ARG1 of the SET\_PROPERTY command is always 0x00. ARG2 and ARG3 are used to select the property number, PROP (0x0201 in this example), and ARG4 and ARG5 are used to set the property value, PROPD (0x8000 or 32768 Hz in the example).

| Action       | Data  | Description                       |

|--------------|-------|-----------------------------------|

| CMD          | 0x12  | SET_PROPERTY                      |

| ARG1         | 0x00  |                                   |

| ARG2 (PROP)  | 0x02  | REFCLK_FREQ                       |

| ARG3 (PROP)  | 0x01  |                                   |

| ARG4 (PROPD) | 0x80  | 32768 Hz                          |

| ARG5 (PROPD) | 0x00  |                                   |

| STATUS       | →0x80 | Reply Status. Clear-to-send high. |

Table 3. Using the SET\_PROPERTY Command

The implementation of the command and response procedures in the system controller differs for each of the three bus modes. Section "6. Control Interface" on page 123 details the required bit transactions on the control bus for each of the bus modes.

## 5. Commands and Properties

There are two different components for these product families:

- 1. FM Receiver component

- 2. AM/SW/LW component

The following two subsections list all the commands and properties used by each of the component.

## 5.1. Commands and Properties for the FM/RDS Receiver (Si4704/05/06/3x)

Tables 4 and 5 summarize the commands and properties for the FM/RDS Receiver component applicable to Si4704/05/06/3x.

Table 4. FM/RDS Receiver Command Summary

| Cmd  | Name            | Description                                                                     | Available In               |

|------|-----------------|---------------------------------------------------------------------------------|----------------------------|

| 0x01 | POWER_UP        | Power up device and mode selection.                                             | All                        |

| 0x10 | GET_REV         | Returns revision information on the device.                                     | All                        |

| 0x11 | POWER_DOWN      | Power down device.                                                              | All                        |

| 0x12 | SET_PROPERTY    | Sets the value of a property.                                                   | All                        |

| 0x13 | GET_PROPERTY    | Retrieves a property's value.                                                   | All                        |

| 0x14 | GET_INT_STATUS  | Reads interrupt status bits.                                                    | All                        |

| 0x15 | PATCH_ARGS*     | Reserved command used for patch file downloads.                                 | All                        |

| 0x16 | PATCH_DATA*     | Reserved command used for patch file downloads.                                 | All                        |

| 0x20 | FM_TUNE_FREQ    | Selects the FM tuning frequency.                                                | All                        |

| 0x21 | FM_SEEK_START   | Begins searching for a valid frequency.                                         | All                        |

| 0x22 | FM_TUNE_STATUS  | Queries the status of previous FM_TUNE_FREQ or FM_SEEK_START command.           | All                        |

| 0x23 | FM_RSQ_STATUS   | Queries the status of the Received Signal Quality (RSQ) of the current channel. | All                        |

| 0x24 | FM_RDS_STATUS   | Returns RDS information for current channel and reads an entry from RDS FIFO.   | Si4705/06,<br>Si4731/32/35 |

| 0x27 | FM_AGC_STATUS   | Queries the current AGC settings                                                | All                        |

| 0x28 | FM_AGC_OVERRIDE | Override AGC setting by disabling and forcing it to a fixed value               | All                        |

| 0x80 | GPIO_CTL        | Configures GPO1, 2, and 3 as output or Hi-Z.                                    | All                        |

| 0x81 | GPIO_SET        | Sets GPO1, 2, and 3 output level (low or high).                                 | All                        |

\*Note: Commands PATCH\_ARGS and PATCH\_DATA are only used to patch firmware. For information on applying a patch file, see "7.2. Powerup from a Component Patch" on page 132.

Table 5. FM/RDS Receiver Property Summary

| Prop   | Name                           | Description                                                                                                                                                                    | Default | Available In                                                                    |

|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------|

| 0x0001 | GPO_IEN                        | Enables interrupt sources.                                                                                                                                                     | 0x0000  | All                                                                             |

| 0x0102 | DIGITAL_OUTPUT_<br>FORMAT      | Configure digital audio outputs.                                                                                                                                               | 0x0000  | Si4704-D60 and later,<br>Si4705/06,<br>Si4731/32/35,<br>Si4730/34-D60 and later |

| 0x0104 | DIGITAL_OUTPUT_<br>SAMPLE_RATE | Configure digital audio output sample rate.                                                                                                                                    | 0x0000  | Si4704-D60 and later,<br>Si4705/06,<br>Si4731/32/35,<br>Si4730/34-D60 and later |

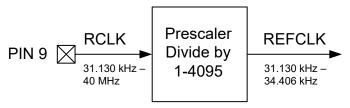

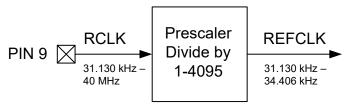

| 0x0201 | REFCLK_FREQ                    | Sets frequency of reference clock in Hz. The range is 31130 to 34406 Hz, or 0 to disable the AFC. Default is 32768 Hz.                                                         | 0x8000  | All                                                                             |

| 0x0202 | REFCLK_PRESCALE                | Sets the prescaler value for RCLK input.                                                                                                                                       | 0x0001  | All                                                                             |

| 0x1100 | FM_DEEMPHASIS                  | Sets deemphasis time constant. Default is 75 µs.                                                                                                                               | 0x0002  | All                                                                             |

| 0x1102 | FM_CHANNEL_FILTER              | Selects bandwidth of chan-<br>nel filter applied at the<br>demodulation stage.                                                                                                 | 0x0001  | Si4706<br>Si4705/31/35-D50, and later,<br>Si4732                                |

|        |                                |                                                                                                                                                                                | 0x0000  | Si4704/30/34-D50 and later                                                      |

| 0x1105 | FM_BLEND_STEREO_<br>THRESHOLD  | Selects bandwidth of chan-<br>nel filter applied at the<br>demodulation stage.                                                                                                 | 0x0031  | Si470x                                                                          |

| 0x1106 | FM_BLEND_MONO_<br>THRESHOLD    | Sets RSSI threshold for mono blend (Full mono below threshold, blend above threshold). To force stereo set this to 0. To force mono set this to 127. Default value is 30 dBµV. | 0x001E  | Si470x                                                                          |

| 0x1107 | FM_ANTENNA_INPUT               | Selects the antenna type and the pin to which it is connected.                                                                                                                 | 0x0000  | Si4704/05/06                                                                    |

| 0x1108 | FM_MAX_TUNE_<br>ERROR          | Sets the maximum freq error allowed before setting the                                                                                                                         | 0x001E  | All                                                                             |

|        |                                | AFC rail (AFCRL) indicator.<br>Default value is 20 kHz.                                                                                                                        | 0x0014  | All others                                                                      |

| 0x1200 | FM_RSQ_INT_<br>SOURCE          | Configures interrupt related to Received Signal Quality metrics.                                                                                                               | 0x0000  | All                                                                             |

Table 5. FM/RDS Receiver Property Summary (Continued)

| Prop   | Name                              | Description                                                                                                                                                 | Default | Available In                                                   |

|--------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------|

| 0x1201 | FM_RSQ_SNR_HI_<br>THRESHOLD       | Sets high threshold for SNR interrupt.                                                                                                                      | 0x007F  | All                                                            |

| 0x1202 | FM_RSQ_SNR_LO_<br>THRESHOLD       | Sets low threshold for SNR interrupt.                                                                                                                       | 0x0000  | All                                                            |

| 0x1203 | FM_RSQ_RSSI_HI_<br>THRESHOLD      | Sets high threshold for RSSI interrupt.                                                                                                                     | 0x007F  | All                                                            |

| 0x1204 | FM_RSQ_RSSI_LO_<br>THRESHOLD      | Sets low threshold for RSSI interrupt.                                                                                                                      | 0x0000  | All                                                            |

| 0x1205 | FM_RSQ_MULTIPATH_HI_<br>THRESHOLD | Sets high threshold for multipath interrupt.                                                                                                                | 0x007F  | Si4706-D50,<br>Si4704/05/30/31/34/35-D50,<br>and later, Si4732 |

| 0x1206 | FM_RSQ_MULTIPATH_<br>LO_THRESHOLD | Sets low threshold for multipath interrupt.                                                                                                                 | 0x0000  | Si4706-D50,<br>Si4704/05/30/31/34/35-D50,<br>and later, Si4732 |

| 0x1207 | FM_RSQ_BLEND_<br>THRESHOLD        | Sets the blend threshold for blend interrupt when boundary is crossed.                                                                                      | 0x0081  | All                                                            |

| 0x1300 | FM_SOFT_MUTE_RATE                 | Sets the attack and decay rates when entering and leaving soft mute.                                                                                        | 0x0040  | Si4706                                                         |

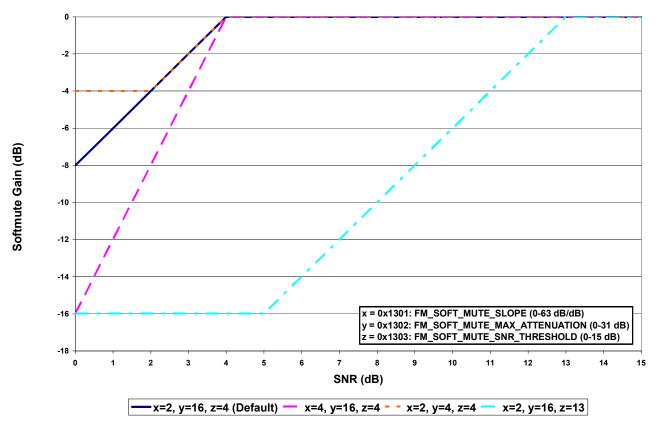

| 0x1301 | FM_SOFT_MUTE_SLOPE                | Configures attenuation slope<br>during soft mute in dB attenu-<br>ation per dB SNR below the<br>soft mute SNR threshold.<br>Default value is 2.             | 0x0002  | Si4704/05/06/3x-D50 and<br>later, Si4732                       |

| 0x1302 | FM_SOFT_MUTE_<br>MAX_ATTENUATION  | Sets maximum attenuation during soft mute (dB). Set to 0 to disable soft mute. Default is 16 dB.                                                            | 0x0010  | All                                                            |

| 0x1303 | FM_SOFT_MUTE_<br>SNR_THRESHOLD    | Sets SNR threshold to engage soft mute. Default is 4 dB.                                                                                                    | 0x0004  | All                                                            |

| 0x1304 | FM_SOFT_MUTE_<br>RELEASE_RATE     | Sets soft mute release rate. Smaller values provide slower release, and larger values provide faster release. The default is 8192 (approximately 8000 dB/s) | 0x2000  | Si4706-D50,<br>Si4704/05/30/31/34/35-D50<br>and later, Si4732  |

Table 5. FM/RDS Receiver Property Summary (Continued)

| Prop   | Name                               | Description                                                                                                                                                                           | Default             | Available In                                                  |

|--------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------|

| 0x1305 | FM_SOFT_MUTE_<br>ATTACK_RATE       | Sets soft mute attack rate.<br>Smaller values provide<br>slower attack, and larger val-<br>ues provide faster attack. The<br>default is 8192 (approxi-<br>mately 8000 dB/s)           | 0x2000              | Si4706-D50,<br>Si4704/05/30/31/34/35-D50<br>and later, Si4732 |

| 0x1400 | FM_SEEK_BAND_<br>BOTTOM            | Sets the bottom of the FM band for seek. Default is 8750 (87.5 MHz).                                                                                                                  | 0x222E              | All                                                           |

| 0x1401 | FM_SEEK_BAND_TOP                   | Sets the top of the FM band for seek. Default is 10790 (107.9 MHz).                                                                                                                   | 0x2A26              | All                                                           |

| 0x1402 | FM_SEEK_FREQ_<br>SPACING           | Selects frequency spacing for FM seek. Default value is 10 (100 kHz).                                                                                                                 | 0x000A              | All                                                           |

| 0x1403 | FM_SEEK_TUNE_<br>SNR_THRESHOLD     | Sets the SNR threshold for a valid FM Seek/Tune. Default value is 3 dB.                                                                                                               | valid FM Seek/Tune. |                                                               |

| 0x1404 | FM_SEEK_TUNE_<br>RSSI_TRESHOLD     | Sets the RSSI threshold for a valid FM Seek/Tune. Default value is 20 dBµV.                                                                                                           | 0x0014              | All                                                           |

| 0x1500 | FM_RDS_INT_SOURCE                  | Configures RDS interrupt behavior.                                                                                                                                                    | 0x0000              | Si4705/06, Si431/32/35                                        |

| 0x1501 | FM_RDS_INT_FIFO_<br>COUNT          | Sets the minimum number of RDS groups stored in the receive FIFO required before RDSRECV is set.                                                                                      | 0x0000              | Si4705/06, Si431/32/35                                        |

| 0x1502 | FM_RDS_CONFIG                      | Configures RDS setting.                                                                                                                                                               | 0x0000              | Si4705/06, Si431/32/35                                        |

| 0x1503 | FM_RDS_CONFIDENCE                  | Sets the confidence level threshold for each RDS block.                                                                                                                               | 0x1111              | Si4706-D50,<br>Si4704/05/30/31/34/35-D50<br>and later, Si4732 |

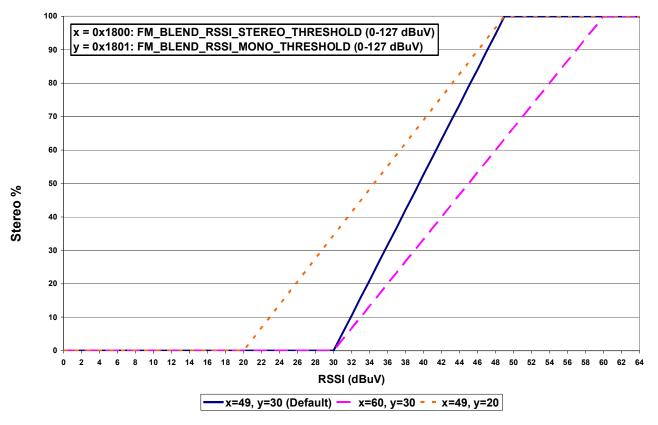

| 0x1800 | FM_BLEND_RSSI_<br>STEREO_THRESHOLD | Sets RSSI threshold for stereo blend. (Full stereo above threshold, blend below threshold.) To force stereo, set this to 0. To force mono, set this to 127. Default value is 49 dBµV. | 0x0031              | Si4706-D50,<br>Si4705/31/35-D50 and later,<br>Si4732          |

Table 5. FM/RDS Receiver Property Summary (Continued)

| Prop   | Name                                | Description                                                                                                                                                                                     | Default | Available In                                                                                  |

|--------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------|

| 0x1801 | FM_BLEND_RSSI<br>MONO_<br>THRESHOLD | Sets RSSI threshold for mono blend (Full mono below threshold, blend above threshold). To force stereo, set this to 0. To force mono, set this to 127. Default value is 30 dBµV.                | 0x001E  | Si4706-D50,<br>Si4705/31/35<br>-D50 and later, Si4732                                         |

| 0x1802 | FM_BLEND_RSSI_<br>ATTACK_RATE       | Sets the stereo to mono attack rate for RSSI based blend. Smaller values provide slower attack and larger values provide faster attack. The default is 4000 (approximately 16 ms).              | 0x0FA0  | Si4706-D50,<br>Si4705/31/35<br>-D50 and later, Si4732                                         |

| 0x1803 | FM_BLEND_RSSI_<br>RELEASE_RATE      | Sets the mono to stereo release rate for RSSI based blend. Smaller values provide slower release and larger values provide faster release. The default is 400 (approximately 164 ms).           | 0x0190  | Si4706-D50,<br>Si4705/31/35<br>-D50 and later, Si4732                                         |

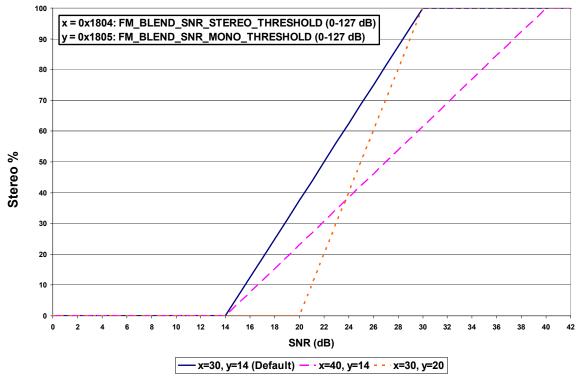

| 0x1804 | FM_BLEND_SNR_<br>STEREO_THRESHOLD   | Sets SNR threshold for stereo blend (Full stereo above threshold, blend below threshold). To force stereo, set this to 0. To force mono, set this to 127. Default value is 27 dB.               | 0x001B  | Si4704/05-D50 and later,<br>Si4706-D50 and later,<br>Si4730/31/34/35-D60 and<br>later, Si4732 |

| 0x1805 | FM_BLEND_SNR_MONO_<br>THRESHOLD     | Sets SNR threshold for mono<br>blend (Full mono below<br>threshold, blend above<br>threshold). To force stereo,<br>set this to 0. To force mono,<br>set this to 127. Default value<br>is 14 dB. | 0x000E  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732           |

| 0x1806 | FM_BLEND_SNR_<br>ATTACK_RATE        | Sets the stereo to mono attack rate for SNR based blend. Smaller values provide slower attack and larger values provide faster attack. The default is 4000 (approximately 16 ms).               | 0x0FA0  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732           |

## Table 5. FM/RDS Receiver Property Summary (Continued)

| Prop   | Name                                    | Description                                                                                                                                                                                            | Default | Available In                                                                           |

|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------|

| 0x1807 | FM_BLEND_SNR_<br>RELEASE_RATE           | Sets the mono to stereo release rate for SNR based blend. Smaller values provide slower release and larger values provide faster release. The default is 400 (approximately 164 ms).                   | 0x0190  | Si4704/05-D50<br>and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732 |

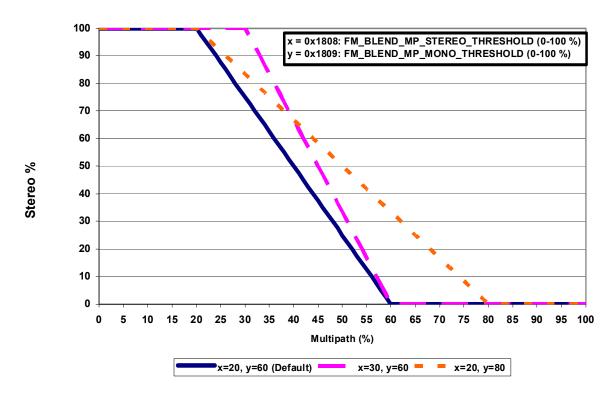

| 0x1808 | FM_BLEND_MULTIPATH_<br>STEREO_THRESHOLD | Sets multipath threshold for<br>stereo blend (Full stereo<br>below threshold, blend above<br>threshold). To force stereo,<br>set this to 100. To force<br>mono, set this to 0. Default<br>value is 20. | 0x0014  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732    |

| 0x1809 | FM_BLEND_MULTIPATH<br>MONO_THRESHOLD    | Sets Multipath threshold for<br>mono blend (Full mono<br>above threshold, blend below<br>threshold). To force stereo,<br>set to 100. To force mono, set<br>to 0. The default is 60.                    | 0x003C  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732    |

| 0x180A | FM_BLEND_MULTIPATH_<br>ATTACK_RATE      | Sets the stereo to mono attack rate for Multipath based blend. Smaller values provide slower attack and larger values provide faster attack. The default is 4000 (approximately 16 ms).                | 0x0FA0  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732    |

| 0x180B | FM_BLEND_MULTIPATH_<br>RELEASE_RATE     | Sets the mono to stereo release rate for Multipath based blend. Smaller values provide slower release and larger values provide faster release. The default is 40 (approximately 1.64 s).              | 0x0028  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732    |

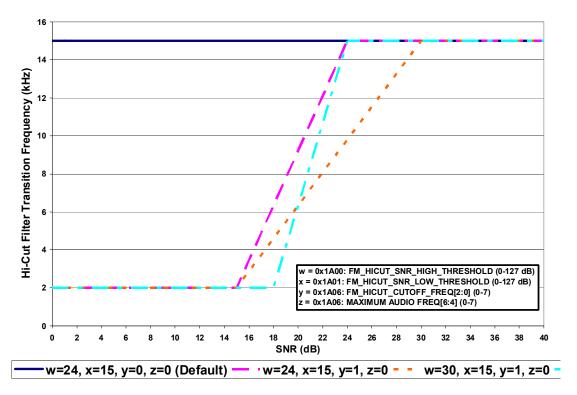

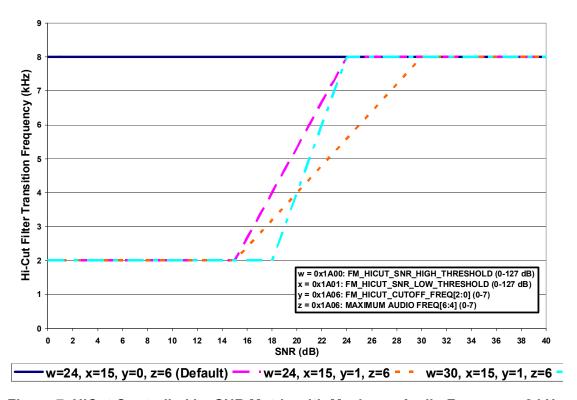

| 0x1A00 | FM_HICUT_SNR_HIGH_<br>THRESHOLD         | Sets the SNR level at which hi-cut begins to band limit. Default value is 24.                                                                                                                          | 0x0018  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60<br>and later, Si4732    |

| 0x1A01 | FM_HICUT_ SNR_LOW_<br>THRESHOLD         | Sets the SNR level at which hi-cut reaches maximum band limiting. Default value is 15.                                                                                                                 | 0x000F  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732    |

Table 5. FM/RDS Receiver Property Summary (Continued)

| Prop   | Name                                        | Description                                                                                                                | Default | Available In                                                                        |

|--------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------|

| 0x1A02 | FM_HICUT_<br>ATTACK_RATE                    | Sets the rate at which hi-cut<br>lowers the cut-off frequency.<br>Default value is 20000<br>(approximately 3 ms)           | 0x4E20  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732 |

| 0x1A03 | FM_HICUT_<br>RELEASE_RATE                   | Sets the rate at which hi-cut increases the cut-off frequency. Default value is 20. (approximately 3.3 s)                  | 0x0014  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732 |

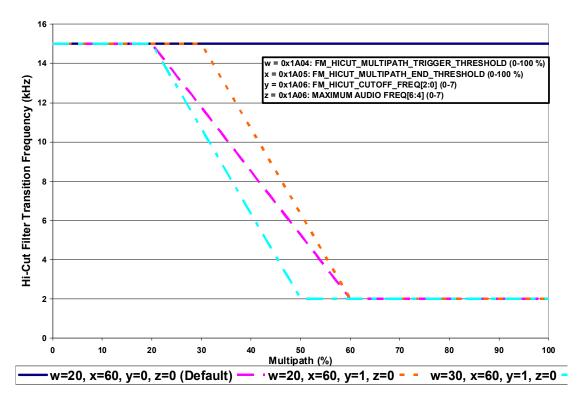

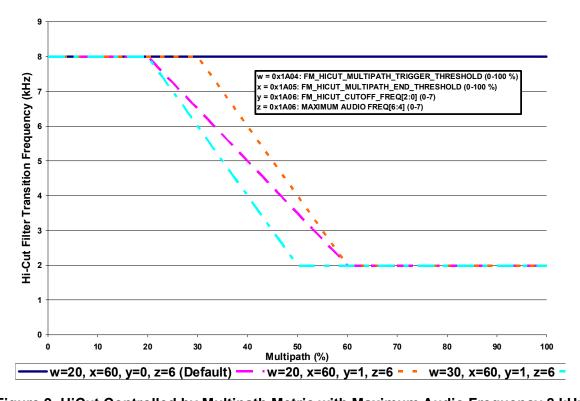

| 0x1A04 | FM_HICUT_<br>MULTIPATH_TRIGGER<br>THRESHOLD | Sets the MULTIPATH level at which hi-cut begins to band limit. Default value is 20.                                        | 0x0014  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732 |

| 0x1A05 | FM_HICUT_<br>MULTIPATH_END_<br>THRESHOLD    | Sets the MULTIPATH level at which hi-cut reaches maximum band limiting. Default value is 60.                               | 0x003C  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732 |

| 0x1A06 | FM_HICUT_CUTOFF_<br>FREQUENCY               | Sets the maximum band limit frequency for hi-cut and also sets the maximum audio frequency. Default value is 0 (disabled). | 0x0000  | Si4704/05-D50 and later,<br>Si4706-D50,<br>Si4730/31/34/35-D60 and<br>later, Si4732 |

| 0x4000 | RX_VOLUME                                   | Sets the output volume.                                                                                                    | 0x003F  | All                                                                                 |

| 0x4001 | RX_HARD_MUTE                                | Mutes the audio output. L and R audio outputs may be muted independently.                                                  | 0x0000  | All                                                                                 |

## Table 6. Status Response for the FM/RDS Receiver

| Bit    | D7  | D6  | D5 | D4 | D3     | D2     | D1 | D0     |

|--------|-----|-----|----|----|--------|--------|----|--------|

| STATUS | CTS | ERR | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |

| Bit | Name     | Function                                                                                                                                                                |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CTS      | Clear to Send.  0 = Wait before sending next command.  1 = Clear to send next command.                                                                                  |

| 6   | ERR      | Error. 0 = No error 1 = Error                                                                                                                                           |

| 5:4 | Reserved | Values may vary.                                                                                                                                                        |

| 3   | RSQINT   | Received Signal Quality Interrupt.  0 = Received Signal Quality measurement has not been triggered.  1 = Received Signal Quality measurement has been triggered.        |

| 2   | RDSINT   | Radio Data System (RDS) Interrupt (Si4705/31/32/35 Only).  0 = Radio data system interrupt has not been triggered.  1 = Radio data system interrupt has been triggered. |

| 1   | Reserved | Values may vary.                                                                                                                                                        |

| 0   | STCINT   | Seek/Tune Complete Interrupt.  0 = Tune complete has not been triggered.  1 = Tune complete has been triggered.                                                         |

#### 5.1.1. FM/RDS Receiver Commands

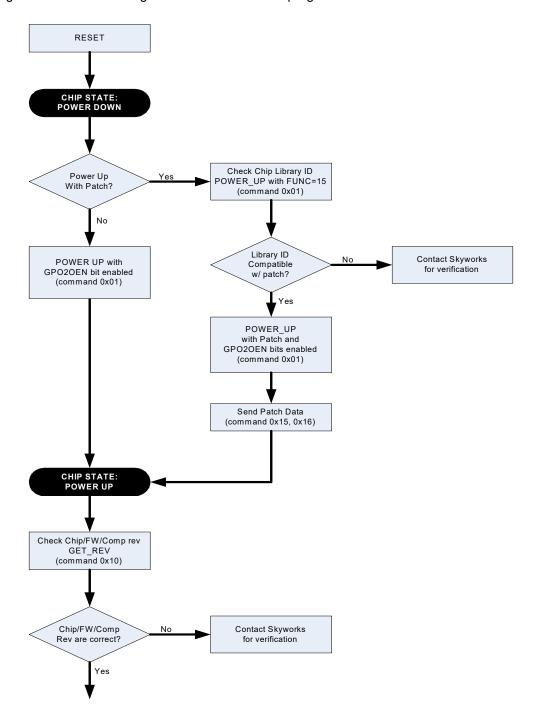

#### Command 0x01. POWER\_UP

Initiates the boot process to move the device from powerdown to powerup mode. The boot can occur from internal device memory or a system controller downloaded patch. To confirm that the patch is compatible with the internal device library revision, the library revision should be confirmed by issuing the POWER\_UP command with FUNC = 15 (query library ID). The device returns the response, including the library revision, and then moves into powerdown mode. The device can then be placed in powerup mode by issuing the POWER\_UP command with FUNC = 0 (FM Receive) and the patch may be applied (See Section "7.2. Powerup from a Component Patch" on page 132).

The POWER\_UP command configures the state of ROUT (pin 13, Si4732 pin 16) and LOUT (pin 14, Si4732 pin 1) for analog audio mode and GPO2/INT (pin 18, Si4732 pin 3) for interrupt operation. For the Si4705/31/32/35, the POWER\_UP command also configures the state of GPO3/DCLK (pin 17, Si4732 pin 2), DFS (pin 16, Si4732 pin 1), and DOUT (pin 15, Si4732 pin 16) for digital audio mode. The command configures GPO2/INT interrupts (GPO2OEN) and CTS interrupts (CTSIEN). If both are enabled, GPO2/INT is driven high during normal operation and low for a minimum of 1 µs during the interrupt. The CTSIEN bit is duplicated in the GPO\_IEN property. The command is complete when the CTS bit (and optional interrupt) is set.

**Note:** To change function (e.g. FM RX to AM RX), issue POWER\_DOWN command to stop current function; then, issue POW-ER\_UP to start new function.

**Note:** Delay at least 500 ms between powerup command and first tune command to wait for the oscillator to stabilize if XOSCEN is set and crystal is used as the RCLK.

Available in: All

Command Arguments: Two

Response Bytes: None (FUNC = 0), Seven (FUNC = 15)

#### Command

| Bit  | D7     | D6          | D5    | D4     | D3 | D2   | D1     | D0 |  |

|------|--------|-------------|-------|--------|----|------|--------|----|--|

| CMD  | 0      | 0           | 0     | 0      | 0  | 0    | 0      | 1  |  |

| ARG1 | CTSIEN | GPO20EN     | PATCH | XOSCEN |    | FUNC | C[3:0] |    |  |

| ARG2 |        | OPMODE[7:0] |       |        |    |      |        |    |  |

| ARG | Bit | Name    | Function                                                                                                             |

|-----|-----|---------|----------------------------------------------------------------------------------------------------------------------|

| 1   | 7   | CTSIEN  | CTS Interrupt Enable. 0 = CTS interrupt disabled. 1 = CTS interrupt enabled.                                         |

| 1   | 6   | GPO2OEN | GPO2 Output Enable.  0 = GPO2 output disabled.  1 = GPO2 output enabled.                                             |

| 1   | 5   | PATCH   | Patch Enable.  0 = Boot normally.  1 = Copy NVM to RAM, but do not boot. After CTS has been set, RAM may be patched. |

| ARG | Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 4   | XOSCEN      | Crystal Oscillator Enable.  0 = Use external RCLK (crystal oscillator disabled).  1 = Use crystal oscillator (RCLK and GPO3/DCLK with external 32.768 kHz crystal and OPMODE=00000101).  See Si47xx Data Sheet Application Schematic for external BOM details.                                                                                                                                                                                                                 |

| 1   | 3:0 | FUNC[3:0]   | Function.  0 = FM Receive.  1–14 = Reserved.  15 = Query Library ID.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | 7:0 | OPMODE[7:0] | Application Setting.  00000101 = Analog audio outputs (LOUT/ROUT).  00001011 = Digital audio output (DCLK, LOUT/DFS, ROUT/DIO) (Si4704/05/21/31/35/37/39/41/43/45/84/85 FMRX component 2.0 or later with XOSCEN = 0)  10110000 = Digital audio outputs (DCLK, DFS, DIO) (Si4704/05/31/35 FMRX component 2.0 or later with XOSCEN = 0).  10110101 = Analog and digital audio outputs (LOUT/ROUT and DCLK, DFS, DIO) (Si4704/05/31 FMRX component 2.0 or later with XOSCEN = 0). |

## Response (FUNC = 0, FM Receive)

| Bit    | D7  | D6  | D5 | D4 | D3     | D2     | D1 | D0     |

|--------|-----|-----|----|----|--------|--------|----|--------|

| STATUS | CTS | ERR | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |

## Response (FUNC = 15, Query Library ID)

| Bit    | D7  | D6           | D5 | D4  | D3         | D2     | D1 | D0     |  |  |

|--------|-----|--------------|----|-----|------------|--------|----|--------|--|--|

| STATUS | CTS | ERR          | Х  | Х   | RSQINT     | RDSINT | Х  | STCINT |  |  |

| RESP1  |     |              |    |     | PN[7:0]    |        |    | •      |  |  |

| RESP2  |     |              |    | F۱  | WMAJOR[7:  | 0]     |    |        |  |  |

| RESP3  |     |              |    | F\  | WMINOR[7:  | 0]     |    |        |  |  |

| RESP4  |     |              |    | RE  | SERVED[7   | :0]    |    |        |  |  |

| RESP5  |     |              |    | RE  | SERVED[7   | :0]    |    |        |  |  |

| RESP6  |     | CHIPREV[7:0] |    |     |            |        |    |        |  |  |

| RESP7  |     |              |    | LII | BRARYID[7: | 0]     |    |        |  |  |

| RESP | Bit | Name         | Function                             |

|------|-----|--------------|--------------------------------------|

| 1    | 7:0 | PN[7:0]      | Final 2 digits of part number (HEX). |

| 2    | 7:0 | FWMAJOR[7:0] | Firmware Major Revision (ASCII).     |

| 3    | 7:0 | FWMINOR[7:0] | Firmware Minor Revision (ASCII).     |

## **AN332**

| 4 | 7:0 | RESERVED[7:0]  | Reserved, various values. |

|---|-----|----------------|---------------------------|

| 5 | 7:0 | RESERVED[7:0]  | Reserved, various values. |

| 6 | 7:0 | CHIPREV[7:0]   | Chip Revision (ASCII).    |

| 7 | 7:0 | LIBRARYID[7:0] | Library Revision (HEX).   |

## Command 0x10. GET\_REV

Returns the part number, chip revision, firmware revision, patch revision and component revision numbers. The command is complete when the CTS bit (and optional interrupt) is set. This command may only be sent when in powerup mode.

Available in: All

Command arguments: None

Response bytes: Fifteen (Si4705/06 only), Eight (Si4704/3x)

#### Command

| Bit | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|----|----|----|----|----|----|----|----|

| CMD | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| Bit    | D7  | D6       | D5 | D4          | D3                   | D2     | D1 | D0     |  |  |

|--------|-----|----------|----|-------------|----------------------|--------|----|--------|--|--|

| STATUS | CTS | ERR      | Х  | Х           | RSQINT               | RDSINT | Х  | STCINT |  |  |

| RESP1  |     |          |    | PN          | [7:0]                |        |    |        |  |  |

| RESP2  |     |          |    | FWMA        | JOR[7:0]             |        |    |        |  |  |

| RESP3  |     |          |    | FWMIN       | IOR[7:0]             |        |    |        |  |  |

| RESP4  |     |          |    | PATCI       | H <sub>H</sub> [7:0] |        |    |        |  |  |

| RESP5  |     |          |    | PATC        | H <sub>L</sub> [7:0] |        |    |        |  |  |

| RESP6  |     |          |    | СМРМА       | JOR[7:0]             |        |    |        |  |  |

| RESP7  |     |          |    | CMPMI       | NOR[7:0]             |        |    |        |  |  |

| RESP8  |     |          |    | CHIPR       | EV[7:0]              |        |    |        |  |  |

| RESP10 |     |          |    | Rese        | erved                |        |    |        |  |  |

| RESP11 |     |          |    | Rese        | erved                |        |    |        |  |  |

| RESP12 |     |          |    | Rese        | erved                |        |    |        |  |  |

| RESP13 |     | Reserved |    |             |                      |        |    |        |  |  |

| RESP14 |     | Reserved |    |             |                      |        |    |        |  |  |

| RESP15 |     |          |    | CID[7:0] (S | Si4705 only)         |        |    |        |  |  |

| RESP | Bit | Name                     | Function                             |

|------|-----|--------------------------|--------------------------------------|

| 1    | 7:0 | PN[7:0]                  | Final 2 digits of Part Number (HEX). |

| 2    | 7:0 | FWMAJOR[7:0]             | Firmware Major Revision (ASCII).     |

| 3    | 7:0 | FWMINOR[7:0]             | Firmware Minor Revision (ASCII).     |

| 4    | 7:0 | PATCH <sub>H</sub> [7:0] | Patch ID High Byte (HEX).            |

| 5    | 7:0 | PATCH <sub>L</sub> [7:0] | Patch ID Low Byte (HEX).             |

| 6    | 7:0 | CMPMAJOR[7:0]            | Component Major Revision (ASCII).    |

| 7    | 7:0 | CMPMINOR[7:0]            | Component Minor Revision (ASCII).    |

| 8    | 7:0 | CHIPREV[7:0]             | Chip Revision (ASCII).               |

| 15   | 7:0 | CID[7:0]                 | CID (Si4705/06 only).                |

### Command 0x11. POWER\_DOWN

Moves the device from powerup to powerdown mode. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup mode. Note that only the POWER\_UP command is accepted in powerdown mode. If the system controller writes a command other than POWER\_UP when in powerdown mode, the device does not respond. The device will only respond when a POWER\_UP command is written. GPO pins are powered down and not active during this state. For optimal power down current, GPO2 must be either internally driven low through GPIO\_CTL command or externally driven low.

**Note:** In FMRX component 1.0, a reset is required when the system controller writes a command other than POWER\_UP when in powerdown mode.

Note: The following describes the state of all the pins when in powerdown mode:

GPIO1, GPIO2, and GPIO3 = 0

ROUT, LOUT, DOUT, DFS = HiZ

Available in: All

Command arguments: None Response bytes: None

#### Command

| Bit | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|----|----|----|----|----|----|----|----|

| CMD | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| Bit    | D7  | D6  | D5 | D4 | D3     | D2     | D1 | D0     |

|--------|-----|-----|----|----|--------|--------|----|--------|

| STATUS | CTS | ERR | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |

## Command 0x12. SET\_PROPERTY

Sets a property shown in Table 5, "FM/RDS Receiver Property Summary," on page 7. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup mode. See Figure 25, "CTS and SET\_PROPERTY Command Complete tCOMP Timing Model," on page 143 and Table 31, "Command Timing Parameters for the FM Receiver," on page 144.

Available in: All

Command Arguments: Five Response bytes: None

#### Command

| Bit  | D7 | D6                       | D5 | D4   | D3                   | D2 | D1 | D0 |  |  |  |

|------|----|--------------------------|----|------|----------------------|----|----|----|--|--|--|

| CMD  | 0  | 0                        | 0  | 1    | 0                    | 0  | 1  | 0  |  |  |  |

| ARG1 | 0  | 0                        | 0  | 0    | 0                    | 0  | 0  | 0  |  |  |  |

| ARG2 |    | PROP <sub>H</sub> [7:0]  |    |      |                      |    |    |    |  |  |  |

| ARG3 |    |                          |    | PROF | P <sub>L</sub> [7:0] |    |    |    |  |  |  |

| ARG4 |    | PROPD <sub>H</sub> [7:0] |    |      |                      |    |    |    |  |  |  |

| ARG5 |    |                          |    | PROP | D <sub>L</sub> [7:0] |    |    |    |  |  |  |

| ARG | Bit | Name                     | Function                                                                                                       |

|-----|-----|--------------------------|----------------------------------------------------------------------------------------------------------------|

| 1   | 7:0 | Reserved                 | Always write to 0.                                                                                             |

| 2   | 7:0 | PROP <sub>H</sub> [7:0]  | Property High Byte. This byte in combination with PROP <sub>L</sub> is used to specify the property to modify. |

| 3   | 7:0 | PROP <sub>L</sub> [7:0]  | Property Low Byte. This byte in combination with PROP <sub>H</sub> is used to specify the property to modify.  |

| 4   | 7:0 | PROPD <sub>H</sub> [7:0] | Property Value High Byte. This byte in combination with PROPD <sub>L</sub> is used to set the property value.  |

| 5   | 7:0 | PROPD <sub>L</sub> [7:0] | Property Value Low Byte. This byte in combination with PROPD <sub>H</sub> is used to set the property value.   |

## Command 0x13. GET\_PROPERTY

Gets a property as shown in Table 5, "FM/RDS Receiver Property Summary," on page 7. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup mode.

Available in: All

Command arguments: Three Response bytes: Three

#### Command

| Bit  | D7 | D6                      | D5 | D4   | D3                   | D2 | D1 | D0 |  |  |

|------|----|-------------------------|----|------|----------------------|----|----|----|--|--|

| CMD  | 0  | 0                       | 0  | 1    | 0                    | 0  | 1  | 1  |  |  |

| ARG1 | 0  | 0                       | 0  | 0    | 0                    | 0  | 0  | 0  |  |  |

| ARG2 |    | PROP <sub>H</sub> [7:0] |    |      |                      |    |    |    |  |  |

| ARG3 |    |                         |    | PROF | P <sub>L</sub> [7:0] |    |    |    |  |  |

| ARG | Bit | Name                    | Function                                                                                                    |

|-----|-----|-------------------------|-------------------------------------------------------------------------------------------------------------|

| 1   | 7:0 | Reserved                | Always write to 0.                                                                                          |

| 2   | 7:0 | PROP <sub>H</sub> [7:0] | Property High Byte. This byte in combination with PROP <sub>L</sub> is used to specify the property to get. |

| 3   | 7:0 | PROP <sub>L</sub> [7:0] | Property Low Byte. This byte in combination with PROP <sub>H</sub> is used to specify the property to get.  |

| Bit    | D7  | D6                       | D5 | D4 | D3     | D2     | D1 | D0     |  |  |  |  |

|--------|-----|--------------------------|----|----|--------|--------|----|--------|--|--|--|--|

| STATUS | CTS | ERR                      | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |  |  |  |  |

| RESP1  | 0   | 0                        | 0  | 0  | 0      | 0      | 0  | 0      |  |  |  |  |

| RESP2  |     | PROPD <sub>H</sub> [7:0] |    |    |        |        |    |        |  |  |  |  |

| RESP3  |     | PROPD <sub>L</sub> [7:0] |    |    |        |        |    |        |  |  |  |  |

| RESP | Bit | Name                     | Function                                                                                                            |

|------|-----|--------------------------|---------------------------------------------------------------------------------------------------------------------|

| 1    | 7:0 | Reserved                 | Always returns 0.                                                                                                   |

| 2    | 7:0 | PROPD <sub>H</sub> [7:0] | Property Value High Byte. This byte in combination with PROPD <sub>L</sub> represents the requested property value. |

| 3    | 7:0 | PROPD <sub>L</sub> [7:0] | Property Value High Byte. This byte in combination with PROPD <sub>H</sub> represents the requested property value. |

### Command 0x14. GET\_INT\_STATUS

Updates bits 6:0 of the status byte. This command should be called after any command that sets the STCINT, RDSINT, or RSQINT bits. When polling this command should be periodically called to monitor the STATUS byte, and when using interrupts, this command should be called after the interrupt is set to update the STATUS byte. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This command may only be set when in powerup mode.

Available in: All

Command arguments: None Response bytes: None

#### Command

| Bit | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|----|----|----|----|----|----|----|----|

| CMD | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  |

#### Response

| Bit    | D7  | D6  | D5 | D4 | D3     | D2     | D1 | D0     |

|--------|-----|-----|----|----|--------|--------|----|--------|

| STATUS | CTS | ERR | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |

## Command 0x20. FM\_TUNE\_FREQ

Sets the FM Receive to tune a frequency between 64 and 108 MHz in 10 kHz units. The CTS bit (and optional interrupt) is set when it is safe to send the next command. The ERR bit (and optional interrupt) is set if an invalid argument is sent. Note that only a single interrupt occurs if both the CTS and ERR bits are set. The optional STC interrupt is set when the command completes. The STCINT bit is set only after the GET\_INT\_STATUS command is called. This command may only be sent when in powerup mode. The command clears the STC bit if it is already set. See Figure 24, "CTS and STC Timing Model," on page 142 and Table 31, "Command Timing Parameters for the FM Receiver," on page 144.

FM: LO frequency is 128 kHz above RF for RF frequencies ≤ 90 MHz and 128 kHz below RF for RF frequencies > 90 MHz. For example, LO frequency is 80.128 MHz when tuning to 80.00 MHz.

Note: For FMRX components 2.0 or earlier, tuning range is 76–108 MHz.

**Note:** Fast bit is supported in FMRX components 4.0 or later. **Note:** Freeze bit is supported in FMRX components 4.0 or later.

Available in: All

Command arguments: Four Response bytes: None

## Command

| Bit  | D7 | D6          | D5 | D4   | D3                   | D2 | D1     | D0   |  |  |

|------|----|-------------|----|------|----------------------|----|--------|------|--|--|

| CMD  | 0  | 0           | 1  | 0    | 0                    | 0  | 0      | 0    |  |  |

| ARG1 | 0  | 0           | 0  | 0    | 0                    | 0  | FREEZE | FAST |  |  |

| ARG2 |    |             |    | FREC | H[7:0]               |    |        |      |  |  |

| ARG3 |    |             |    | FREC | Q <sub>L</sub> [7:0] |    |        |      |  |  |

| ARG4 |    | ANTCAP[7:0] |    |      |                      |    |        |      |  |  |

| ARG | Bit | Name                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 7:1 | Reserved                | Always write to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1   | 1   | FREEZE                  | Freeze Metrics During Alternate Frequency Jump. If set will cause the blend, hicut, and softmute to transition as a function of the associated attack/release parameters rather than instantaneously when tuning to alternate frequency.                                                                                                                                                                                                                                                                                                   |

| 1   | 0   | FAST                    | FAST Tuning. If set, executes fast and invalidated tune. The tune status will not be accurate.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2   | 7:0 | FREQ <sub>H</sub> [7:0] | Tune Frequency High Byte. This byte in combination with FREQ <sub>L</sub> selects the tune frequency in 10 kHz. In FM mode the valid range is from 6400 to 10800 (64–108 MHz).                                                                                                                                                                                                                                                                                                                                                             |

| 3   | 7:0 | FREQ <sub>L</sub> [7:0] | Tune Frequency Low Byte. This byte in combination with FREQ <sub>H</sub> selects the tune frequency in 10 kHz. In FM mode the valid range is from 6400 to 10800 (64–108 MHz).                                                                                                                                                                                                                                                                                                                                                              |

| 4   | 7:0 | ANTCAP[7:0]             | <ul> <li>Antenna Tuning Capacitor (valid only when using TXO/LPI pin as the antenna input).</li> <li>This selects the value of the antenna tuning capacitor manually, or automatically if set to zero. The valid range is 0 to 191. Automatic capacitor tuning is recommended.</li> <li>Note: When tuned manually, the varactor is offset by four codes. For example, if the varactor is set to a value of 5 manually, when read back the value will be 1. The four codes (1pf) delta accounts for the capacitance at the chip.</li> </ul> |

| Bit    | D7  | D6  | D5 | D4 | D3     | D2     | D1 | D0     |

|--------|-----|-----|----|----|--------|--------|----|--------|

| STATUS | CTS | ERR | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |

### Command 0x21. FM\_SEEK\_START

Begins searching for a valid frequency. Clears any pending STCINT or RSQINT interrupt status. The CTS bit (and optional interrupt) is set when it is safe to send the next command. RSQINT status is only cleared by the RSQ status command when the INTACK bit is set. The ERR bit (and optional interrupt) is set if an invalid argument is sent. Note that only a single interrupt occurs if both the CTS and ERR bits are set. The optional STC interrupt is set when the command completes. The STCINT bit is set only after the GET\_INT\_STATUS command is called. This command may only be sent when in powerup mode. The command clears the STCINT bit if it is already set. See Figure 24, "CTS and STC Timing Model," on page 142 and Table 31, "Command Timing Parameters for the FM Receiver," on page 144.

Available in: All

Command arguments: One Response bytes: None

#### Command

| Bit  | D7 | D6 | D5 | D4 | D3     | D2   | D1 | D0 |

|------|----|----|----|----|--------|------|----|----|

| CMD  | 0  | 0  | 1  | 0  | 0      | 0    | 0  | 1  |

| ARG1 | 0  | 0  | 0  | 0  | SEEKUP | WRAP | 0  | 0  |

| ARG | Bit | Name     | Function                                                                                          |

|-----|-----|----------|---------------------------------------------------------------------------------------------------|

| 1   | 7:4 | Reserved | Always write to 0.                                                                                |

| 1   | 3   | SEEKUP   | Seek Up/Down. Determines the direction of the search, either UP = 1, or DOWN = 0.                 |

| 1   | 2   | WRAP     | Wrap/Halt.  Determines whether the seek should Wrap = 1, or Halt = 0 when it hits the band limit. |

| 1   | 1:0 | Reserved | Always write to 0.                                                                                |

| Bit    | D7  | D6  | D5 | D4 | D3     | D2     | D1 | D0     |

|--------|-----|-----|----|----|--------|--------|----|--------|

| STATUS | CTS | ERR | Х  | Х  | RSQINT | RDSINT | Х  | STCINT |

### Command 0x22. FM\_TUNE\_STATUS

Returns the status of FM\_TUNE\_FREQ or FM\_SEEK\_START commands. The command returns the current frequency, RSSI, SNR, multipath, and the antenna tuning capacitance value (0-191). The command clears the STCINT interrupt bit when INTACK bit of ARG1 is set. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup mode.

Available in: All

Command arguments: One Response bytes: Seven

#### Command

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1     | D0     |

|------|----|----|----|----|----|----|--------|--------|

| CMD  | 0  | 0  | 1  | 0  | 0  | 0  | 1      | 0      |

| ARG1 | 0  | 0  | 0  | 0  | 0  | 0  | CANCEL | INTACK |

| ARG | Bit | Name     | Function                                                                                     |

|-----|-----|----------|----------------------------------------------------------------------------------------------|

| 1   | 7:2 | Reserved | Always write to 0.                                                                           |

| 1   | 1   | CANCEL   | Cancel seek.  If set, aborts a seek currently in progress.                                   |

| 1   | 0   | INTACK   | Seek/Tune Interrupt Clear. If set, clears the seek/tune complete interrupt status indicator. |

| Bit    | D7                          | D6                          | D5    | D4          | D3           | D2       | D1    | D0     |  |  |  |  |

|--------|-----------------------------|-----------------------------|-------|-------------|--------------|----------|-------|--------|--|--|--|--|

| STATUS | CTS                         | ERR                         | Х     | Х           | RSQINT       | RDSINT   | Х     | STCINT |  |  |  |  |

| RESP1  | BLTF                        | Х                           | Х     | Х           | Х            | Х        | AFCRL | VALID  |  |  |  |  |

| RESP2  |                             | READFREQ <sub>H</sub> [7:0] |       |             |              |          |       |        |  |  |  |  |

| RESP3  | READFREQ <sub>L</sub> [7:0] |                             |       |             |              |          |       |        |  |  |  |  |

| RESP4  |                             |                             |       | RSS         | I[7:0]       |          |       |        |  |  |  |  |

| RESP5  |                             |                             |       | SNR         | [7:0]        |          |       |        |  |  |  |  |

| RESP6  | MULT[7:0]                   |                             |       |             |              |          |       |        |  |  |  |  |

| RESP7  |                             |                             | READA | ANTCAP[7:0] | (Si4704/05/0 | 06 only) |       |        |  |  |  |  |

| RESP | Bit | Name                        | Function                                                                                                                                                                 |

|------|-----|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 7   | BLTF                        | Band Limit.                                                                                                                                                              |

|      |     |                             | Reports if a seek hit the band limit (WRAP = 0 in FM_START_SEEK) or wrapped to the original frequency (WRAP = 1).                                                        |

| 1    | 6:2 | Reserved                    | Always returns 0.                                                                                                                                                        |

| 1    | 1   | AFCRL                       | AFC Rail Indicator.                                                                                                                                                      |

|      |     |                             | Set if the AFC rails.                                                                                                                                                    |

| 1    | 0   | VALID                       | Valid Channel.                                                                                                                                                           |

|      |     |                             | Set if the channel is currently valid as determined by the seek/tune properties (0x1403, 0x1404, 0x1108) and would have been found during a Seek.                        |

| 2    | 7:0 | READFREQ <sub>H</sub> [7:0] | Read Frequency High Byte.                                                                                                                                                |

|      |     |                             | This byte in combination with READFREQ <sub>L</sub> returns frequency being tuned (10 kHz).                                                                              |

| 3    | 7:0 | READFREQ <sub>L</sub> [7:0] | Read Frequency Low Byte.                                                                                                                                                 |

|      |     |                             | This byte in combination with READFREQ <sub>H</sub> returns frequency being tuned (10 kHz).                                                                              |

| 4    | 7:0 | RSSI[7:0]                   | Received Signal Strength Indicator.                                                                                                                                      |

|      |     |                             | This byte contains the receive signal strength when tune is complete (dBµV).                                                                                             |

| 5    | 7:0 | SNR[7:0]                    | SNR.                                                                                                                                                                     |

|      |     |                             | This byte contains the SNR metric when tune is complete (dB).                                                                                                            |

| 6    | 7:0 | MULT[7:0]                   | Multipath.                                                                                                                                                               |

|      |     |                             | This byte contains the multipath metric when tune is complete. Multipath indicator is available only for Si4706-D50 and Si4704/05/30/31/34/35-D50 and later, and Si4732. |

| 7    | 7:0 | READANTCAP [7:0]            | Read Antenna Tuning Capacitor (Si4704/05/06 only).                                                                                                                       |

|      |     |                             | This byte contains the current antenna tuning capacitor value.                                                                                                           |

#### Command 0x23. FM\_RSQ\_STATUS

Returns status information about the received signal quality. The commands returns the RSSI, SNR, frequency offset, and stereo blend percentage. It also indicates valid channel (VALID), soft mute engagement (SMUTE), and AFC rail status (AFCRL). This command can be used to check if the received signal is above the RSSI high threshold as reported by RSSILINT. It can also be used to check if the signal is above the SNR high threshold as reported by SNRHINT, or below the SNR low threshold as reported by SNRLINT. For the Si4706, it can be used to check if the detected multipath is above the multipath high threshold as reported by MULTHINT, or below the multipath low threshold as reported by MULTLINT. If the PILOT indicator is set, it can also check whether the blend has crossed a threshold as indicated by BLENDINT. The command clears the RSQINT, BLENDINT, SNRHINT, SNRLINT, RSSIHINT, MULTHINT, and MULTLINT interrupt bits when INTACK bit of ARG1 is set. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup mode.

Available in: All

Command arguments: One Response bytes: Seven

#### Command

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0     |

|------|----|----|----|----|----|----|----|--------|

| CMD  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1      |

| ARG1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | INTACK |

| ARG | Bit | Name   | Function                                                                                                                                        |

|-----|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0   | INTACK | Interrupt Acknowledge.  0 = Interrupt status preserved.  1 = Clears RSQINT, BLENDINT, SNRHINT, SNRLINT, RSSIHINT, RSSILINT, MULTHINT, MULTLINT. |

| Bit    | D7        | D6  | D5       | D4       | D3          | D2      | D1       | D0        |  |  |

|--------|-----------|-----|----------|----------|-------------|---------|----------|-----------|--|--|

| STATUS | CTS       | ERR | Х        | Х        | RSQINT      | RDSINT  | Х        | STCINT    |  |  |

| RESP1  | BLENDINT  | Х   | MULTHINT | MULTLINT | SNRHINT     | SNRLINT | RSSIHINT | RSSIILINT |  |  |

| RESP2  | Х         | Х   | Х        | Х        | SMUTE       | Х       | AFCRL    | VALID     |  |  |

| RESP3  | PILOT     |     |          | S        | STBLEND[6:0 | ]       |          |           |  |  |

| RESP4  |           |     |          | RSS      | I[7:0]      |         |          |           |  |  |

| RESP5  |           |     |          | SNR      | [7:0]       |         |          |           |  |  |

| RESP6  | MULT[7:0] |     |          |          |             |         |          |           |  |  |

| RESP7  |           |     |          | FREQC    | FF[7:0]     |         |          |           |  |  |

| RESP | Bit | Name         | Function                                                                                                                                                                                                                                                      |

|------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

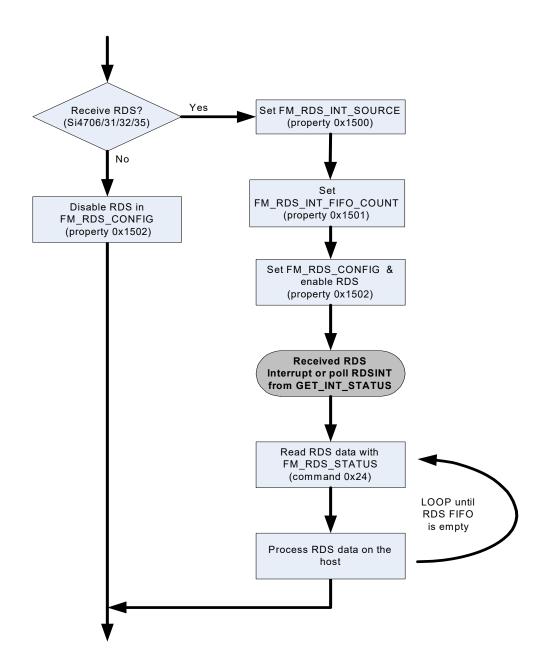

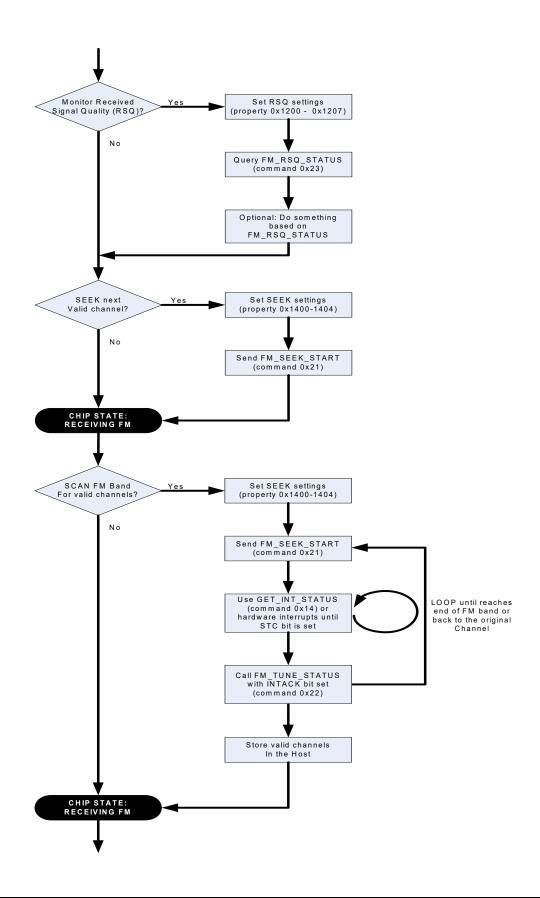

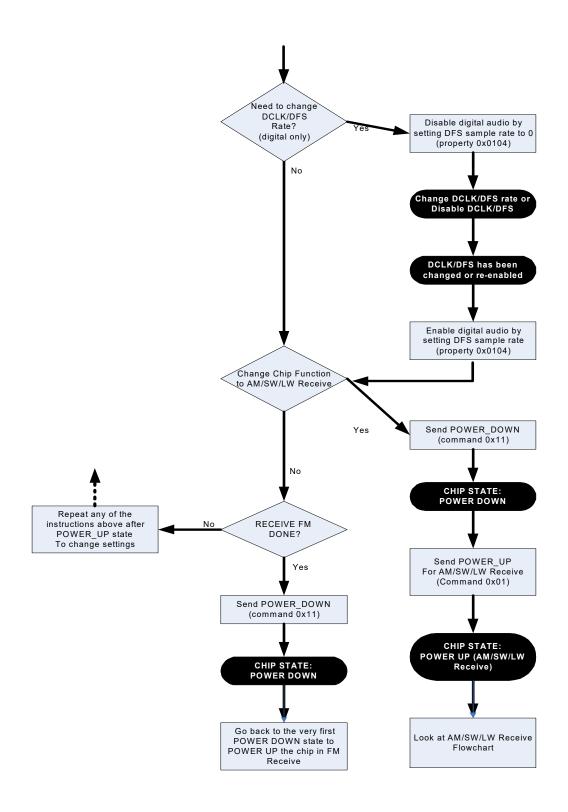

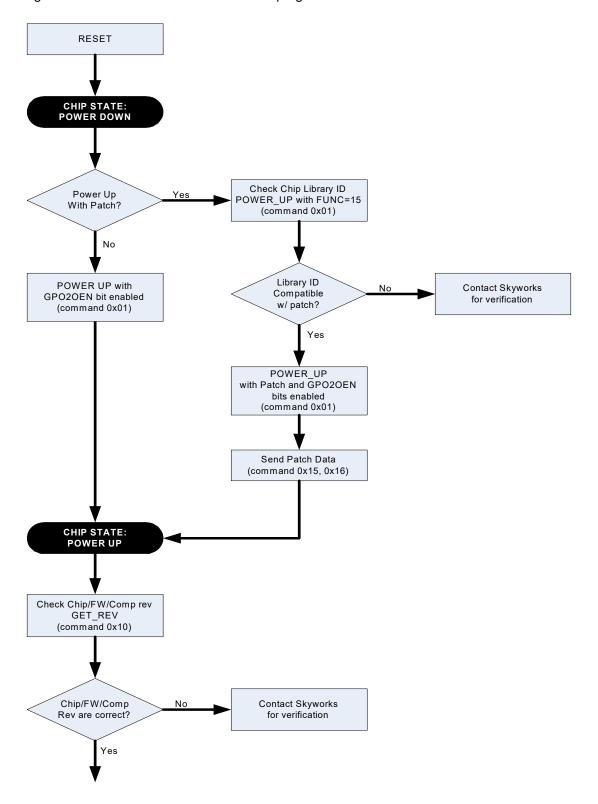

| 1    | 7   | BLENDINT     | Blend Detect Interrupt.  0 = Blend is within the Blend threshold settings.  1 = Blend goes above or below the Blend threshold settings.                                                                                                                       |