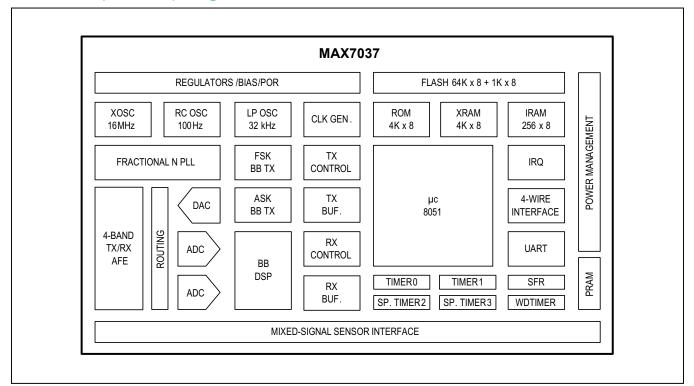

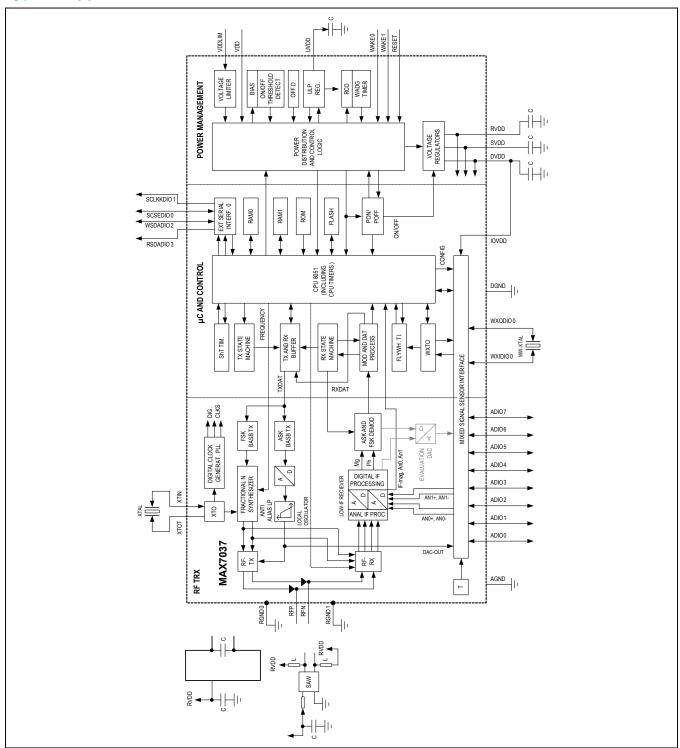

### **General Description**

The MAX7037 is an ultra-low-power, high-performance quad-band multichannel transceiver with integrated 8051 microcontroller, flash memory, and sensor interface. The MAX7037 runs from a minimum supply voltage of only 2.1V, extending battery life and enabling it to cope with different sources of energy, like solar cells, electromechanical or thermoelectrical energy. Hardware-implemented transmit-and-receive routines, in combination with a microcontroller, enable a high-efficiency transceiver system for wireless fail-safe multiband/multichannel communication with advanced FSK and ASK protocol features. Sleep modes allow easy implementation of low-power applications with fast reaction times.

### **Applications**

- Ultra-Low-Power Sensor Networks

- Smart Metering

- Building Automation

- Short-Range Communication

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Ultra-Low-Power Consumption for Battery-Based Operation

- Current Consumption TX (P<sub>OUT</sub> = +6dBm, FSK): 16mA

- · Current Consumption RX (FSK): 22mA

- Current Consumption Deep Sleep Mode (Watchdog Timer and PRAM Active): 100nA

- Supply Voltage Range: 2.1V to 5.5V

- Integrated Ultra-Low-Power On/Off Voltage Threshold Detectors

- Worldwide Usable Frequency Band Coverage

- ISM Band Frequency Coverage: 315/433/868/915~930MHz

- Fractional-N LO Generation For Multichannel Operation

- RF Synthesizer Resolution: 244Hz/488Hz

- FFSK/FMSK/ASK Modulation for Optimum Compatibility with Various Communication Standards

- · Gross Data Rates: Up To 125Kbit/s

- ASK with Programmable Transition Shape for Spectral Tuning

- Fully Integrated RF, TX, and RX Front-End for Minimum External Components

- Maximum TX Output Power (R<sub>LOAD</sub> = 400Ω): +10dBm

- RX Sensitivity (FFSK, BW = 150kHz): -100dBm

- Mixed-Signal Sensor Interface with Analog I/O Through ADC/DAC and On-Chip Buffers (Contact Factory for Future Support)

- Integrated 9-Bit Sigma Delta ADC for Applications

- · Integrated 8-Bit DAC

- 8 Mixed-Signal I/Os with Versatile Switching Matrix; Up to 18 Digital I/Os

- Wristwatch Crystal-Based Real-Time Clock (Contact Factory for Future Support)

- · Wristwatch Crystal Oscillator Integrated: 32768Hz

### **Absolute Maximum Ratings**

| Continuous Current In/Out of Pins±100mA Duration of Pin Short Circuit to Ground or Supply Continuous Duration of Short-Circuit Between PinsContinuous Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) Package 1 Multilayer Board |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (derate 37mW/°C above +70°C)2600mW                                                                                                                                                                                                     |

| Junction Temperature+150°C                                                                                                                                                                                                             |

| Operating Temperature Range40°C to +85°C                                                                                                                                                                                               |

| Storage Temperature Range65°C to +150°C                                                                                                                                                                                                |

| Lead Temperature (soldering, 10s)+300°C                                                                                                                                                                                                |

| Supply Voltage at High-Voltage Supply Pins                                                                                                                                                                                             |

| V <sub>DD</sub> and V <sub>DDLIM</sub> 0.5V to +6.0V                                                                                                                                                                                   |

| Supply Voltage for Mixed-Signal Sensor Interface                                                                                                                                                                                       |

| (GPIO1) and Extended Serial Interface 0 Pins                                                                                                                                                                                           |

| (GPIO0)0.5V to +6.0V                                                                                                                                                                                                                   |

| Voltage at GPIO1 Port Pins (ADIO0~7) and GPIO2 Port Pins                                                                                                                                                                               |

| (WXIDIO, WXODIO) in Analog Mode0.5V to 2.0V                                                                                                                                                                                            |

| age at Digital Input Pins                               |               |

|---------------------------------------------------------|---------------|

| VAKE0, WAKE1, RESET GND                                 | 0.5V to 3.6V  |

| age at GPIO2 Port Pins                                  |               |

| WXIDIO, WXODIO) in digital mode                         | 0.5V to 2.0V  |

| age at GPIO0 Port Pins                                  |               |

| BIST_DONE, TEST1, TEST3, SCSEDIO0,                      | ,             |

| CLKDIO1, WSDADIO2, RSDADIO3, BIST                       | Γ_PASS) and   |

| SPIO1 Port Pins (ADIO0~7) in Digital Mode               | e0.5V to 6.0V |

| kimum Permanent Elimination Current at t                | he Parallel   |

| Regulator (Generally Limited by Max ( $V_{ m DD}$ )     | ) and PTOT)   |

|                                                         | 50mA          |

| ut Current Into Any Pin Except Supply Pins              | S             |

|                                                         | 50mA to +50mA |

| ctrostatic Discharge Sensible Pins, as are:             |               |

| RFP, RFN, XTIN, XTOT, $V_{ m DD}$ , $V_{ m DDLIM}$ , UV | DD, WAKE0,    |

| VAKE1, RESET                                            | 2kV           |

| ctrostatic Discharge Normal Pins                        |               |

| ver Dissipation                                         | 300 mW        |

Note 1: ESD Test according to AEC-Q100-002 (JESD22-A114): HBM: R = 1.5kΩ, C = 100pF. ESD protected to 2kV Human Body Model.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 2)**

40-Pin QFN (6mm x 6mm)

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......27°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )........16.5°C/W

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

#### **Operating Conditions**

| PARAMETER                                                                                   | SYMBOL             | CONDITIONS                                                                             | MIN                                   | TYP  | MAX | UNITS |

|---------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------|---------------------------------------|------|-----|-------|

| Positive Supply Voltage                                                                     | V <sub>DD</sub>    | At input pins V <sub>DD</sub> and V <sub>DDLIM</sub>                                   | Min<br>(V <sub>OFF</sub> )            | 3.3  | 5.5 | V     |

| Tolerated Supply Voltage Slope for Ambient Supply                                           | V <sub>DDSLP</sub> | Valid for rising and falling slope.                                                    | 0                                     | 3    | 5   | V/ms  |

| Positive Supply Voltage at<br>Shutdown                                                      | V <sub>DDS</sub>   | At input pins V <sub>DD</sub> and V <sub>DDLIM</sub> . No normal performance required. | Min<br>(V <sub>OFF</sub> ) –<br>0.025 |      |     | V     |

| Supply Voltage for Mixed-Signal<br>Sensor Interface and Extended<br>Serial Interface 0 Pins | V <sub>IOVDD</sub> | GPIO0/1                                                                                | 1.7                                   | DVDD | 5.5 | V     |

| Ground                                                                                      | GND                |                                                                                        |                                       | 0    |     | V     |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

#### **Operating Conditions (continued)**

| PARAMETER                                                                           | SYMBOL                        | CONDITIONS                                                                                                                                                                                                     | MIN             | TYP  | MAX                  | UNITS                    |

|-------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|----------------------|--------------------------|

| Logic Levels on Digital I/O Pins of GPIO0/1 Ports                                   | V <sub>L</sub>                | All pins which are or can be configured as digital I/O.                                                                                                                                                        | Min<br>(VIOVDD) |      | Max<br>(VIOVDD)      |                          |

| Tolerated Ripple on V <sub>DD</sub>                                                 | V <sub>DDR</sub>              | 100Hz ripple from full wave rectifier on V <sub>DD</sub> whereas Min(V <sub>DD</sub> ) > V <sub>ON</sub>                                                                                                       |                 |      | 50                   | mV <sub>P-P</sub>        |

| ADC Measurement Input<br>Common Mode Range                                          |                               | The sigma-delta ADCs have a differential input. The ADC input CMR is provided by the R2R buffer.                                                                                                               | 0               |      | RVDD                 | V                        |

| ADC Measurement Input<br>Amplitude for Single-Ended or<br>Differential Measurements | VIN_MEAS                      | Measurement possible only via<br>R2R input buffer.<br>Possible selectable internal<br>references: GND, RVDD,<br>VADCCMR (~0.8V), VBG                                                                           | 0               |      | ±RVDD                | Vd                       |

| Analog Input Range<br>(GPIO1 Port, ADIO0~7)                                         |                               | Single-ended                                                                                                                                                                                                   | 0               |      | VRVDD                | V                        |

| Nominal Differential Load<br>Resistance                                             | R <sub>LOAD</sub><br>(Note 3) | Resonance resistance R <sub>LOAD</sub> at fCTX of the load resonance circuit with the impedance Z <sub>LOAD</sub> . Smaller R <sub>LOAD</sub> values will lead to increased current consumption for equal POUT |                 | 400  | 900                  | Ω                        |

| RF Port DC Supply Voltage                                                           |                               | RF_N, RF_P pins                                                                                                                                                                                                | Min<br>(RVDD)   | RVDD | Max<br>(RVDD)        | V                        |

| Differential Voltage Swing<br>Between RF Pins                                       | V <sub>TX</sub>               | Absolute Maximum Rating. Must be respected even if different load impedances are used                                                                                                                          |                 |      | 6.0                  | V <sub>P-P</sub>         |

| Required Relative 16M XTAL<br>Frequency Tolerance for WB/<br>DWB Operation          | d <sub>fXO</sub>              | ~315MHz band:<br>~433MHz band:<br>~868MHz band:<br>~915MHz band:                                                                                                                                               |                 |      | 55<br>40<br>20<br>19 | ppm<br>ppm<br>ppm<br>ppm |

| TX-RX Carrier Frequency<br>Deviation                                                | d <sub>fTRD</sub>             | Application design requirement.<br>Given by SAW based ASK<br>transmitters                                                                                                                                      |                 |      | 100                  | kHz                      |

| Ambient Operating Temperature                                                       | T <sub>A</sub>                |                                                                                                                                                                                                                | -40°C           |      | +85°C                | °C                       |

Note 3: Maximum differential  $R_{LOAD}$  for +6dBm output power (based on  $P = V^2/R$  formula and considering  $RVDD_{MIN}$  and  $V_{DSAT}$  of output stage MOS).

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

#### **Current Consumption**

| PARAMETER                                      | SYMBOL                    | CONDITIONS                                                                                                          | MIN TYP | MAX | UNITS |

|------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|---------|-----|-------|

| Current Consumption in RESET (Off Mode)        | I <sub>DD_RESET</sub>     | Current into V <sub>DD</sub> pin. RESET active.                                                                     | 15      |     | nA    |

| Current Consumption Deep Sleep Mode            | I <sub>DD_DS</sub>        | On/Off threshold detectors, UVDD regulator and watchdog timer running.                                              | 100     |     | nA    |

| Current Consumption Flywheel Sleep Mode        | I <sub>DD_FS</sub>        | On/Off threshold detectors,<br>UVDD regulator, watchdog timer,<br>wristwatch crystal and flywheel<br>timer running. | 700     |     | nA    |

| Current Consumption<br>Short-Term Sleep Mode   | I <sub>DD_</sub> ss       | On/Off threshold detectors, UVDD regulator, watchdog timer, short-term RCO and timer running.                       | 3.4     |     | μА    |

| Current Consumption CPUSTOP Mode               | I <sub>DD_CPUSTOP</sub>   |                                                                                                                     | 1       |     | mA    |

| Current Consumption CPUIDLE Mode               | I <sub>DD_CPUIDLE</sub>   |                                                                                                                     | 1.3     |     | mA    |

| Current Consumption CPU Mode – CRCO            | I <sub>DD_CRCO</sub>      | R/S/DVDD regulators, CPU RCO, and CPU 8051 at ~16MHz.                                                               | 3.3     |     | mA    |

| Current Consumption CPU Mode – XTAL            | I <sub>DD_XTAL</sub>      | R/S/DVDD regulators, XTAL 16M, and CPU 8051 at 16MHz.                                                               | 3.9     |     | mA    |

| FLASH Program/Page<br>Erase/Mass Erase Current |                           | This current is additional to normal CPU Mode operating current.                                                    | < 7     |     | mA    |

| Current Consumption TX Mode ASK                | ITX9A10_MO                | At ~868MHz and +10dBm<br>available TX power during<br>transmitting a PRBS sequence.<br>CPU 8051 stopped.            | 23      |     | mA    |

| Current Consumption TX Mode ASK                | I <sub>TX9A6</sub> _MO    | At ~868MHz and +6dBm available TX power during transmitting a PRBS sequence. CPU 8051 stopped.                      | 16      |     | mA    |

| Current Consumption RX Mode                    | I <sub>RX9_</sub> ASK/FSK | At ~868MHz:<br>ASK or FSK, at maximum<br>sensitivity. CPU 8051 stopped.                                             | 22      |     | mA    |

| Current Consumption TX Mode ASK                | I <sub>TX3A10_</sub> MO   | At ~315MHz and +10dBm<br>available TX power during<br>transmitting a PRBS sequence.<br>CPU 8051 stopped.            | 26      |     | mA    |

Maxim Integrated | 4 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Current Consumption (continued)**

| PARAMETER                       | SYMBOL                    | CONDITIONS                                                                                     | MIN | TYP | MAX | UNITS |

|---------------------------------|---------------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Current Consumption TX Mode ASK | I <sub>TX3A6</sub> _MO    | At ~315MHz and +6dBm available TX power during transmitting a PRBS sequence. CPU 8051 stopped. |     | 20  |     | mA    |

| Current Consumption RX Mode     | I <sub>RX3_</sub> ASK/FSK | At ~315MHz:<br>ASK or FSK, at maximum<br>sensitivity. CPU 8051 stopped.                        |     | 22  |     | mA    |

### **Ambient Power Management and Voltage Regulators**

| PARAMETER                                                  | SYMBOL                 | CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNITS           |

|------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------|------|------|------|-----------------|

| ADC BANDGAP                                                |                        |                                                                                     |      |      |      |                 |

| Sigma-Delta ADC/Mixed-<br>Signal I/O Bandgap<br>Reference  | V <sub>BGADC</sub>     |                                                                                     | 1.10 | 1.21 | 1.30 | V               |

| Bandgap Voltage Tolerance<br>Magnitude                     | d <sub>VBG</sub>       | Overtemperature and process variations                                              |      | < 4  |      | %               |

| Bandgap Voltage<br>Tolerance Magnitude Over<br>Temperature | d <sub>VBGT</sub>      | Overtemperature per device, related to room temperature                             |      | < ±2 |      | %               |

| VOLTAGE LIMITER (SHUNT                                     | REGULATOR)             |                                                                                     |      |      |      |                 |

| Limitation Voltage of Shunt Regulator                      | V <sub>LIM_50m</sub> A | At 50mA current sink                                                                | 3.9  | 4.8  | 5.5  | V <sub>DC</sub> |

| Current Consumption Voltage Limiter Only                   | I <sub>LIM_3V5</sub>   | Current into $V_{DDLIM}$ pin. $V_{DD} = 3.5 \text{ V}.$                             |      | 15   |      | nA              |

| Maximum Permanent Elimination Current of Limiter           | ILIM                   |                                                                                     |      | 50   |      | mA              |

| ON/OFF THRESHOLD DETE                                      | ECTION                 |                                                                                     |      |      |      | •               |

| Turn-On Threshold Voltage                                  | V <sub>ON</sub>        |                                                                                     | 2.3  | 2.45 | 2.6  | V <sub>DC</sub> |

| Shutdown Threshold<br>Voltage                              | V <sub>OFF</sub>       | Automatic shutdown when not in sleep mode if V <sub>DD</sub> drops below this level | 1.82 | 1.92 | 2.10 | V <sub>DC</sub> |

Maxim Integrated | 5 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Frequency Generation**

| PARAMETER                                                | SYMBOL              | CONDITIONS                                                                                                                                                  | MIN | TYP                                         | MAX  | UNITS |

|----------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------|------|-------|

| XTAL OSCILLATOR                                          |                     |                                                                                                                                                             |     |                                             |      |       |

| XTAL Oscillator frequency                                | f <sub>XO</sub>     |                                                                                                                                                             |     | 16.000                                      |      | MHz   |

| TX – RX Frequency<br>Difference at Wideband<br>Operation | d <sub>fTR_WB</sub> | Within all frequency bands assuming equal XO tolerances in TX and RX                                                                                        |     | 35                                          |      | kHz   |

| Crystal Oscillator Startup<br>Time                       | txoon               | Crystal ESR maximum 300Ω                                                                                                                                    |     | 0.7                                         | 1.2  | ms    |

| WRISTWATCH XTAL OSCIL                                    | LATOR               |                                                                                                                                                             |     |                                             |      |       |

| Wristwatch XTAL Oscillator Frequency                     | fwxo                | 2 (Note 15)                                                                                                                                                 |     | 32.768                                      |      | kHz   |

| Wristwatch Crystal<br>Oscillator Tolerance               | df <sub>WXO</sub>   | Depends on application and used crystal tolerance. Oscillator circuit will add ~30% typ to crystal tolerance. Typical crystal tolerance assumed here: 30ppm |     | 40                                          |      | ppm   |

| Wristwatch Crystal<br>Oscillator Startup Time            | t <sub>WXOON</sub>  | Crystal ESR maximum 50kΩ                                                                                                                                    |     | 1                                           |      | s     |

| RF SYNTHESIZER                                           |                     |                                                                                                                                                             |     |                                             |      |       |

| RF Synthesizer Type                                      |                     |                                                                                                                                                             | con | ional N with<br>figurable ra<br>(B3, B4, B9 | nges | _     |

| RF Synthesizer Reference Frequency                       | f <sub>REF_RF</sub> |                                                                                                                                                             | _   | f <sub>XO</sub>                             | _    | MHz   |

| Low-Frequency Band<br>Coverage                           | f <sub>RF_B3</sub>  |                                                                                                                                                             | 312 |                                             | 320  | MHz   |

| Mid-Frequency Band<br>Coverage                           | f <sub>RF_B4</sub>  |                                                                                                                                                             | 431 |                                             | 465  | MHz   |

| High-Frequency Band<br>Coverage                          | fRF_B9              |                                                                                                                                                             | 862 |                                             | 930  | MHz   |

| Low-Frequency Step Size                                  | d <sub>fLO</sub>    | B3/B4 band:<br>B9 band:                                                                                                                                     |     | ~244<br>~488                                |      | Hz    |

| RF Synthesizer Switching Speed                           | tsynth_sw3/4/9      | Settling to a frequency error of ±10kHz from steady-state value                                                                                             |     | <50                                         |      | μs    |

| RF Synthesizer Turn-On<br>Time                           | tsynth_on3/4/9      | At turning on at available reference frequency settling to a frequency error of ±10kHz from steady-state value                                              |     |                                             | 75   | μѕ    |

Maxim Integrated | 6 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A = 85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Frequency Generation (continued)**

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                                                           | MIN  | TYP             | MAX  | UNITS  |

|--------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------|------|-----------------|------|--------|

| DIGITAL CLOCK SYNTHESI                           | ZER                 |                                                                                                      |      |                 |      |        |

| Digital Clock Synthesizer Type                   |                     |                                                                                                      |      | Integer N       |      | _      |

| Digital Clock Synthesizer<br>Reference Frequency | fREFDC              |                                                                                                      | _    | f <sub>XO</sub> | -    | MHz    |

| Primary Digital Clock<br>Frequency               | f <sub>S0</sub>     | Synthesized by digital clock synthesizer                                                             |      | 32.000          |      | MHz    |

| Digital Clock Synthesizer<br>Turn-On Speed       | tf <sub>S0_ON</sub> | At turning on at available reference frequency to a frequency error of ±1kHz from steady-state value | < 75 |                 |      | μs     |

| CPU RCO (CRCO)                                   |                     |                                                                                                      |      |                 |      |        |

| Nominal CRCO Frequency                           |                     | Free-running frequency                                                                               | 11.7 | 16              | 20.0 | MHz    |

| CRCO Startup Time                                |                     | From start of RCO to usable clock                                                                    |      | 4               |      | Cycles |

Maxim Integrated | 7 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Transmit Operation**

| PARAMETER                                                                                      | SYMBOL                        | CONDITIONS                                                               | MIN   | TYP                 | MAX | UNITS  |

|------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------|-------|---------------------|-----|--------|

| ASK TRANSMISSION                                                                               |                               |                                                                          |       |                     |     |        |

| Nominal ASK Transmit Data<br>Rate                                                              | RTXA<br>(Note 4)              |                                                                          | 31.25 |                     | 125 | kBit/s |

| ASK TX Data Rate<br>Tolerance                                                                  | d <sub>RTXA</sub>             |                                                                          |       | < d <sub>fXO</sub>  |     | ppm    |

| ASK Transmit Filter Order                                                                      |                               |                                                                          | _     | 4                   | _   | _      |

| ASK Transmit Filter Type                                                                       |                               |                                                                          |       | Bessel              |     | _      |

| ASK Transmit Filter<br>Bandwidth                                                               | ВТХА                          | -3dB bandwidth                                                           |       | 1.5/2<br>RTXA       |     | kHz    |

| Transmit DAC Resolution                                                                        |                               |                                                                          |       | 6                   |     | Bit    |

| Over Sampling of ASK TX<br>Waveform                                                            |                               |                                                                          |       | 16                  |     | _      |

| ASK Anti-Aliasing Filter<br>Bandwidth                                                          | BAAA                          | -3dB bandwidth                                                           |       | 1.5<br>RTXA         |     | kHz    |

| FSK TRANSMISSION                                                                               |                               |                                                                          |       |                     |     |        |

| ASK Carrier Leakage                                                                            |                               | Transmitting a long "L" sequence at POUT = 10dBm. Related to power high. |       | < -40               |     | dB     |

| Nominal FSK Transmit Data<br>Rate                                                              | RTXF<br>(Note 4)              | Digital NCO based (derived from 16MHz XTAL)                              | 31.25 |                     | 125 | kBit/s |

| FSK TX Data Rate Tolerance                                                                     | $d_{RTXF}$                    |                                                                          |       | <d<sub>fXO</d<sub>  |     | ppm    |

| FSK Transmit Filter Order                                                                      |                               |                                                                          | -     | 2                   | -   | _      |

| FSK Transmit Filter Type                                                                       |                               |                                                                          |       | Bessel              |     | _      |

| FSK Transmit Filter<br>Bandwidth                                                               | BTXF                          | -3dB bandwidth                                                           |       | 1.5/2<br>RTXF       |     | kHz    |

| Magnitude of FSK<br>Frequency Deviation                                                        | d <sub>fTXF</sub><br>(Note 4) | Digital NCO based (derived from 16MHz XTAL)                              | 4     | RTXF/4<br>(for MSK) | 60  | kHz    |

| ASK AND FSK TRANSMISSIO                                                                        | )N                            |                                                                          |       |                     |     |        |

| TX power steps                                                                                 | NPTX                          |                                                                          |       | 7                   |     | _      |

| Maximum Available TX Output Power, Into Resonant Circuit with R <sub>LOAD</sub> (Differential) | PTX<br>(Note 1)               | For ASK: TX power during physical 'H'                                    |       | -2 to<br>+10        |     | dBm    |

| TX Output Power Variation Over Temperature                                                     | PTX_T<br>(Note 1)             | T <sub>A</sub> = -40°C to +85°C                                          |       | < ±1.5              |     | dB     |

Maxim Integrated | 8 www.maximintegrated.com

#### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

#### **Transmit Operation (continued)**

| PARAMETER                                                                                                                          | SYMBOL                   | CONDITIONS                                                              | MIN TYP                 | MAX | UNITS             |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------|-------------------------|-----|-------------------|

| Spurious Emission Power Transmitting At ~315Mhz At P <sub>OUT+10</sub> Into Resonant Circuit With R <sub>LOAD</sub> (Differential) | POUT_SP3<br>(Notes 2, 3) | ≈2 x 315MHz:<br>≈3 x 315MHz:<br>≥≈4 x 315MHz:<br>(harmonics of US band) | < -29<br>< -29<br>< -21 |     | dBm<br>dBm<br>dBm |

| Spurious Emission Power Transmitting At ~433Mhz At P <sub>OUT+10</sub> Into Resonant Circuit With R <sub>LOAD</sub> (Differential) | POUT_SP4<br>(Notes 2, 3) | ≈2 x 433MHz:<br>≥≈3 x 433MHz:<br>(harmonics of EU band)                 | < -16<br>< -10          |     | dBm<br>dBm        |

| Spurious Emission Power Transmitting At ~868Mhz At P <sub>OUT+10</sub> Into Resonant Circuit With R <sub>LOAD</sub> (Differential) | POUT_SP8<br>(Notes 2, 3) | ≈2 x 868MHz:<br>≥≈3 x 868MHz:<br>(harmonics of EU band)                 | < -10<br>< -10          |     | dBm<br>dBm        |

| Spurious Emission Power Transmitting At ~915Mhz At P <sub>OUT+10</sub> Into Resonant Circuit With R <sub>LOAD</sub> (Differential) | POUT_SP9<br>(Notes 2, 3) | ≈2 x 915MHz:<br>≥ ≈3 x 915MHz:<br>(harmonics of US band)                | < -16<br>< -10          |     | dBm<br>dBm        |

- Note 1: Available TX power from the MAX7037 in reactive load with R<sub>LOAD</sub> while transmitting at the transmit frequency f<sub>TX</sub>. The TX power is measured by a matching network and a measurement balun single-ended on 50Ω level. The measurement result is backwards projected to the MAX7037 port by the known transfer function of the measurement balun and the matching network. Additionally, the radiated TX power is dependent on the (optional) RF-filter, antenna selectivity, and loss. Therefore, it will NOT be production tested.

- Note 2: Spurious power generated by the MAX7037 in reactive load with R<sub>LOAD</sub> while transmitting at the transmit frequency f<sub>TX</sub>. Spurious emission values are measured by a matching network and a measurement balun single-ended on 50Ω level with a RBW of 100kHz being a replacement for the matching network and the differential antenna. The measurement result is backwards projected to the MAX7037 port by the known transfer function of the measurement balun and the matching network. Additionally, the radiated spurious emissions are dependent on the (optional) RF-filter, antenna-selectivity, and loss. Therefore, it will NOT production tested. Spurious emission suppression at carrier harmonics is also a part of filter and antenna design.

- Note 3: Antenna and matching network loss and attenuation by antenna selectivity for spurious assumed to be at least 20dB. The (optional) RF filter is not taken into account.

- Note 4: Digital implementation parameter, not parametrically tested (covered by ATPG testing).

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Receive Operation**

| PARAMETER                                               | SYMBOL                        | CONDITIONS                                                 | MIN                        | TYP                     | MAX                        | UNITS             |

|---------------------------------------------------------|-------------------------------|------------------------------------------------------------|----------------------------|-------------------------|----------------------------|-------------------|

| Receiver Input Impedance (Differential)                 | RIN<br>(Note 5)               | For all frequency bands B3/B4/<br>B9. LNACONF = "001001"   |                            | 288~526<br>Typ: 400     |                            | Ω                 |

| Receiver Source Impedance (Differential)                | RSOURCE                       | (Antenna impedance)                                        |                            | 400                     |                            | Ω                 |

| Receiving Protocol                                      |                               |                                                            | SSB r                      | eception LSB selectable | or USB                     | -                 |

| Receiving Mode                                          |                               |                                                            | SSB r                      | eception LSB selectable | or USB                     | -                 |

| Received Modulation Method                              |                               |                                                            |                            | ASK or FSK              |                            | _                 |

| LNA Gain                                                | GLNA                          | Switchable in NLNA steps                                   |                            | 0/20                    |                            | dB <sub>V/V</sub> |

| LNA Gain Steps                                          | NLNA                          |                                                            |                            | 2                       |                            | _                 |

| VGA Gain                                                | G_IVGA<br>G_QVGA              | Switchable in NVGA steps                                   |                            | 0/3/6/9/12/<br>15/18/21 |                            | dB <sub>V/V</sub> |

| VGA Gain Steps                                          | NVGA                          |                                                            |                            | 8                       |                            | _                 |

| 1dB Input Compression<br>Point (In-Band)                | ICP1                          | At highest sensitivity (LNA and VGA maximum gain)          |                            | -43                     |                            | dBm               |

| Dynamic Range Of Sigma-<br>Delta ADC                    | DYNADC                        | Sinusoidal signal at 125kHz in 200kHz output bandwidth     |                            | 78                      |                            | dB                |

| Data Oversampling Factor                                | OV                            | Different logical treatment in compatible asynchronous SOF | _                          | 8                       | _                          | _                 |

| ASK/FSK RX Data Rate                                    | RRX<br>(Note 7)               | ASK or FSK tested at maximum data rate. ASK: FSK:          | min<br>RTXA<br>min<br>RTXF | RTXA<br>RTXF            | max<br>RTXA<br>max<br>RTXF | kBit/s            |

| Acceptable Advanced TX-<br>RX Data Rate Deviation       | d <sub>RTRXA</sub>            | Tolerance of nominal FSK data rate between TX and RX.      |                            | < 2 df <sub>XO</sub>    |                            | ppm               |

| IF Magnitude Word Width                                 |                               |                                                            |                            | 16                      |                            | Bits              |

| RSS Word Width                                          |                               |                                                            |                            | 16                      |                            | Bits              |

| LTRSS Word Width                                        |                               |                                                            |                            | 16                      |                            | Bits              |

| DOUBLE WIDEBAND OPERA                                   | ATION                         |                                                            | •                          |                         |                            | Į.                |

| Nominal Intermediate<br>Frequency Wideband<br>Operation | fIFD                          |                                                            |                            | 250                     |                            | kHz               |

| Effective Receiver<br>Bandwidth                         | BRXD                          | -3dB, defined by integrated digital IF filter              | -                          | 300                     | -                          | kHz               |

| Magnitude Of FSK<br>Frequency Deviation                 | df <sub>RXD</sub><br>(Note 5) |                                                            | 15                         | dfTX                    | 60                         | kHz               |

Maxim Integrated | 10 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Receive Operation (continued)**

| PARAMETER                                                        | SYMBOL                                              | CONDITIONS                                                                                                      | MIN T | ΥP          | MAX                           | UNITS |

|------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|-------------|-------------------------------|-------|

| Normal ASK Receiver<br>Sensitivity At MAX7037<br>Input           | S0RX3_D_A<br>S0RX4_D_A<br>S0RX9_D_A<br>(Notes 1, 3) | At max RTXA, high LNA gain<br>and max IF gain for SRQ<br>(Note 2) at -10°C < T <sub>A</sub> < +70°C             | -1    | 95          |                               | dBm   |

| Normal FSK Receiver<br>Sensitivity At MAX7037<br>Input           | S0RX3_D_F<br>S0RX4_D_F<br>S0RX9_D_F<br>(Notes 1, 3) | At MSK with max RTXF,<br>high LNA gain and max IF gain<br>for SRQ (Note 2) at<br>-10°C < T <sub>A</sub> < +70°C | -1    | 95          |                               | dBm   |

| Temperature Sensitivity Reduction                                | d <sub>SOD_T</sub>                                  | -40°C < T <sub>A</sub> <-10°C or<br>+70°C < T <sub>A</sub> <+85°C.                                              | •     | <3          |                               | dB    |

| Receiver Sensitivity Reduction Caused By TX- RX Frequency Offset | d <sub>SOD_F</sub>                                  | For SRQ (Note 2) at maximum df <sub>TRW</sub>                                                                   | •     | <4          |                               | dB    |

| Receiver Sensitivity Reduction Caused By Data Rate Deviation     | d <sub>S0D_R</sub>                                  | For SRQ (Note 2) at maximum d <sub>RTRXC</sub>                                                                  | •     | <3          |                               | dB    |

| Reduced FSK Receiver<br>Sensitivity                              | S1RX3/4/9_D_F<br>(Notes 1, 3)                       | At low LNA gain, for SRQ<br>(Note 2) at -10°C < T <sub>A</sub> < +70°C                                          | -     | 84          |                               | dBm   |

| Maximum ASK Target Signal Input Level                            | PMAX_D_A<br>(Note 1)                                | At max RTXA, high LNA gain and max IF gain for SRQ (Note 2) at -10°C < T <sub>A</sub> < +70°C                   | -:    | 20          |                               | dBm   |

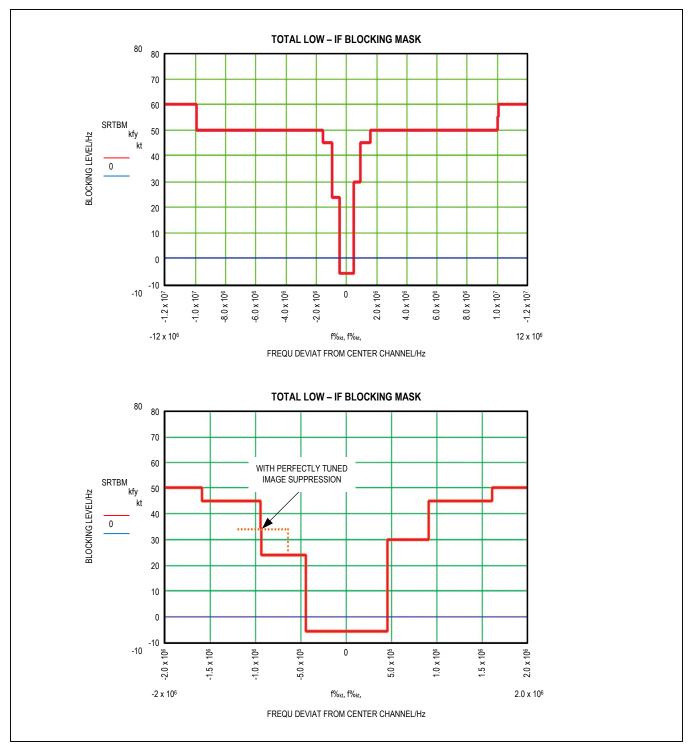

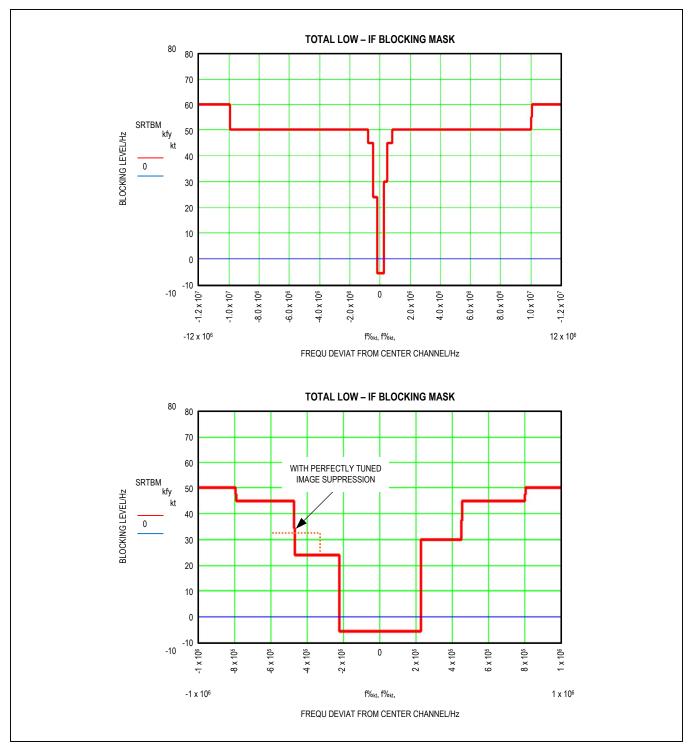

| Target Blocking Mask                                             | (Note 4)                                            | Covered by digital tests                                                                                        | Fig   | ure 3       |                               | dBc   |

| Equivalent IF Magnitude<br>Bandwidth                             | BIFMAG_D                                            |                                                                                                                 | 1     | 50          |                               | kHz   |

| RSS Bandwidth                                                    | BRSS_D                                              |                                                                                                                 | •     | 10          |                               | kHz   |

| RSS Settling Time                                                | t <sub>RSS0_D</sub><br>(Note 7)                     | Dominated by BRSS_D kHz RSS measurement bandwidth                                                               | 1     | 50          | 250                           | μs    |

| LTRSS Bandwidth                                                  | BLTRSS_D                                            |                                                                                                                 |       | 1           |                               | kHz   |

| LTRSS Settling Time                                              | t <sub>RSS1_D</sub><br>(Note 7)                     | Given by BLTRSS_D kHz measurement bandwidth                                                                     | 1     | .5          | 2.0                           | ms    |

| Gain Control Switching Time                                      | <sup>t</sup> GCD<br>(Note 7)                        | One cycle from highest gain to lower gain                                                                       |       | yp<br>S0_D) | max<br>(t <sub>RSSO_D</sub> ) | μs    |

Maxim Integrated | 11 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **Receive Operation (continued)**

| PARAMETER                                                        | SYMBOL                                              | CONDITIONS                                                                                                         | MIN | TYP      | MAX | UNITS |

|------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|----------|-----|-------|

| WIDEBAND OPERATION                                               |                                                     |                                                                                                                    |     |          |     |       |

| Nominal Intermediate<br>Frequency Wideband<br>Operation          | fIFW                                                |                                                                                                                    |     | 125      |     | kHz   |

| Effective Receiver<br>Bandwidth                                  | BRXW                                                | -3dB, defined by integrated digital IF filter                                                                      | _   | 150      | -   | kHz   |

| Magnitude Of FSK<br>Frequency Deviation                          | df <sub>RXW</sub><br>(Note 7)                       |                                                                                                                    | 15  | dfTX     | 60  | kHz   |

| Normal ASK Receiver<br>Sensitivity At MAX7037 Input              | S0RX3_W_A<br>S0RX4_W_A<br>S0RX9_W_A<br>(Notes 1, 3) | At max RTXA, high LNA gain<br>and max IF gain for SRQ (Note 2)<br>at 10°C < T <sub>A</sub> < +70 C                 |     | -100     |     | dBm   |

| Normal FSK Receiver<br>Sensitivity At MAX7037 Input              | S0RX3_W_F<br>S0RX4_W_F<br>S0RX9_W_F<br>(Notes 1, 3) | At MSK with max RTX <sub>F</sub> , high LNA gain and max IF gain for SRQ (Note 2) at 10°C < T <sub>A</sub> < +70°C |     | -100     |     | dBm   |

| Temperature Sensitivity Reduction                                | d <sub>S0W_T</sub>                                  | -40°C < T <sub>A</sub> < -10°C or<br>+70°C < T <sub>A</sub> < +85°C                                                |     | <3       |     | dB    |

| Receiver Sensitivity Reduction Caused By TX- RX Frequency Offset | d <sub>S0W_F</sub>                                  | For SRQ (Note 2) at maximum df <sub>TRW</sub>                                                                      |     | <4       |     | dB    |

| Receiver Sensitivity Reduction Caused By Data Rate Deviation     | d <sub>S0W_R</sub>                                  | For SRQ (Note 2) at maximum d <sub>RTRXC</sub>                                                                     |     | <3       |     | dB    |

| Reduced FSK Receiver<br>Sensitivity.                             | S1RX3/4/9_W_F<br>(Notes 1, 3)                       | At low LNA gain, for SRQ<br>(Note 2) at -10°C < T <sub>A</sub> < +70°C                                             |     | -88      |     | dBm   |

| Maximum ASK Target Signal Input Level                            | PMAX_W_A<br>(Notes 1, 3)                            | At max RTX <sub>A</sub> , high LNA gain,<br>and max IF gain for SRQ (Note 2)<br>at -10°C < T <sub>A</sub> < +70°C  |     | -20      |     | dBm   |

| Target Blocking Mask                                             | (Note 4)                                            | Covered by digital tests                                                                                           |     | Figure 4 |     | dBc   |

| Equivalent IF Magnitude<br>Bandwidth                             | BIFMAG_W                                            |                                                                                                                    |     | 75       |     | kHz   |

| RSS Bandwidth                                                    | BRSS_W                                              |                                                                                                                    |     | 5        |     | kHz   |

| RSS Settling Time                                                | t <sub>RSS0_W</sub><br>(Note 7)                     | Dominated by BRSS_W kHz RSS measurement bandwidth                                                                  |     | 300      | 500 | μs    |

Maxim Integrated | 12 www.maximintegrated.com

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

#### **Receive Operation (continued)**

| PARAMETER                                                | SYMBOL                           | CONDITIONS                                                                                                                                                                                                                                        | MIN | TYP                           | MAX                           | UNITS |

|----------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------|-------------------------------|-------|

| LTRSS Bandwidth                                          | BLTRSS_W<br>(Note 7)             |                                                                                                                                                                                                                                                   |     | 500                           |                               | Hz    |

| LTRSS Settling Time                                      | t <sub>RSS1_W</sub><br>(Note 7)  | Given by BLTRSS_W kHz measurement bandwidth                                                                                                                                                                                                       |     | 3                             | 4                             | ms    |

| Gain Control Switching Time                              | t <sub>GCW</sub><br>(Note 7)     | One cycle from highest gain to lower gain                                                                                                                                                                                                         |     | Typ<br>(t <sub>RSS0_W</sub> ) | Max<br>(t <sub>RSSO_W</sub> ) | μs    |

| GENERAL                                                  |                                  |                                                                                                                                                                                                                                                   |     |                               |                               |       |

| Image Rejection Untrimmed                                | XRX3_IRJ<br>XRX4_IRJ<br>XRX9_IRJ | Untrimmed, at maximum RX sensitivity setting. Image signal in-band at LSB RX +2 f <sub>IF</sub> above band center. Image signal in-band at USB RX -2 f <sub>IF</sub> below band center                                                            |     | 24                            |                               | dB    |

| Image Rejection Trimmed                                  |                                  | Trimmed, at maximum RX sensitivity setting. Image signal in-band at LSB RX +2 f <sub>IF</sub> above band center. Image signal in-band at USB RX -2 f <sub>IF</sub> below band center See receive section for image rejection tuning and Figure 4. |     | 34                            |                               | dB    |

| Available RX Low Power<br>Leakage at f <sub>LORX,X</sub> | PLOLeak<br>(Note 6)              | Low power in a differentially matching source resistor as load with LNA in high or low gain mode                                                                                                                                                  |     | < -50                         |                               | dBm   |

- Note 5: The RX sensitivity is measured close to the application by a single-ended on  $50\Omega$  source through a balun and a matching network to the input impedance. The measurement result is forward projected to the MAX7037 port by the known transfer function of the balun and the matching network.

- Note 6: Standard Receive Quality (SRQ) is a bit error probability (without error correcting coding) of 10<sup>-3</sup>.

- Note 7: The radiated sensitivity of the whole RX is dependent of the (optional) RF filter- and antenna- selectivity and loss is therefore NOT production tested.

- Note 8: SRQ fulfilled with: Useful signal applied 3dB above the measured sensitivity limit, however not below maximum of S0<sub>X</sub> + 3dB. Blocking signal un-modulated CW. This measurement method is slightly more restrictive than the EN300 220-1V 1.3.1 (2000) section 9.3.2 for class 2 receivers due to they are related to the nominal received carrier position instead of the band edges. Blocking is not production tested.

- Note 9: Values from simulation. Actual obtained RIN is also dependent on the LNACONF configuration setting.

- Note 10: Carrier generated by the MAX7037 in reactive load with R<sub>LOAD</sub> while receiving at the frequency fTRX. The leakage power is measured by a matching network and a measurement balun single-ended on 50Ω level being a replacement for the matching network and the differential antenna. The measurement result is backwards projected to the MAX7037 port by the known transfer function of the measurement balun and the matching network. The radiated leakage is furthermore dependent on the (optional) RF-filter- and antenna- loss and, therefore, NOT production tested. Spurious emission suppression at carrier harmonics is also a part of filter and antenna design.

Note 11: Digital implementation parameter, not parametrically tested (covered by ATPG testing).

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### **TX and RX Timing Parameters**

| PARAMETER                                       | SYMBOL                           | CONDITIONS                                                                                                     | MIN TYP MAX                               | X UNITS |

|-------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------|

| STARTING AND RE-START                           | TING TX AND RX                   |                                                                                                                |                                           |         |

| TX Starting Time                                | t <sub>0CT</sub> (Notes 1, 2)    | Time for starting transmitting a packet from turned off synthesizer. Dominated by synthesizer startup.         | <t<sub>SYNTH<br/>_ON</t<sub>              | μs      |

| TX Restarting Time                              | t <sub>CT</sub><br>(Notes 1, 2)  | Time for starting transmitting a packet at running synthesizer.  Dominated by synthesizer switching.           | <tsynth<br>_sw</tsynth<br>                | μs      |

| TX Continuing Time                              | t <sub>T</sub><br>(Notes 1, 2)   | Time for starting transmitting a packet at synthesizer running on correct channel.                             | <tsynth<br>_sw</tsynth<br>                | μs      |

| RX Starting Time                                | t <sub>0CR</sub><br>(Notes 1, 2) | Time for starting receiving from turned off synthesizer. Dominated by synthesizer startup. LTRSS is forced     | < <sup>t</sup> SYNTH<br>_ON<br>+tRSS1x    | μs      |

| RX Restarting Time                              | t <sub>CR</sub><br>(Notes 1, 2)  | Time for starting receiving running synthesizer. Dominated by synthesizer switching. LTRSS is forced           | <tsynth<br>_sw<br/>+trss1x</tsynth<br>    | μs      |

| RX Continuing Time                              | t <sub>R</sub><br>(Notes 1, 2)   | Time for starting receiving at synthesizer running on correct channel                                          | <sup>t</sup> RSS0x~<br><sup>t</sup> RSS1x | μs      |

| SINGLE CHANNEL (BAND                            | ) OPERATION                      |                                                                                                                |                                           |         |

| TX->TX Switching Time<br>Same RF Channel (Band) | t <sub>TT</sub><br>(Notes 1, 2)  | Time between transmitting two packets. Estimation, given by CPU 8051.                                          | 10                                        | μs      |

| TX->RX Switching Time<br>Same RF Channel (Band) | t <sub>TR0</sub><br>(Notes 1, 2) | At constant LTRSS, until packet start possible (for receiving at SRQ)                                          | <t<sub>RSS0x</t<sub>                      | μs      |

| TX->RX Switching Time<br>Same RF Channel (Band) | t <sub>TR1</sub> (Notes 1, 2)    | At totally different RSS where the LTRSS has to be adapted until packet start possible (for receiving at SRQ). | <trss1x< td=""><td>μs</td></trss1x<>      | μs      |

| RX->TX Switching Time<br>Same RF Channel (Band) | t <sub>RT</sub> (Notes 1, 2)     | Time between end receiving and start transmitting a packet. Estimation, given by CPU 8051.                     | 10                                        | μs      |

| RX->RX Switching Time<br>Same RF Channel (Band) | t <sub>RR0</sub> (Notes 1, 2)    | At constant LTRSS, until packet start possible (for receiving at SRQ).                                         | <t<sub>RSS0x</t<sub>                      | μs      |

| RX->RX Switching Time<br>Same RF Channel (Band) | t <sub>RR1</sub> (Notes 1, 2)    | At totally different RSS where the LTRSS has to be adapted until packet start possible (for receiving at SRQ). | <t<sub>RSS1x</t<sub>                      | μs      |

Maxim Integrated | 14 www.maximintegrated.com

Electrical Characteristics (continued) (Limits are 100% tested at  $T_A$  = 85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

### TX and RX Timing Parameters (continued)

| PARAMETER                                        | SYMBOL                            | CONDITIONS                                                                                                     | MIN TYP                                             | MAX | UNITS |  |  |

|--------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-------|--|--|

| MULTI CHANNEL (BAND)                             | MULTI CHANNEL (BAND) OPERATION    |                                                                                                                |                                                     |     |       |  |  |

| TX->TX Channel (Band)<br>Switching Time          | t <sub>TCT</sub><br>(Notes 1, 2)  | Time between transmitting two packets. Dominated by synthesizer switching.                                     | <t<sub>SYNTH<br/>_SW</t<sub>                        |     | þs    |  |  |

| TX->RX Switching Time<br>Other RF Channel (Band) | t <sub>TCR0</sub><br>(Notes 1, 2) | At constant LTRSS, until packet start possible (for receiving at SRQ).                                         | <tsynth<br>_sw<br/>+t<sub>RSS0x</sub></tsynth<br>   |     | hг    |  |  |

| TX->RX Switching Time<br>Other RF Channel (Band) | t <sub>TCR1</sub><br>(Notes 1, 2) | At totally different RSS where the LTRSS has to be adapted until packet start possible (for receiving at SRQ). | <tsynth<br>_sw<br/>+trss1x</tsynth<br>              |     | μs    |  |  |

| RX->TX Switching Time<br>Other RF Channel (Band) | t <sub>RCT</sub><br>(Notes 1, 2)  | Time between end receiving and start transmitting a packet. Dominated by synthesizer switching.                | <t<sub>SYNTH<br/>_SW</t<sub>                        |     | μs    |  |  |

| RX->RX Switching Time<br>Other RF Channel (Band) | t <sub>RCR0</sub><br>(Notes 1, 2) | At constant LTRSS, until packet start possible (for receiving at SRQ).                                         | <tsynth<br>_sw<br/>+t<sub>RSS0x</sub></tsynth<br>   |     | þs    |  |  |

| RX->RX Switching Time<br>Other RF Channel (Band) | <sup>†</sup> RCR1<br>(Notes 1, 2) | At totally different RSS where the LTRSS has to be adapted until packet start possible (for receiving at SRQ). | <t<sub>SYNTH<br/>_SW<br/>+t<sub>RSS1x</sub></t<sub> |     | μs    |  |  |

Note 1: SRQ fulfilled with: Useful signal applied 3dB above the measured sensitivity limit, however not below maximum of  $S0_X + 3dB$ .

Note 2: Timings are a composite of tested subtimings therefore laboratory evaluation only, not directly production tested.

Maxim Integrated | 15 www.maximintegrated.com

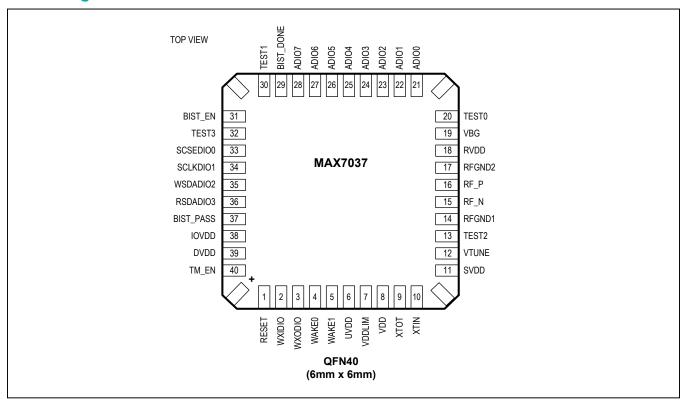

## **Pin Configuration**

## **Pin Description**

| PIN | PIN NAME | DIRECTION | PAD<br>TYPE | DESCRIPTION                                                           | SUPPLY/<br>IO VOLTAGE<br>DOMAIN |

|-----|----------|-----------|-------------|-----------------------------------------------------------------------|---------------------------------|

| 1   | RESET    | DI        | PD          | External Reset Input. High active.                                    | 1.8                             |

| 2   | WXIDIO   | ADIO      | SPUPD       | GPIO2 Group: Analog/Slow Digital I/O – 32kHz Oscillator<br>XTAL Input | 1.8                             |

| 3   | WXODIO   | ADIO      | SPUPD       | GPIO2 Group: Analog/Slow Digital I/O – 32kHz Oscillator XTAL Output.  | 1.8                             |

| 4   | WAKE0    | DI        | S           | Wake 0 Input.                                                         | 1.8                             |

| 5   | WAKE1    | DI        | S           | Wake 1 Input.                                                         | 1.8                             |

| 6   | UVDD     | AP        |             | UVDD Regulator Output.                                                | 1.8                             |

| 7   | VDDLIM   | A_HV      |             | V <sub>DD</sub> Limiter.                                              | 5                               |

| 8   | $V_{DD}$ | A_HV      |             | Main V <sub>DD</sub> – Input for DVDD/SVDD/RVDD/UVDD regulators       | 5                               |

| 9   | хтот     | AO        |             | 16MHz XTAL Output                                                     | 1.8                             |

| 10  | XTIN     | Al        |             | 16MHz XTAL Input                                                      | 1.8                             |

## **Pin Description (continued)**

| PIN | PIN NAME  | DIRECTION | PAD<br>TYPE | DESCRIPTION                                                                                | SUPPLY/<br>IO VOLTAGE<br>DOMAIN |

|-----|-----------|-----------|-------------|--------------------------------------------------------------------------------------------|---------------------------------|

| 11  | SVDD      | AP        |             | SVDD Regulator Output.                                                                     | 1.8                             |

| 12  | VTUNE     | AIO       |             | RF PLL Vtune Debug I/O.                                                                    | 1.8                             |

| 13  | TEST2     | DI        | PD          | Test2                                                                                      | 1.8                             |

| 14  | RFGND1    | AG        |             | RF GND                                                                                     | 1.8                             |

| 15  | RF_N      | AIO       |             | RF I/O (n)                                                                                 | 1.8                             |

| 16  | RF_P      | AIO       |             | RF I/O (p)                                                                                 | 1.8                             |

| 17  | RFGND2    | AG        |             | RF GND                                                                                     | 1.8                             |

| 18  | RVDD      | AP        |             | RVDD Regulator Output.                                                                     | 1.8                             |

| 19  | VBG       | AIO       |             | SD-ADC Bandgap Reference Buffered Output. Decoupling capacitor needed.                     | 1.8                             |

| 20  | TEST0     | DI        | PD          | Test0                                                                                      | 3.3                             |

| 21  | ADIO0     | ADIO      | SPUPD       | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 22  | ADIO1     | ADIO      | SPUPD       | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 23  | ADIO2     | ADIO      | SPUPD       | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 24  | ADIO3     | ADIO      | SPUPD       | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 25  | ADIO4     | ADIO      | PUPD        | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 26  | ADIO5     | ADIO      | PUPD        | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 27  | ADIO6     | ADIO      | PUPD        | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 28  | ADIO7     | ADIO      | PUPD        | GPIO1 Group: Analog/Digital I/O.                                                           | 3.3                             |

| 29  | BIST_DONE | ADIO      | PD          | GPIO0 Group: DIO5. BIST done output (BIST_EN = 1). Analog functionality only in test mode. | 3.3                             |

| 30  | TEST1     | DIO       | PD          | GPIO0 Group: DIO6. Test1 in test mode.                                                     | 3.3                             |

| 31  | BIST_EN   | DI        | PD          | BIST Enable.                                                                               | 3.3                             |

| 32  | TEST3     | DIO       | PD          | GPIO0 Group: DIO7. Test3 in test mode.                                                     | 3.3                             |

| 33  | SCSEDIO0  | DIO       | PUPD        | GPIO0 Group: DIO0 – SPI Chip Select.                                                       | 3.3                             |

| 34  | SCLKDIO1  | DIO       | PUPD        | GPIO0 Group: DIO1 - SPI Clock.                                                             | 3.3                             |

| 35  | WSDADIO2  | DIO       | PUPD        | GPIO0 Group: DIO2 - SPI Data In.                                                           | 3.3                             |

| 36  | RSDADIO3  | DIO       | PUPD        | GPIO0 Group: DIO3 - SPI Data Out.                                                          | 3.3                             |

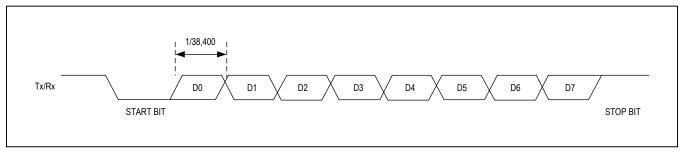

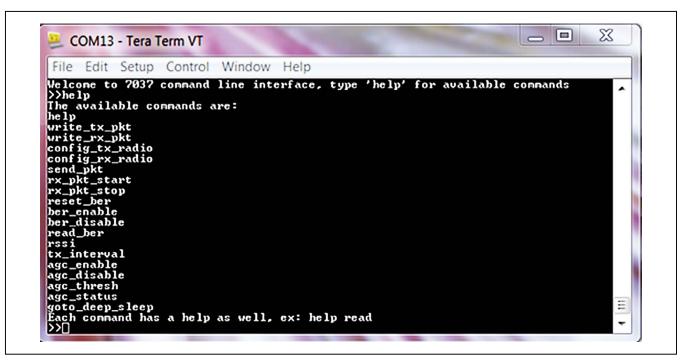

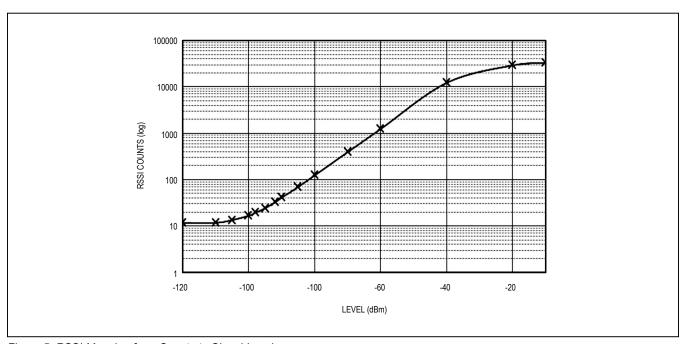

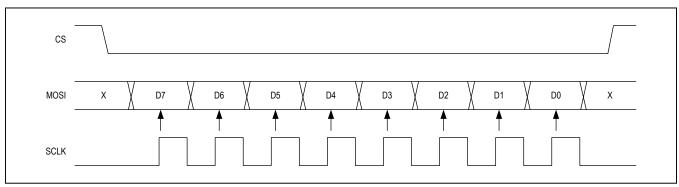

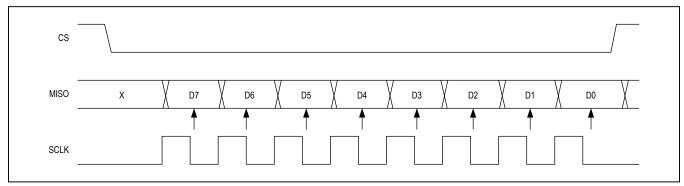

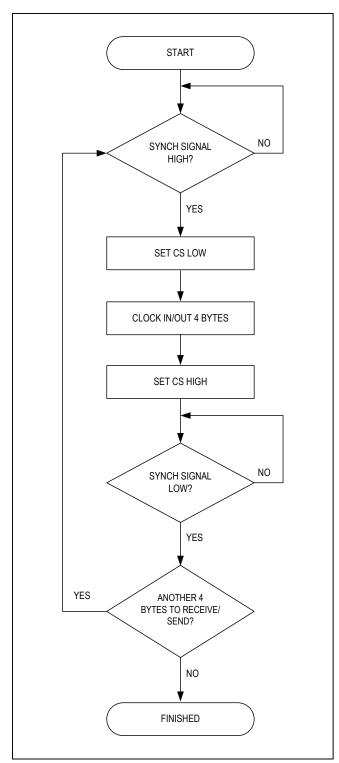

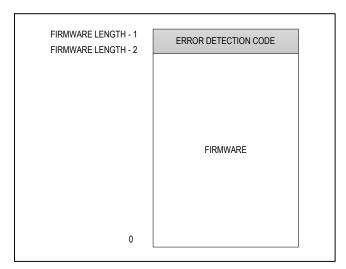

| 37  | BIST_PASS | DIO       | PD          | GPIO0 Group: DIO4. BIST pass/fail output (BIST_EN=1).                                      | 3.3                             |