# AsahiKASEI AK2404 MICRODEVICES 45 to 960MHz Direct Conversion Transceiver for high performance narrowband system

#### 1. General Description

The AK2404 is a direct conversion transceiver IC that realizes high-performance narrowband wireless communication. The receiver section incorporates an LNA, quadrature demodulator, PGA, 24-bit  $\Delta\Sigma$  A/D Converter, and digital filter to provide a receiver with high sensitivity and high interference immunity without the use of ceramic or SAW filter. In particular, the blocking characteristics of  $\Delta$ 10MHz are over 100dB (Standard: TIA603, EN 300 0861-1). The digital filter with variable bandwidth supports channel selection for multiple different wireless systems, enabling easy system design in wireless platforms. In addition, a  $\Delta\Sigma$  fractional N PLL synthesizer is incorporated to configure high-performance PLLs with an external VCO. The transmitter has a built-in DAC and driver amplifier. The compact QFN Package of 8mm square contributes to the miniaturization of radio equipment.

#### 2. Features and Applications

#### Features

- □ Operating Frequency: 45MHz to 960MH

- Dever Supply: 2.7 to 3.45V (IOVDD: 1.7 to 1.9V also used 2.7 to 3.45V)

- □ Operational Temperature: -40 to +85°C

- LNA, Attenuator (ATT) and PDET for interference detection

- □ Automatic PGA gain control function for high dynamic range

- □ High Linearity Direct Conversion I/Q Demodulator

- $\Box$  24-bit  $\Delta\Sigma$  A/D Converter: up to 192kHz Output Sampling Rate (TCXO=24.576MHz)

- Band Changeable Digital Filter (The FIR filter coefficients can be set arbitrarily)

- RSSI Functions: Data read by SPI and Analog voltage output

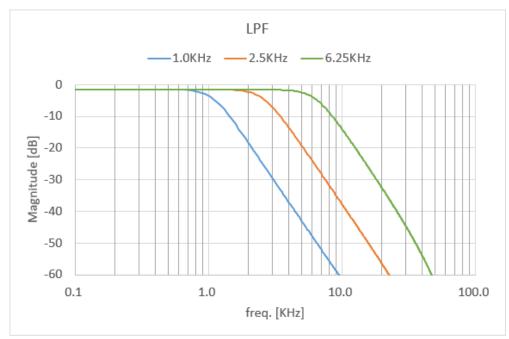

- □ FM Detection Circuit and Noise Squelch Function

- □ Support Zero IF and Very Low IF architecture

- DC Offset Cancelation: Real-time DC Offset Canceller (RDOC) Function and HPF

- $\Box$  23-bit  $\Delta\Sigma$  Fractional-N PLL Synthesizer

- □ Modulation data input interface suitable for 2-point modulation for FM/FSK applications

- □ 12-bit D/A Converter: 96kHz Max. Sampling Rate, S/N 72dB

- □ Transmission Drive Amplifier: -10 to +2dBm Output

- □ Local Signal Dividing Circuit and Poly Phase Filter

- TCXO Frequency: 18.432MHz / 19.2MHz / 24.576MHz recommended

- □ Clock Rate Converter

- □ Package: 68-pin QFN (8×8mm, 0.4 mm pitch)

#### Applications

- Narrow Band Radio Communications: 6.25kHz / 7.5kHz / 12.5kHz / 15kHz / 20kHz / 25kHz etc.

- Modulation Method: FM / 2FSK/ 4FSK / QPSK / π/4 DQPSK / 16QAM (The demodulation needs to be externally executed except the FM modulation.)

- Analog/Digital Dual Mode Transceiver

- Digital Radio System for Industrial Use

- D Public Safety and Community/Emergence Radio System

- □ Convenience Transceiver

- □ Marine/Mobile Communication System

- □ Low power / Telemeter Transmitter

- □ Amateur Radio System

# 3. Table of Contents

| 1. General Description                                                                                                                                         |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2. Features and Applications                                                                                                                                   |              |

| 3. Table of Contents                                                                                                                                           |              |

| 4. Representation                                                                                                                                              |              |

| 5. Block Diagram and Functions                                                                                                                                 |              |

| 5.1. Block Diagram                                                                                                                                             |              |

| 5.2. Block Functions                                                                                                                                           |              |

| 6. Pin Configurations and Functions                                                                                                                            |              |

| 6.1. Pin Configurations                                                                                                                                        |              |

| 6.2. Pin Functions                                                                                                                                             |              |

| 6.3. Handling of Unused Pins                                                                                                                                   |              |

| 7. Absolute Maximum Ratings.                                                                                                                                   |              |

| 8. Recommended Operating Conditions                                                                                                                            |              |

| 9. Digital Characteristics                                                                                                                                     |              |

| 9.1. DC Characteristics                                                                                                                                        |              |

| 9.2. System Reset<br>9.3. Serial Interface Timing for Register Access                                                                                          |              |

| <ul> <li>9.3. Serial Interface Timing for Register Access</li> <li>9.4. Serial Interface Timing for Programmable Digital Filter Coefficient Setting</li> </ul> | . 10         |

| 9.4. Serial Interface Timing for Receiving Data and Status Output Read                                                                                         |              |

|                                                                                                                                                                |              |

|                                                                                                                                                                |              |

| <ol> <li>Analog Characteristics</li> <li>10.1. Receiving Characteristics</li> </ol>                                                                            |              |

| 10.1.1. LNA                                                                                                                                                    |              |

| 10.1.1. LNA                                                                                                                                                    |              |

| 10.1.2. ATT                                                                                                                                                    |              |

| 10.1.3. PDE1                                                                                                                                                   |              |

|                                                                                                                                                                |              |

| 10.1.5. LOCAL DIVIDER(RX)<br>10.1.6. PLL SYNTHESIZER                                                                                                           |              |

|                                                                                                                                                                |              |

| 10.1.7. RSSI<br>10.1.8. CLOCK BUFFER+CLOCK RATE CONVERTER                                                                                                      |              |

|                                                                                                                                                                |              |

| 10.1.9. DETDAC+SMF<br>10.2. Transmission Characteristics                                                                                                       |              |

|                                                                                                                                                                |              |

| 10.2.1. MODDAC+SMF<br>10.2.2. LOCAL DIVIDER(TX)+DRIVER AMP                                                                                                     | 30           |

|                                                                                                                                                                |              |

| <ul> <li>10.3. Current Consumption</li> <li>11. Standard Characteristics Example</li> </ul>                                                                    |              |

|                                                                                                                                                                |              |

|                                                                                                                                                                |              |

| 12.1. Power-up Sequence                                                                                                                                        |              |

| 12.1.1. Using internal LDC                                                                                                                                     |              |

| 12.1.2. Supplying voltage to VREFT pintexternally                                                                                                              |              |

| 12.3. Power-up Sequence of the Receiver                                                                                                                        |              |

| 13. Functional Description                                                                                                                                     |              |

| 13.1. Power Control                                                                                                                                            |              |

| 13.1.1. Power Control Logic of the LNA and ATT                                                                                                                 |              |

| 13.2. Operation Mode Setting                                                                                                                                   |              |

| 13.3. Level Diagram                                                                                                                                            |              |

| 13.3.1. Level Diagram of Analog Receiving Circuit                                                                                                              |              |

| 13.3.2. Level Diagram of Digital Receiving Circuit                                                                                                             |              |

| 13.4. Analog Receiving Circuits (LNA, ATT, PDET, MIXER, PGA, AAF)                                                                                              |              |

| 13.4.1. LNA, ATT                                                                                                                                               |              |

| 13.4.1. ENA, ATT                                                                                                                                               |              |

| 13.4.2. PDET                                                                                                                                                   |              |

| 13.4.3. MIXER                                                                                                                                                  |              |

| 13.4.4. FGA, AAF                                                                                                                                               |              |

| 220900015-E-04 2023                                                                                                                                            |              |

|                                                                                                                                                                | <i>v</i> /04 |

| 13.5.  | LOCAL DIVIDER                                                                                                   | 54  |

|--------|-----------------------------------------------------------------------------------------------------------------|-----|

| 13.5.1 | 1. LOCAL DIVIDER                                                                                                | 54  |

| 13.5.2 | 2. Phase Calibration                                                                                            | 54  |

| 13.6.  | CLOCK BUFFER+CLOCK RATE CONVERTER                                                                               | 57  |

| 13.7.  | PLL SYNTHESIZER                                                                                                 | 58  |

| 13.7.1 |                                                                                                                 |     |

| 13.7.2 |                                                                                                                 |     |

| 13.7.3 |                                                                                                                 |     |

| 13.7.4 |                                                                                                                 |     |

| 13.7.5 |                                                                                                                 |     |

| 13.8.  | Digital Receiving Circuits (ADC, DIGITAL FILTER, RSSI, AGC, ADC P/S IF)                                         |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.2 |                                                                                                                 |     |

| 13.8.3 | I Contraction of the second |     |

| 13.8.4 |                                                                                                                 |     |

| 13.8.5 |                                                                                                                 |     |

| 13.8.6 |                                                                                                                 |     |

| 13.8.7 | -                                                                                                               |     |

| 13.8.8 |                                                                                                                 |     |

| 13.8.9 |                                                                                                                 |     |

| 13.8.1 |                                                                                                                 | -   |

| 13.8.1 |                                                                                                                 |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.1 | ,                                                                                                               |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.1 | •                                                                                                               |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.1 |                                                                                                                 |     |

| 13.8.2 |                                                                                                                 |     |

| 13.9.  | Transmit Data Generation Circuit (MODDAC, SMF)                                                                  |     |

| 13.10. | Transmit Preamplifier Circuit (DRIVER AMP)                                                                      |     |

| 13.11. | Internal Low Voltage Generator Circuit (LDO)                                                                    |     |

|        | gister Map and Detailed Description                                                                             |     |

| 14.1.  | Register Map                                                                                                    |     |

| 14.2.  | Special Register Access                                                                                         |     |

| 14.3.  | CLOCK/PLL                                                                                                       |     |

| 14.3.  |                                                                                                                 |     |

| 14.3.2 |                                                                                                                 | 117 |

| 14.3.3 | 2. <0x02 to 00-01 0_1000/01 0_1 1102/01 0_DE10                                                                  | 117 |

| 14.3.4 |                                                                                                                 | 118 |

| 14.3.5 |                                                                                                                 |     |

| 14.3.6 |                                                                                                                 |     |

| 14.3.7 |                                                                                                                 |     |

| 14.3.8 |                                                                                                                 |     |

| 14.3.9 |                                                                                                                 |     |

| 14.4.  |                                                                                                                 |     |

| 14.4.  |                                                                                                                 |     |

| 14.4.2 | -                                                                                                               |     |

| 14.4.2 |                                                                                                                 |     |

| 14.4.4 |                                                                                                                 |     |

| 14.4.4 |                                                                                                                 |     |

| 14.5.  |                                                                                                                 |     |

| 14.5.  |                                                                                                                 |     |

| -      | AGC                                                                                                             |     |

| 14.0.  |                                                                                                                 |     |

| 14.0.  |                                                                                                                 | 120 |

| 14.6.2.    | <0x34 to 3F>AGC DIG                       | 120 |

|------------|-------------------------------------------|-----|

|            | <0x34 to 3F2AGC_DIG                       |     |

| 14.7. DIG  | <pre></pre> <pre></pre> <pre></pre>       |     |

| 14.7.1.    |                                           |     |

|            | <0x42>DFIL_SET                            |     |

| 14.7.3.    | <0x43 to 45>NCO MIXER                     |     |

| 14.7.4.    | <0x46>PRE_HPF                             | 136 |

| 14.7.5.    | <0x47 to 48-MIXER_ATT                     |     |

| 14.7.6.    | <0x4A>CH FILTER                           |     |

| 14.7.7.    | <0x4C to 4E>RSSI                          |     |

| 14.7.8.    | <0x50 to 52> Out of Band Power Monitoring | 139 |

| 14.7.9.    | <0x54 to 58>FMDET                         |     |

| 14.7.10.   | <0x59 to 5C>NSQ                           |     |

| 14.7.11.   | <0x5D>FMDET2                              |     |

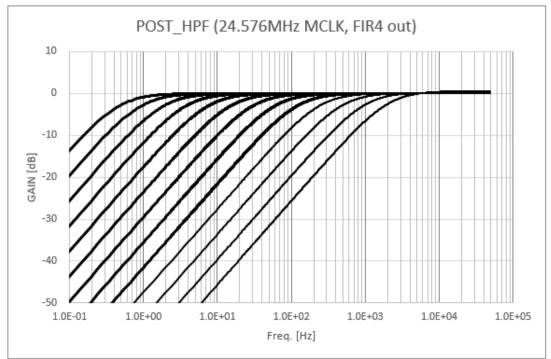

| 14.7.12.   | <0x5F>POST_HPF                            |     |

| 14.7.13.   | <0x62-6B>RDOC                             |     |

| 14.7.14.   | <0x6D-6F> PD                              | 145 |

| 14.8. PDE  | T ADDITIONAL OFFSET                       | 145 |

| 14.9. PRE  | E TEST FUNCTION                           |     |

| 14.9.1.    | <0x75>CURRENT                             | 146 |

| 14.9.2.    | <0x79 to 7A>DEBUG                         | 146 |

| 14.10. SOF | TWARE REST & PAGE                         | 147 |

| 14.10.1.   | <0x7D>PAGE                                | 147 |

| 14.10.2.   | <0x7E>SOFT RESET                          |     |

| 14.11. REA | AD BACK ONLY                              |     |

| 14.11.1.   | <0x03>READ COEF                           |     |

| 14.11.2.   | <0x04>STATUS                              |     |

| 14.11.3.   | <0x06 to 0B>READ RSSI                     |     |

| 14.11.4.   | <0x0C to 0D>READ NSQ                      |     |

| 14.11.5.   | <0x0E>READ PGA                            |     |

| 14.11.6.   | <0x10 to 11>READ ANA OFST                 |     |

| 14.11.7.   | <0x12 to 17>READ DIG OFST                 |     |

| 14.11.8.   | <0x18 to 1D>READ DIG OFST (OOB)           | 150 |

| 14.11.9.   | <0x1E to 23>READ AGC OFST                 | 151 |

| 14.11.10.  | <0x24 to 29>READ RDOC                     |     |

| -          | Circuit                                   |     |

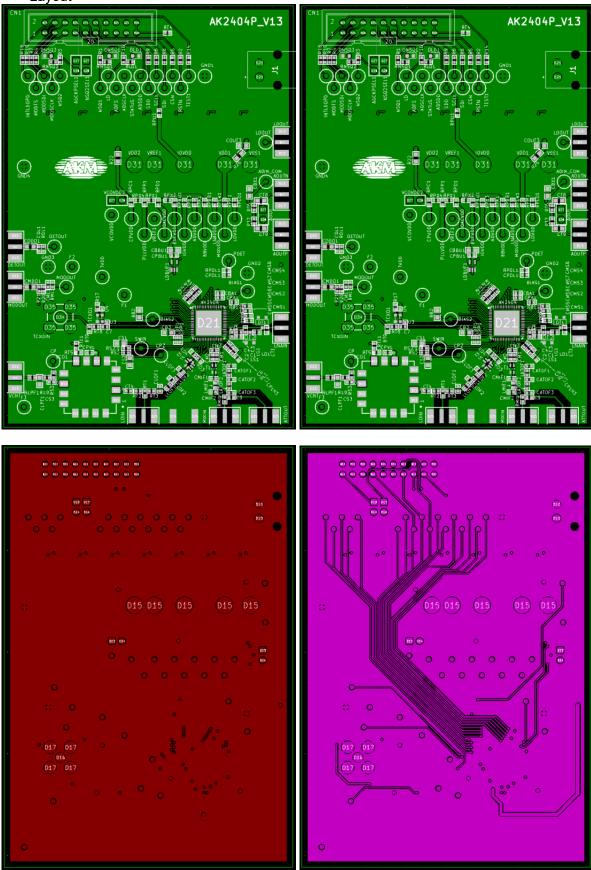

|            | erence Evaluation Board                   |     |

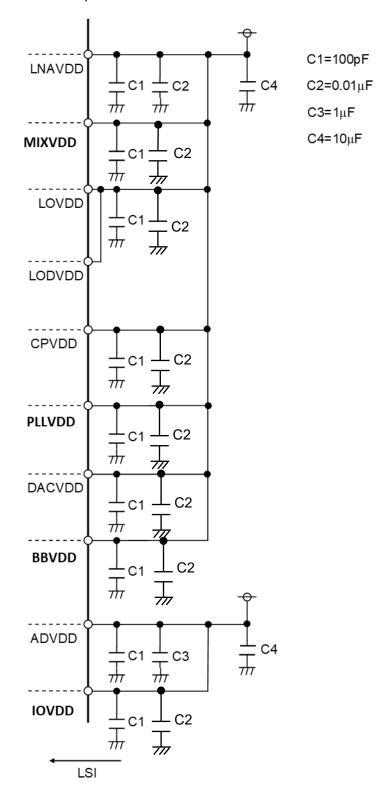

|            | ver pins and ground pins                  |     |

|            |                                           |     |

|            |                                           |     |

|            | face circuit                              |     |

|            | eut Dimensione                            |     |

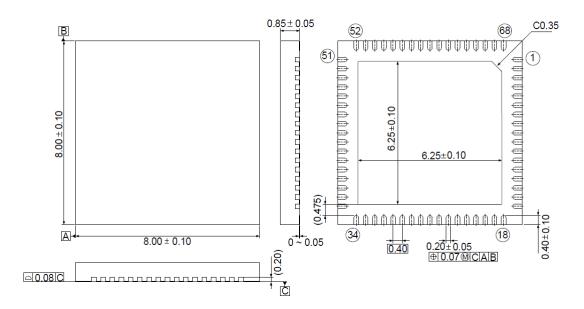

|            | Dimensions                                |     |

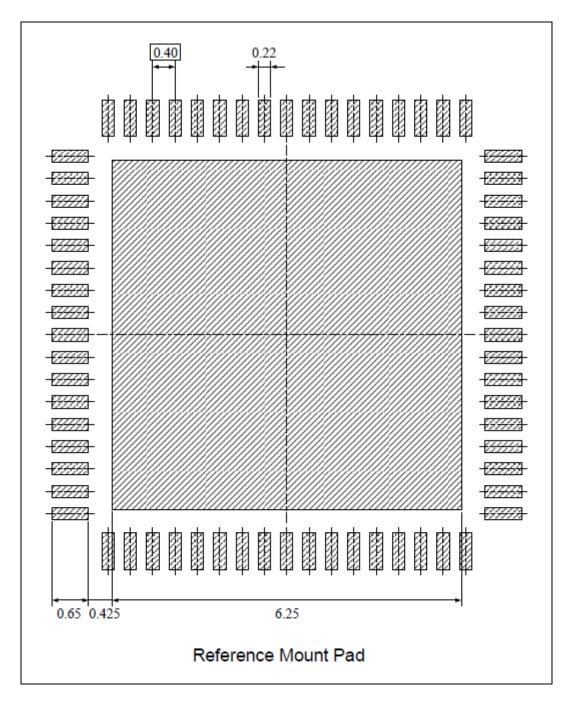

|            | Dimensions (for reference)                |     |

|            | king                                      |     |

| -          | Guide                                     |     |

|            | history                                   | 164 |

| IMPORTANT  | NOTICE                                    | 165 |

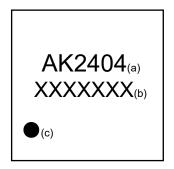

#### 4. Representation

Register names and pin names and their polarities are described below.

| NameA bit = "0" or "1" | Register           |

|------------------------|--------------------|

| NameB pin = "L" or "H" | Pin                |

| NameC, NameD bits      | Multiple registers |

| NameE, NameF pins      | Multiple pins      |

To specify the bit width of a register or to indicate a specific 1-bit of the register data, describe as follows.

NameG[2:0] bits = "000" or "101" NameH[1] bit = "0" or "1"

The address is written in the register that appears first for each page or chapter.

<Address0x9A>NameD bits

The AK2404 has multiple register maps, and <Address0x7D>PAGE bits select which register map to access.

<ROpage Address0x06>R\_RSSI bits

: Indicates the READ BACK ONLY page accessed by writing PAGE bits=46(hex).

<Address0x09>PLL\_R bits

: Unless otherwise specified, it indicates the normal page accessed by writing PAGE bits=00(hex).

Numerical values are described as follows.

- 0x9A : A hexadecimal number. Mainly used for addresses.

- 3B(hex) : A hexadecimal number. Mainly used for data.

- 18(dec) : A decimal number. Mainly used for dates.

- "10101" : A binary number. Mainly use for data.

The units used to count coefficients for digital filters are shown below.

FIR: 1TAP、2TAP、3TAP…

$\mathsf{IIR}:$  one coefficient, two coefficients, three coefficients,  $\ldots$

Abbreviations and acronyms are as follows.

- AAF : Anti-Aliasing Filter

- ADC : A/D Converter

- DAC : D/A Converter

- LDO : Low Drop Out

- LNA : Low Noise Amplifier

- LSB : Least Significant Bit

- MCU : Micro Controller Unit

- MSB : Most Significant Bit

- PGA : Programmable Gain Amplifier

220900015-E-04

PLL : Phase Locked Loop

RDOC : Real-time DC Offset Canceller

SMF : Smoothing Filter

# 5. Block Diagram and Functions

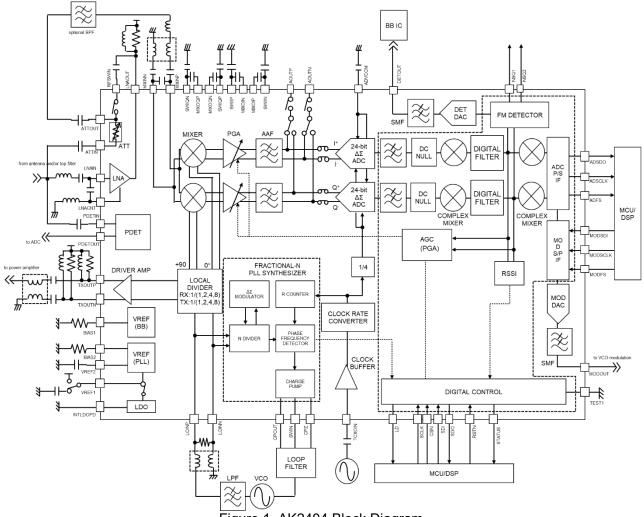

#### 5.1. Block Diagram

#### 5.2. Block Functions

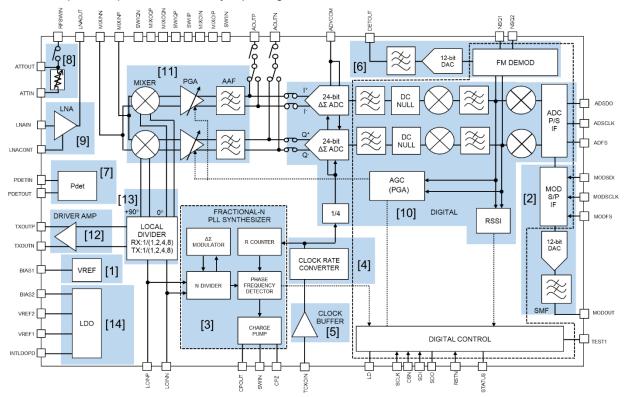

The AK2404 consists of the Analog RF Receiving Circuit (LNA, ATT and PDET), the Analog Baseband Receiving Circuit (MIXER, PGA and AAF), the Digital Receiving Circuit (ADC, DIGITAL FILTER, DC NULL, COMPLEX MIXER, AGC and ADC P/S IF), the Received Signal Strength Indication Circuit (RSSI), the FM Detection Circuit (FM DETECTION CIRCUIT, DETDAC and SMF), the Local Oscillation Circuit (PLL SYNTHESIZER, LOCAL DIVIDER, CLOCK BUFFER and CLOCK RATE CONVERTER), the Transmitting Data Generation Circuit (MOD S/P IF, MODDAC and SMF), the Transmitting Pre-amplifier Circuit (DRIVER AMP), the Reference Voltage Generation Circuit (VREF), the Internal Low Voltage Generation Circuit (LDO), and the Digital Control Circuit (DIGITAL CONTROL).

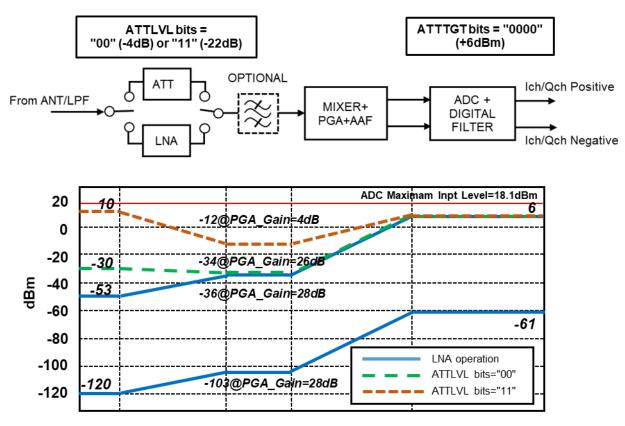

■ Analog RF Receiving Circuit (LNA, ATT, PDET)

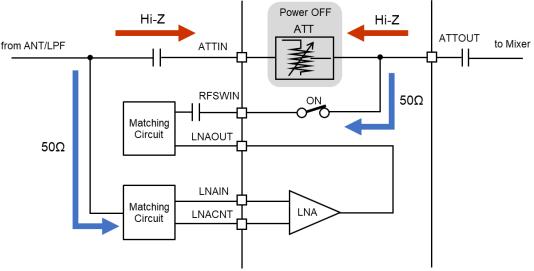

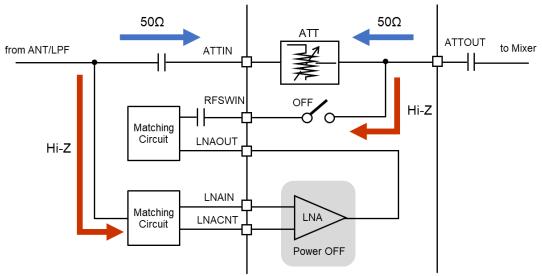

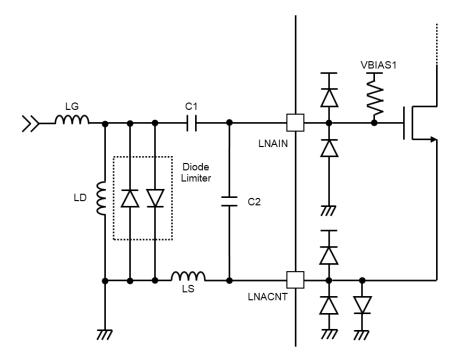

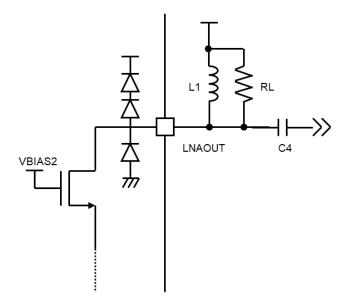

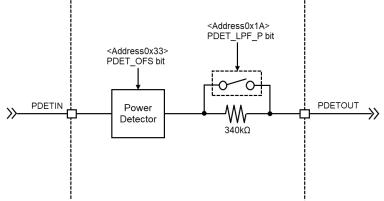

The LNA amplifies the received signal with low noise. And the ATT attenuates the received signal. The amount of attenuation can be switched to 4 levels of 0, 6, 12 or 18dB based on the insertion loss by register setting. The LNA and the ATT are connected in parallel, and operating block can be switched by register control. The PDET detects the received RF signal strength and outputs a voltage corresponding to the RF signal strength from the PDETOUT pin. The LNA requires a matching circuit. The external filter can be added between the LNA and MIXER for the request of image rejection. Refer to 13.4 Analog Receiving Circuits (LNA, ATT, PDET, MIXER, PGA, AAF) for detail.

220900015-E-04

Analog baseband circuit for receiver (MIXER, PGA, AAF)

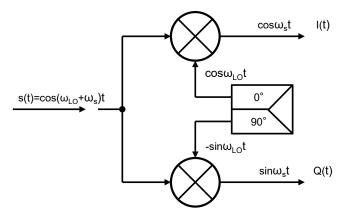

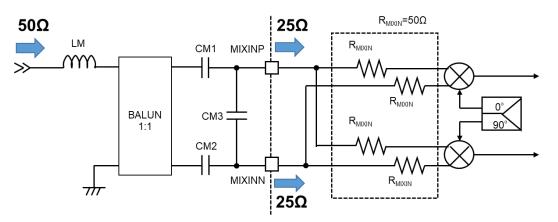

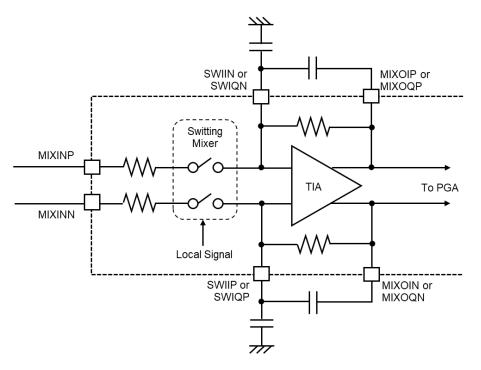

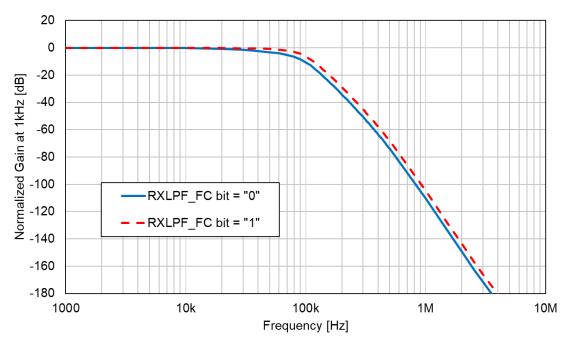

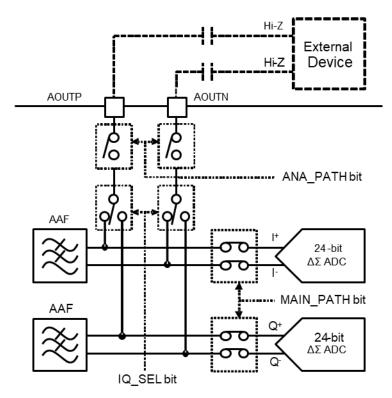

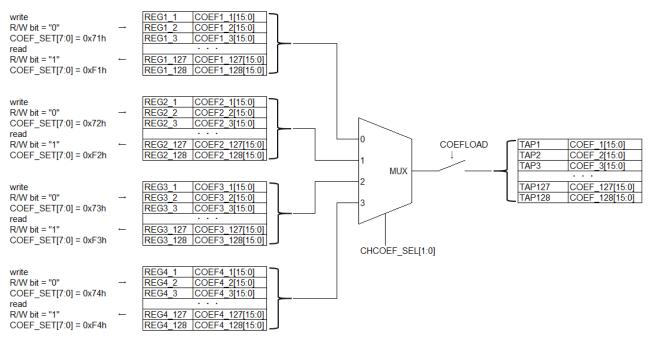

The signal amplified by the LNA is down converted to the baseband signal by the MIXER of direct conversion architecture. The MIXER works with two local signal which have a phase difference of 90 degree each other and generates the baseband signal of Ich and Qch. The MIXER input requires a matching circuit. Also, the MIXER configures a first order low pass filter with external elements. The PGA is composed by first order low pass filer with variable gain set by a register and keeps the input level of the ADC to increase the dynamic range. An AGC function is equipped to change the PGA gain automatically according to the signal input level. The AAF is anti-aliasing filter composed by the 3rd order low pass filter (Fc=100kHz) to reduce the anti-aliasing. An analog filter is composed by the MIXER, PGA and AAF to reduce the blocking signal input to the ADC. Refer 13.4 Analog Receiving Circuits (LNA, ATT, PDET, MIXER, PGA, AAF) for detail.

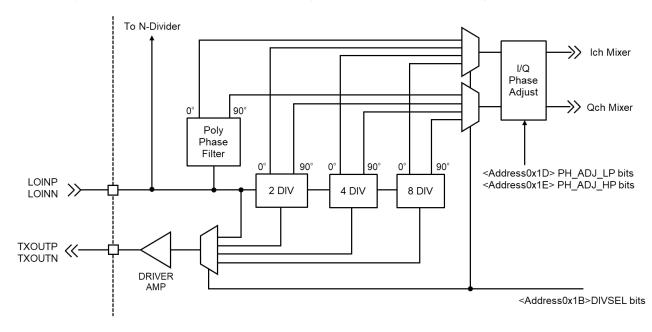

Local divider (LOCAL DIVIDER) The LOCAL DIVIDER converts the signal generated by the PLL SYTHESIZER and input from the LOINP and LOINN pins to the local frequency by dividing the signal by 1 (undivided), 2, 4 or 8. The LOCAL DIVIDER generates two local signals with 90-degree phase difference during receiving. During transmitting, the output signal from LOCAL DIVIDER is amplified by DRIVER AMP and output. Refer 13.5 LOCAL DIVIDER for detail.

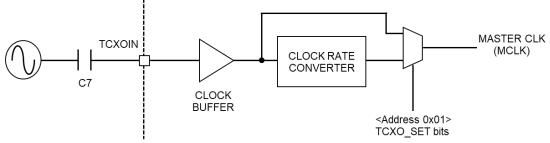

Master clock generator(CLOCK BUFFER, CLOCK RATE CONVERTER) The CLOCK BUFFER amplifies the amplitude of the reference clock input from TCXOIN pin. The CLOCK RATE CONVERTER converts the frequency of reference clock and generates an internal master clock (MCLK). If the CLOCK RATE CONVERTER is not used, the reference clock is used as master clock. The master clock is used as for the clock of the ADC and digital filters and for the reference signal generating the local signal. Refer 13.6 CLOCK BUFFER+CLOCK RATE CONVERTER for detail.

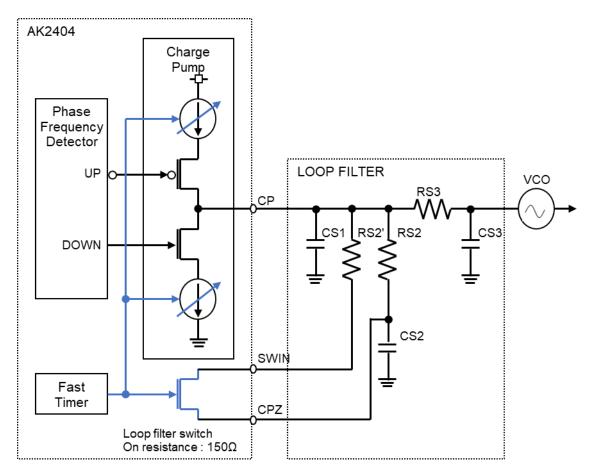

PLL synthesizer (PLL SYNTHESIZER) The FRACTIONAL-N PLL is composed by the PLL SYNTHESIZER, external LOOP FILTER and VCO and generates local frequency signal based on the master clock. Refer 13.7 PLL SYNTHESIZER for detail.

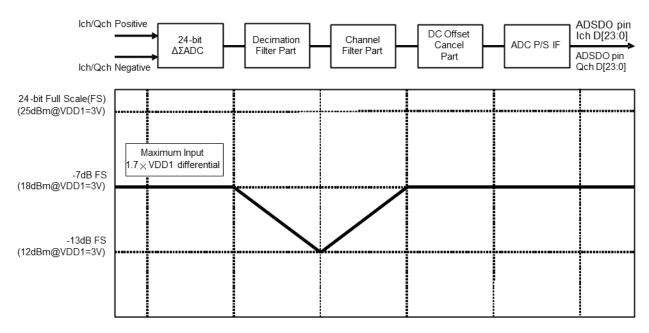

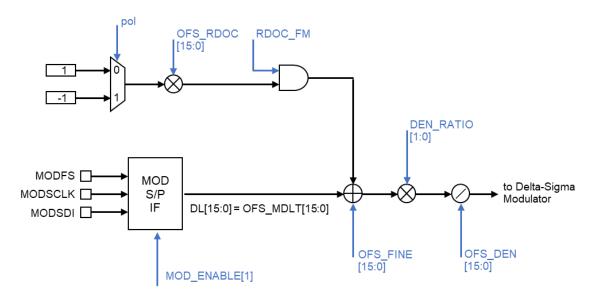

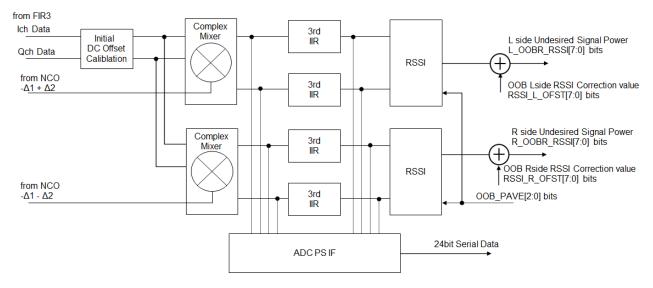

Digital circuit for receiver (ADC, DIGITAL FILTER, DC NULL, COMPLEX MIXER, AGC, ADC P/S IF)

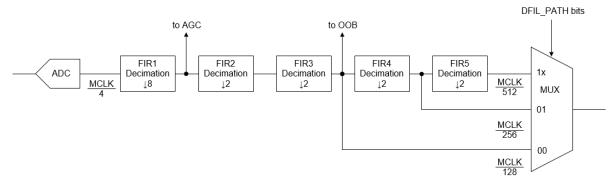

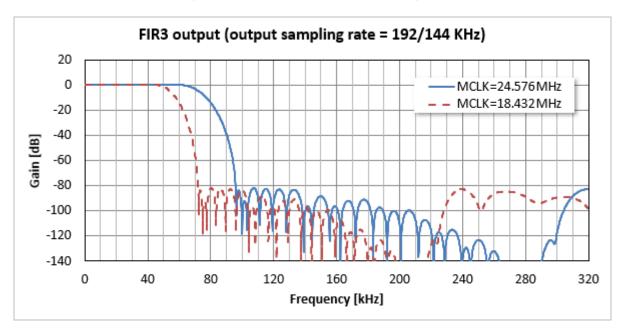

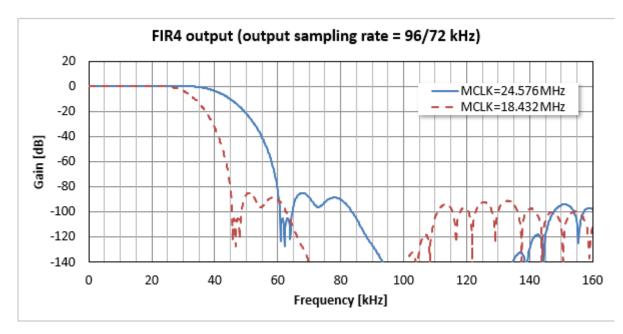

The 24-bit  $\Delta\Sigma$  ADC convert the analog signal generated by analog baseband circuit to digital signal. The digital filter is composed by decimation filter and channel filter to eliminate interference signal. The channel filter is composed by maximum 128TAP coefficients FIR filter which coefficients can be set arbitrarily to design the frequency characteristic freely.

The output sampling rate is different by a path of the selected decimation filter and the maximum sampling rate is 192kHz when the reference clock of 24.576MHz is used. The DC NULL is composed by DC offset calibration and Real-time DC Offset Canceller (RDOC) to cancel the DC offset on the baseband signal.

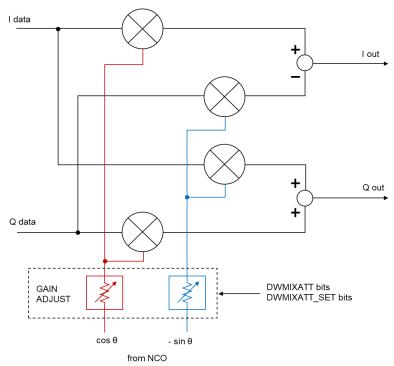

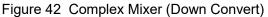

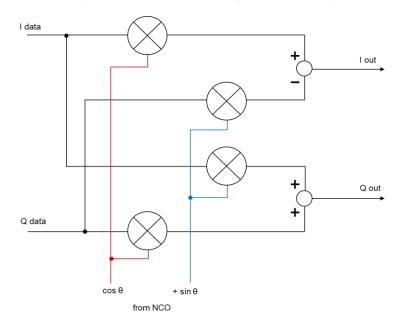

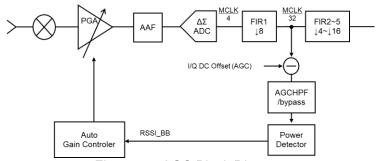

The COMPLEX MIXER is used for the frequency conversion between Low IF and Zero IF. The parallel-serial interface for ADC serially outputs the digital baseband signal by serial. By received signal strength, the AGC adjusts the PGA gain. Refer 13.8 Digital Receiving Circuits (ADC, DIGITAL FILTER, RSSI, AGC, ADC P/S IF) for detail.

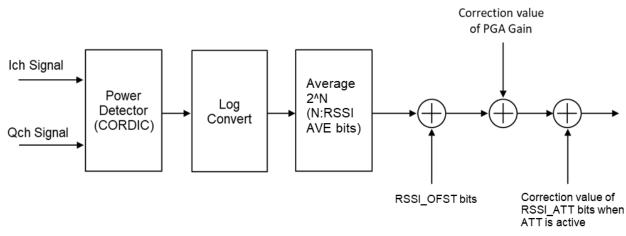

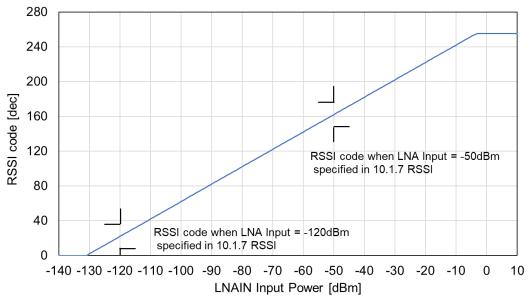

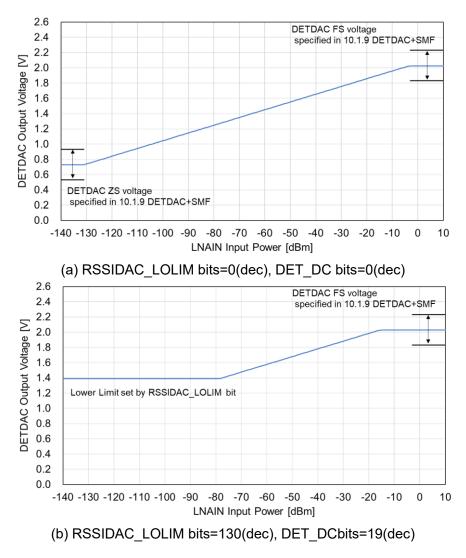

- Receiver Signal Strength Indicator (RSSI) The RSSI outputs the receiver signal strength by 8bit digital data. The 8bit data is confirmed by reading via SPI. The value of RSSI can be output from ADSDO pin or STATUS pin with synchronizing to ADFS. Refer 13.8.15 RSSI Function for detail.

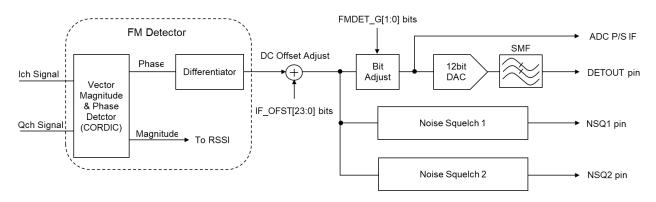

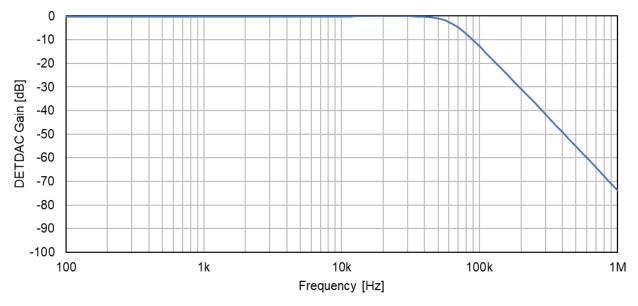

- FM detection circuit (FM DETECTOR, DETDAC, SMF) The FM DETECTOR demodulates the received FM signal. The demodulated signal is converted to analog signal by 12-bit DA (DETDAC) converter and is smoothed by the SMF with Fc=64kHz and is output from DETOUT pin. And the demodulated signal can be output as digital serial output

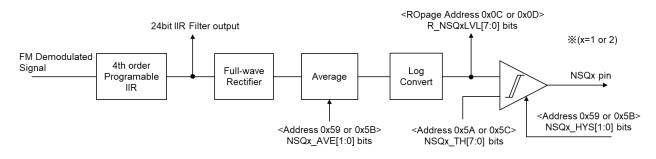

through the ADSDOI, ADSCLK and ADFS pins by a register setting. The output rate is same with the front digital filter. The FM DETECTOR also incorporates noise squelch function1 and noise squelch function2 and output the calculation result to NSQ1 and NSQ2 pins as High/Low signal respectively. Refer 13.8.13 FM Detection Function for detail.

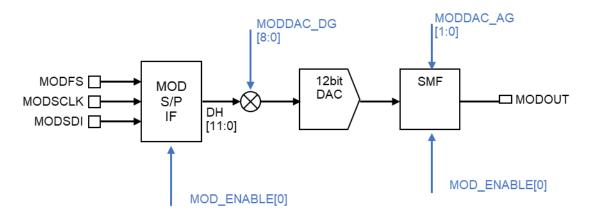

Data generator circuit for transmitter (MOD S/P IF, MODDAC, SMF) The MODDAC is 12-bit DA convertor and converts the digital baseband signal serially input to the MOD S/P IF to the analog baseband signal. The SMF (SMOOTHING FILTER) is a low pass filter which smoothen the DAC output (Fc=20kHz). These circuits are supposed to be used to generate the transmitter data when the direct modulation is executed to external VCO. Refer 13.9 Transmit Data Generation Circuit (MODDAC, SMF) for detail.

- Pre-amp circuit (DRIVER AMP) This circuit amplifies and outputs the signal divided by N by LOCAL DIVIDER. When the direct modulation is executed to external VCO, this circuit is supposed to be used as transmitter signal output. Refer 13.10 Transmit Preamplifier Circuit (DRIVER AMP) for detail.

- Internal low voltage generator circuit (LDO) This circuit generates 1.96V voltage from external 3V voltage source (PLLVDD) to a receiver digital circuit, a digital control circuit and a part of local oscillating circuit. It is possible to operate these circuits without using the LDO by suppling an external power supply to VREF1 pin. Refer 13.11 Internal Low Voltage Generator Circuit (LDO) for detail.

- Reference voltage generator (VREF)

This circuit generates the reference voltage for each block.

- Digital control circuit (DIGITAL CONTROL)

- Register write/read by 4-wire serial interface (CSN, SCLK, SDI, SDO pins)

- Input hardware reset signal (RSTN pin)

- The state of PLL (LD pin)

- Output internal state (STATUS pin)

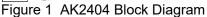

Figure 2 Pin Configurations (68-pin QFN0808, Top View)

# 6.2. Pin Functions

Al: Analog Input Pin, AO: Analog Output Pin, DI: Digital Input Pin, DO: Digital Output Pin, P: Power Supply Pin, G: Ground Pin

All digital input pins must not be allowed to float. Refer to 15.1 Reference Evaluation Board for the external element constant.

| Pin# | Pin Name  | I/O | Power Down<br>State * 1 | Function                                                                                                                     |

|------|-----------|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1    | IOVDD     | Р   | -                       | Power Supply for Digital Interface Circuit                                                                                   |

| 2    | LD        | DO  | Low                     | Lock Detection Flag Output<br>"L" : Unlock<br>"H" : Lock                                                                     |

| 3    | NSQ1      | DO  | Low                     | Noise Squelch Detection Flag Output 1                                                                                        |

| 4    | NSQ2      | DIO | Low                     | Noise Squelch Detection Flag Output 2 * 2                                                                                    |

| 5    | MODSCLK   | DI  | Hi-Z                    | Clock Input for Modulation Data Interface                                                                                    |

| 6    | MODSDI    | DI  | Hi-Z                    | Data Input for Modulation Data Interface                                                                                     |

| 7    | MODFS     | DI  | Hi-Z                    | Frame Sync Input for Modulation Data Interface                                                                               |

| 8    | DETOUT    | AO  | Hi-Z                    | FM Detection Signal Output                                                                                                   |

| 9    | MODOUT    | AO  | Hi-Z                    | Modulation Signal for Transmission Output                                                                                    |

| 10   | DACVDD    | Р   | -                       | Analog Power Supply for DETDAC and MODDAC                                                                                    |

| 11   | BIAS2     | AI  | Hi-Z                    | Resistor Connecting Pin for Charge Pump Current<br>Setting<br>Connect this pin to VSS via a 27kΩ resistor.                   |

| 12   | VREF1 * 3 | AO  | -                       | Stabilization Capacitor Connecting Pin for LDO<br>Connect this pin to VSS via a 10µF capacitor.                              |

|      |           | Р   | -                       | Digital Power Supply for Digital Circuit                                                                                     |

| 13   | TCXOIN    | AI  | Hi-Z                    | Reference Clock Input<br>Connect a 100pF capacitor to this pin<br>The pin capacitance is 3pF.                                |

| 14   | INTLDOPD  | DI  | Hi-Z                    | Internal LDO Disable Signal Input                                                                                            |

| 15   | VREF2     | AO  | -                       | Capacitor Connecting Pin for Noise Attenuation of Reference Voltage (VBG)<br>Connect this pin to VSS via a 0.47µF capacitor. |

| 16   | PLLVDD    | Ρ   | -                       | Analog Power Supply for LDO, N-DIVIDER and CLOCKRATE CONVERTER                                                               |

| 17   | PLLVSS    | G   | -                       | Analog Ground for LDO, N-DIVIDER and CLOCKRATE CONVERTER                                                                     |

| 18   | CPVDD     | Р   | -                       | Power Supply for Charge Pump                                                                                                 |

| 19   | CPOUT     | AO  | Hi-Z * 4                | Charge Pump Output                                                                                                           |

| 20   | SWIN      | AI  | Hi-Z * <mark>5</mark>   | Resistor Connecting Pin for Fast Lock                                                                                        |

| 21   | CPZ       | AI  | Hi-Z * <mark>5</mark>   | Capacitor Connecting Pin for Loop Filter                                                                                     |

| 22   | LOINP     | AI  | Hi-Z                    | Local Positive Input                                                                                                         |

| 23   | LOINN     | AI  | Hi-Z                    | Local Negative Input                                                                                                         |

| 24 | LODVDD | Р  | -                     | Analog Power Supply for Local Divider                                                          |

|----|--------|----|-----------------------|------------------------------------------------------------------------------------------------|

| 25 | TXOUTP | AO | Hi-Z * 6              | Driver Amplifier Positive Output                                                               |

| 26 | TXOUTN | AO | Hi-Z * <mark>6</mark> | Driver Amplifier Negative Output                                                               |

| 27 | LOVDD  | Р  | -                     | Analog Power Supply for Receiver Local Amplifier and Driver Amplifier                          |

| 28 | MIXINP | AI | 350Ω<br>Pull down     | MIXER Positive Input                                                                           |

| 29 | MIXINN | AI | 350Ω<br>Pull down     | MIXER Negative Input                                                                           |

| 30 | MIXVDD | Р  | -                     | Analog Power Supply for MIXER                                                                  |

| 31 | NC     | -  | -                     | Non-Connection<br>Connect to VSS.                                                              |

| 32 | ATTOUT | AO | 11kΩ<br>Pull down     | ATT Output                                                                                     |

| 33 | RFSWIN | AI | Hi-Z                  | RF Switch Input                                                                                |

| 34 | LNAOUT | AO | Hi-Z * <mark>6</mark> | LNA Output                                                                                     |

| 35 | VSS    | G  | * 7                   | Ground                                                                                         |

| 36 | LNAVDD | Р  | -                     | Analog Power Supply for LNA and ATT                                                            |

| 37 | LNACNT | AI | Hi-Z                  | LNA Matching Adjustment Pin                                                                    |

| 38 | LNAIN  | AI | 100kΩ<br>Pull down    | LNA Input                                                                                      |

| 39 | NC     | -  | -                     | Non-Connection<br>Connect to VSS.                                                              |

| 40 | ATTIN  | AI | 101kΩ<br>Pull down    | ATT Input                                                                                      |

| 41 | PDETIN | AI | 100kΩ<br>Pull down    | RF Power Detection Circuit Input                                                               |

| 42 | SWIIN  | AI | 100kΩ<br>Pull down    | Ich MIXER Switch Negative Input                                                                |

| 43 | MIXOIP | AO | 100kΩ<br>Pull down    | Ich MIXER Positive Output                                                                      |

| 44 | MIXOIN | AO | 100kΩ<br>Pull down    | Ich MIXER Negative Output                                                                      |

| 45 | SWIIP  | AI | 100kΩ<br>Pull down    | Ich MIXER Switch Positive Input                                                                |

| 46 | SWIQP  | AI | 100kΩ<br>Pull down    | Qch MIXER Switch Positive Input                                                                |

| 47 | MIXOQN | AO | 100kΩ<br>Pull down    | Qch MIXER Negative Output                                                                      |

| 48 | MIXOQP | AO | 100kΩ<br>Pull down    | Qch MIXER Positive Output                                                                      |

| 49 | SWIQN  | AI | 100kΩ<br>Pull down    | Qch MIXER Switch Negative Input                                                                |

| 50 | BBVDD  | Р  | -                     | Analog Power Supply for Base Band Circuit and PDET                                             |

| 51 | BIAS1  | AI | Hi-Z                  | Current regulating resistor connection pin Connect this pin to VSS via a $47k\Omega$ resistor. |

| 52 | AOUTP  | AO | Hi-Z                  | Receiving Analog Baseband Signal Positive Output                                               |

| 53 | AOUTN  | AO | Hi-Z                  | Receiving Analog Baseband Signal Negative Output                                               |

220900015-E-04

| 54 | PDETOUT | AO | Hi-Z               | RF Power Detection Circuit Output                                               |

|----|---------|----|--------------------|---------------------------------------------------------------------------------|

| 55 | ADVSS   | G  | -                  | Analog Ground for ADC                                                           |

| 56 | ADVDD   | Р  | -                  | Analog Power Supply for ADC                                                     |

| 57 | ADVCOM  | AO | VSS                | Stabilizing Capacitor Connecting Pin for ADC                                    |

| 58 | TEST1   | DI | 100kΩ<br>Pull down | TEST Mode Setting Pin<br>Connect to VSS.                                        |

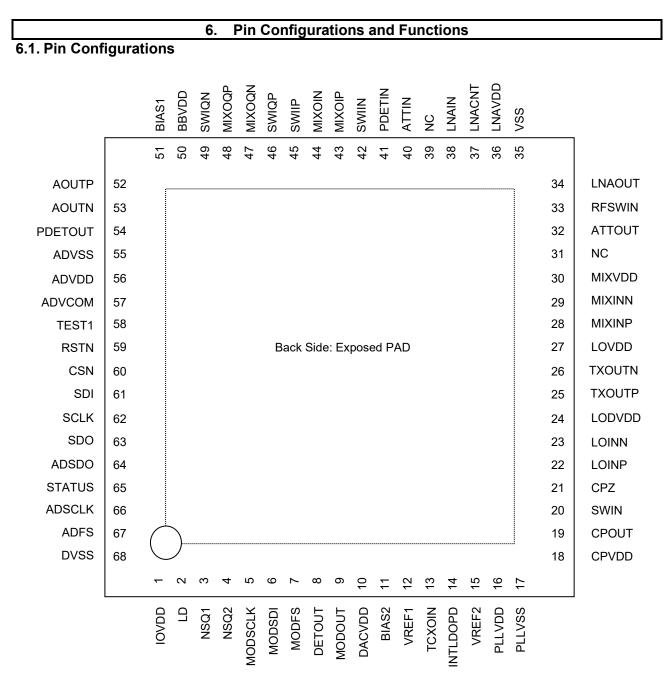

| 59 | RSTN    | DI | Hi-Z               | Hardware Reset Signal Input<br>The AK2404 is reset by "L" input of 1µs or more. |

| 60 | CSN     | DI | Hi-Z               | Chip Select Input for Register Access Interface                                 |

| 61 | SDI     | DI | Hi-Z               | Data Input for Register Access Interface                                        |

| 62 | SCLK    | DI | Hi-Z               | Clock Input for Register Access Interface                                       |

| 63 | SDO     | DO | Hi-Z               | Data Output for Register Access Interface                                       |

| 64 | ADSDO   | DO | Low                | Data Output for Receiving Data Interface                                        |

| 65 | STATUS  | DO | Low                | Status Output for Receiving Data Interface                                      |

| 66 | ADSCLK  | DO | Low                | Clock Output for Receiving Data Interface                                       |

| 67 | ADFS    | DO | Low                | Frame Sync Output for Receiving Data Interface                                  |

| 68 | DVSS    | G  | -                  | Digital Ground for Digital Interface Circuit and Digital Circuit                |

| -  | ТАВ     | G  | -                  | Exposed pad on the bottom surface of the package must be connected to VSS       |

Notes:

- \* 1. It corresponds to the state of RSTN pin="L" or the state each block is power down by the power control register described in the chapter 13.1 Power Control.

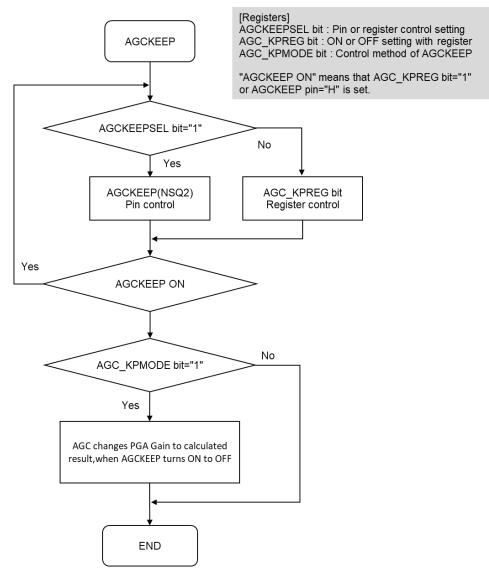

- \* 2. When <Address0x30>AGC\_KPSEL bit = "1", it works as AGC\_KEEP pin (DI). Refer to 13.8.12 AGC KEEP Function for detail. Even when used as DI, the initial value of this pin is DO, so pay attention to the polarity of the connected port. If necessary, handle it appropriately, such as adding a pull-down resistor.

- \* 3. When INTLDOPD pin = "L", the internal LDO works. When INTLDOPD pin = "H", input the power supply voltage from external source to the VREF1 pin without using internal LDO. Refer to 13.11 Internal Low Voltage Generator Circuit (LDO) for detail.

- \* 4. Though the initial state is Hi-Z, the <Address0x16>CPO\_PDST bits can switch the output state during power down. Refer to 13.7 PLL SYNTHESIZER for detail.

- \* 5. When <Address0x6E>PD\_SYNTH\_N bit = "0", the switch of loop filter selector is OFF. Refer to 13.7 PLL SYNTHESIZER.

- \* 6. Power supply must be supplied via an inductor since this pin is open drain/corrector pin.

- \* 7. Internally connected to the TAB.

# 6.3. Handling of Unused Pins

Unused input / output pins must be handled appropriately by making the following settings.

| Pin# | Pin Name | I/O | Handling       | Note                                                                                                                                    |

|------|----------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 11   | BIAS2    | AI  | Open           |                                                                                                                                         |

| 16   | PLLVDD   | Р   | Supply Voltage |                                                                                                                                         |

| 17   | PLLVSS   | G   | Connect to VSS |                                                                                                                                         |

| 18   | CPVDD    | Р   | Supply Voltage |                                                                                                                                         |

| 19   | CPOUT    | AO  | Open           |                                                                                                                                         |

| 20   | SWIN     | AI  | Open           | The same handling is also adopted in the case of that PLL SYNTHESIZER is used but the fast lock function is not used.                   |

| 21   | CPZ      | AI  | Open           | Connection is required if the PLL SYNTHESIZER is used but the fast lock function is not used. Refer to 13.7 PLL SYNTHESIZER for detail. |

# ■ Without using the PLL SYNTHESIZER

The power must be supplied to the PLLVDD/CPVDD pins even when not using the PLL SYNTHESIZER.

When the PLL SYNTHESIZER is not used, the RDOC function can not be used.

#### Without using the LNA

| Pin# | Pin Name | I/O | Handling             | Note |

|------|----------|-----|----------------------|------|

| 33   | RFSWIN   | Al  | Open                 |      |

| 34   | LNAOUT   | AO  | Connect to<br>LNAVDD |      |

| 36   | LNAVDD   | Р   | Supply Voltage       |      |

| 37   | LNACNT   | Al  | Connect to VSS       |      |

| 38   | LNAIN    | Al  | Open                 |      |

The power must be supplied to the LNAVDD pin even when not using the LNA.

#### Without using the ATT

| Pin# | Pin Name | I/O | Handling       | Note |

|------|----------|-----|----------------|------|

| 32   | ATTOUT   | AO  | Open           |      |

| 33   | RFSWIN   | Al  | Open           |      |

| 36   | LNAVDD   | Р   | Supply Voltage |      |

| 40   | ATTIN    | G   | Open           |      |

The power must be supplied to the LNAVDD pin even when not using the ATT. If the LNA is connected to the MIXER, do not use the RFSWIN pin and connect the LNAOUT pin to the MIXINP and MIXINN pins via a matching circuit.

# Without using the PDET

| Pin# | Pin Name | I/O | Handling       | Note |

|------|----------|-----|----------------|------|

| 41   | PDETIN   | Al  | Open           |      |

| 50   | BBVDD    | Р   | Supply Voltage |      |

| 54   | PDETOUT  | AO  | Open           |      |

The power must be supplied to the BBVDD pin even when not using the PDET.

#### Without using MODDAC

| Pin# | Pin Name | I/O | Handling       | Note |

|------|----------|-----|----------------|------|

| 5    | MODSCLK  | DI  | Connect to VSS |      |

| 6    | MODSDI   | DI  | Connect to VSS |      |

| 7    | MODFS    | DI  | Connect to VSS |      |

| 9    | MODOUT   | AO  | Open           |      |

| 10   | DACVDD   | Р   | Supply Voltage |      |

The power must be supplied to the DACVDD pin even when not using the MODDAC.

# Without using DRIVER AMP

| Pin# | Pin Name | I/O | Handling       | Note                                               |

|------|----------|-----|----------------|----------------------------------------------------|

| 25   | TXOUTP   | AO  | Open           | In the case of single-ended output, connect unused |

| 26   | TXOUTN   | AO  | Open           | pin to VDD.                                        |

| 27   | LOVDD    | Р   | Supply Voltage |                                                    |

The power must be supplied to the LOVDD pin even when not using the DRIVER AMP.

#### Without using FM detection circuit

| Pin# | Pin Name | I/O | Handling | Note |

|------|----------|-----|----------|------|

| 8    | DETOUT   | AO  | Open     |      |

The power must be supplied to the DACVDD pin even when not using the FM detection circuit.

#### Without using corresponding function

| Pin# | Pin Name | I/O | Handling | Note                                                     |

|------|----------|-----|----------|----------------------------------------------------------|

| 2    | LD       | DO  | Open     | Including the case of not using lock detection function. |

| 3    | NSQ1     | DO  | Open     |                                                          |

| 4    | NSQ2     | DIO | Open     |                                                          |

| 52   | AOUTP    | AO  | Open     |                                                          |

| 53   | AOUTN    | AO  | Open     |                                                          |

| 65   | STATUS   | DO  | Open     |                                                          |

#### 7. Absolute Maximum Ratings

#### (DVSS=PLLVSS=ADVSS=VSS=0V; \* 8)

| Parameter                                           |                    | Symbol             | Min. | Max.      | Unit |

|-----------------------------------------------------|--------------------|--------------------|------|-----------|------|

|                                                     | * 9                | VDD1               | -0.3 | +3.6      | V    |

| Supply Voltage                                      | IOVDD pin          | IOVDD              | -0.3 | +3.6      | V    |

|                                                     | VREF1 pin * 10     | VREF1              | -0.3 | +2.3      | V    |

| Applied Analog                                      | Input Voltage      | V <sub>AIN</sub>   | -0.3 | VDD1+0.3  | V    |

| Applied Digital I                                   | nput Voltage       | V <sub>DIN</sub>   | -0.3 | IOVDD+0.3 | V    |

| Applied Input Current<br>(except Power Supply pins) |                    | l <sub>in</sub>    | -10  | +10       | mA   |

| Maximum LNAI                                        | N Input Level * 11 | V <sub>LNAIN</sub> |      | 2.4       | Vp-p |

| Maximum ATTIN                                       | N Input Level      | ATTPOW             |      | +10       | dBm  |

| Maximum MIXIN                                       | I Input Level* 12  | MIXPOW1            |      | +14       | dBm  |

| Maximum LOIN Input Level * 13                       |                    | LOPOW              |      | +14       | dBm  |

| Maximum PDETIN Input Level                          |                    | PDETPOW            |      | +10       | dBm  |

| Storage Temper                                      | rature Range       | T <sub>stg</sub>   | -55  | 125       | °C   |

Notes:

\* 8. All voltages are with respect to ground. The DVSS, PLLVSS, ADVSS and VSS must be connected to the same ground.

\* 9. The VDD1 means PLLVDD, CPVDD, LODVDD, LOVDD, MIXVDD, LNAVDD, BBVDD, ADVDD, DACVDD pins.

\* 10. When supplying the voltage to VREF1 pin externally, set INTLDOPD pin = "H".

\* 11. This is the AC amplitude specification without DC bias at the LNAIN pin.

\* 12. This specification includes the matching circuit connected to the MIXINP and MIXINN pins.

\* 13. This specification includes the matching circuit connected to the LOINP and LOINN pins.

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# 8. Recommended Operating Conditions

#### (DVSS=PLLVSS=ADVSS=VSS=0V;\* 14)

| (Bree ree ree er; r)        |        |      |      |      |      |

|-----------------------------|--------|------|------|------|------|

| Parameter                   | Symbol | Min. | Тур. | Max. | Unit |

| Operating Temperature Range | Та     | -40  |      | 85   | °C   |

|                             | VDD1   | 2.7  | 3.0  | 3.45 | V    |

| Dewer Supply Veltage        |        | 2.7  | 3.0  | 3.45 | V    |

| Power Supply Voltage        | IOVDD  | 1.7  | 1.8  | 1.9  | V    |

|                             | VREF1  | 1.7  | 1.8  | 2.0  | V    |

Note:

\* 14. All voltages are with respect to ground. The DVSS, PLLVSS, ADVSS and VSS must be connected to the same ground.

#### 9. **Digital Characteristics** 9.1. DC Characteristics Uni Parameter Symbol Min. Тур. Max. t \* 15 0.8×IOVDD V $V_{IH1}$ High Level Input Voltage \* 16 V 0.8×PLLVDD V<sub>IH2</sub> \* 15 V V<sub>IL1</sub> 0.2×IOVDD Low Level Input Voltage \* 16 V 0.2×PLLVDD V<sub>IL2</sub> VIH1=IOVDD \* 15 +10 μA I<sub>IH1</sub> High Level Input Current VIH2=PLLVDD \* 16 +10 μΑ I<sub>IH2</sub> V<sub>IL1</sub>=0V \* 15 I<sub>IL1</sub> -10 uА Low Level Input Current V<sub>IL2</sub>=0V \* 16 $I_{1L2}$ -10 μA I<sub>OH</sub>=+0.5mA \* 17 IOVDD-0.4 IOVDD V High Level Output Voltage Vон I<sub>OL</sub>=-0.5mA \* 17 Low Level Output Voltage 0.0 0.4 V $V_{OL}$

Regarding the input current, the direction in which the current flows into the IC is defined as + and the direction in which the current flows out from the IC is defined as -.

Regarding the output current, the direction in which the current flows out from the IC is defined as + and the direction in which the current flows into the IC is defined as -.

Notes:

\* 15. MODSCLK, MODSDI, MODFS, RSTN, CSN, SDI, SCLK pins and NSQ2 pin at <Address0x30>AGC\_KPSEL bit = "1"

\* 16. INTLDOPD pin

\* 17. LD, NSQ1, NSQ2, SDO, ADSDO, STATUS, ADSCLK and ADFS pins and NSQ2 pin at <Address 0x30>AGC\_KPSEL bit = "0".

# 9.2. System Reset

# Hardware Reset

Hardware reset is executed by inputting "L" for 1µs or longer to the RSTN pin. All internal statuses are initialized by the hardware reset. Therefore, all operational settings should be made after this reset. For a certain reset of the device, inputs of the SCLK, the SDI and the CSN pins should be fixed to "L" or "H" during reset and reset release timings.

#### Software Reset

Software reset is executed by writing <Address0x7E>SRST[7:0] bits = "10101010". All internal statuses are initialized as with the hardware reset. Therefore, all operational settings should be made after this reset. The SRST[7:0] bits will be set to "00000000" automatically after software reset is completed.

#### 9.3. Serial Interface Timing for Register Access

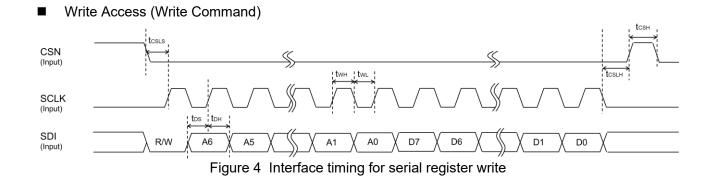

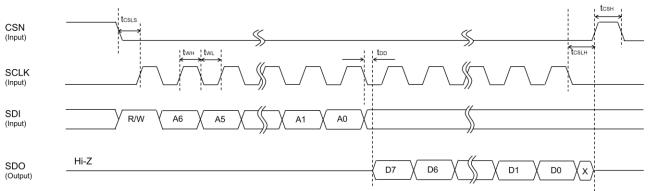

Register write and read are executed via serial interface pins (CSN, SCLK, SDI and SDO pins). A serial data input to the SDI pin consists of 1 bit Read/Write instruction, 7 bits address (MSB first, A6 to A0) and 8 bits data (MSB first, D7 to D0) in one frame (16 bits). The Figure 4 shows the timing chart of the register write operation and the Figure 5 shows the timing chart of the register read operation. And the Table 2 shows the AC timing of the register write and read operation.

Read Access (Read Command)

Figure 5 Interface timing for serial register read

R/W : Instruction bit controls the operation that writes data to the AK2404 or reads out data from the AK2404. When this bit is "0", a write operation is executed. When this bit is "1", a read operation is executed.

A6 to A0 : Register address to be accessed

D7 to D0 : Write or Read data

- (1) The CSN pin should be set to "H" when not accessing to the registers. The input clock and data are ignored when the CSN pin = "H". The serial interfaces will be activated by setting the CSN pin to "L".

- (2) In write operation, during the CSN pin = "L", register write is executed in synchronization to a rising edge of the SCLK clock that is 16 cycles. A serial data is input to the SDI pin in the order of instruction bit, address and data. The input data is latched on the 16th rising edge of the SCLK. The CSN pin must be set to "H" every time data write is finished (note that input data will be invalid if the CSN pin becomes "H" before 16th SCLK crock count. If the clock input is kept after 16 cycles while the CSN pin = "L", input clock and data after the 16th clock are also ignored).

- (3) In read operation, instruction and address bits are received in synchronization to rising edges of first 8 SCLK clocks and the data is read out from the SDO pin in synchronization to falling edge of the 8th to 15th SCLK clocks. The CSN pin must be set to "H" every time data read is finished since a consecutive reading is not supported. The polarity of the SDO pin is output only when outputting data, and it is Hi-Z output at other timings. Also, after data output, it becomes Hi-Z output at the rising edge of the CSN pin.

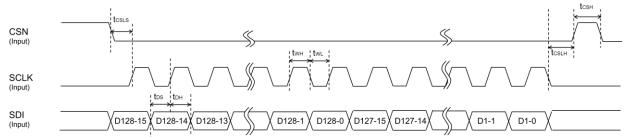

# 9.4. Serial Interface Timing for Programmable Digital Filter Coefficient Setting

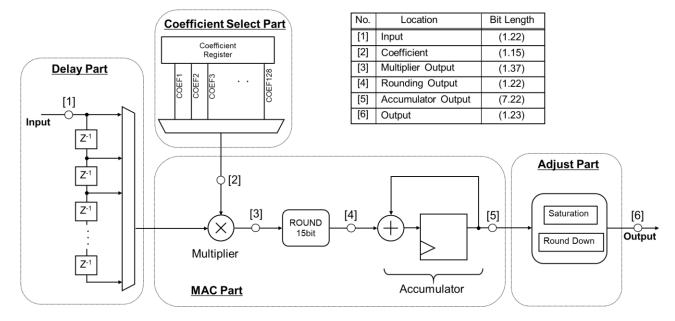

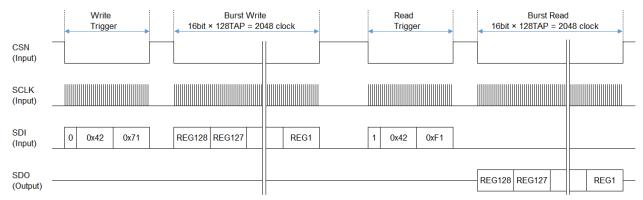

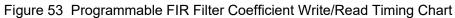

By setting the Read/Write identification bit = "0" and <Address0x42>COEF\_SET bits to the specified data, the AK2404 moves to the coefficient setting mode for programmable digital filter from register writing mode. The Table 1 shows the coefficient setting mode corresponding to the specified data.

| R/W bit | COEF_SET[7:0] (hex) | Mode                                             | Clock count                 |

|---------|---------------------|--------------------------------------------------|-----------------------------|

| "0"     | 71                  | FIR Channel Filter 1 Write                       | 2048 * 18                   |

| "0"     | 72                  | FIR Channel Filter 2 Write                       | 2048 * 18                   |

| "0"     | 73                  | FIR Channel Filter 3 Write                       | 2048 * 18                   |

| "0"     | 74                  | FIR Channel Filter 4 Write                       | 2048 * 18                   |

| "0"     | 11                  | NSQ1 IIR Filter Write                            | 160 (10 coeficients×16-bit) |

| "0"     | 12                  | NSQ2 IIR Filter Write                            | 160 (10 coeficients×16-bit) |

| "0"     | 13                  | Out of Band Power<br>Monitoring IIR Filter Write | 160 (8 coeficients×20-bit)  |

| "1"     | F1                  | FIR Channel Filter 1 Read                        | 2048 * <mark>18</mark>      |

| "1"     | F2                  | FIR Channel Filter 2 Read                        | 2048 * <mark>18</mark>      |

| "1"     | F3                  | FIR Channel Filter 3 Read                        | 2048 * 18                   |

| "1"     | F4                  | FIR Channel Filter 4 Read                        | 2048 * 18                   |

| "1"     | 91                  | NSQ1 IIR Filter Read                             | 160 (10 coeficients×16-bit) |

| "1"     | 92                  | NSQ2 IIR Filter Read                             | 160 (10 coeficients×16-bit) |

| "1"     | 93                  | Out of Band Power<br>Monitoring IIR Filter Read  | 160 (8 coeficients×20-bit)  |

| Table 1 | Programmable | digital filter | coefficient setting | mode list |

|---------|--------------|----------------|---------------------|-----------|

|         | Trogrammabic | uigitai ilitoi | coomore actung      | moue list |

Note:

\* 18. When writing and reading the coefficient of the FIR Channel Filter, if the FIR4/5 path is selected, it is 128TAP × 16-bit = 2048 clocks. When FIR3 path is selected, 64 TAP × 16-bit is repeated twice for a total of 2048 clocks.

After switching to the mode, write the coefficient data from CSN, SCLK and SDI pins according to the timings shown in Figure 6. When writing the coefficient, do not return the CSN pin to "H", and write all data continuously in the "L" state. The Figure 6 shows an example of FIR Channel Filter (128TAP), and the coefficient data of 128TAP×16-bit=2048-bits is written continuously.

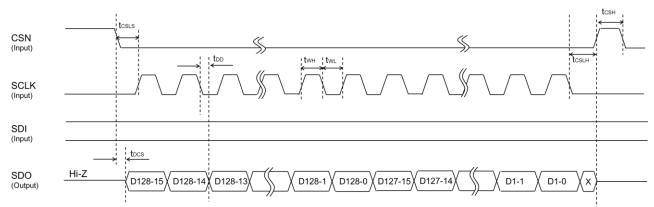

Figure 6 Interface timing for programmable digital filter coefficient write (FIR, 128TAP)

When the identification bit = "1" and the specified data is written to <Address0x42>COEF\_SET bits, the mode switches from register write mode to the programmable digital filter coefficient read mode. The Table 1 shows the coefficient read mode corresponding to the specified data. After switching to the mode, read the coefficient data from CSN, SCLK, and SDO pins according to the timings shown in the Figure 7. The Figure 7 shows an example of FIR Channel Filter (128TAP), and coefficient data of 128TAP×16-bit=2048-bits is read continuously.

Figure 7 Interface timing for programmable digital filter coefficient read (FIR, 128TAP)

When writing/reading the coefficient, input the clock for the total number of bits of all data (described in Table 1). The programmable digital filter may not operate properly if the CSN pin is raised by inputting a clock with less or more clocks than the specified clock.

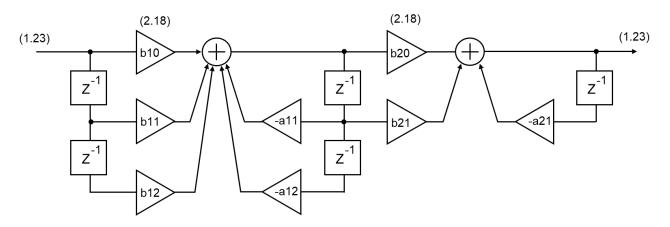

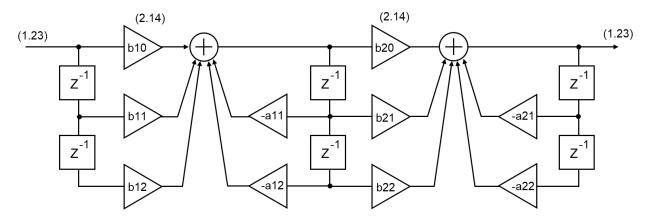

By reading back <ROpage Address0x03>R\_COEFSTS\_x bit (x=1, 2, 3, 4, OOB, NSQ1, NSQ2), it is possible to confirm whether writing/reading was successful or not. When R\_COEFSTS\_x bit = "0", it is written/read normally. The Table 2 shows the AC timing of the programmable digital filter coefficient setting mode. For details on programmable digital filter, refer to 13.8.7 Channel Filter and 13.8.17 IIR Filter.

Table 2 AC timing of register write / read and programmable digital filter coefficient setting

| Parameter                      |                  | Symbol            | Min. | Тур. | Max. | Unit |

|--------------------------------|------------------|-------------------|------|------|------|------|

| CSN low setup time             |                  | t <sub>CSLS</sub> | 50   |      |      | ns   |

| SDI setup time                 |                  | t <sub>DS</sub>   | 25   |      |      | ns   |

| SDI hold time                  |                  | t <sub>DH</sub>   | 25   |      |      | ns   |

| SCLK high time                 |                  | t <sub>WH</sub>   | 50   |      |      | ns   |

| SCLK low time                  |                  | t <sub>vvL</sub>  | 50   |      |      | ns   |

| CSN low hold time              |                  | t <sub>CSLH</sub> | 25   |      |      | ns   |

| CSN high time                  | t <sub>CSH</sub> | 50                |      |      | ns   |      |

| SCLK to SDO output delay time. | 20pF load        | t <sub>DD</sub>   |      |      | 45   | ns   |

| CSN to SDO output delay time   | 20pF load        | t <sub>DCS</sub>  |      |      | 45   | ns   |

Digital input and output timings refer to a rising/falling signal of  $0.5 \times IOVDD$ .

# 9.5. Serial Interface Timing for Receiving Data and Status Output Read

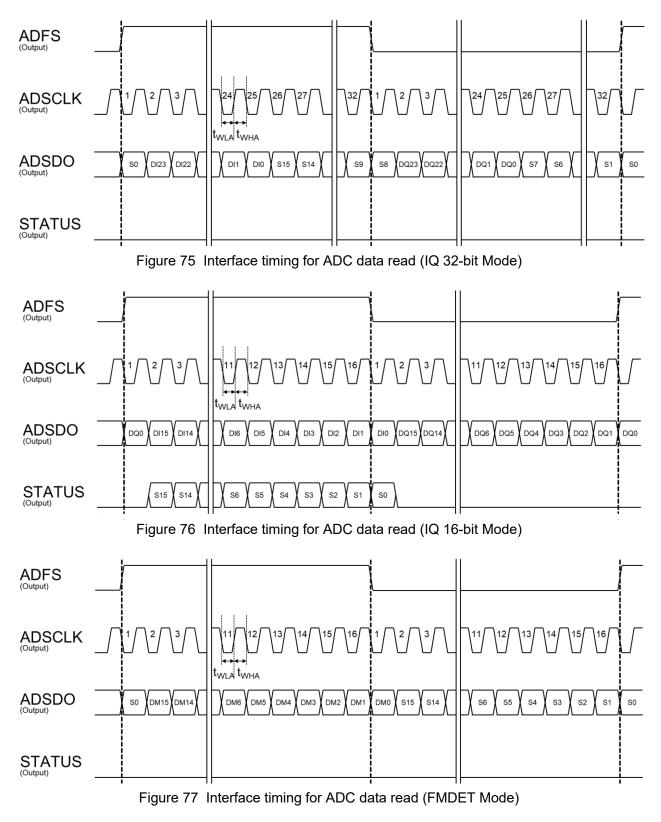

The receiving data and status output are readout via serial interface that is configured with the ADFS, ADSCLK, ADSDO and STATUS pins. The data format is selected from three types of IQ 32-bit Mode, IQ 16-bit Mode and FMDET Mode by <Address0x41>ADIFSEL[1:0] bits. The Table 3 shows AC timing.

The output sampling rate (=ADFS pin output) of receiving data and status output depends on master clock (Refer to 13.6 CLOCK BUFFER+CLOCK RATE CONVERTER for the definition of  $f_{MCLK}$ ), digital filter configuration set by <Address0x41>DFIL\_PATH[1:0] bits and the output sampling rate division setting set by <Address0x41>RXIF\_SR[1:0] bits. Refer to 13.8.18 Output Sampling Rate for detail.

The clock output from the ADSCLK pin is 64 times the output sampling rate in IQ 32-bit Mode and 32 times in both IQ 16-bit Mode and FMDET Mode. For example, when used in  $f_{MCLK}$  =24.576MHz, DFIL\_PATH[1:0] bits = "01", RXIF\_SR bits = "00", IQ 32-bit Mode, the clock frequency is 24.576MHz / 256 × 64 = 6.144MHz.

| Parameter        |           | Symbol           | Min.                   | Тур. | Max. | Unit |

|------------------|-----------|------------------|------------------------|------|------|------|

| ADSCLK frequency |           | fcka             |                        |      | 12.5 | MHz  |

| ADSCLK high time | 20pF load | t <sub>WHA</sub> | 0.4 / f <sub>ска</sub> |      |      | μs   |

| ADSCLK low time  | 20pF load | t <sub>WLA</sub> | 0.4 / f <sub>CKA</sub> |      |      | μs   |

#### Table 3 AC timing of receiving data read

Digital input and output timings refer to a rising/falling signal of 0.5 IOVDD.

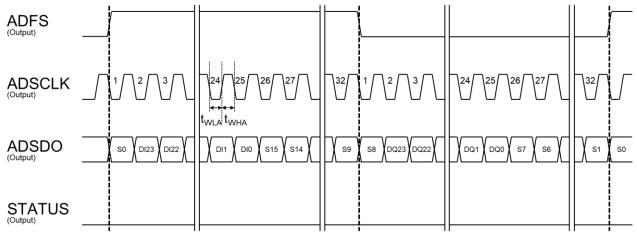

#### ■ IQ 32-bit Mode

This mode uses a fast clock for 3-wire communication and is a compatible mode with the AK2401A lineup product. Set it with ADIFSEL bits = "00". The Figure 8 shows the timing chart.

A total of 64-bit serial data is output from the ADSDO pin in synchronization with a falling edge of the ADSCLK pin. The I channel serial data is output after rising edge of the ADFS pin and the Q channel serial data is output after falling edge of ADFS pin as 32-bits data for each channel. First, 24-bits IQ data (DI23 to DI0, DQ23 to DQ0, 2's complement format, MSB first) after digital filter processes is output. Then, the internal status of RSSI and AGC is output as a status bit (S15 to S0) for 8 clocks after the last data of each "DI0" and "DQ0". In this mode, the STATUS pin outputs "L". Refer to 13.8.19 Status Output for detail.

Figure 8 Interface timing for ADC data read (IQ 32-bit Mode)

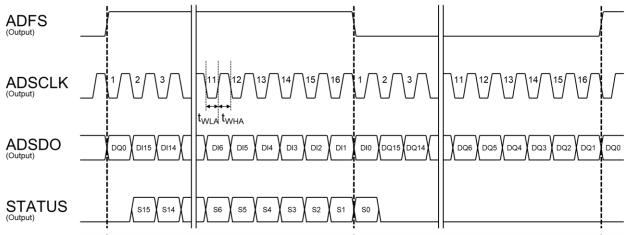

### IQ 16-bit Mode

This mode uses a slow clock for 4-wire communication. Set it with ADIFSEL bits = "01". The Figure 9 shows the timing chart.

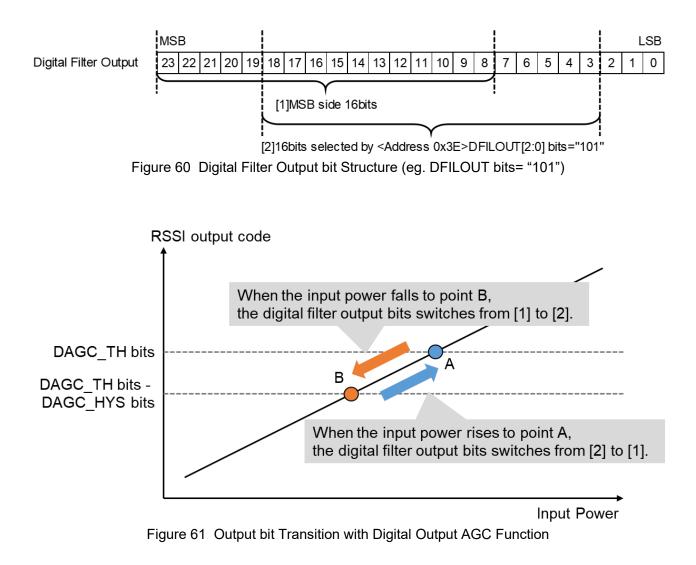

A 32-bit serial data is output from the ADSDO pin in synchronization with a falling edge of the ADSCLK pin. The I channel serial data is output after rising edge of the ADFS pin and the Q channel serial data is output after falling edge of ADFS pin as 16-bits data for each channel. These data are 16-bit data of I and Q channel (DI15 to DI0, DQ15 to DQ0, 2's complement format, MSB first), and are selected by <Address0x3E>DFILOUT bits out of 24-bit data after passing the Digital Filter. The internal status of RSSI and AGC is output as a status bit (S15 to S0) from the STATUS pin. Refer to 13.8.19Status Output for detail.

Figure 9 Interface timing for ADC data read (IQ 16-bit Mode)

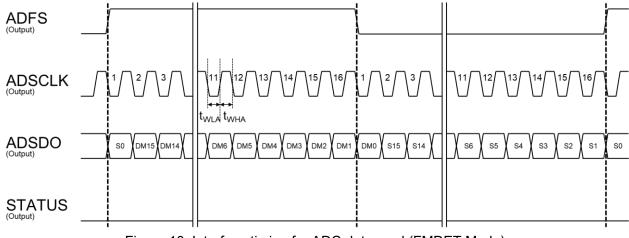

# FMDET Mode

This mode outputs the signal after FM demodulation. Set it with ADIFSEL bits = "10". The Figure 10 shows the timing chart.

A 32-bit serial data is output from the ADSDO pin in synchronization with a falling edge of the ADSCLK pin. The FM demodulation data (DM15 to DM0, 2's complement format and MSB first) is output after rising edge of the ADFS pin as 16-bits data. After that, the internal status of RSSI and AGC is output as a status bit (S15 to S0). The STATUS pin outputs "L" in this mode. Refer to 13.8.19 Status Output for detail.

Figure 10 Interface timing for ADC data read (FMDET Mode)

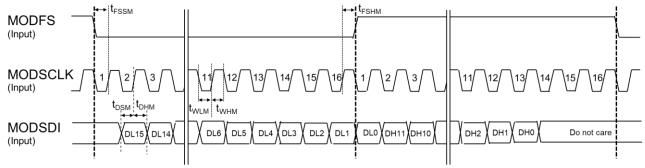

#### 9.6. Serial Interface Timing for Modulation Data Write (MOD I/F)

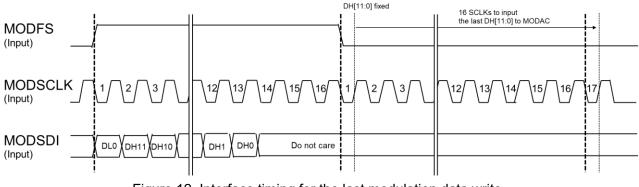

The modulation data write is executed via serial interface that is configured with the MODFS, MODSCLK and MODSDI pins. The Figure 11 shows the timing chart of the write operation of the modulation data and the Table 4 shows the AC timing of the write operation of the modulation data.

A total of 32-bit of serial data is input from the MODSDI pin in synchronization with the rising edge of the MODSCLK pin. The serial data consists of the Lch modulation data to be input to the OFS\_MDLT section of the PLL SYNTHESIZER frequency calculation formula (described in 13.7.1 Frequency Setting) from the falling edge of the second MODSCLK pin after the falling edge of MODFS pin and the Hch modulation data to be input to MODDAC from the rising edge of the second MODSCLK pin after the rising edge of MODFS pin.

The modulation data for the Lch is 16-bit and the modulation data for Hch is 12-bit. Both are in 2's complement format and MSB first. Do not care for 4 clocks after the last modulation data "DH0" of Hch. The input data is fixed at the rising edge of the clock that is 15 clocks after the MSB (DH11) of Hch (the rising edge of the first clock after the falling edge of the MODFS pin). It is necessary to input the additional 16 clocks as described in Figure 12 after the input data is fixed to input the final data to the MODDAC at the end of data input.

The input data is invalid if less than 16 clocks are input during the "L" or "H" interval of MODFS. And the first data is valid if the more than 16 clocks are input.

Figure 11 Interface timing for modulation data write

Figure 12 Interface timing for the last modulation data write

|                   | , to anning o     |      |      |      |      |

|-------------------|-------------------|------|------|------|------|

| Parameter         | Symbol            | Min. | Тур. | Max. | Unit |

| MODFS frequency   | f <sub>FSM</sub>  |      |      | 96   | kHz  |

| MODFS setup time  | t <sub>FSSM</sub> | 50   |      |      | ns   |

| MODFS hold time   | t <sub>FSHM</sub> | 50   |      |      | ns   |

| MODSDI setup time | t <sub>DSM</sub>  | 50   |      |      | ns   |

| MODSDI hold time  | t <sub>DHM</sub>  | 50   |      |      | ns   |

| MODSCLK high time | t <sub>wнм</sub>  | 100  |      |      | ns   |

| MODSCLK low time  | tw∟m              | 100  |      |      | ns   |

Table 4 AC timing of modulation data write

# 10. Analog Characteristics

Refer to 13.1 Power Control for the setting of each operation mode.

The Reference values are not tested.

The test circuit is shown in 15.1 Reference Evaluation Board and the specification includes external circuits.

# 10.1. Receiving Characteristics

Unless otherwise specified, the conditions are as follows.

VDD1= 2.7 to 3.45V, IOVDD= 1.7 to 1.9V or 2.7 to 3.45V, Temperature= -40 to 85°C

BAND1: Operating Frequency (LNA, ATT, PDET, MIXER) = 450MHz, Local Frequency = 900MHz, <Address0x1B>DIVSEL[1:0] bits = "01" (2 div)

BAND2: Operating Frequency (LNA, ATT, PDET, MIXER) = 960MHz, Local Frequency = 960MHz, <br/><a href="https://www.attication.com"></a> <br/>

<a href="https://www.attication.com">></a> <br/>

<a href="https://www.attication.com">></a> <br/>

</a> <br/>

</attication.com"<br/>

</attication.com</a> <br/>

</attication.com</td></a>

# 10.1.1. LNA

Connecting the LNA with the ATT as shown in the 15.1 Reference Evaluation Board, the characteristics at the output at the ATTOUT pin are described. This is the characteristic evaluated in Schematic Example 2 (Figure 81 Reference Evaluation Board Example 2).

| Parameter                         | Min.  | Тур. | Max. | Unit | Description     |

|-----------------------------------|-------|------|------|------|-----------------|

| Operating Frequency Range         | 45    |      | 960  | MHz  |                 |

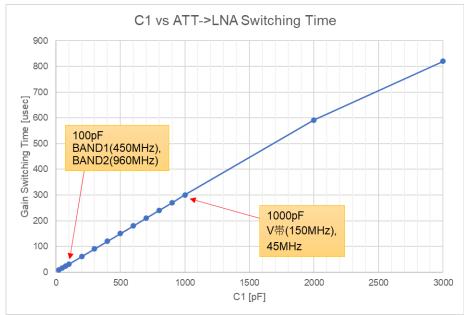

| Switching Time (ATT->LNA)         |       |      | 50   | μs   | * 19            |

| BAND1, High Power Mode, Reference | Value |      |      |      |                 |

| Gain                              | 14    | 17   | 20   | dB   |                 |

| Noise Figure                      |       | 1.7  | 2.3  | dB   |                 |

| IIP3                              | 0     | 5    |      | dBm  | * 20            |

| IP1dB                             | -15   | -7   |      | dBm  |                 |

| BAND1, Low Power Mode, Reference  | Value |      |      |      |                 |

| Gain                              | 14    | 17   | 20   | dB   |                 |

| Noise Figure                      |       | 1.7  | 2.3  | dB   |                 |

| IIP3                              | -9    | -4   |      | dBm  | * 20            |

| IP1dB                             | -15   | -7   |      | dBm  |                 |

| BAND2, High Power Mode, Reference | Value |      |      |      |                 |

| Gain                              | 14    | 17   | 20   | dB   |                 |

| Noise Figure                      |       | 2.2  | 2.8  | dB   | Reference Value |

| IIP3                              | -1    | 3    |      | dBm  | * 21            |

| IP1dB                             | -15   | -7   |      | dBm  |                 |

| BAND2, Low Power Mode, Reference  | Value |      |      |      |                 |

| Gain                              | 14    | 17   | 20   | dB   |                 |

| Noise Figure                      |       | 2.2  | 2.8  | dB   |                 |

| IIP3                              | -9    | -4   |      | dBm  | * 21            |

| IP1dB                             | -15   | -7   |      | dBm  |                 |

Notes:

\* 19. Depends on the capacitance C1 of the matching circuit, the larger the capacitance value, the longer the time. The specified value is to connect the capacitor of 100pF specified on 15.1 Reference Evaluation Board.

#### 220900015-E-04

- \* 20. Input two tone signals of 450.025MHz and 450.047MHz and measure the output signal of 450.003MHz.

- \* 21. Input two tone signals of 959.975MHz and 959.953MHz and measure the output signal of 959.997MHz.

### 10.1.2. ATT

Connecting the LNA with the ATT as shown in the 15.1 Reference Evaluation Board, the characteristics at the output at the ATTOUT pin are described. This is the characteristic evaluated in Schematic Example 2 (Figure 81 Reference Evaluation Board Example 2).

| Parameter                 | Min. | Тур. | Max. | Unit | Description           |

|---------------------------|------|------|------|------|-----------------------|

| Operating Frequency Range | 45   |      | 960  | MHz  |                       |

| BAND1, Reference Value    |      |      |      |      |                       |

| Insertion Loss            | 1.0  | 3.0  | 5.0  | dB   | ATTLVL[1:0] bits="00" |

|                           | 4.0  | 6.0  | 8.0  | dB   | ATTLVL[1:0] bits="01" |

| Attenuation Level * 22    | 10.0 | 12.5 | 15.0 | dB   | ATTLVL[1:0] bits="10" |

|                           | 15.0 | 18.5 | 22.0 | dB   | ATTLVL[1:0] bits="11" |

| IP1dB                     |      | 20   |      | dBm  |                       |

| IIP3                      |      | 30   |      | dBm  | * 23                  |

| Switching Time * 24       |      |      | 1    | μs   |                       |

| BAND2                     |      |      |      |      |                       |

| Insertion Loss            | 2.5  | 4.5  | 6.5  | dB   | ATTLVL[1:0] bits="00" |

|                           | 4.5  | 6.5  | 8.5  | dB   | ATTLVL[1:0] bits="01" |

| Attenuation Level * 22    | 10.5 | 13   | 15.5 | dB   | ATTLVL[1:0] bits="10" |

|                           | 15.5 | 19   | 22.5 | dB   | ATTLVL[1:0] bits="11" |

| IP1dB                     |      | 20   |      | dBm  | Reference Value       |

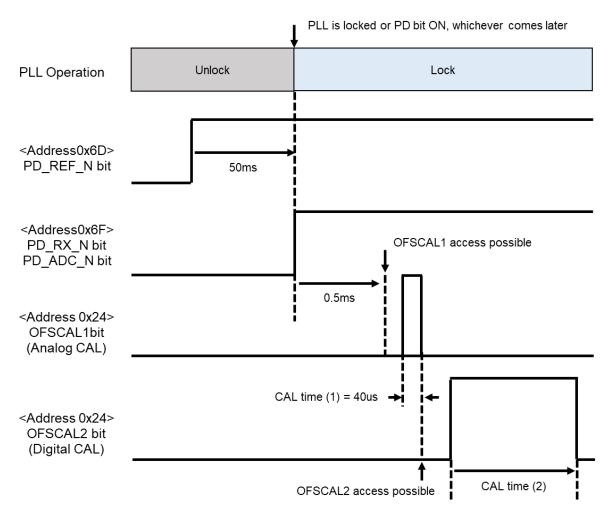

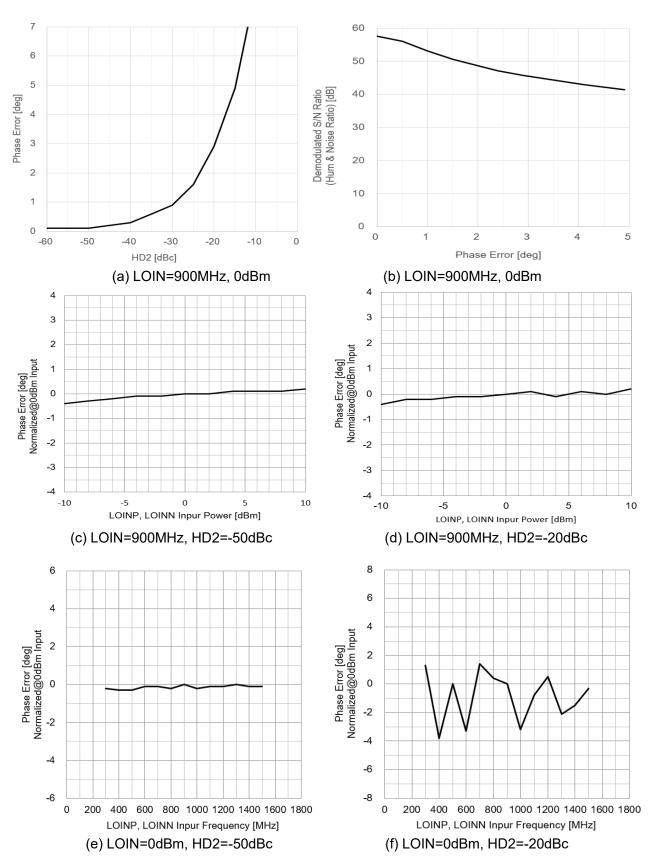

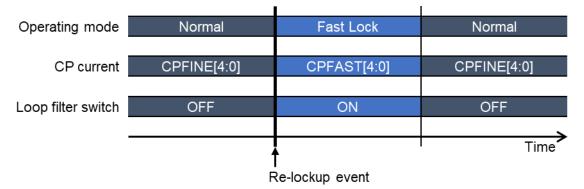

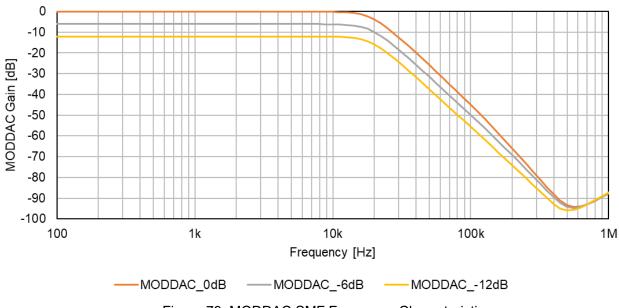

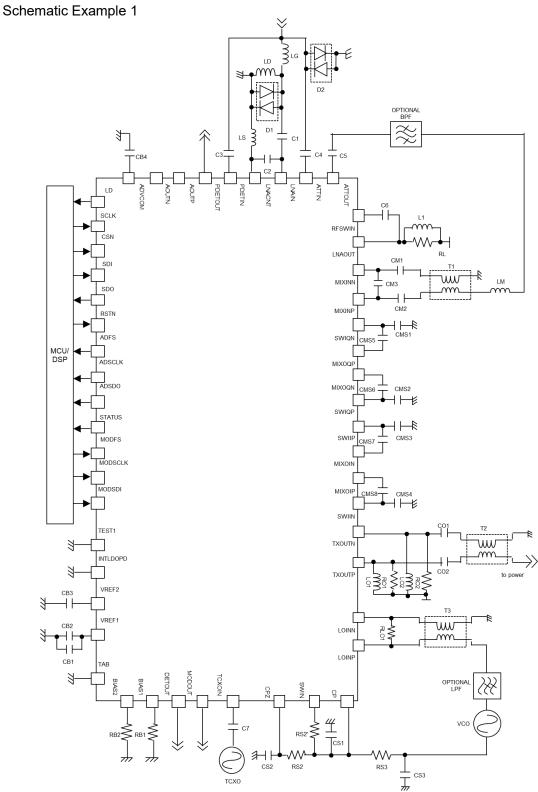

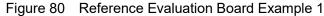

| IIP3                      |      | 30   |      | dBm  | * 25                  |