**Datasheet**

# Dynamic NFC/RFID tag IC with up to two PWM outputs and 2-Kbit EEPROM

#### Product status link

ST25DV02K-W1

ST25DV02K-W2

#### **Features**

#### Pulse width modulation outputs

- Two independent outputs: 1x PWM output on ST25DV02K-W1, 2x PWM outputs on ST25DV02K-W2

- From 488 Hz to 31250 Hz

- 62.5 ns pulse width resolution: from 15-bit resolution at 488 Hz to 9-bit resolution at 31.25 kHz

- Accuracy: ±10% over temperature range

- No need for external oscillator

- Supply voltage from 1.8 V to 5.5 V, independent from contactless interface

- · Independent push-pull outputs

- Up to 4 mA drive capability per output

- Adjustable output drive for low power and low noise application

- Live update of PWM parameters controlled by contactless interface

#### **Contactless interface**

- Based on ISO/IEC 15693 and NFC Forum Type 5 Tag

- Supports all ISO/IEC 15693 modulations, coding, sub-carrier modes and data rates

- Single and multiple blocks read

- Internal tuning capacitance: 28.5 pF

### Memory

- 2-Kbit of EEPROM

- Accessible in blocks of 4x bytes

- 5 ms typical write time (one block)

- Data retention: 40 years

- Write cycles endurance: 100k write cycles at 85 °C

#### **Data protection**

- Up to four independent areas, including the PWM control area, with flexible protection mechanism based on 32/64-bit passwords

- System configuration: write protection by 32-bit password

- TruST25 digital signature mechanism for authentication

#### Temperature range

- From -40 °C to +85 °C (contactless interface)

- From -40 °C to +105 °C (PWM interface)

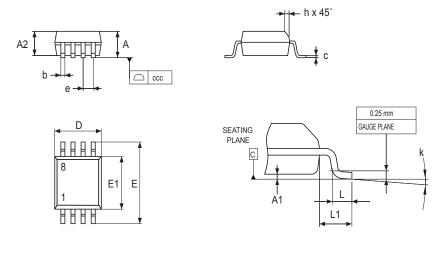

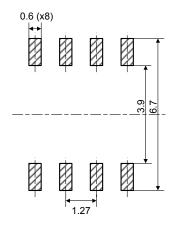

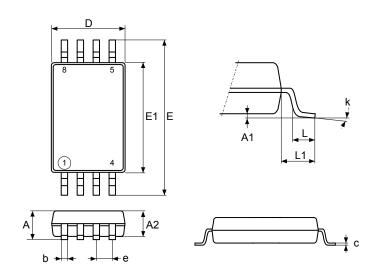

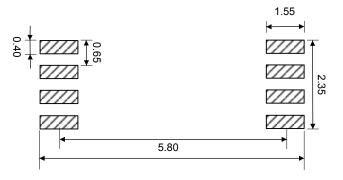

#### **Package**

- SO8N and TSSOP8

- ECOPACK2 (RoHS compliant)

# 1 Description

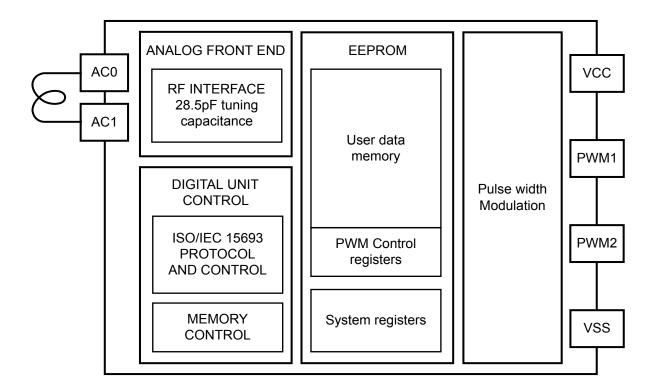

The ST25DV02K-W1/2 is an ISO 15693 and NFC Forum Type 5 tag, with one or two pulse width modulation (PWM) outputs and 2 Kbits of electrically erasable programmable memory (EEPROM).

It offers two interfaces. The first delivers up to 2x independent PWM output signals and the second is an RF link activated by the received carrier electromagnetic wave.

The PWM outputs are configured at boot time, and can be updated live through RF link. RF and PWM are independently powered and can work in stand-alone mode.

The ST25DV02K-W1/2 contains 256 bytes (64 blocks) of memory for User data. This memory is accessible through the RF interface, following ISO/IEC 15693 or NFC Forum Type 5 Tag recommendations.

The device is based on technology and design solutions for which there are pending patents.

# 1.1 Block diagram

Figure 1. Block diagram

Note: PWM2 is available only on ST25DV02K-W2.

DS12114 - Rev 7 page 2/75

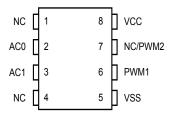

# 1.2 Package connections

ST25DV02K-W1/2 is provided in two different packages:

- SO8N

- TSSOP8

Table 1. Signal names

| Signal name     | Function           | Direction |

|-----------------|--------------------|-----------|

| AC0             | Antenna coils      | I/O       |

| AC1             | Antenna coils      | I/O       |

| V <sub>CC</sub> | PWM supply voltage | Power     |

| PWM1            | PWM output         | Output    |

| PWM2 (1)        | PWM output         | Output    |

| V <sub>SS</sub> | Ground             | -         |

<sup>1.</sup> Available only on ST25DV02K-W2.

Figure 2. ST25DV02K-W1/2 8-pin package connections

DS12114 - Rev 7 page 3/75

# 2 Signal description

# 2.1 Pulse width modulation output (PWM1)

This signal provides a pulse width modulation output. It is a push-pull output signal, driven between  $V_{SS}$  and  $V_{CC}$ . PWM1 output is in high impedance state, as long as it is disabled.

# 2.2 Pulse width modulation output (PWM2)

This signal provides a pulse width modulation output. It is a push-pull output signal, driven between  $V_{SS}$  and  $V_{CC}$ . PWM2 is independent from PWM1. PWM2 output is available on ST25DV02K-W2 only, and it is in high impedance state, as long as it is disabled.

# 2.3 PWM power supply (V<sub>CC</sub>)

This pin must be connected to an external DC supply voltage to have the PWM output(s) working.

PWM power supply is independent from the RF NFC tag part: The RF NFC tag works whatever  $V_{CC}$  power supply state is. On the other side, PWM outputs work as soon as  $V_{CC}$  power is supplied, and whatever RF field state is.

# 2.4 PWM ground reference (V<sub>SS</sub>)

$V_{SS}$  is the reference for the  $V_{CC}$  and PWM pins.

# 2.5 Antenna coil (AC0, AC1)

These inputs are used exclusively to connect the ST25DV02K-W1/2 device to an external coil. It is advised not to connect any other DC or AC path to AC0 or AC1.

When correctly tuned, the coil is used to power and access the device using the ISO/IEC 15693 and ISO 18000-3 mode 1 protocols.

DS12114 - Rev 7 page 4/75

# 3 Power management

### 3.1 Wired interface

### Operating supply voltage V<sub>CC</sub>

A valid and stable  $V_{CC}$  voltage within the specified [ $V_{CC}$ (min),  $V_{CC}$ (max)] range must be applied to guarantee PWM outputs within expected range (clock stability, jitter). To maintain a stable DC supply voltage, it is recommended to decouple the  $V_{CC}$  line with a suitable capacitor (usually one ~10 nF capacitor plus one ~100 pF capacitor) close to the  $V_{CC}/V_{SS}$  package pins.

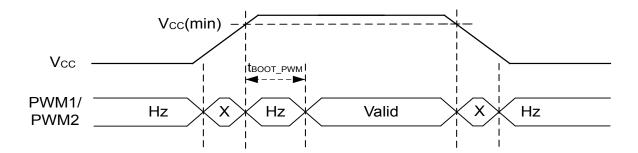

### **Power-up conditions**

When the power supply is turned on,  $V_{CC}$  rises from  $V_{SS}$  to  $V_{CC}$ . The  $V_{CC}$  rise time must not vary faster than  $1V/\mu s$ .

At power-up (continuous rise of  $V_{CC}$ ), the ST25DV02K-W enter PWM boot, as soon as  $V_{CC}$  reaches the power-on reset threshold voltage.

t boot PWM time applies to complete PWM boot and get valid PWM output signals.

In case of contactless interface access to EEPROM, the PWM boot is waiting for the end of EEPROM accesses to start.

#### **Power-down conditions**

At power-down (continuous decrease of  $V_{CC}$ ), as soon as  $V_{CC}$  drops below the power-on reset threshold voltage, the PWM output states are not guaranteed anymore.

Figure 3. Power-up/down sequence

Note: Valid when RF interface is OFF, otherwise the priorities described in Section 3.3 RF and PWM boots priority apply.

DS12114 - Rev 7 page 5/75

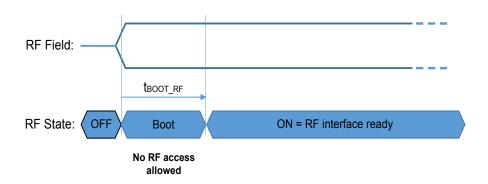

### 3.2 Contactless interface

#### Device set in RF mode

To ensure a proper boot of the RF circuitry, the RF field must be turned ON without any modulation for a minimum period of time t<sub>RF\_ON</sub>. Before this time, ST25DV02K-W1/2 ignores all received RF commands (see Figure 4. RF power-up sequence).

#### Device reset in RF mode

To ensure a proper reset of the RF circuitry, the RF field must be turned off for a minimum t<sub>RF OFF</sub> period of time.

Figure 4. RF power-up sequence

Valid when PWM power supply (V<sub>CC</sub>) is stable since t\_boot\_PWM, otherwise the priorities described in Section 3.3 RF and PWM boots priority apply.

# 3.3 RF and PWM boots priority

RF and PWM interfaces are independent, but the following boots priorities apply:

- If PWM boot (V<sub>CC</sub> rising edge) occurs while RF is booting, or RF is in use, the PWM boot is delayed upon

end of RF boot, or end of RF activity (EOF).

- If RF boot (Field On) occurs while PWMs are booting, the RF boot is delayed upon PWM boot completion.

- If RF boot (Field On) occurs while PWMs are running (valid PWM output signals), RF boot starts as described in Section 3.2 Contactless interface.

Note:

It is recommended to run RF sequences (RF Field On, set of RF commands, RF Field Off) either before PWM boot ( $V_{CC}$  power supply is OFF and stable), or after PWM boot is completed ( $V_{CC}$  power supply is ON and stable).

DS12114 - Rev 7 page 6/75

# 4 Memory management

# 4.1 Memory organization

The ST25DV02K-W1/2 memory is organized as follows:

- User memory: it is composed of four different areas, as described in Section 4.2 User memory. It contains areas for user's data, area for PWM control and area to store NFC T5 CC file if required.

- System configuration memory: it is composed of different configuration registers, among which the device configuration, the ISO15693 AFI & DSFID registers. It also contains the UID and different protection registers. Refer to Section 4.3 System configuration memory for more details

Figure 5. Memory organization

|                      | AREA0<br>(CC File)   |

|----------------------|----------------------|

|                      | AREA1                |

| User memory          | AREA2 <sup>(1)</sup> |

|                      | PWM_CTRL             |

| System configuration | CFG                  |

<sup>1.</sup> Can be merged with AREA1

DS12114 - Rev 7 page 7/75

### 4.2 User memory

User memory is addressed as blocks (= pages) of 4 bytes, starting at address 0.

All the blocks of the user memory are initialized to 00h in the factory.

The ST25DV02K-W1/2 user memory areas are defines as follow:

- AREA0 starts at address 00h. It is composed of 1x block (4x bytes) which is always readable, and can be

locked. AREA0 has been though for the CC file content according to NFC Type 5 formalism. However an

application, which does not require to be NFC Type5 compliant, can do any other usage of this block.

- AREA1 starts at address 01h. It is composed of 31x blocks (124x bytes). It can be read and/or write-protected by dedicated 1x32-bit password. AREA1 is dedicated to user's data.

- AREA2 starts at address 20h. It is composed of 32x blocks (128x bytes). It can be read, and/or write-protected by dedicated 1x32-bit password. AREA2 is dedicated to user's data.

Note:

AREA1 and AREA2 can be merged in a single area of 63x blocks (252x bytes), which can be read - and/or - write-protected by 1x64-bit password.

• PWM CTRL area starts at address F8h. It is composed of 2x blocks, one per PWM, and is dedicated to PWM control (Enable, Period value and Pulse Width value). It can be individually read - and/or - write-protected by 32-bit password.

Areas definition are fixed and can not be changed (expect the merge of AREA1 and AREA2)

Table 2 and Table 3 show the user area mode explained above.

Table 2. User memory 4x areas configuration

| Block addr. (hex) | Data bits [31:1]       | Comment                                       | RF command                                                |

|-------------------|------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 0                 | User 0 (4x bytes)      | AREA0 = CC file in case of NFC T5 application |                                                           |

| 1                 |                        |                                               |                                                           |

| 2                 |                        |                                               |                                                           |

|                   | User area (124x bytes) | AREA1                                         |                                                           |

| 1E                |                        |                                               | Read Single Block Read Multiple Blocks Write Single Block |

| 1F                |                        |                                               |                                                           |

| 20                |                        | AREA2                                         |                                                           |

|                   | User area (128x bytes) |                                               |                                                           |

|                   |                        |                                               |                                                           |

|                   |                        |                                               |                                                           |

| 3F                |                        |                                               |                                                           |

| -                 | -                      | -                                             |                                                           |

| F8                | PWM1 control           | DWM CTDI                                      |                                                           |

| F9                | PWM2 control           | PWM_CTRL                                      |                                                           |

DS12114 - Rev 7 page 8/75

Table 3. User memory 3x areas configuration

| Block addr. (hex) | Data bits [31:0]        | Comment                                       | RF command                             |

|-------------------|-------------------------|-----------------------------------------------|----------------------------------------|

| 0                 | User 0 (4x bytes)       | AREA0 = CC file in case of NFC T5 application |                                        |

| 1                 |                         |                                               |                                        |

| 2                 |                         |                                               |                                        |

|                   |                         |                                               |                                        |

| 1E                |                         |                                               |                                        |

| 1F                | Lloor area (252v bytes) | AREA1 merged with AREA2                       |                                        |

| 20                | User area (252x bytes)  |                                               | Read Single Block Read Multiple Blocks |

|                   |                         |                                               | Write Single Block                     |

|                   |                         |                                               | Time Single 27551                      |

|                   |                         |                                               |                                        |

| 3F                |                         |                                               |                                        |

| -                 | -                       | -                                             |                                        |

| F8                | PWM1 control            | PWM_CTRL                                      |                                        |

| F9                | PWM2 control            |                                               |                                        |

DS12114 - Rev 7 page 9/75

### 4.3 System configuration memory

In addition to user memory, ST25DV02K-W1/2 includes a set of registers located in the system configuration memory. Registers content is read during the boots sequences and define basic ST25DV02K-W1/2 behaviour. Some of those registers can be accessed via Read Configuration and Write Configuration commands, with an identifier acting as the register address.

Table 4. System configuration memory map shows the complete map of the system configuration registers, including their accessibility (Read / Write) and related conditions. More details are available in related registers table descriptions.

Table 4. System configuration memory map

| RF access |                                   | Static Register                                       |                                                     |  |

|-----------|-----------------------------------|-------------------------------------------------------|-----------------------------------------------------|--|

| Address   | Туре                              | Name                                                  | Function                                            |  |

| 00h       | RW (1)                            | Table 15. A1SA access                                 | AREA1 security attributes                           |  |

| 01h       | RW <sup>(1)</sup>                 | Table 17. A2SA access                                 | AREA2 security attributes                           |  |

| 02h       | RW <sup>(1)</sup>                 | Table 19. APSA access                                 | Area PWM_CTRL security attributes                   |  |

| 03h       | RW <sup>(1)</sup>                 | Table 9. PWM_CFG access                               | PWM Configuration and coexistence with RF interface |  |

| 04h       | RW <sup>(1)</sup>                 | Table 21. LOCK_CFG access                             | Configuration registers permanent lock              |  |

| NA        | R <sup>(2)</sup> W <sup>(3)</sup> | Table 23. LOCK_BLOCK of AREA0/1/2 and PWM_CTRL access | Blocks Write protection (1x lock bit per block)     |  |

| NA        | WO (4)                            | Table 34. LOCK_DSFID access                           | DSFID lock status                                   |  |

| NA        | WO <sup>(5)</sup>                 | Table 36. LOCK_AFI access                             | AFI lock status                                     |  |

| NA        | RW <sup>(4)</sup>                 | Table 38. DSFID access                                | DSFID value                                         |  |

| NA        | RW <sup>(5)</sup>                 | Table 40. AFI access                                  | AFI value                                           |  |

| NA        | RO                                | Table 42. IC_REF access                               | IC reference value                                  |  |

| NA        | RO                                | Table 44. UID access                                  | Unique identifier, 8 bytes                          |  |

| NA        | WO <sup>(6)</sup>                 | Table 25. PWD_PWM access                              | PWM Control area security session password, 4 bytes |  |

| NA        | WO <sup>(6)</sup>                 | Table 27. PWD_A1 access                               | User AREA1 security session password, 4 bytes       |  |

| NA        | WO <sup>(6)</sup>                 | Table 29. PWD_A2 access                               | User AREA2 security session password, 4 bytes       |  |

| NA        | WO <sup>(6)</sup>                 | Table 31. PWD_CFG access                              | Configuration security session password, 4 bytes    |  |

- Write access is granted if RF configuration security session is open and configuration is not locked (LOCK\_CFG register equals to 0).

- 2. LOCK\_BLOCK content is only readable through reading the Block Security Status of blocks.

- 3. Write access if the blocks are not already locked (=corresponding security session is open + block not already locked by a previous LOCK\_BLOCK command).

- 4. Write access if DSFID is not already locked by a previous LOCK\_DSFID command.

- 5. Write access if AFI is not already locked by a previous LOCK\_AFI command.

- 6. Write access only if corresponding security session is open.

DS12114 - Rev 7 page 10/75

# 5 Specific features

ST25DV02K-W1/2 offers the following features:

- Pulse width modulation output

- Data protection

- TruST25 digital signature

- · Device parameter registers

For some of them, the control registers are located in System Configuration area, and require the use of Read\_Configuration or Write\_Configuration commands. Update is only possible when the access right has been granted by presenting the configuration password (PWD\_CFG), and if the system configuration was not previously locked (by LOCK\_CFG=1).

After any valid write access to the configuration registers, the new configuration is immediately applied.

DS12114 - Rev 7 page 11/75

# 5.1 Pulse width modulation output

The chip provides up to 2x Pulse width modulation (PWM) outputs. This chapter describes how to configure and use each PWM.

# **5.1.1** Control and configuration registers

PWM control registers define the basic PWM settings for each PWM output: Enable, Period and Pulse width, as described in Section 5.1.2 Pulse width modulation feature description.

Table 5. PWM1\_CTRL access

| RF                                       |                                                                        |  |

|------------------------------------------|------------------------------------------------------------------------|--|

| Command                                  | Туре                                                                   |  |

| Read Single Block (cmd code 20h) @F8h    |                                                                        |  |

| Read Multiple Blocks (cmd code 23h) @F8h | Read and Write protectable depending on APSA register content,         |  |

| Lock Single Block (cmd code 22h) @ F8h   | on block lock status and on security session status (opened or closed) |  |

| Write Single Block (cmd code 21h) @F8h   |                                                                        |  |

Table 6. PWM1\_CTRL

| Bit     | Name        | Function                                                                                                                                                                                                                                                                | Factory Value |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| b14-b0  | PWM1_PERIOD | PWM period value <sup>(1)</sup> The period of the PWM1 output signal is calculated using the following formula: Period = 'PWM1_PERIOD' x PWMres (see Table 113. PWM characteristics ). PWM1_PERIOD value must be within the [512 : 32767] range.                        | 0000h         |

| b15     | RFU         | Reserved for future usage                                                                                                                                                                                                                                               | 0b            |

| b30-b16 | PWM1_PULSEW | PWM pulse width value <sup>(1)</sup> :  The pulse width duration of the PWM1 output signal is calculated using the following formula:  Pulse width = 'PWM1_PULSEW' x PWMres (see Table 113. PWM characteristics). PWM1_PULSEW value must be within the [0:32767] range. | 00000h        |

| b31     | PWM1_ENABLE | Enable of PWM output signal                                                                                                                                                                                                                                             | 0b            |

<sup>1.</sup> Refer to Section 5.1.2 Pulse width modulation feature description for details on PWM1\_PERIOD and PWM1\_PULSEW values.

DS12114 - Rev 7 page 12/75

PWM2\_CTRL register only applies with ST25DV02K-W2 chip version (2x PWM outputs). In case of single PWM output device version (ST25DV02K-W1), PWM2\_CTRL register value has to be kept to its factory value (all bits = 0).

Table 7. PWM2\_CTRL access

| RF                                       |                                                                |  |

|------------------------------------------|----------------------------------------------------------------|--|

| Command                                  | Туре                                                           |  |

| Read Single Block (cmd code 20h) @F9h    |                                                                |  |

| Read Multiple Blocks (cmd code 23h) @F9h | R & W protectable depending on APSA register content, on block |  |

| Lock Single Block (cmd code 22h) @ F9h   | lock status and on security session status (opened or closed)  |  |

| Write Single Block (cmd code 21h) @F9h   |                                                                |  |

Table 8. PWM2\_CTRL

| Bit     | Name        | Function                                                                                                                                                                                                                                                                   | Factory Value |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| b14-b0  | PWM2_PERIOD | PWM period value: (1) The period of the PWM2 output signal is calculated using following formula: Period = 'PWM2_PERIOD' x PWMres (see Table 113. PWM characteristics ) PWM2_PERIOD value must be within the [512: 32767] range.                                           | 0000h         |

| b15     | RFU         | Reserved for future usage                                                                                                                                                                                                                                                  | 0b            |

| b30-b16 | PWM2_PULSEW | PWM pulse width value <sup>(1)</sup> :  The pulse width duration of the PWM2 output signal is calculated using the following formula:  Pulse Width = 'PWM2_PULSEW' x PWMres (see Table 113. PWM characteristics )  PWM2_PULSEW value must be within the [0 : 32767] range. | 00000h        |

| b31     | PWM2_ENABLE | Enable of PWM output signal                                                                                                                                                                                                                                                | 0b            |

<sup>1.</sup> Refer to Section 5.1.2 Pulse width modulation feature description for details on PWM2\_PERIOD and PWM2\_PULSEW values.

DS12114 - Rev 7 page 13/75

PWM Configuration register defines the expert PWM settings: Drive and coexistence parameters, as described in Section 5.1.2 Pulse width modulation feature description.

Table 9. PWM\_CFG access

| RF                                                                                                               |          |  |

|------------------------------------------------------------------------------------------------------------------|----------|--|

| Command Type                                                                                                     |          |  |

| Read Configuration (cmd code A0h) @03h                                                                           | R always |  |

| Write Configuration (cmd code A1h) @03h W if configuration security session is open and configuration not locked |          |  |

# Table 10. PWM\_CFG

| Bit   | Name         | Function                                                                                                                                                                                                                                                                                                                                                                         | Factory Value |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| b1-b0 | PWM1_DRIVE   | PWM output driver trimming:                                                                                                                                                                                                                                                                                                                                                      | 00b           |

| b3-b2 | PWM2_DRIVE   | <ul> <li>00: Full power output available</li> <li>01: ¾ of full power output available</li> <li>10: ½ of full power output available</li> <li>11: ¼ of full power output available</li> </ul>                                                                                                                                                                                    | 00b           |

| b6-b4 | DUALITY_MNGT | PWM and RF interface coexistence (applies to both PWM):  000: Full coexistence of PWM output and RF interface  1xx: PWM output set in HiZ during RF commands <sup>(1)</sup> 1x: Power of PWM output reduced to ¼ of full power during RF commands (1)  2x1: PWM frequency reduced below Low_Freq <sup>(2)</sup> during RF commands <sup>(1)</sup> , while keeping PWM duty cycle | 000Ь          |

| b7    | RFU          | Reserved for future usage                                                                                                                                                                                                                                                                                                                                                        | 0b            |

<sup>1.</sup> During RF command period starts from SOF (Start of Frame) and ends at the end of the Answer.

DS12114 - Rev 7 page 14/75

<sup>2.</sup> Refer to Section 8 Device parameters.

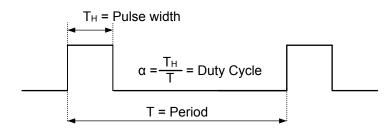

#### 5.1.2 Pulse width modulation feature description

A PWM output is characterized by two parameters:

- its period (or frequency)

- its duty cycle, representing the percentage of time the signal is in high state

Figure 6. PWM output

Period and pulse width are used to define and control the PWM output, in addition to an enable signal, allowing to put the PWM output in HiZ state.

PWM stage is supplied by  $V_{CC}/V_{SS}$  power pins. It is not supplied by RF interface. PWM works even when RF interface is OFF, as long as power is supplied through  $V_{CC}/V_{SS}$  pins. Similarly, RF interface works without  $V_{CC}/V_{SS}$ .

The PWM output stage is a push pull.

Refer to Section 3 Power management for details on V<sub>CC</sub> Power-on/power-off and related PWM output states.

#### PWM control (PWM1 CTRL and PWM2 CTRL)

PWM control registers are located in a dedicated user area (PWM\_CTRL), which is protected by a dedicated password (PWD\_PWM) and its own access right register (APSA). Each PWM output is controlled by an independent register: PWM1\_CTRL and PWM2\_CTRL.

Each PWM control register provides user access to period value, pulse width value and an enable bit of the corresponding PWM output. Period and pulse width parameters are coded on 15 bits each: PWMx\_PERIOD and PWMx\_PULSEW.

PWM output state is defined from these three parameters as follows:

PWMx PULSEW PWM EN PWMx PERIOD PWM output state Comments 0 Х х HiZ Disabled 0 0  $< V_{OL}$ Ρ 0 < W < P PWM w. Duty Cycle 1 [512:32767] ≥P > V<sub>OH</sub> 1

Table 11. PWM output parameters

An internal oscillator fixes the PWM resolution to PWMres (see Table 113. PWM characteristics ). The PWM output period and pulse width are defined as multiples of this resolution value:

- Period = PWMres x PWMx PERIOD

- Pulse Width = PWMres x PWMx PULSEW

PWM output functionality is guaranteed over PWMx\_PERIOD range from 512 to 32767, which implies a Period range from 32 to 2048  $\mu$ s (corresponding to a frequency from 31250 to 488.3 Hz). Over this range, the PWM output resolution is as follows:

DS12114 - Rev 7 page 15/75

| PWM output frequency | Number of bits used | PWM resolution                                 |

|----------------------|---------------------|------------------------------------------------|

| (Hz)                 | for PWMx_PERIOD     | (number of bits available to code PWMx_PULSEW) |

| 31250                | 9                   | 9                                              |

| 15625                | 10                  | 10                                             |

| 7813                 | 11                  | 11                                             |

| 3906                 | 12                  | 12                                             |

| 1953                 | 13                  | 13                                             |

| 977                  | 14                  | 14                                             |

| 488                  | 15                  | 15                                             |

Table 12. PWM output resolution

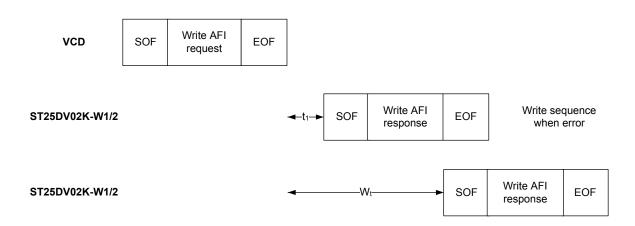

When PWM\_CTRL registers are updated by a successful RF command (Write Single Block @ F8h/F9h with response), the related PWM output change applies as follows:

RF SOF Write single block new setup @ PWM\_CTRL EOF SOF ST25DV02K-W response EOF tpwm-upp New setup

Figure 7. PWM output change

There is no anti-tearing mechanism on PWM\_CTRL registers. Write access to PWM\_CTRL registers must be done with stable RF field and constant  $V_{CC}$  state (either ON or OFF). Otherwise the RF write operation may not complete properly, implying a loss/corruption of register content, requiring a new Write operation.

### **PWM Configuration (PWM\_CFG)**

PWM configuration register is located in System Configuration area.

It provides access to output driver level adjustment, in addition to extended coexistence modes between RF and PWM interfaces.

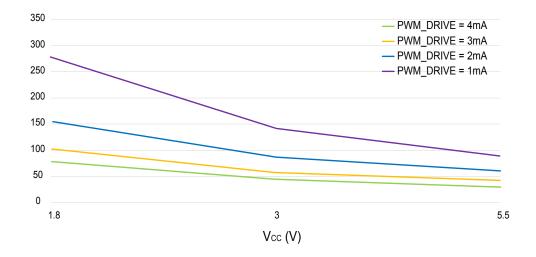

Configuration of PWM output driver trimming: the PWM push-pull output stage is able to drive up to  $I_{MAX}$  (refer to Section 8 Device parameters) by default. If the application does not require full power it is possible to reduce the output drive capability independently through PWM\_CFG trimming registers (PWM\_CFG bits b1-b0 for PWM1 and PWM\_CFG bits b3-b2 for PWM2).

| PWM_CFG[1:0]/PWM_CFG[3:2]/ PWM1/PWM2 output drive capability (sink and source) |                                                 |

|--------------------------------------------------------------------------------|-------------------------------------------------|

| 00b                                                                            | I <sub>MAX</sub> (default setup) <sup>(1)</sup> |

| 01b 75% of I <sub>MAX</sub> <sup>(1)</sup>                                     |                                                 |

| 10b                                                                            | 50% of I <sub>MAX</sub> <sup>(1)</sup>          |

| 11b                                                                            | 25% I <sub>MAX</sub> <sup>(1)</sup>             |

Table 13. PWM output driver trimming

DS12114 - Rev 7 page 16/75

<sup>1.</sup> Refer to Section 8 Device parameters.

Configuration of PWM output coexistence with RF: a PWM\_CFG Duality\_Mngt register (PWM\_CFG bits b6-b4) allows to reduce the impact of PWM noise over RF interface, and then help the coexistence. This register applies to both PWM outputs (when applicable).

Table 14. PWM output coexistence with RF interface

| PWM_CFG[6:4]                                                        | Coexistence setting                                                                                                                                                                                                                                                                                        |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 000b PWM and RF working normally and simultaneously (default setup) |                                                                                                                                                                                                                                                                                                            |  |

| 1xxb Put PWM outputs in HiZ state during RF commands.               |                                                                                                                                                                                                                                                                                                            |  |

| 01xb                                                                | Reduce PWM outputs drive to minimum power level (25% of the maximum output power level), during RF commands.                                                                                                                                                                                               |  |

| 0x1b                                                                | Reduce PWM outputs frequencies (while keeping duty cycles), in order to move them below a predefined value (Low_Freq, see Table 113. PWM characteristics), and then move out of the VCD RF sensitivity region. This option only applies if PWM output frequencies are above the predefined frequency value |  |

The option 1xxb = "Put PWM outputs in HiZ state" is exclusive option, whereas "Reduced PWM drive" and "Reduced frequency" options can be cumulated if needed.

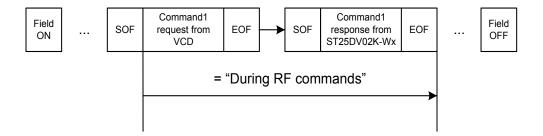

Coexistence options only applies "during RF commands", in order to minimize impact on PWM output signals. "During RF commands" period is defined from Start-of-Frame of the request command, up to the End-of-Frame of the corresponding answer:

Figure 8. PWM answer

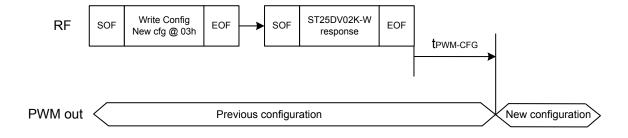

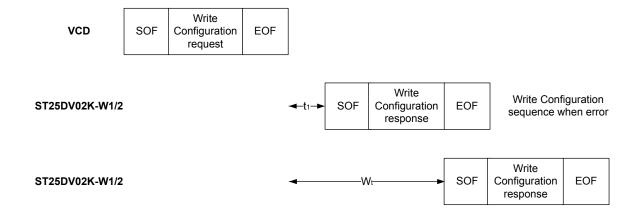

When PWM\_CFG register is updated by a successful RF command (Write\_Config @ 03h with response), PWM outputs change applies as follow:

Figure 9. PWM output change

There is no anti-tearing mechanism on PWM\_CFG register. Write access to PWM\_CFG registers shall be done with stable RF field and constant VCC state (either ON or OFF). Otherwise the RF write operation may not complete properly, and could imply a loss/corruption of register content, requiring a new Write config operation.

DS12114 - Rev 7 page 17/75

# 5.2 Data protection

ST25DV02K-W1/2 provides a special data protection mechanism based on passwords that unlock security sessions. 4 x 32 bits passwords are stored in EEPROM, covering:

- Password for AREA1

- Password for AREA2 (If AREA1 and AREA2 are merged, the corresponding area will be protected by a 64 bits password),

- Password for PWM control area

- Password for System Configuration area

User memory can be protected from read and/or write access. The system configuration is always protected from write access.

Other lock mechanisms are supported (lock block, lock AFI, lock DSFID), as described in the following sections.

### 5.2.1 Data protection registers

Registers described in this chapter are all located in System configuration memory. Refer to Table 4. System configuration memory map for more details.

Table 15. A1SA access

| RF                                      |                                                                          |  |

|-----------------------------------------|--------------------------------------------------------------------------|--|

| Command Type                            |                                                                          |  |

| Read Configuration (cmd code A0h) @00h  | R always                                                                 |  |

| Write Configuration (cmd code A1h) @00h | W if configuration security session is open and configuration not locked |  |

Table 16, A1SA

| Bit   | Name             | Function                                                                                                                                                                               | Factory Value |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|       | RW_PROTECTION_A1 | AREA1 access rights:                                                                                                                                                                   |               |

|       |                  | 00: Read always is allowed / Write always allowed                                                                                                                                      |               |

| b1-b0 |                  | 01: Read always is allowed / Write allowed only if AREA1 user security session is opened (= the proper AREA1 password has been presented)                                              | 00b           |

|       |                  | 10: Read and Write is allowed only if AREA1 user security session is opened (the proper AREA1 password has been presented)                                                             |               |

|       |                  | 11: Read is only allowed if AREA1 user security session is opened (the proper AREA1 password has been presented) / Write always forbidden                                              |               |

|       | MEM_ORG          | User memory split:                                                                                                                                                                     |               |

|       |                  | 0: user memory is split in four areas (AREA0/1/2 & PWM_CTRL)                                                                                                                           |               |

| b2    |                  | 1: user memory is split in three areas (AREA0/1 & PWM_CTRL) = AREA1 & AREA2 are merged in a single AREA1. In case of merged areas, RW_PROTECTION_A1 register applies as access rights. | 1b            |

| b7-b3 | RFU              | -                                                                                                                                                                                      | 00000b        |

DS12114 - Rev 7 page 18/75

### Table 17. A2SA access

| RF                                      |                                                                          |

|-----------------------------------------|--------------------------------------------------------------------------|

| Command Type                            |                                                                          |

| Read Configuration (cmd code A0h) @01h  | R always                                                                 |

| Write Configuration (cmd code A1h) @01h | W if configuration security session is open and configuration not locked |

# Table 18. A2SA

| Bit   | Name             | Function                                                                                                                                     | Factory Value |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|       | RW_PROTECTION_A2 | AREA2 access rights:                                                                                                                         |               |

|       |                  | 00: Read is always allowed / Write always allowed                                                                                            |               |

|       |                  | 01: Read always is allowed. Write is only allowed if AREA2 user security session is opened (= the proper AREA2 password has been presented)  |               |

| b1-b0 |                  | 10: Read and Write is only allowedif AREA2 user security session is opened (the proper AREA2 password has been presented)                    | 00b           |

|       |                  | 11: Read is only allowed if AREA2 user security session is opened (the proper AREA2 password has been presented), Write is always forbidden. |               |

|       |                  | In case of merged AREA1 + AREA2 in a single AREA1, the RW_PROTECTION_A2 bits are not used.                                                   |               |

| b7-b2 | RFU              | -                                                                                                                                            | 00000b        |

# Table 19. APSA access

| RF                                                                                                               |          |

|------------------------------------------------------------------------------------------------------------------|----------|

| Command Type                                                                                                     |          |

| Read Configuration (cmd code A0h) @02h                                                                           | R always |

| Write Configuration (cmd code A1h) @02h W if configuration security session is open and configuration not locked |          |

### Table 20. APSA

| Bit   | Name             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Factory Value |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| b1-b0 | RW_PROTECTION_AP | Area PWM_CTRL access rights:  00: Read and Write are always allowed.  01: Read is always allowed. Write is only allowed if Area PWM_CTRL user security session is opened (= the proper Area PWM_CTRL password has been presented)  10: Read and Write are only allowed if Area PWM_CTRL user security session is opened (the proper area PWM_CTRL password has been presented)  11: Read is only allowed if Area PWM_CTRL user security session is opened (the proper area PWM_CTRL password has been presented). Write is always forbidden. | 00Ь           |

| b7-b2 | RFU              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00000b        |

DS12114 - Rev 7 page 19/75

# Table 21. LOCK\_CFG access

| RF                                                                                                               |          |

|------------------------------------------------------------------------------------------------------------------|----------|

| Command Type                                                                                                     |          |

| Read Configuration (cmd code A0h) @04h                                                                           | R always |

| Write Configuration (cmd code A1h) @04h W if configuration security session is open and configuration not locked |          |

# Table 22. LOCK\_CFG

| Bit         | Name                                    | Function                                                                                                                                                                   | Factory Value |

|-------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|             |                                         | Lock configuration register:                                                                                                                                               |               |

| b0 LOCK_CFG | 0: Configuration registers are unlocked |                                                                                                                                                                            |               |

|             | LOCK_CFG                                | 1: Configuration registers are permanently locked in write.                                                                                                                | 0b            |

|             | _                                       | It only concerns configuration registers accessible by Write_Config command. Passwords, AFI, DSFID, Block lock, AFI lock & DSFID lock are not concerned by this mechanism. |               |

| b7-b1       | RFU                                     | -                                                                                                                                                                          | 0000000b      |

# Table 23. LOCK\_BLOCK of AREA0/1/2 and PWM\_CTRL access

| RF                                                         |                                             |  |

|------------------------------------------------------------|---------------------------------------------|--|

| Command                                                    | Туре                                        |  |

| Read Block (cmd code 20h) @Block addr                      |                                             |  |

| Read Multi Block (cmd code 23h) @Block addr                | R always                                    |  |

| Get Multi Block Security Status (cmd code 2Ch) @Block addr | W only if corresponding Block is not locked |  |

| Lock single Block (cmd code 22h) @Block addr               |                                             |  |

# Table 24. LOCK\_BLOCK of AREA0/1/2 and PWM\_CTRL

| Bit | Name       | Function                                  | Factory Value |    |

|-----|------------|-------------------------------------------|---------------|----|

|     |            | Lock write access of corresponding block: |               |    |

| N/A | LOCK_BLOCK | 0: Block not locked in Write              |               | 0b |

|     |            | 1: Block permanently locked in write      |               |    |

### Table 25. PWD\_PWM access

| RF                                              |                                                    |

|-------------------------------------------------|----------------------------------------------------|

| Command                                         | Туре                                               |

| No Read                                         | No Read                                            |

| Write password (cmd code B1h) with Pwd_Id = 00h | W only if PWM_CTRL Area security session is opened |

# Table 26. PWD\_PWM

| Bit      | Name    | Function                         | Factory Value |

|----------|---------|----------------------------------|---------------|

| bit31-b0 | PWD_PWM | Password value for PWM_CTRL area | 00000000h     |

DS12114 - Rev 7 page 20/75

# Table 27. PWD\_A1 access

| RF                                              |                                             |  |

|-------------------------------------------------|---------------------------------------------|--|

| Command                                         | Туре                                        |  |

| No Read                                         | No Read                                     |  |

| Write password (cmd code B1h) with Pwd_ld = 01h | W only if AREA1 security session is opened. |  |

# Table 28. PWD\_A1

| Bit    | Name   | Function                                                                                                                               | Factory Value |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|

| b31-b0 | PWD_A1 | When MEM_ORG=0: Password value for user AREA1 When MEM_ORG=1: LSB password value (32bits out of 64) for user AREA1 (merged with AREA2) | 00000000h     |

# Table 29. PWD\_A2 access

| RF                                                      |                                                                                                                                                 |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Command                                                 | Туре                                                                                                                                            |  |

| No Read Write password (cmd code B1h) with Pwd_Id = 02h | No Read W only if:  AREA2 security session is opened (when MEM_ORG=0) AREA1 security session is opened (when MEM_ORG=1, AREA1+AREA2 are merged) |  |

# Table 30. PWD\_A2

| Bit    | Name   | Function                                                                                     | Factory Value |

|--------|--------|----------------------------------------------------------------------------------------------|---------------|

|        |        | When MEM_ORG = 0: Password value for user AREA2                                              |               |

| b31-b0 | PWD_A2 | When MEM_ORG = 1: MSB password value (32 bits out of 64) for user area 1 (merged with AREA2) | 00000000h     |

# Table 31. PWD\_CFG access

| RF                                              |                                                                     |  |

|-------------------------------------------------|---------------------------------------------------------------------|--|

| Command Type                                    |                                                                     |  |

| No Read                                         | No Read                                                             |  |

| Write password (cmd code B1h) with Pwd_Id = 03h | W only if the System Configuration Area security session is opened. |  |

# Table 32. PWD\_CFG

| Bit        | Name    | Function                              | Factory Value |

|------------|---------|---------------------------------------|---------------|

| b31-<br>b0 | PWD_CFG | Password value for configuration area | 00000000h     |

DS12114 - Rev 7 page 21/75

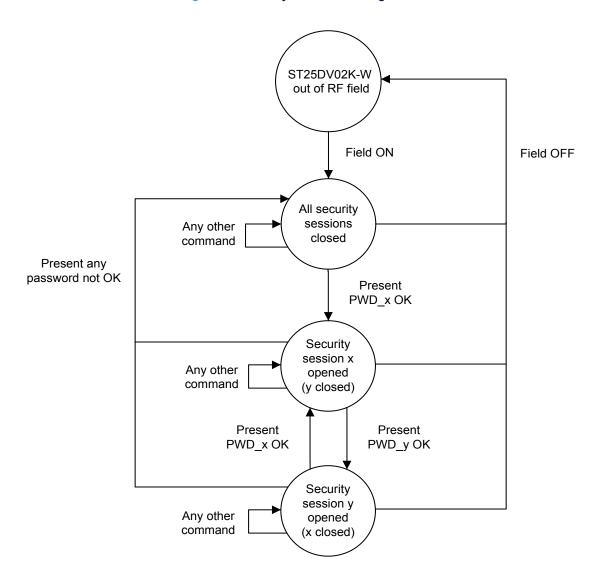

#### 5.2.2 Passwords and security sessions

ST25DV02K-W1/2 provides protection of user memory and system configuration registers. User can access to the protected data by opening security sessions thanks to the help of corresponding password.

There is two types of security sessions, as shown in Table 33:

Table 33. Security session type

| Security session | Open by presenting    | Right granted when security session is open, and until it is closed                                                                         |

|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| user             | PWD_A1 PWD_A2 PWD_PWM | User can access to corresponding user memory as defined in AiSA registers User can update the password corresponding to the opened session. |

| configuration    | PWD_CFG               | User can write configuration registers (if not permanently locked)  User can update PWM_CFG password                                        |

If AREA1 and AREA2 are independent (MEM\_ORG = 0b), each of the AREA1 and 2 passwords is 32-bit long. If AREA1 and AREA2 are merged in a single area (MEM\_ORG = 1b), the merged area password is 64-bit long (made with 32-bit AREA1 password + 32-bit AREA2 password).

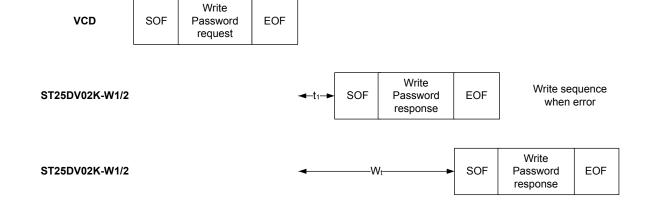

The ST25DV02K-W1/2 passwords management is based on two commands:

- Write Password (code B1h) (see Section 6.4.17 Write Password).

- Present Password (code B3h) (See Section 6.4.18 Present Password).

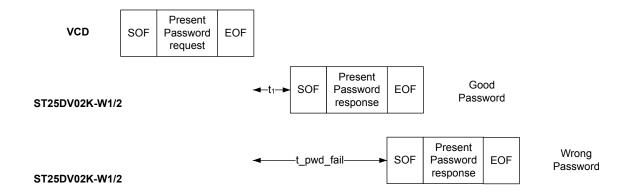

For any of the 4x passwords available, three actions are possible:

- Open Security Session: use Present\_Password command, with password identifier (00h for PWD\_PWM, 01h for PWD\_A1, 02h for PWD\_A2 and 03h for PWD\_CFG) and the valid corresponding password.

- Write password: use Present\_Password command, with password identifier (00h for PWD\_PWM, 01h for PWD\_A1, 02h for PWD\_A2 and 03h for PWD\_CFG) and the valid corresponding password. Then use Write Password command, with same password identifier and the new password.

- Close Security Session: to close the current security session, user can choose one of the following options:

- Remove tag from RF field

- Use Present Password command with a wrong password

- Use Present\_Password command to open security session of another Area (using a different password identifier). Opening a new security session (user or configuration) automatically close the previously opened one (even if the new opening fails)

Note: In case of merged AREA1 + AREA2 (MEM\_ORG=1b), the Security session opening is different:

- The 64-bit password is presented with one Present Password operation,

- Write\_Password command still applies on 32-bit password, hence update of the 64-bit password must be

done by 2x Write Password operations, with AREA1 password Id and with AREA2 password Id.

DS12114 - Rev 7 page 22/75

Figure 10 describes the mechanism to open/close the security sessions.

Figure 10. Security sessions management

### 5.2.3 User memory protection

- AREA0 (composed of a single block= block0):

- It is always readable,

- It can only be individually write locked by issuing a Lock Single Block command. This lock is permanent,

- User needs no password to lock block 0,

- Locking block 0 is possible even if the configuration is locked (LOCK\_CFG=1).

- AREA1, AREA2 and PWM CTRL areas:

- Protections are independently defined by corresponding AiSA registers (A1SA, A2SA, APSA). See

Table 15, Table 17 and Table 19 for details about available read and write protections.

- When updating AiSA registers, the new protection value is effective immediately after the register write completion.

- In addition to the password protection mechanism, each block composing AREA1, AREA2 & PWM\_CTRL can be individually locked by issuing a Lock Single Block command (permanently lock the write access to the corresponding block).

DS12114 - Rev 7 page 23/75

On factory delivery, user areas protection are all disabled.

#### Retrieve the security status of a user memory block or byte

User can read a block security status by issuing following commands:

- Get Multiple Blocks Security Status command

- Read Single Block with option flag set to 1

- Read Multiple Blocks with option flag set to 1

ST25DV02K-W1/2will respond with a Block security status containing a Lock\_bit flag as specified in ISO 15693 standard. This lock bit flag is set to one if block is locked against write.

Such lock against write can be obtained by different ways:

- Either the Lock Block bit of the block has been set (permanent)

- Or security session is closed with protection in Write (RW\_PROTECTION\_Ax = 01b or 10b or 11b)

- Or security session is opened with protection on Write always forbidden (RW\_PROTECTION\_Ax = 11b)

### 5.2.4 System configuration memory protection

By default, system memory is write protected.

To enable write access to system configuration registers, user must open the configuration security session by presenting a valid password PWD\_CFG (Id=03h) and system configuration must not be permanently locked (LOCK\_CFG=00h).

By default, user can read every system configuration registers, except passwords, LOCK\_DSFID and LOCK\_AFI. Configuration lock:

- Write access to system configuration registers can be permanently locked by writing 01h in the LOCK\_CFG register.

- User cannot unlock system configuration if LOCK\_CFG=01h, even after opening configuration security session (Lock is definitive).

- When system configuration is locked (LOCK\_CFG=01h), it is still possible to change passwords (PWD\_A1, PWD\_A2, PWD\_PWM, PWD\_CFG).

- When system configuration is locked (LOCK\_CFG=01h), it is still possible to lock AFI & DSFID registers (as described here after).

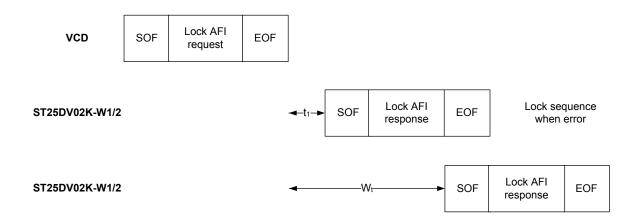

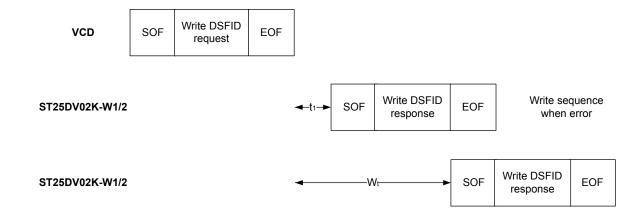

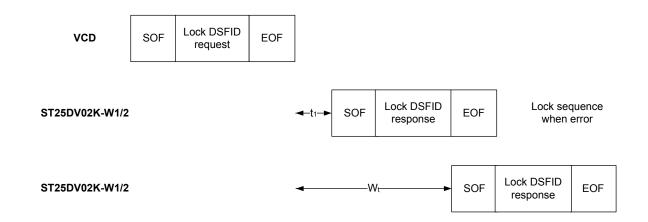

Device identification registers:

- AFI and DFSID registers can be independently locked by user, issuing respectively a Lock AFI and a Lock DSFID command. Lock is definitive: once locked, AFI and DSFID registers cannot be unlocked.

- Other device identification registers (IC\_REF, UID) are read only registers.

### 5.3 TruST25 digital signature

The ST25DV02K-W devices support the TruST25 digital signature feature, which allows the user to verify the authenticity of the device, thanks to a unique digital signature.

TruST25 solution encompasses secure industrialization processes and tools deployed by STMicroelectronics to generate, store and check the signature in the device.

Refer to "AN5149 – TruST25 digital signature for ST25DV02K-W series Dynamic NFC Tags", available under NDA, for more details on how to use it. Contact your STMicroelectronics sales office to get this document.

DS12114 - Rev 7 page 24/75

# 5.4 Device parameter registers

Registers described in this chapter are located in System configuration memory. Refer to Table 4. System configuration memory map for more details.

# Table 34. LOCK\_DSFID access

| RF                        |                        |

|---------------------------|------------------------|

| Command                   | Туре                   |

| Lock DSFID (cmd code 2Ah) | WO if DSFID not locked |

# Table 35. LOCK\_DSFID

| Bit   | Name       | Function                                  | Factory Value |

|-------|------------|-------------------------------------------|---------------|

| b0    | LOCK_DSFID | 0: DSFID is not locked 1: DSFID is locked | 0b            |

| b7-b1 | RFU        | -                                         | 0000000b      |

### Table 36. LOCK\_AFI access

| RF                      |                      |  |

|-------------------------|----------------------|--|

| Command                 | Туре                 |  |

| Lock AFI (cmd code 28h) | WO if AFI not locked |  |

# Table 37. LOCK\_AFI

| Bit   | Name     | Function                              | Factory Value |

|-------|----------|---------------------------------------|---------------|

| b0    | LOCK_AFI | 0: AFI is not locked 1: AFI is locked | 0b            |

| b7-b1 | RFU      | -                                     | 000000b       |

### Table 38. DSFID access

| RF                             |                       |  |  |  |  |

|--------------------------------|-----------------------|--|--|--|--|

| Command                        | Туре                  |  |  |  |  |

| Inventory (cmd code 01h)       | Delivere              |  |  |  |  |

| Get System Info (cmd code 2Bh) | R always              |  |  |  |  |

| Write DSFID (cmd code 28h)     | W if DSFID not locked |  |  |  |  |

### Table 39. DSFID

| Bit   | Name  | Function                                     | Factory Value |

|-------|-------|----------------------------------------------|---------------|

| b7-b0 | DSFID | ISO/IEC 15693 Data Storage Format Identifier | 00h           |

DS12114 - Rev 7 page 25/75

### Table 40. AFI access

| RF                             |                     |  |  |  |  |

|--------------------------------|---------------------|--|--|--|--|

| Command                        | Туре                |  |  |  |  |

| Inventory (cmd code 01h)       | Delugra             |  |  |  |  |

| Get System Info (cmd code 2Bh) | R always            |  |  |  |  |

| Write AFI (cmd code 27h)       | W if AFI not locked |  |  |  |  |

### Table 41. AFI

| Bit   | Name | Function                                    | Factory Value |

|-------|------|---------------------------------------------|---------------|

| b7-b0 | AFI  | ISO/IEC 15693 Application Family Identifier | 00h           |

# Table 42. IC\_REF access

| RF                             |      |  |

|--------------------------------|------|--|

| Command                        | Туре |  |

| Get System Info (cmd code 2Bh) | RO   |  |

### Table 43. IC\_REF

| Bit   | Name   | Function                   | Factory Value         |

|-------|--------|----------------------------|-----------------------|

| b7-b0 | IC_REF | ISO/IEC 15693 IC Reference | 38/39h <sup>(1)</sup> |

1. 38h applies to ST25DV02K-W1, 39h applies to ST25DV02K-W2.

### Table 44. UID access

| RF                             |      |  |  |  |

|--------------------------------|------|--|--|--|

| Command                        | Туре |  |  |  |

| Inventory (cmd code 01h)       | RO   |  |  |  |

| Get System Info (cmd code 2Bh) | NO   |  |  |  |

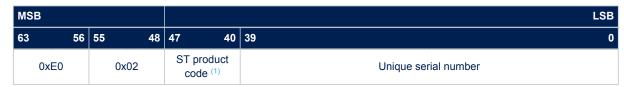

### Table 45. UID

| Bit     | Name | Function                                  | Factory Value                 |

|---------|------|-------------------------------------------|-------------------------------|

| b7-b0   | UID  | ISO/IEC 15693 UID byte 0 (LSB)            |                               |

| b15-b8  |      | ISO/IEC 15693 UID byte 1                  |                               |

| b23-b16 |      | ISO/IEC 15693 UID byte 2                  | IC manufacturer serial number |

| b31-b24 |      | ISO/IEC 15693 UID byte 3                  |                               |

| b39-b32 |      | ISO/IEC 15693 UID byte 4                  |                               |

| b47-b40 |      | ISO/IEC 15693 UID byte 5: ST Product code | 38/39h <sup>(1)</sup>         |

| b55-b48 |      | ISO/IEC 15693 UID byte 6: IC Mfg code     | 02h                           |

| b63-b56 |      | ISO/IEC 15693 UID byte 7 (MSB)            | E0h                           |

1. 38h applies to ST25DV02K-W1, 39h applies to ST25DV02K-W2

DS12114 - Rev 7 page 26/75

# 6 RF operation

Contactless exchanges are performed as specified by ISO/IEC 15693 and NFC Forum Type 5 Tag. The device communicates via the 13.56 MHz carrier electromagnetic wave on which incoming data are demodulated from the received signal amplitude modulation (ASK: amplitude shift keying). The received ASK wave is 10% or 100% modulated with a data rate of 1.6 Kbit/s using the 1/256 pulse coding mode or a data rate of 26 Kbit/s using the 1/4 pulse coding mode.

Outgoing data are generated by the ST25DV02K-W1/2 load variation using Manchester coding with one or two subcarrier frequencies at 423 kHz and 484 kHz. Data are transferred from the ST25DV02K-W1/2 at 6.6 Kbit/s in low data rate mode and 26 Kbit/s in high data rate mode.

The device follows ISO/IEC 15693 and NFC Forum Type 5 Tag recommendation for radio-frequency power and signal interface and for anticollision and transmission protocol.

### 6.1 RF communication

#### 6.1.1 Access to an ISO/IEC 15693 device

The dialog between the reader and the ST25DV02K-W1/2 takes place as follows:

- activation of the ST25DV02K-W1/2 by the operating field of the reader

- transmission of a command by the reader (ST25DV02K-W1/2 detects carrier amplitude modulation)

- transmission of a response by the ST25DV02K-W1/2 using load modulation.

These operations use the power transfer and communication signal interface described below. This technique is called RTF (reader talk first).

#### Operating field

The ST25DV02K-W1/2 operates continuously between the minimum and maximum values of the electromagnetic field H defined in Table 112. RF characteristics. The reader has to generate a field within these limits.

#### Power transfer

Power is transferred to the ST25DV02K-W1/2 by radio frequency at 13.56 MHz via coupling antennas in the ST25DV02K-W1/2 and the reader. The operating field of the reader is transformed on the ST25DV02K-W1/2 antenna to an AC voltage that is rectified, filtered and internally regulated. During communications, the amplitude modulation (ASK) on this received signal is demodulated by the ASK demodulator.

#### **Frequency**

The ISO 15693 standard defines the carrier frequency (f<sub>C</sub>) of the operating field as 13.56 MHz ± 7 kHz.

# 6.2 RF protocol

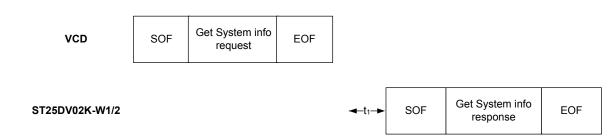

### 6.2.1 Protocol description

The transmission protocol (or simply "the protocol") defines the mechanism used to exchange instructions and data between the VCD (vicinity coupling device) and the VICC (vicinity integrated circuit card) in both directions. It is based on the concept of "VCD talks first". The device acts as the VICC.

This means that a ST25DV02K-W1/2 does not start transmitting unless it has received and properly decoded an instruction sent by the VCD. The protocol is based on an exchange of:

- a request from the VCD to the ST25DV02K-W1/2

- a response from the ST25DV02K-W1/2 to the VCD.

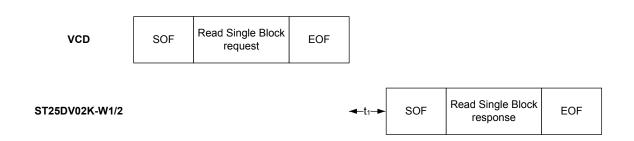

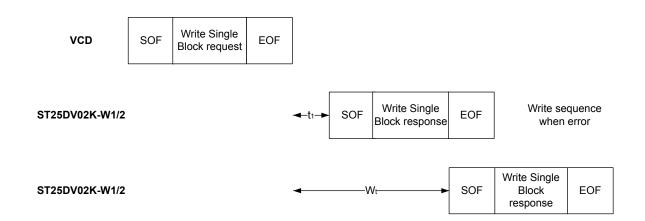

Each request and each response are contained in a frame. The frames are delimited by a Start of Frame (SOF) and End of Frame (EOF).

The protocol is bit-oriented. The number of bits transmitted in a frame is a multiple of eight (8), that is an integer number of bytes.

A single-byte field is transmitted least significant bit (LSBit) first. A multiple-byte field is transmitted least significant byte (LSByte) first and each byte is transmitted least significant bit (LSBit) first.

DS12114 - Rev 7 page 27/75

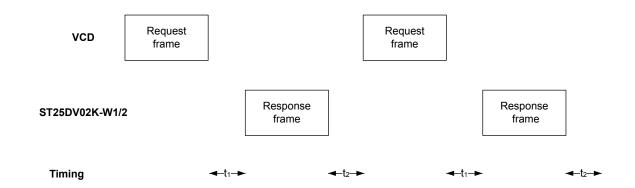

Figure 11. ST25DV02K-W1/2 protocol timing

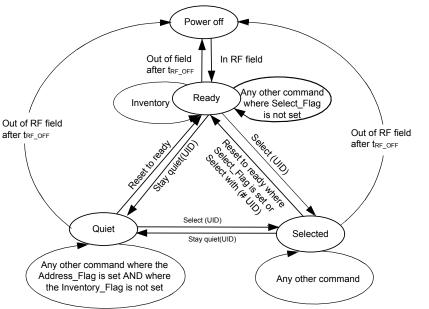

### 6.2.2 Supported states

- Power-off

- Ready

- Quiet

- Selected

Transitions between these states are specified in Figure 12. Device state transition diagram and Table 46. Device response depending on Request\_flags.

# Power-off state

The ST25DV02K-W1/2 is in RF Power-off state when it does not receive enough energy from the VCD.

### Ready state

The ST25DV02K-W1/2 is in the Ready state when it receives enough energy from the VCD. When in the Ready state, the ST25DV02K-W1/2 answers any request where the Select\_flag is not set.

### **Quiet state**

When in the Quiet state, the ST25DV02K-W1/2 answers any request with the Address\_flag set, except for Inventory requests.

#### Selected state

In the Selected state, the ST25DV02K-W1/2 answers any request in all modes (see Section 6.2.3 Modes):

- Request in Select mode with the Select\_flag set

- Request in Addressed mode if the UID matches

- Request in Non-Addressed mode as it is the mode for general requests

DS12114 - Rev 7 page 28/75

DT43017V2

| Table 46. Device response depending on Request_flags | Table 46. | Device response | depending o | n Request_fl | ags |

|------------------------------------------------------|-----------|-----------------|-------------|--------------|-----|

|------------------------------------------------------|-----------|-----------------|-------------|--------------|-----|

|                                                                                  | Add       | ress_flag     | Select_flag |              |

|----------------------------------------------------------------------------------|-----------|---------------|-------------|--------------|

| Flags                                                                            | 1         | 0             | 1           | 0            |

|                                                                                  | Addressed | Non addressed | Selected    | Non selected |

| ST25DV02K-W1/2 in Ready or Selected state (devices in Quiet state do not answer) | -         | x             | -           | ×            |

| ST25DV02K-W1/2 in Selected state                                                 | -         | X             | X           | -            |

| ST25DV02K-W1/2 in Ready, Quiet or Selected state (the device matching the UID)   | Х         | -             | -           | X            |

| Error (03h) or no response (command dependent)                                   | X         | -             | Х           | -            |

Figure 12. Device state transition diagram

The ST25DV02K-W1/2 returns to the power-off state if the tag is out of the field for at least  $t_{RF\_OFF}$ .

The intention of the state transition method is that only one ST25DV02K-W1/2 must be in the Selected state at any given time.

When the Select\_flag is set to 1, the request must NOT contain a unique ID.

When the Address\_flag is set to 0, the request must NOT contain a unique ID.

#### **6.2.3** Modes

The term "mode" refers to the mechanism used in a request to specify the set of ST25DV02K-W1/2 devices that must execute the request.

#### Addressed mode

When the Address\_flag is set to 1 (Addressed mode), the request contains the UID (unique ID) of the addressed ST25DV02K-W1/2.

Any ST25DV02K-W1/2 receiving a request with the Address\_flag set to 1 compares the received UID to its own. If it matches the device executes the request (if possible) and returns a response to the VCD as specified in the command description.

If the UID does not match the device remains silent.

DS12114 - Rev 7 page 29/75

#### Non-addressed mode (general request)

When the Address\_flag is cleared to 0 (Non-Addressed mode), the request does not contain a UID.

#### Select mode

When the Select\_flag is set to 1 (Select mode), the request does not contain a unique ID. The ST25DV02K-W1/2 in the Selected state that receives a request with the Select\_flag set to 1 executes it and returns a response to the VCD as specified in the command description.

Only the ST25DV02K-W1/2 in the Selected state answers a request where the Select\_flag is set to 1.

The system design ensures that only one ST25DV02K-W1/2 can be in the Select state at a given time.

### 6.2.4 Request format

The request consists of:

- an SOF

- flags

- a command code

- parameters and data

- a CRC

- an EOF.

#### Table 47. General request format

| SOF | Request_flags | Command code | Parameters | Data | 2 byte CRC | EOF |  |

|-----|---------------|--------------|------------|------|------------|-----|--|

|-----|---------------|--------------|------------|------|------------|-----|--|

### 6.2.5 Request flags

In a request, the "flags" field specifies the actions to be performed by the ST25DV02K-W1/2 and whether corresponding fields are present or not.

The flags field consists of eight bits. Bit 3 (Inventory\_flag) of the request flag defines the contents of the four MSBs (bits 5 to 8). When bit 3 is reset (0), bits 5 to 8 define the ST25DV02K-W1/2 selection criteria. When bit 3 is set (1), bits 5 to 8 define the ST25DV02K-W1/2 Inventory parameters.

Table 48. Definition of request flags 1 to 4

| Bit No | Flag                    | Level | Description                                                                                               |

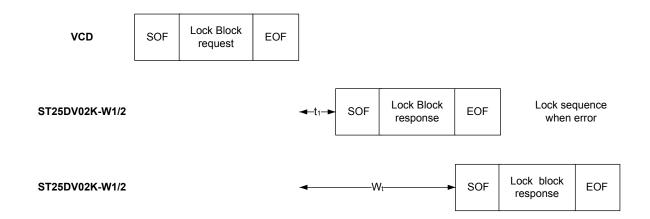

|--------|-------------------------|-------|-----------------------------------------------------------------------------------------------------------|