### **Datasheet**

Single-channel 5.7 kV (rms) isolated gate driver IC with adjustable DESAT and soft-off

### **Features**

- 650 V, 1200 V, 1700 V, 2300 V IGBTs, SiC, and Si MOSFETs

- 40 V absolute maximum output supply voltage

- ±3 A, ±6 A, and ±9 A typical sinking and sourcing peak output current

- Separate source and sink outputs for hard switching and with active Miller clamp/clamp driver

- Adjustment pins for parameter configuration from input side

- Precise V<sub>CEsat</sub> detection (DESAT) with fault output and adjustable filter time and leading edge blanking time with resistor at ADJB pin

- Adjustable IGBT soft turn-off after desaturation detection with resistor at ADJA pin

- Operation at high ambient temperature up to 125 °C with over-temperature shut down at 160 °C (±10 °C)

- Tight IC-to-IC propagation delay matching ( $t_{PDD,max} = 30 \text{ ns}$ )

- Undervoltage lockout protection with hysteresis for input and output side with active shut-down

- High common-mode transient immunity CMTI = 200 kV/μs

- Small space-saving DSO-16 fine-pitch package with large creepage distance (>8 mm)

- Safety certification

- UL 1577 recognized (File E311313) with  $V_{ISO,test}$  = 6840 V (rms) for 1 s,  $V_{ISO}$  = 5700 V (rms) for 60 s

- VDE 0884-11 approval (Certificate no. 40053980) with  $V_{IORM}$  = 1767 V (peak, reinforced)

- Evaluation board available EVAL-1ED3491MX12M

## **Potential applications**

- Industrial motor drives compact, standard, premium, servo drives

- Solar inverters

- · UPS systems

- Welding

- Commercial and agricultural vehicles (CAV)

- Commercial air-conditioning (CAC)

- High-voltage isolated DC-DC converters

- Isolated switch mode power supplies (SMPS)

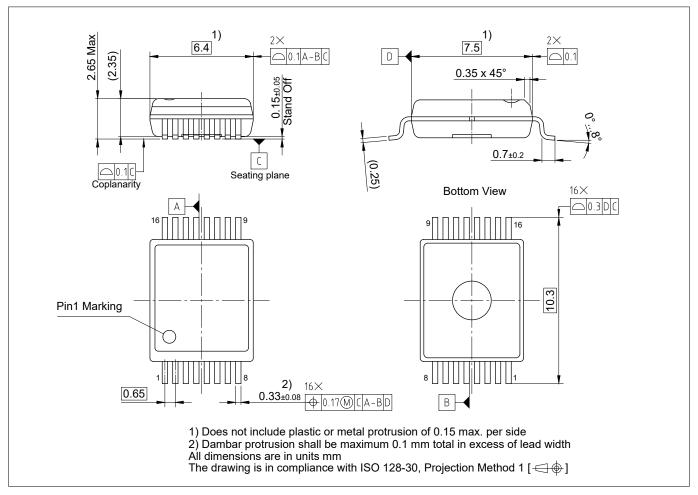

PG-DSO-16

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

**Device information**

### **Device information**

| Product type | Output current | CLAMP type <sup>1)</sup> | Isolation class | Marking  | OPN               |

|--------------|----------------|--------------------------|-----------------|----------|-------------------|

| 1ED3431MC12M | 3 A (typ)      | CLAMP                    | reinforced      | 3431MC12 | 1ED3431MC12MXUMA1 |

| 1ED3461MC12M | 6 A (typ)      | CLAMPDRV                 | reinforced      | 3461MC12 | 1ED3461MC12MXUMA1 |

| 1ED3491MC12M | 9 A (typ)      | CLAMPDRV                 | reinforced      | 3491MC12 | 1ED3491MC12MXUMA1 |

| 1ED3431MU12M | 3 A (typ)      | CLAMP                    | UL 1577         | 3431MU12 | 1ED3431MU12MXUMA1 |

| 1ED3461MU12M | 6 A (typ)      | CLAMPDRV                 | UL 1577         | 3461MU12 | 1ED3461MU12MXUMA1 |

| 1ED3491MU12M | 9 A (typ)      | CLAMPDRV                 | UL 1577         | 3491MU12 | 1ED3491MU12MXUMA1 |

<sup>1)</sup> Please refer to Chapter 4.5.4.1 for circuit connection to avoid damage to the gate driver IC

## **Description**

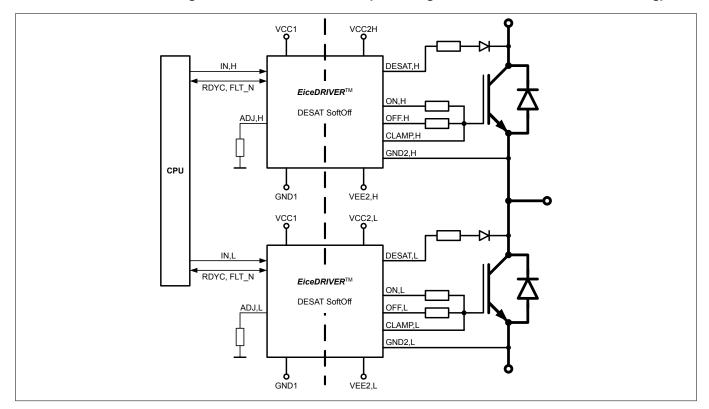

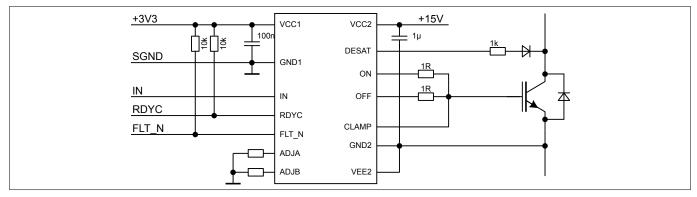

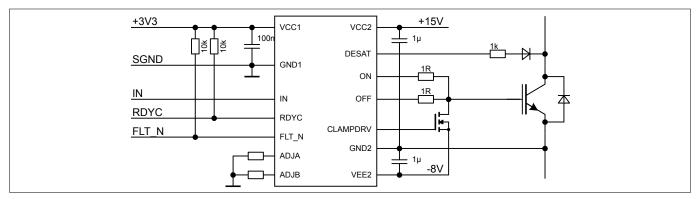

The 1ED34x1Mc12M family (X3 Analog) consists of galvanically isolated single channel gate driver ICs in a small PG-DSO-16 package with a large creepage and clearance of 8 mm. The gate driver ICs provide a typical peak output current of 3 A, 6 A, and 9 A.

Adjustable control and protection functions are included to simplify the design of highly reliable systems. All parameter adjustments are done from the input side, including adjustable DESAT filter time, leading edge blanking time, and soft-off current level with only two resistors..

All logic I/O pins are supply voltage dependent 3.3 V or 5 V CMOS compatible and can be directly connected to a microcontroller.

The data transfer across the galvanic isolation is realized by the integrated coreless transformer technology.

Figure 1 Typical application

### **Table of contents**

|            | Table of contents                                                | 3  |

|------------|------------------------------------------------------------------|----|

| 1          | Block diagram                                                    | 5  |

| 2          | Related products                                                 | 6  |

| 3          | Pin configuration and functionality                              |    |

| 3.1<br>3.2 | Pin configuration                                                |    |

| 4          | Functional description                                           | 11 |

| 4.1        | Start-up and fault clearing                                      | 11 |

| 4.2        | Supply                                                           | 12 |

| 4.2.1      | Input side undervoltage lockout, VCC1 UVLO                       | 13 |

| 4.2.2      | Output side under-voltage lockout, VCC2 UVLO                     | 13 |

| 4.3        | Input side logic                                                 | 15 |

| 4.3.1      | IN non-inverting driver input                                    | 15 |

| 4.3.2      | RDYC ready status output, fault-off and fault clear input        | 15 |

| 4.3.2.1    | RDYC fault-off input                                             | 15 |

| 4.3.2.2    | RDYC fault clear input                                           | 16 |

| 4.3.3      | FLT_N status output and fault-off input                          | 16 |

| 4.3.3.1    | FLT_N fault-off input                                            | 16 |

| 4.4        | Desaturation protection                                          | 18 |

| 4.4.1      | DESAT behavior                                                   | 18 |

| 4.4.2      | DESAT filter and leading edge blanking time adjustment with ADJB | 19 |

| 4.5        | Gate driver output                                               | 21 |

| 4.5.1      | Turn-on behavior                                                 | 22 |

| 4.5.2      | Turn-off and fault turn-off behavior                             | 22 |

| 4.5.2.1    | Hard switching turn-off                                          | 22 |

| 4.5.2.2    | Soft turn-off                                                    | 22 |

| 4.5.2.2.1  | Soft-off current source adjustment with ADJA                     |    |

| 4.5.3      | Active shut-down                                                 |    |

| 4.5.4      | Active Miller clamp                                              |    |

| 4.5.4.1    | CLAMP output types                                               |    |

| 4.5.5      | Switch-off timeout until forced switch-off                       |    |

| 4.6        | Short circuit clamping                                           | 26 |

| 5          | Electrical parameters                                            | 28 |

| 5.1        | Absolute maximum ratings                                         | 28 |

| 5.2        | Thermal parameters                                               | 29 |

| 5.3        | Operating parameters                                             | 29 |

| 5.4        | Electrical characteristics                                       | 31 |

| 5.4.1      | Voltage supply                                                   | 31 |

|            |                                                                  |    |

# **EiceDRIVER**<sup>™</sup> **1ED34x1Mc12M Enhanced Datasheet**

### **Table of contents**

| 5.4.2 | Logic input and output                                                              | 32 |

|-------|-------------------------------------------------------------------------------------|----|

| 5.4.3 | Analog input                                                                        |    |

| 5.4.4 | Gate driver                                                                         | 34 |

| 5.4.5 | Active Miller clamp                                                                 | 35 |

| 5.4.6 | Dynamic characteristics                                                             | 36 |

| 5.4.7 | Desaturation protection                                                             | 37 |

| 5.4.8 | Soft-off current source                                                             | 39 |

| 5.4.9 | Over-temperature protection                                                         | 40 |

| 6     | Insulation characteristics                                                          | 41 |

| 6.1   | Certified according to VDE 0884-11 reinforced insulation (Certificate no. 40053980) | 41 |

| 6.2   | Recognized under UL 1577 (File E311313)                                             | 42 |

| 7     | Package information                                                                 | 43 |

| 8     | Application notes                                                                   | 44 |

| 8.1   | Reference layout for thermal data                                                   | 44 |

| 8.2   | Printed circuit board guidelines                                                    | 44 |

|       | Revision history                                                                    | 44 |

|       | Disclaimer                                                                          | 45 |

### **Datasheet**

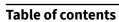

1 Block diagram

### **Block diagram** 1

Figure 2 **Block diagram**

### **Datasheet**

#### **Related products** 2

Note:

Please consider the gate driver IC power dissipation and insulation requirements for the selected power switch and operating condition.

| Product group            | Product name      | Description                                                                          |  |  |  |  |

|--------------------------|-------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| TRENCHSTOP™              | IKQ75N120CS6      | High Speed 1200 V, 75 A IGBT with anti-parallel diode in TO247-3                     |  |  |  |  |

| IGBT Discrete            | IKW15N120BH6      | High Speed 1200 V, 15 A IGBT with anti-parallel diode in TO247                       |  |  |  |  |

|                          | IHW40N120R5       | Reverse conducting 1200 V, 40 A IH IGBT with integrated diode in TO247               |  |  |  |  |

| CoolSiC <sup>™</sup> SiC | IMBF170R650M1     | 1700 V, 650 mΩ SiC MOSFET in TO263-7 package                                         |  |  |  |  |

| MOSFET Discrete          | IMBG120R045M1H    | 1200 V, 45 mΩ SiC MOSFET in TO263-7 package                                          |  |  |  |  |

|                          | IMZ120R350M1H     | 1200 V, 350 mΩ SiC MOSFET in TO247-4 package                                         |  |  |  |  |

| CoolSiC <sup>™</sup> SiC | FS45MR12W1M1_B11  | EasyPACK <sup>™</sup> 1B 1200 V / 45 mΩ sixpack module                               |  |  |  |  |

| MOSFET Module            | FF23MR12W1M1_B11  | EasyDUAL <sup>™</sup> 1B 1200 V, 23 mΩ half-bridge module                            |  |  |  |  |

|                          | FF6MR12W2M1_B11   | EasyDUAL <sup>™</sup> 2B 1200 V, 6 mΩ half-bridge module                             |  |  |  |  |

|                          | F3L11MR12W2M1_B74 | EasyPACK <sup>™</sup> 2B 1200 V, 11 mΩ 3-Level module in Advanced NF (ANPC) topology |  |  |  |  |

|                          | F4-23MR12W1M1_B11 | EasyPACK <sup>™</sup> 1B 1200 V, 23 mΩ fourpack module                               |  |  |  |  |

| TRENCHSTOP <sup>™</sup>  | F4-100R17N3E4     | EconoPACK <sup>™</sup> 3 1700 V, 100 A fourpack IGBT module                          |  |  |  |  |

| IGBT Modules             | F4-200R17N3E4     | EconoPACK <sup>™</sup> 3 1700 V, 200 A fourpack IGBT module                          |  |  |  |  |

|                          | FS150R17N3E4      | EconoPACK <sup>™</sup> 3 1700 V, 150 A sixpack IGBT module                           |  |  |  |  |

|                          | FF650R17IE4       | PrimePACK <sup>™</sup> 3 1700 V, 650 A half-bridge dual IGBT module                  |  |  |  |  |

|                          | FF1000R17IE4      | PrimePACK <sup>™</sup> 3 1700 V, 1000 A half-bridge dual IGBT module                 |  |  |  |  |

|                          | FF1200R17IP5      | PrimePACK <sup>™</sup> 3+ 1700 V, 1200 A dual IGBT module                            |  |  |  |  |

|                          | FF1500R17IP5      | PrimePACK <sup>™</sup> 3+ 1700 V, 1500 A dual IGBT module                            |  |  |  |  |

|                          | FF1500R17IP5R     | PrimePACK <sup>™</sup> 3 1700 V, 1500 A dual IGBT module                             |  |  |  |  |

|                          | FF1800R17IP5      | PrimePACK <sup>™</sup> 3+ 1700 V, 1800 A dual IGBT module                            |  |  |  |  |

|                          | FP10R12W1T7_B11   | EasyPIM <sup>™</sup> 1B 1200 V, 10 A three phase input rectifier PIM IGBT module     |  |  |  |  |

|                          | FS100R12W2T7_B11  | EasyPACK <sup>™</sup> 2B 1200 V, 100 A sixpack IGBT module                           |  |  |  |  |

|                          | FP150R12KT4_B11   | EconoPIM <sup>™</sup> 3 1200V three-phase PIM IGBT module                            |  |  |  |  |

|                          | FS200R12KT4R_B11  | EconoPACK <sup>™</sup> 3 1200 V, 200 A sixpack IGBT module                           |  |  |  |  |

### **Datasheet**

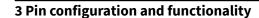

# 3 Pin configuration and functionality

The pin assignment at the gate driver IC generally differentiates between the input side and the output side.

### Table 1 General pin assignment

| Pins    | Designation                                              |

|---------|----------------------------------------------------------|

| 1 to 8  | input side, input logic signal side, or low voltage side |

| 9 to 16 | output side, driver power side, or high voltage side     |

For simplicity reasons the driver is described as an IGBT driver. For use with MOSFETs and other power switches simply replace any mentioning of collector and emitter with their corresponding pin names.

### 3.1 Pin configuration

Table 2 Pin configuration table abbreviations

| Abbreviation | Description                                               |

|--------------|-----------------------------------------------------------|

| Pin type     |                                                           |

| PWR          | Power supply and gate current output pins                 |

| I/O          | Digital input and output pin                              |

| I            | Digital input pin                                         |

| GND          | Ground reference pin                                      |

| Al           | Analog input pin                                          |

| Buffer type  |                                                           |

| OD           | Open drain output                                         |

| CMOS         | CMOS compatible input threshold levels                    |

| PP           | Push/pull output buffer                                   |

| special      | Special output/input function, see individual description |

| Pull device  |                                                           |

| PD           | Pull-down resistor                                        |

| CS           | Current source                                            |

### Table 3 Pin configuration

| Pin<br>no. | Pin name | Pin type | Buffer type | Pull<br>device | Function                                                                                |  |  |

|------------|----------|----------|-------------|----------------|-----------------------------------------------------------------------------------------|--|--|

| 1          | GND1     | GND      | _           | _              | Ground input side                                                                       |  |  |

| 2          | VCC1     | PWR      | _           | _              | Positive power supply input side                                                        |  |  |

| 3          | ADJA     | Al       | special     | CS             | Parameter adjust set A                                                                  |  |  |

| 4          | ADJB     | Al       | special     | CS             | Parameter adjust set B                                                                  |  |  |

| 5          | RDYC     | I/O      | OD, CMOS    | -              | Combined ready output, high active and fault clear input and soft-off input, low active |  |  |

| 6          | FLT_N    | I/O      | OD, CMOS    | _              | Fault output, low active and soft- off input, low active                                |  |  |

| 7          | IN       | I        | CMOS        | PD, 40 kΩ      | Non inverted driver input                                                               |  |  |

### 3 Pin configuration and functionality

(continued) Pin configuration Table 3

| Pin<br>no. | Pin name | Pin type | Buffer type | Pull<br>device | Function                                                                      |  |  |

|------------|----------|----------|-------------|----------------|-------------------------------------------------------------------------------|--|--|

| 8          | GND1     | GND      | _           | _              | Ground input side                                                             |  |  |

| 9          | VEE2     | GND      | -           | -              | Negative power supply output side                                             |  |  |

| 10         | CLAMP    | PWR      | OD          | -              | Active Miller clamping, open drain to VEE2 (1ED3431M only)                    |  |  |

| 10         | CLAMPDRV | PWR      | PP          | -              | Active miller clamping, clamp driver for external MOSFET (1ED3461M, 1ED3491M) |  |  |

| 11         | OFF      | PWR, AI  | OD          | _              | Driver sink output                                                            |  |  |

| 12         | ON       | PWR, AI  | OD          | _              | Driver source output                                                          |  |  |

| 13         | DESAT    | Al       | special     | CS, 500 μA     | Enhanced desaturation protection                                              |  |  |

| 14         | VCC2     | PWR      | -           | _              | Positive power supply output side                                             |  |  |

| 15         | GND2     | Al       | -           | _              | Signal ground output side                                                     |  |  |

| 16         | VEE2     | GND      | _           | _              | Negative power supply output side                                             |  |  |

|   | Го    |       | 1  |

|---|-------|-------|----|

| 1 | GND1  | VEE2  | 16 |

| 2 | VCC1  | GND2  | 15 |

| 3 | ADJA  | VCC2  | 14 |

| 4 | ADJB  | DESAT | 13 |

| 5 | RDYC  | ON    | 12 |

| 6 | FLT_N | OFF   | 11 |

| 7 | IN    | CLAMP | 10 |

| 8 | GND1  | VEE2  | 9  |

| l |       |       | J  |

PG-DSO-16 (top view) with CLAMP Figure 3

Figure 4 PG-DSO-16 (top view) with CLAMPDRV

#### **Datasheet**

3 Pin configuration and functionality

### 3.2 Pin functionality

#### GND1

Reference ground of the input side. Connect direct to input signal ground.

#### VCC1

Positive power supply terminal of the input side, connect to 5 V or 3.3 V for proper operation. Place a decoupling capacitor close to this pin and *GND1*.

### ADJA and ADJB parameter adjust input for set A or B

The pins ADJA and ADJB are used to adjust two sets of independent parameters of output functions.

Connect a resistor between 1.33 k $\Omega$  and 28.0 k $\Omega$  to GND1 to adjust each parameter. All valid resistor values belong to the E96-series with 1% tolerance.

Connecting ADJA to GND1 uses a default value for soft switch-off. Connecting it to VCC1 is disabling the gate driver IC.

Connecting ADJB to GND1 is disabling the gate driver IC. Connecting it to VCC1 is setting the function to minimum values.

### RDYC ready status output, fault-off input and fault-clear input

Open-drain output reports the correct operation of the device, ready output is high active. Fault-clear input and fault-off input clears a gate driver fault or switch the gate driver output to off with fault-off function, input is low active. Connect to a microcontroller with 5 V or 3.3 V I/O with an external pull-up resistor to VCC1. A typical value for this resistor is 2.2 k $\Omega$ . The RDCY signal is referenced to GND1.

### FLT\_N fault output and fault-off input

Open-drain output reports the failures related to operating of the inverter system to the microcontroller, fault output is active low. Fault-off input switch the gate driver output to off with fault-off function, input is low active. Connect to a microcontroller with 5 V or 3.3 V I/O with an external pull-up resistor to VCC1. A typical value for this resistor is  $2.2 \text{ k}\Omega$ . The  $FLT_N$  signal is referenced to GND1.

### IN non inverting gate driver input

*IN* input controls the output of the gate driver IC, the IGBT is turned on if *IN* is set to high. Connect to a PWM output of the microcontroller with 5 V or 3.3 V IO. An internal pull-down resistor ensures IGBT off-state if not connected. A minimum pulse width of typical 103 ns is defined to make the gate driver IC robust against glitches at *IN*.

#### VEE2

Negative power supply terminal of the output side. Connect to a voltage of 0 V to -25 V referenced to *GND2* for proper operation. Place a decoupling capacitor close to the following pins:

- VCC2 and VEE2

- GND2 and VEE2

If no negative supply voltage is used, all VEE2 pins have to be connected to GND2.

### CLAMP Miller clamp output, CLAMPDRV Miller clamp pre-driver output

*CLAMP*: High-current clamp output to hold the gate voltage low during collector-emitter-voltage rise. Connect directly to the gate of the IGBT.

*CLAMPDRV*: Clamp pre-driver output for the use of an external clamp switch. Connect directly to the gate of a n-channel MOSFET.

#### **Datasheet**

### 3 Pin configuration and functionality

### **OFF** driver output

High-current driver sink output to discharge the gate of the external IGBT. The gate driver IC also sinks the Soft-off current at this pin. Connect to the gate of the IGBT via a chosen turn-off gate resistor.

### **ON** driver output

High-current driver source output to charge the gate of the external IGBT and turn it on and sense input for the CLAMP function. Connect to the gate of the IGBT via a chosen turn-on gate resistor.

### **DESAT** enhanced desaturation detection input

Desaturation detection input to monitor the IGBT collector-emitter voltage ( $V_{CE}$ ) to detect desaturation caused by short circuit events. Connect to the collector of the driven IGBT via a series connection of a protection resistor and a high-voltage diode. The *DESAT* signal is referenced to *GND2*.

### VCC2

Positive power supply terminal of the output side. Connect to sufficient supply voltage referenced to *GND2* for proper operation. Place a decoupling capacitor close to the following pins:

- VCC2 and VEE2

- VCC2 and GND2

### **GND2** reference ground

Reference ground of the output side. Connect to common voltage of a bipolar supply and the emitter of the IGBT. Place a decoupling capacitor close to the following pins:

- VCC2 and GND2

- GND2 and VEE2

#### **Datasheet**

### 4 Functional description

### 4 Functional description

The 1ED34x1Mc12M family (X3 Analog) consists of galvanically isolated single channel gate driver ICs with adjustable feature parametrization by two simple resistors. All adjustments can be done from the low voltage input side.

To start-up the gate driver IC for normal operation both input and output sides of the gate driver IC need to be powered.

The 1ED34x1Mc12M family (X3 Analog) is designed to support various supply configurations on the input and output side. On the output side unipolar and bipolar supply is possible.

The output stage is realized as rail-to-rail. There the gate driver voltage follows the supply voltage without an additional voltage drop. In addition it provides an easy clamping of the gate voltage during short circuit of an external IGBT.

The *RDYC* status output reports correct operation of the gate driver IC like sufficient voltage supply. The *FLT\_N* status output reports failures in the application like desaturation detection.

To ensure safe operation the gate driver IC is equipped with an input and output side under-voltage lockout circuit. The UVLO levels are optimized for IGBTs.

The desaturation detection circuit protects the external IGBT from destruction at a short circuit. The gate driver IC reacts on a DESAT fault by turning off the IGBT with the adjustable soft-off method.

The soft turn-off function is used to switch-off the external IGBT in overcurrent conditions in a soft-controlled manner to protect the IGBT against collector emitter over-voltages.

An active Miller clamp function protects the IGBT from parasitic turn-on in fast switching applications.

### 4.1 Start-up and fault clearing

For normal operation both input and output sides of the gate driver IC need to be powered. A low level at the FLT\_N pin always indicates a fault condition. In this case the IC starts internal mechanisms for fault clearing.

### Input side start-up

- 1. Voltage at VCC1 reaches the input UVLO threshold: input side of gate driver IC starts operating

- **2.** *FLT\_N* follows input supply voltage

- 3. Records resistor programmable function from ADJA and ADJB

- **4.** Waits until output side is powered

- 5. Initiates internal start-up: Transfers configured values to output side

- **6.** Performs internal self-test

The start-up delay takes approx. 200  $\mu$ s and is part of the complete start-up time  $t_{START1}$ .

#### **Output side start-up**

- 1. Voltage at VCC2 reaches the output UVLO threshold: output side of gate driver IC starts operating

- 2. Activates OFF gate driver output: connected gate stays discharged

- **3.** Waits until input side is powered

- **4.** Initiates internal start-up: Receives configured values from input side

- **5.** Performs internal self-test

The start-up delay takes approx. 200  $\mu$ s and is part of the complete start-up time  $t_{\mathsf{START2}}$ .

The gate driver IC releases *RDYC* to high to signal a successful start-up and its readiness to operate. The gate driver IC will follow the status of the *IN* signal.

### Clearing a fault with RDYC to low cycle

- **1.** Set *IN* to low

- **2.** Set *RDYC* to low for a duration longer than the fault clear time  $t_{CLRMIN}$

#### **Datasheet**

### 4 Functional description

- 3. Release RDYC to high

- If the source of the fault is no longer present, FLT\_N is released to high

- If another fault source is active, FLT\_N stays low and the cycle needs to be repeated

- 4. Continue PWM operation

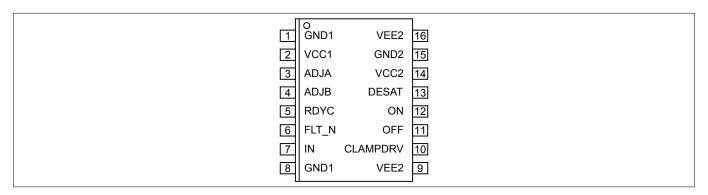

#### 4.2 Supply

The 1ED34x1Mc12M family (X3 Analog) is designed to support various supply configurations. The input side can be used with a 3.3 V or 5 V supply.

The output side requires either an unipolar supply (VEE2 = GND2) or a bipolar supply.

- Individual supply voltages between VCC2 and GND2 or GND2 and VEE2 shall not exceed 25 V.

- The total supply voltage between VCC2 and VEE2 shall not exceed 35 V.

To ensure safe operation of the gate driver IC, it is equipped with an input and output side undervoltage lockout circuit.

### **Unipolar supply**

In unipolar supply configuration the gate driver IC is typically supplied with a positive voltage of 15 V at VCC2. GND2 and VEE2 are connected together and this common potential is connected to the IGBT emitter.

Application example with unipolar supply (1ED3431M) Figure 5

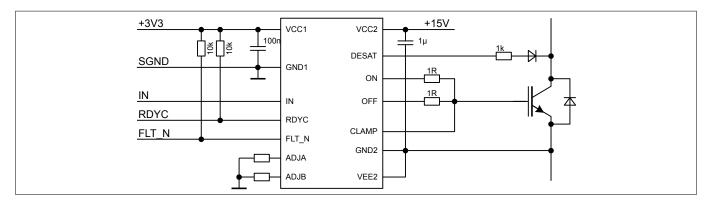

### **Bipolar supply**

For bipolar supply the gate driver IC is typically supplied with a positive voltage of 15 V at VCC2 and a negative voltage of -8 V or -15 V at VEE2 relative to GND2.

Between VCC2 and VEE2 the maximum potential difference is 35 V.

Application example with bipolar supply (1ED3431M) Figure 6

Negative supply prevents a parasitic turn-on due to the additional voltage margin to the gate turn-on threshold.

#### **Datasheet**

### 4 Functional description

### VEE2 over GND2 supply connection check

The gate driver IC has a built-in connection check for VEE2. A loss of VEE2 connection will be detected and signaled via RDYC.

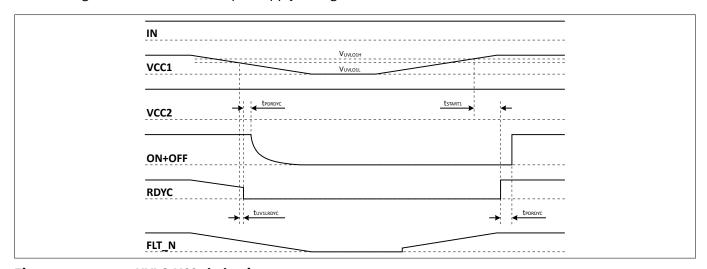

### 4.2.1 Input side undervoltage lockout, VCC1 UVLO

To ensure correct operation of the input side and safe operation of the application the gate driver IC is equipped with an input supply undervoltage lockout for *VCC1*.

UVLO behavior during start-up:

- **1.** The voltage at the supply terminal VCC1 reaches the  $V_{UVLO1H}$  threshold

- 2. The gate driver IC reads the ADJA and ADJB resistor values and transfers the configuration to the output side

- **3.** The IC releases the *RDYC* output to **high** and is ready to operate.

The start-up delay takes approx. 200  $\mu$ s and is part of the complete start-up time  $t_{\text{START1}}$ .

UVLO behavior during shut-down:

If the supply voltage V<sub>VCC1</sub> of the input side drops below V<sub>UVLO1L</sub> the RDYC signal is switched to low and the

output will be switched off.

The fault signal *FLT\_N* follows the input supply voltage.

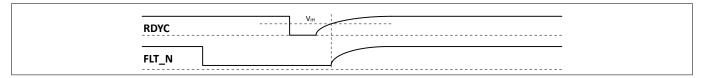

Figure 7 UVLO VCC1 behavior

### 4.2.2 Output side under-voltage lockout, VCC2 UVLO

To ensure correct operation of the output side and safe operation of the IGBT in the application, the gate driver IC is equipped with an output supply undervoltage lockout for VCC2 versus GND2.

UVLO behavior during start-up:

If the voltage at the supply terminal VCC2 reaches the V<sub>UVLO2H</sub> threshold the RDYC output is released to high

and the gate driver IC is ready to operate.

The start-up delay takes approx. 200  $\mu$ s and is part of the complete start-up time  $t_{\mathsf{START2}}$ .

UVLO behavior during shut-down:

If the supply voltage V<sub>VCC2</sub> of the output side drops below V<sub>UVLO2L</sub> the RDYC signal is switched to low and the

output will be switched off.

### **Datasheet**

### **4 Functional description**

Figure 8 **UVLO VCC2** behavior

Any  $V_{\text{UVLO2L}}$  event will lead to a fault-off and a RDYC low level. Depending of the level of the voltage drop, the gate driver IC either stays in a not ready state and waits for the supply voltage to recover, or it will fully reset the gate driver IC. Both variants differ in the necessary delay of RDYC release after the supply voltage has recovered. After a reset, the gate driver IC needs to fully restart until it becomes ready again.

#### **Datasheet**

### 4 Functional description

### 4.3 Input side logic

The input threshold levels are always CMOS compliant. The threshold levels are 30% of *VCC1* for low level and 70% of *VCC1* for high level.

The 1ED34x1Mc12M family (X3 Analog) has three input pins (*IN*, *ADJA*, *ADJB*) and two I/O pins (*RDYC*, *FLT\_N*) at the input side.

### 4.3.1 IN non-inverting driver input

The input pin has a positive logic. To turn on the associated IGBT apply a logic high signal at the *IN* pin. A minimum pulse width of typical 103 ns is defined to make the IC robust against glitches at *IN*.

### 4.3.2 RDYC ready status output, fault-off and fault clear input

The RDYC pin is a logic input and open drain output and has three different functions:

- RDYC as ready status output of all ready sources

- RDYC as fault-off input

- RDYC as fault clear input

In a typical application the *RDYC* pins of all gate driver ICs in the inverter are connected together and form a single wire *RDYC* signal.

An external pull-up resistor is required to ensure RDYC status output during operation.

### **Ready sources**

- the input side is properly supplied, VCC1 supply above UVLO1 threshold

- the output side is properly supplied with a positive voltage, VCC2 supply above UVLO2 threshold

- no VEE2 over GND2 failure

- Internal signal transmission is operating nominal

- the ON pin monitoring of the gate driver is below VEE2 + 2 V, IGBT has to be off at start-up

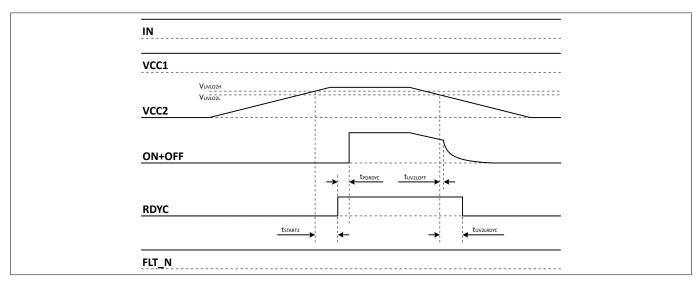

### 4.3.2.1 RDYC fault-off input

Pulling *RDYC* to low disables the operation of the gate driver IC. The gate driver IC ignores *IN* signals as long as the *RDYC* pin stays low and the IC uses its fault-off function to switch-off the IGBT.

The defined minimum pulse width makes the IC robust against glitches at *RDYC*. The gate driver ignores pulses with a shorter duration.

Figure 9 RDYC short pulse behavior of external manipulation of the RDYC pin

After an external *RDYC* low signal the IC is actively pulling *RDYC* to low until the voltage at *ON* pin falls below the *VEE2*+2 V threshold.

The RDYC fault-off input is active low.

#### **Datasheet**

### 4 Functional description

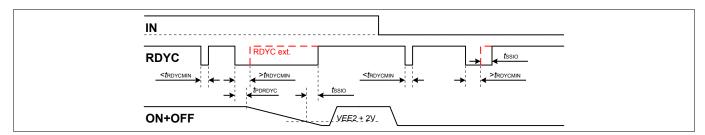

### 4.3.2.2 RDYC fault clear input

Setting *RDYC* to low for longer than the fault clear time  $t_{\text{CLRMIN}}$  will reset the stored fault signal at pin *FLT\_N* with the rising edge of *RDYC*. Additionally the following conditions have to be met as well:

- PWM IN pin level needs to be low,

- voltage at ON pin has dropped below the VEE2+2 V threshold, and

- triggering fault condition is no longer present.

The typical fault clear time  $t_{CLRMIN}$  is 1.0 µs.

Figure 10 RDYC fault clear timing

Figure 11 RDYC fault clear rising edge to FLT\_N

### 4.3.3 FLT\_N status output and fault-off input

The FLT\_N pin is a logic input and open drain output and has two different functions:

- FLT\_N as fault-status output for fault sources

- FLT\_N as fault-off input

In a typical application the *FLT\_N* pins of all gate driver ICs in the inverter are connected together and form a single wire *FLT\_N* signal.

An external pull-up-resistor is required to ensure FLT\_N status output during operation.

### **Fault sources**

The following fault sources can trigger a FLT\_N pin to low and initiate a fault turn-off:

- · desaturation detection of IGBT

- gate driver over temperature protection

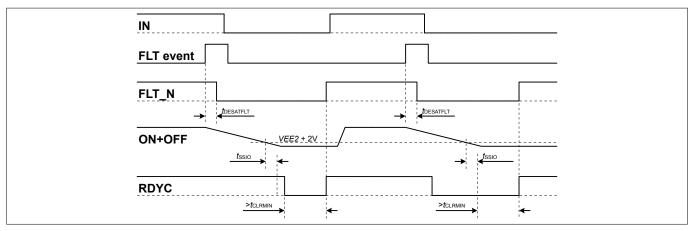

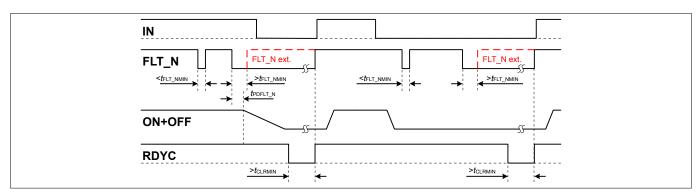

### 4.3.3.1 *FLT\_N* fault-off input

Pulling *FLT\_N* to low disables the operation of the gate driver IC. The gate driver IC ignores *IN* signals as long as the *FLT\_N* pin stays low and the IC uses its fault-off function to switch-off the IGBT.

The defined minimum pulse width makes the gate driver IC robust against glitches at FLT N.

After a low at the FLT\_N pin either internally or externally applied, the fault event is latched until cleared.

1.10

### **Datasheet**

# infineon

### **4 Functional description**

The FLT\_N fault-off input is active low.

Figure 12 FLT\_N short pulse behavior of external manipulation of the FLT\_N pin cleared by RDYC

#### **Datasheet**

### 4 Functional description

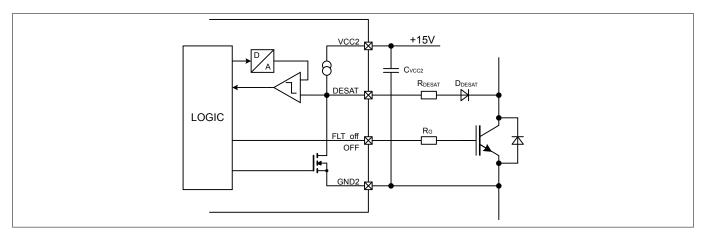

### 4.4 Desaturation protection

The desaturation detection circuit protects the external IGBT from destruction at a short circuit. The desaturation protection follows the given sequence:

- 1. Voltage at DESAT pin reaches DESAT threshold level, for a period of time exceeding the filter time

- 2. Gate driver IC output switches the external IGBT off, using the soft-off method

- **3.** Gate driver IC switches FLT\_N pin to low to indicate the fault to a connected microcontroller

- 4. Short circuit situation is resolved

- after the voltage at the ON pin has dropped below the VEE2+2 V threshold,

- no other fault condition is present,

- the input has been turned off and

- the fault has been cleared using the RDYC low cycle method

Figure 13 DESAT circuit (only relevant pins shown)

The 1ED34x1Mc12M family (X3 Analog) has a fixed DESAT threshold level of typical 9.18 V. If lower threshold levels are required, the DESAT resistor can be increased. Larger DESAT resistor values lead to lower DESAT threshold voltages. The threshold voltage reduction is equal to the DESAT current multiplied by the DESAT resistance.

The high-precision internal current source results in a minimum impact on the DESAT detection variation.

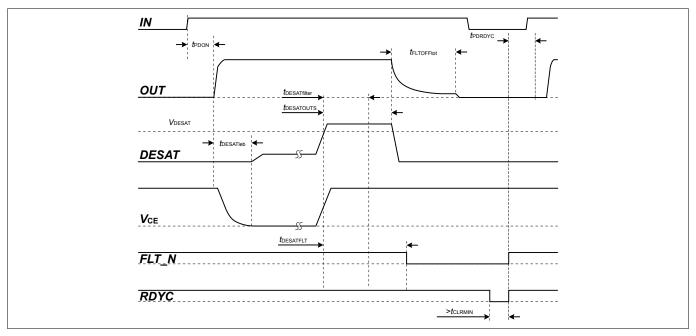

### 4.4.1 DESAT behavior

The DESAT function offers a leading edge blanking time and filters to optimize the DESAT detection for application usage.

The leading edge blanking inhibits threshold detection during an IGBT turn on phase. The typical IGBT turn on behavior starts with charging of the gate, commutation of the application load current and finally  $V_{CE}$  voltage decrease to  $V_{CEsat}$  voltage levels. To prevent the gate driver IC from detecting a false DESAT event, leading edge blanking pauses the DESAT circuit until the time  $t_{DESATleb}$  has elapsed.

Following the leading edge blanking time, the gate driver IC forces the DESAT current into the external DESAT circuit. The current typically flows through a protection resistor, a fast high voltage diode and the collector-emitter path of the IGBT. The resulting voltage at the *DESAT* pin is the sum of the voltage drop across this path.

During a short circuit condition, the  $V_{CE}$  voltage increases, resulting in a reverse polarity condition of the DESAT diode. The remaining DESAT current also increases the voltage level at the *DESAT* pin and triggers the DESAT threshold. If the pin voltage level stays above the threshold for the duration of the DESAT filter time  $t_{DESATfilter}$ , the gate driver IC registers the DESAT event and acts accordingly.

### **Datasheet**

### 4 Functional description

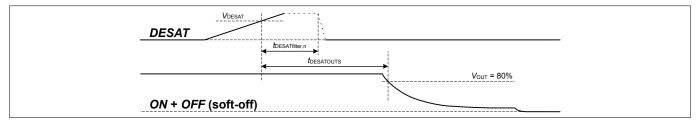

The internal processing time after DESAT threshold crossing, filtering and beginning of fault-off is defined as  $t_{\mathsf{DESATOUT}}$ . The duration of the gate discharge during fault-off is defined as  $t_{\mathsf{FLTOFFtot}}$  and is depending on the soft-off function and the gate load.

Figure 14 DESAT timing with leading edge blanking, filter and reaction times

#### 4.4.2 DESAT filter and leading edge blanking time adjustment with ADJB

The ADJB pin configures the DESAT leading edge blanking time and DESAT filter time:

- A resistor from ADJB to GND1 sets the DESAT leading edge blanking time and the DESAT filter time used during DESAT detection

- Use resistors from the E96 resistor-series with 1% tolerance values to achieve accurate parameter configuration

- The gate driver IC reads the resistor value once during start-up

- Connecting ADJB to GND1 inhibits the gate driver operation and stops the start-up sequence

- Connecting ADJB to VCC1 disables the filtering resulting in minimum response times

Table 4 **DESAT filter timing ADJB adjustment**

| DESAT filter time set up      | stopped                         | 0       | 1       | 2       | 3       | 4       | 5       | 6       | 7       |

|-------------------------------|---------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Resistance at ADJB to GND1    | < 1.05 kΩ or tied to GND1       | 1.33 kΩ | 1.58 kΩ | 1.91 kΩ | 2.26 kΩ | 2.74 kΩ | 3.32 kΩ | 4.02 kΩ | 4.87 kΩ |

| typ. t <sub>DESATleb</sub>    | inhibit                         | 650 ns  |

| typ. t <sub>DESATfilter</sub> | gate<br>driver<br>operatio<br>n | 1575 ns | 1775 ns | 1975 ns | 2375 ns | 2775 ns | 3175 ns | 3575 ns | 3975 ns |

### **Datasheet**

### 4 Functional description

### Table 4 DESAT filter timing ADJB adjustment

| DESAT filter time set up      | 8       | 9       | 10      | 11      | 12      | 13      | 14      | 15      | default                               |

|-------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------------------------|

| Resistance at ADJB to GND1    | 5.90 kΩ | 7.15 kΩ | 8.66 kΩ | 10.7 kΩ | 13.7 kΩ | 17.4 kΩ | 23.2 kΩ | 28.0 kΩ | >45.3 kΩ<br>or tied<br>to <i>VCC1</i> |

| typ. t <sub>DESATleb</sub>    | 1150 ns | 400 ns                                |

| typ. t <sub>DESATfilter</sub> | 3975 ns | 3575 ns | 3175 ns | 2775 ns | 2375 ns | 1975 ns | 1775 ns | 1575 ns | 225 ns                                |

**4 Functional description**

# **Datasheet**

### **Gate driver output** 4.5

The gate driver output side uses MOSFETs to provide a rail-to-rail output. Therefore, the gate drive voltage follows the supply voltage closely.

Due to the low internal voltage drop, the switching behavior of the IGBT is predominantly governed by the external gate resistor. The gate driver IC offers separate sink and source outputs to adapt the gate resistor for turn-on and turn-off separately without additional bypass components.

The cell value x in the following table is placeholder for high or low and indicates that this pin does not influence the resulting gate driver output state. The arrow (→) in cells indicate the transition initiated by the pin of the logic input and gate driver supply pins resulting in a transition to the gate driver output state as listed.

Table 5 **Driver output state including transition behavior**

| Logic inp  | ut and gate driver    | Gate driver output |                 |            |             |                  |

|------------|-----------------------|--------------------|-----------------|------------|-------------|------------------|

| IN         | RDYC                  | FLT_N              | VCC1            | VCC2       | ON          | OFF              |

| Static gat | e driver output stat  | e: on and off      |                 |            | <u>'</u>    | ,                |

| high       | high                  | high               | high            | high       | high        | tri-state        |

| low        | high                  | high               | high            | high       | tri-state   | low              |

| Transition | n to not ready and s  | tatic not ready s  | state           |            |             |                  |

| x          | high → low            | high               | high            | high       | → tri-state | → fault off      |

| x          | low                   | high               | high            | high       | tri-state   | low              |

| Transitior | n to fault and static | fault state        |                 |            |             |                  |

| x          | high                  | high → low         | high            | high       | → tri-state | → fault off      |

| X          | high                  | low                | high            | high       | tri-state   | low              |

| Transitior | n with VCC1 power l   | oss and unsupp     | lied input side |            | ,           |                  |

| x          | х                     | х                  | high → low      | high       | → tri-state | → fault off      |

| X          | х                     | х                  | low             | high       | tri-state   | low              |

| Transition | n with VCC2 power l   | oss and unsupp     | lied output sid | e          | <b>'</b>    | ,                |

| X          | х                     | х                  | х               | high → low | → tri-state | → fault off      |

| X          | х                     | х                  | х               | low        | tri-state   | active shut down |

### **Datasheet**

### **4 Functional description**

### 4.5.1 Turn-on behavior

The 1ED34x1Mc12M family (X3 Analog) is optimized for hard switching turn-on. A turn-on command switches the ON pin internally to VCC2.

### 4.5.2 Turn-off and fault turn-off behavior

The gate driver IC supports different turn-off sequences to adapt to different applications and IGBT currents during normal switching operation and in the case of a fault.

Table 6 Turn-off sequences

| Turn-off reason | Turn-off sequence | Turn-off sequence            |                     |  |  |  |  |

|-----------------|-------------------|------------------------------|---------------------|--|--|--|--|

|                 | Hard switching    | Hard switching Soft turn-off |                     |  |  |  |  |

| normal off      | Х                 |                              |                     |  |  |  |  |

| fault turn-off  |                   | X                            | adjustable via ADJA |  |  |  |  |

The gate driver fault turn-off behavior can be configured with the ADJA pin

Once started, the fault turn-off sequence cannot be interrupted by an IN = low turn-off signal.

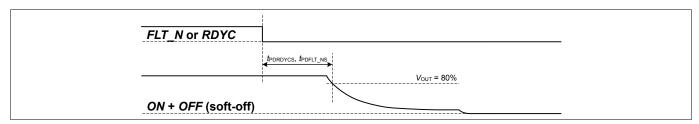

Figure 15 Fault turn-off sequence initiated by FLT\_N or RDYC

Figure 16 Fault turn-off sequence initiated by DESAT event

### 4.5.2.1 Hard switching turn-off

The gate driver IC supports hard switching turn-off during normal switching operation. Switching the IGBT gate off by turning on the discharge MOSFET in the output stage, the *OFF* pin is switched to *VEE2* pin.

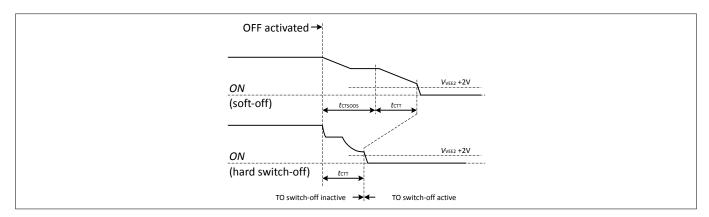

### 4.5.2.2 Soft turn-off

The soft turn-off function protects the IGBT against collector-emitter overvoltage during turn off in an overcurrent condition. It turns-off the IGBT with a reduced gate current to reduce the di/dt induced overvoltage..

The IGBT gate is connected via *OFF* to an internal current sink circuit. The discharge current is typically lower than the hard switch-off current used for normal operation. Since soft turn-off is a single event after a failure, the gate driver IC can handle the additional power dissipation internally.

Soft turn-off can be configured with the ADJA pin. The function is only active during fault turn-off.

The adjustable range depends on the current strength of the gate driver IC:

#### **Datasheet**

### **4 Functional description**

1ED3431M: 15 mA - 233 mA 1ED3461M: 29 mA - 466 mA 1ED3491M: 44 mA - 699 mA

#### Soft-off current source adjustment with ADJA 4.5.2.2.1

The ADJA pin configures the Soft-off function and current level:

- A resistor from ADJA pin to GND1 sets the Soft-off current level for the fault-off function

- Use resistors from the E96 resistor-series with 1% tolerance values to achieve accurate parameter configuration

- The gate driver IC reads the resistor value once during start-up

- Connecting ADJA to GND1 results in a Soft-off function for fault-off with a predefined value

- Connecting ADJA to VCC1 inhibits the gate driver operation and stops the start-up sequence

#### Table 7 Soft-off adjustment with ADJA

| Soft-off set up                     | default                                  | 0       | 1       | 2       | 3       | 4       | 5       | 6       | 7       |

|-------------------------------------|------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Resistance from<br>ADJA to GND1     | $< 1.05 \text{ k}\Omega$ or tied to GND1 | 1.33 kΩ | 1.58 kΩ | 1.91 kΩ | 2.26 kΩ | 2.74 kΩ | 3.32 kΩ | 4.02 kΩ | 4.87 kΩ |

| typ. I <sub>CSOFF</sub><br>1ED3431M | 146 mA                                   | 15 mA   | 29 mA   | 44 mA   | 58 mA   | 73 mA   | 87 mA   | 102 mA  | 116 mA  |

| typ. I <sub>CSOFF</sub><br>1ED3461M | 291 mA                                   | 29 mA   | 58 mA   | 87 mA   | 116 mA  | 146 mA  | 175 mA  | 204 mA  | 233 mA  |

| typ. I <sub>CSOFF</sub><br>1ED3491M | 437 mA                                   | 44 mA   | 87 mA   | 131 mA  | 175 mA  | 218 mA  | 262 mA  | 306 mA  | 349 mA  |

#### Table 7 Soft-off adjustment with ADJA

| Soft-off set up                            | 8       | 9       | 10      | 11      | 12      | 13      | 14      | 15      | stopped                         |

|--------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------------------|

| Resistance from <i>ADJA</i> to <i>GND1</i> | 5.90 kΩ | 7.15 kΩ | 8.66 kΩ | 10.7 kΩ | 13.7 kΩ | 17.4 kΩ | 23.2 kΩ | 28.0 kΩ | >45.3 kΩ or tied to <i>VCC1</i> |

| typ. I <sub>CSOFF</sub><br>1ED3431M        | 131 mA  | 146 mA  | 160 mA  | 175 mA  | 189 mA  | 204 mA  | 218 mA  | 233 mA  | inhibit gate<br>driver          |

| typ. I <sub>CSOFF</sub><br>1ED3461M        | 262 mA  | 291 mA  | 320 mA  | 349 mA  | 379 mA  | 408 mA  | 437 mA  | 466 mA  | operation                       |

| typ. I <sub>CSOFF</sub><br>1ED3491M        | 393 mA  | 437 mA  | 480 mA  | 524 mA  | 568 mA  | 612 mA  | 655 mA  | 699 mA  |                                 |

#### **Datasheet**

### 4 Functional description

#### 4.5.3 **Active shut-down**

The active shut-down feature ensures a safe IGBT off-state, if the output chip is not supplied. It protects the IGBT against a floating gate. The IGBT gate is always clamped via OFF to VEE2.

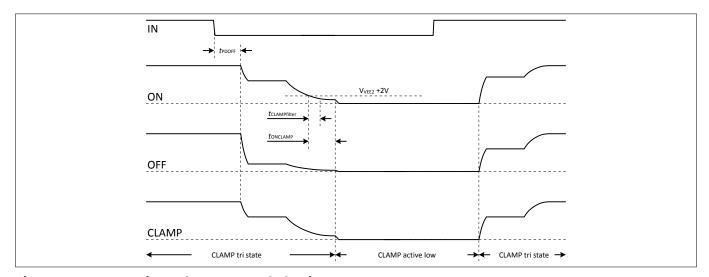

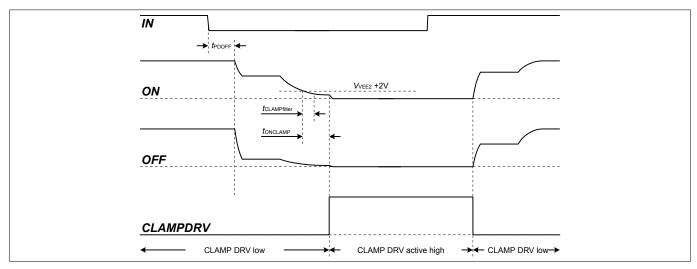

#### 4.5.4 Active Miller clamp

The 1ED34x1Mc12M family (X3 Analog) is equipped with an active Miller clamp function to protect the IGBT from parasitic turn-on in fast switching applications.

After a turn-off command the gate driver IC follows the implemented sequence:

- 1. Discharge of the IGBT gate while monitoring the voltage level at the ON pin

- 2. Detection of a voltage at the ON pin less than a level of VEE2 + 2.0 V

- 3. Filtering of the detection to avoid false CLAMP activation and not to influence regular turn-off behavior

- 4. Activating clamp function to keep IGBT gate at VEE2 level

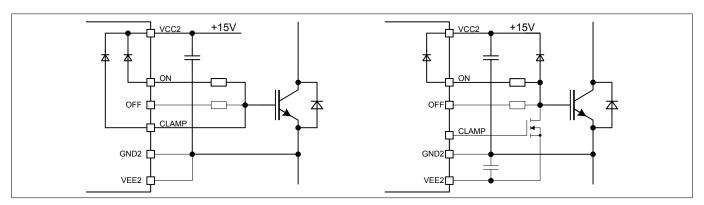

#### **CLAMP output types** 4.5.4.1

The CLAMP output stage offers two operating modes:

- direct gate clamping with an open drain output for medium clamping current, 1ED3431M variants

- pre-driver output, to clamp IGBT gate with external transistor for high clamping current, 1ED3461M and 1ED3491M variants

### **Direct gate clamping**

Direct gate clamping with an open drain output is tailored for direct clamping of IGBT gate to VEE2. The output current capability is typically 2 A. Useful IGBT current rating for direct gate clamping is a collector current of typically smaller than 100 A. Connect the CLAMP pin directly to the gate with low inductive tracks.

Application example with unipolar supply (1ED3431M) Figure 17

### **Datasheet**

### **4 Functional description**

Figure 18 Direct clamp output behavior

### **Pre-driver output**

Track inductance and clamp output resistance reduces the clamping capability for large IGBTs. In this case, select the pre-driver output product variant with an external MOSFET.

The external small signal n-channel MOSFET transistor in combination with the pre-driver output enables clamping of high gate currents. Connect the MOSFET between the *CLAMPDRV* output, *VEE2* pin, and IGBT gate. Due to the pre-driver configuration the clamp current is only limited by the external clamp MOSFET transistor. Depending on the external MOSFET a Miller current clamping up to 20 A can be reached. The clamping MOSFET has to be placed close to the IGBT gate to minimize track resistance and inductance.

Figure 19 Application example with bipolar supply and CLAMP pre-driver output (1ED3461M, 1ED3491M)

### **Datasheet**

### 4 Functional description

Figure 20 Clamp pre-driver output behavior

#### 4.5.5 Switch-off timeout until forced switch-off

The gate driver IC is equipped with a switch-off timeout monitoring feature. In case the pin monitoring comparator has not registered an off-state within the timeout time this feature activates a forced switch-off. The monitoring feature secures the IGBT switch-off in case of a connection failure between the OFF output

and the IGBT gate or a faulty gate resistor. In a forced switch-off all available output switch-off paths (OFF and CLAMP/CLAMPDRV) will be used to hard switch-off the IGBT after such an event.

Figure 21 Switch-off timeout behavior

The timing diagram shows the switch-off timeout behavior from the moment of OFF output activation until the timeout has elapsed and the CLAMP output is activated.

#### 4.6 **Short circuit clamping**

The integrated short circuit clamping diode limits the IGBT gate over voltage during a short circuit. The over voltage is typically triggered by the capacitive feedback of the Miller capacitance.

The internal diodes from ON and CLAMP to VCC2 limit the gate driver voltage to a value slightly higher than the supply voltage. These diode paths are rated for a maximum current of 0.75 A and the duration of 6 μs. Add an external Schottky diode if higher currents are expected or a tighter clamping is desired. Also use an external diode if the active Miller clamping circuit uses the pre-driver output configuration.

### **Datasheet**

### 4 Functional description

Figure 22 Short circuit clamping circuitry

### **Datasheet**

### **5 Electrical parameters**

#### **Electrical parameters** 5

#### **Absolute maximum ratings 5.1**

Note:

Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. Unless otherwise noted all voltages are given with respect to their respective GND (GND1 for pins 1 to 8, GND2 for pins 9 to 16).

Table 8 **Absolute maximum ratings**

| Parameter                                                                  | Symbol               | Values                 |                        | Unit | Note /                                                                                                                             |  |

|----------------------------------------------------------------------------|----------------------|------------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                            |                      | Min. Max.              |                        |      | Test Condition                                                                                                                     |  |

| Input to output offset voltage                                             | V <sub>OFFSET</sub>  | -                      | 2300                   | V    | $V_{\text{VEE2,max}}$ - $V_{\text{VEE2,min}}$<br>with $V_{\text{VEE2,max}} \ge V_{\text{GND1}}$<br>$\ge V_{\text{VEE2,min}}^{1/2}$ |  |

| Supply voltage input side                                                  | V <sub>VCC1</sub>    | -0.3                   | 6.5                    | V    | _                                                                                                                                  |  |

| Logic input voltage (IN)                                                   | V <sub>LogicIN</sub> | -0.3                   | 6.5                    | V    | -                                                                                                                                  |  |

| Logic input voltage (RDYC, FLT_N)                                          | $V_{\text{LogicRF}}$ | -0.3                   | 6.5                    | V    | -                                                                                                                                  |  |

| Logic input voltage (ADJA, ADJB)                                           | $V_{LogicAD}$        | -0.3                   | 6.5                    | V    | -                                                                                                                                  |  |

| Open drain logic output current (RDYC, FLT_N)                              | I <sub>LogicOC</sub> | _                      | 10                     | mA   | -                                                                                                                                  |  |

| Positive supply voltage output side                                        | V <sub>VCC2</sub>    | -0.3                   | 40                     | ٧    | -                                                                                                                                  |  |

| Negative supply voltage output side                                        | V <sub>VEE2</sub>    | -40                    | 0.3                    | V    | -                                                                                                                                  |  |

| Maximum supply voltage difference output side ( $V_{VCC2}$ - $V_{VEE2}$ )  | V <sub>max2</sub>    | -                      | 40                     | V    | -                                                                                                                                  |  |

| DESAT input voltage                                                        | $V_{DESAT}$          | -0.3                   | V <sub>VCC2</sub> +0.3 | V    | -                                                                                                                                  |  |

| CLAMP input voltage                                                        | V <sub>CLAMP</sub>   | V <sub>VEE2</sub> -0.3 | V <sub>VCC2</sub> +0.3 | V    | 3)                                                                                                                                 |  |

| Maximum <i>CLAMP</i> output current                                        | I <sub>CLAMP</sub>   | _                      | 2.4                    | А    | t < 5 μs                                                                                                                           |  |

| Gate driver output voltage (ON, OFF)                                       | V <sub>OUT</sub>     | V <sub>VEE2</sub> -0.3 | V <sub>max2</sub> +0.3 | V    | -                                                                                                                                  |  |

| Maximum <i>CLAMP</i> to <i>VCC2</i> diode IGBT short circuit clamping time | t <sub>CLP</sub>     | _                      | 6                      | μs   | $I_{\text{CLAMP/OUT}} = 0.75 \text{ A}$                                                                                            |  |

| Junction temperature                                                       | TJ                   | -40                    | 150                    | °C   | -                                                                                                                                  |  |

| Storage temperature                                                        | $T_{Stg}$            | -55                    | 150                    | °C   | -                                                                                                                                  |  |

| Power dissipation, input side                                              | $P_{D,IN}$           | _                      | 100                    | mW   | @T <sub>A</sub> = 25 °C                                                                                                            |  |

| Power dissipation, output side                                             | $P_{D,OUT}$          | _                      | 700                    | mW   | $@T_{A} = 25^{\circ}C^{4}$                                                                                                         |  |

| ESD capability: Human body model                                           | V <sub>ESDHBM</sub>  | _                      | 2                      | kV   | 5)                                                                                                                                 |  |

| ESD capability: Charged device model                                       | $V_{ESDCDM}$         | _                      | 500                    | V    | 6)                                                                                                                                 |  |

- for functional operation only 1)

- See also Chapter 6 on page 41 2)

- 3) May be exceeded during short circuit clamping.

- Derating the power above 65°C with 8 mW/°C

#### **Datasheet**

# **(infineon**

### **5 Electrical parameters**

- 5) According to ANSI/ESDA/JEDEC-JS-001-2017 (discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor).

- 6) According to ANSI/ESDA/JEDEC-JS-002-2014 (TC = test condition in volt)

### 5.2 Thermal parameters

Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

Figure 23 Reference layout for thermal data (Two layer PCB; copper thickness 35 μm; left: top layer; right: bottom layer)

The PCB layout represents the reference layout used for the thermal characterization. Pins 1 and 8 (*GND1*) and pins 9 and 16 (*VEE2*) require ground plane connections for achieving maximum power dissipation. The 1ED34x1Mc12M family (X3 Analog) is conceived to dissipate most of the heat generated through these pins.

Table 9 Thermal parameters

| Parameter                                                     | Symbol                | Value | Unit | Note / Test Condition                                                                                          |

|---------------------------------------------------------------|-----------------------|-------|------|----------------------------------------------------------------------------------------------------------------|

| Thermal resistance junction to ambient                        | R <sub>THJA,OUT</sub> | 122   | K/W  | @ $T_A = 65^{\circ}\text{C}$ , $P_{D, OUT} = 400 \text{ mW}$ , $P_{D, IN} = 50 \text{ mW}$ , 4 layer test PCB, |

| Characterization parameter junction to package top input side | $\Psi_{Jtop}$         | 8     | K/W  | PG-DSO-16                                                                                                      |

### 5.3 Operating parameters

Note:

Within the operating range the IC operates as described in the functional description. Unless otherwise noted all voltages are given with respect to their respective GND (GND1 for pins 1 to 8, GND2 for pins 9 to 16).

Table 10 Operating parameters

| Parameter <sup>1)</sup>                | Symbol            | Values |      | Unit | Note /         |  |

|----------------------------------------|-------------------|--------|------|------|----------------|--|

|                                        |                   | Min.   | Max. |      | Test Condition |  |

| Supply voltage input side              | V <sub>VCC1</sub> | 3.0    | 5.5  | V    | _              |  |

| Logic input voltages (IN, RDYC, FLT_N) | $V_{LogicIN}$     | -0.3   | 5.5  | V    | -              |  |

| Positive supply voltage output side    | V <sub>VCC2</sub> | 13     | 25   | V    | -              |  |

| Negative supply voltage output side    | V <sub>VEE2</sub> | -25    | 0    | V    | -              |  |

(table continues...)

### **Datasheet**

# **infineon**

### **5 Electrical parameters**

Table 10 (continued) Operating parameters

| Parameter <sup>1)</sup>                                       | Symbol            | Values |      | Unit | Note /                            |  |

|---------------------------------------------------------------|-------------------|--------|------|------|-----------------------------------|--|

|                                                               |                   | Min.   | Max. |      | Test Condition                    |  |

| Supply voltage difference output side $(V_{VCC2} - V_{VEE2})$ | V <sub>max2</sub> | 13     | 35   | V    | -                                 |  |

| Ambient temperature                                           | T <sub>A</sub>    | -40    | 125  | °C   | 2)                                |  |

| Switching frequency                                           | $f_{SW}$          | 0      | 250  | kHz  | max P <sub>D</sub> applies        |  |

| Common mode transient immunity                                | CMTI              | 0      | 200  | V/ns | V <sub>OFFSET,test</sub> = 1500 V |  |

<sup>1)</sup> Parameter is not subject to production test - verified by design/characterization

<sup>2)</sup>  $T_J$  has to be below over temperature protection temperature  $T_{OTPOFF}$

### **Datasheet**

### **5 Electrical parameters**

#### **Electrical characteristics 5.4**

Note:

The electrical characteristics include the spread of values in supply voltages, load, and junction temperatures within the operating parameters unless specified otherwise. Typical values represent the median values at  $T_A$  = 25°C. Unless otherwise noted all voltages are given with respect to their respective GND (GND1 for pins 1 to 8, GND2 for pins 9 to 16).

#### **Voltage supply** 5.4.1

Table 11 **Voltage supply**

| Parameter                                                                | Symbol                |      | Values | Unit | Note or Test |                                                                                                                          |  |

|--------------------------------------------------------------------------|-----------------------|------|--------|------|--------------|--------------------------------------------------------------------------------------------------------------------------|--|

|                                                                          |                       | Min. | Тур.   | Max. |              | Condition                                                                                                                |  |

| VCC1 UVLO threshold                                                      | V <sub>UVLO1H</sub>   | _    | 2.95   | 3.05 | V            | -                                                                                                                        |  |

|                                                                          | V <sub>UVLO1L</sub>   | 2.6  | 2.8    | _    | V            | -                                                                                                                        |  |

| VCC1 UVLO hysteresis (V <sub>UVLO1H</sub> - V <sub>UVLO1L</sub> )        | V <sub>HYS1</sub>     | 0.1  | 0.14   | -    | V            | -                                                                                                                        |  |

| VCC1 quiescent current                                                   | I <sub>Q1</sub>       | -    | 2.4    | 4.0  | mA           | $V_{VCC1} = 3.3 \text{ V}, IN =$ High, $RDYC = \text{High},$ $FLT_N = \text{High}$                                       |  |

| VCC1 operating current                                                   | I <sub>O1</sub>       | -    | 2.4    | 4.0  | mA           | V <sub>VCC1</sub> = 3.3 V, IN =<br>16 kHz, 50%, RDYC =<br>High, FLT_N = High                                             |  |

| VCC2 UVLO threshold                                                      | V <sub>UVLO2H,0</sub> | _    | 12.0   | 12.6 | V            |                                                                                                                          |  |

|                                                                          | V <sub>UVLO2L,0</sub> | 10.4 | 11.0   | _    | V            |                                                                                                                          |  |

| VCC2 UVLO hysteresis<br>(V <sub>UVLO2H,0</sub> - V <sub>UVLO2L,0</sub> ) | V <sub>HYS2,0</sub>   | 0.75 | 1.0    | -    | V            |                                                                                                                          |  |

| VEE2 not connected detection threshold                                   | V <sub>VEE2,NC</sub>  | -    | 0.5    | -    | V            | V <sub>VEE2</sub> - V <sub>GND2</sub>                                                                                    |  |

| VCC2 quiescent current                                                   | $I_{\mathrm{Q2}}$     | -    | 3.9    | 5    | mA           | $V_{VCC2} = 15 \text{ V}, V_{VEE2}$<br>= -8 V, <i>OUT</i> = High,<br><i>DESAT</i> = Low                                  |  |

| VCC2 operating current                                                   | I <sub>02</sub>       | -    | 3.9    | 5    | mA           | $V_{VCC2} = 15 \text{ V}, V_{VEE2} = -8 \text{ V}, OUT = 16 \text{ kHz}, 50\%, DESAT = Low, } C_{LOAD} = 100 \text{ pF}$ |  |

### **Datasheet**

**5 Electrical parameters**

#### **Logic input and output** 5.4.2

Table 12 **Logic input and output**

| Parameter                                    | Symbol Values                                 |      |      | Unit | Note or Test |                          |

|----------------------------------------------|-----------------------------------------------|------|------|------|--------------|--------------------------|

|                                              |                                               | Min. | Тур. | Max. |              | Condition                |

| Logic low input voltage (IN, RDYC, FLT_N)    | V <sub>LogicINL</sub>                         | -    | -    | 30   | %            | of V <sub>VCC1</sub>     |

| Logic high input voltage (IN, RDYC, FLT_N)   | V <sub>LogicINH</sub>                         | 70   | -    | -    | %            | of V <sub>VCC1</sub>     |

| Logic low output voltage (RDYC, FLT_N)       | V <sub>RDYC5</sub> ,<br>V <sub>FLT_N5</sub>   | _    | -    | 300  | mV           | I <sub>SINK</sub> = 5 mA |

| Logic input pull down resistor (IN)          | R <sub>INPD</sub>                             | 33   | 40   | 47   | kΩ           | -                        |

| Logic input pull down resistor (RDYC, FLT_N) | R <sub>RDYCPD</sub> ,<br>R <sub>FLT_NPD</sub> | 0.8  | 1.0  | 1.2  | ΜΩ           | -                        |

#### **Analog input** 5.4.3

Resistor values outside of the 1% tolerance range results in the gate driver IC selecting either the lower or higher step for the corresponding function.

**Analog input** Table 13

| Parameter <sup>1)</sup>               | Symbol              |      | Values |      | Unit | Note or Test                          |  |

|---------------------------------------|---------------------|------|--------|------|------|---------------------------------------|--|

|                                       |                     | Min. | Тур.   | Max. |      | Condition                             |  |

| Analog input resistor ( <i>ADJA</i> , | R <sub>ADJx0</sub>  | _    | 1.33   | _    | kΩ   | all resistor values are               |  |

| ADJB)                                 | R <sub>ADJx1</sub>  | _    | 1.58   | -    |      | from the E96-series with 1% tolerance |  |

|                                       | R <sub>ADJx2</sub>  | _    | 1.91   | -    |      | with 170 tolerance                    |  |

|                                       | R <sub>ADJx3</sub>  | _    | 2.26   | _    |      |                                       |  |

|                                       | R <sub>ADJx4</sub>  | _    | 2.74   | -    |      |                                       |  |

|                                       | R <sub>ADJx5</sub>  | _    | 3.32   | _    |      |                                       |  |

|                                       | R <sub>ADJx6</sub>  | _    | 4.02   | -    |      |                                       |  |

|                                       | R <sub>ADJx7</sub>  | _    | 4.87   | _    |      |                                       |  |

|                                       | R <sub>ADJx8</sub>  | _    | 5.90   | _    |      |                                       |  |

|                                       | R <sub>ADJx9</sub>  | _    | 7.15   | -    |      |                                       |  |

|                                       | R <sub>ADJx10</sub> | _    | 8.66   | _    |      |                                       |  |

|                                       | R <sub>ADJx11</sub> | _    | 10.7   | _    |      |                                       |  |

|                                       | R <sub>ADJx12</sub> | _    | 13.7   | _    |      |                                       |  |

|                                       | R <sub>ADJx13</sub> | _    | 17.4   | _    |      |                                       |  |

|                                       | R <sub>ADJx14</sub> | _    | 23.2   | _    |      |                                       |  |

|                                       | R <sub>ADJx15</sub> | _    | 28.0   | _    |      |                                       |  |

# **EiceDRIVER**<sup>™</sup> **1ED34x1Mc12M Enhanced Datasheet**

# infineon

### **5 Electrical parameters**

1) Parameter is not subject to production test - verified by design/characterization

### **Datasheet**

### **5 Electrical parameters**

### 5.4.4 Gate driver

Note: High and low level output currents are absolute values without an information of current direction.

Table 14 Gate driver

| Parameter                                       | Symbol                           |      | Values                   |                          | Unit | Note or Test                                     |  |

|-------------------------------------------------|----------------------------------|------|--------------------------|--------------------------|------|--------------------------------------------------|--|

|                                                 |                                  | Min. | Тур.                     | Max.                     |      | Condition                                        |  |

| High level output<br>voltage                    | V <sub>ON0</sub>                 | -    | V <sub>VCC2</sub> + 0.87 | V <sub>VCC2</sub> + 1.01 | V    | $I_{ON} = 500 \text{ mA}^{1}$                    |  |

| High level output peak<br>current 1ED3431M      | I <sub>ON</sub>                  | 2.6  | 3.8                      | -                        | A    | $^{2)3)}C_{LOAD} = 33 \text{ nF}$                |  |

| High level output on resistance 1ED3431M        | R <sub>DSON,H</sub>              | 0.51 | 1.12                     | 2.24                     | Ω    | $I_{ON} = 67 \text{ mA}^{3)}$                    |  |

| Low level output peak<br>current 1ED3431M       | I <sub>OFF</sub>                 | 2.0  | 2.5                      | -                        | A    | <sup>2) 4)</sup> C <sub>LOAD</sub> = 33 nF       |  |

| Low level ouput on resistance 1ED3431M          | $R_{DSON,L}$                     | 0.31 | 0.82                     | 1.64                     | Ω    | I <sub>OFF</sub> = 67 mA <sup>4)</sup>           |  |

| High level output peak<br>current 1ED3461M      | I <sub>ON</sub>                  | 5.2  | 7.5                      | -                        | A    | $^{2) \ 3)} C_{LOAD} = 68 \text{ nF}$            |  |

| High level output on resistance 1ED3461M        | R <sub>DSON,H</sub>              | 0.26 | 0.56                     | 1.13                     | Ω    | I <sub>ON</sub> = 133 mA <sup>3)</sup>           |  |

| Low level output peak<br>current 1ED3461M       | I <sub>OFF</sub>                 | 4.0  | 5.0                      | -                        | A    | $^{2)} C_{LOAD} = 68 \text{ nF}$                 |  |

| Low level ouput on resistance 1ED3461M          | R <sub>DSON,L</sub>              | 0.16 | 0.41                     | 0.83                     | Ω    | I <sub>OFF</sub> = 133 mA <sup>4)</sup>          |  |

| High Level output peak current 1ED3491M         | I <sub>ON</sub>                  | 7.9  | 11                       | -                        | А    | $^{2)3)}C_{LOAD} = 100 \text{ nF}$               |  |

| High level output on resistance 1ED3491M        | R <sub>DSON,H</sub>              | 0.17 | 0.38                     | 0.75                     | Ω    | $I_{ON} = 200 \text{ mA}^{3}$                    |  |

| Low Level output peak<br>current 1ED3491M       | I <sub>OFF</sub>                 | 6.0  | 7.5                      | -                        | A    | <sup>2) 4)</sup> C <sub>LOAD</sub> = 100 nF      |  |

| Low level ouput on resistance 1ED3491M          | $R_{DSON,L}$                     | 0.11 | 0.28                     | 0.55                     | Ω    | $I_{OFF} = 200 \text{ mA}^{4}$                   |  |

| Active Shut Down<br>Voltage <i>OFF</i> 1ED3431M | V <sub>ACTSD</sub> <sup>5)</sup> | -    | -                        | V <sub>VEE2</sub> +2.4   | V    | I <sub>OUT</sub> = 67 mA,V <sub>VCC2</sub> open  |  |

| Active Shut Down<br>Voltage <i>OFF</i> 1ED3461M | V <sub>ACTSD</sub> <sup>5)</sup> | -    | -                        | V <sub>VEE2</sub> +2.4   | V    | / <sub>OUT</sub> = 133 mA,V <sub>VCC2</sub> open |  |