Home / Design resources

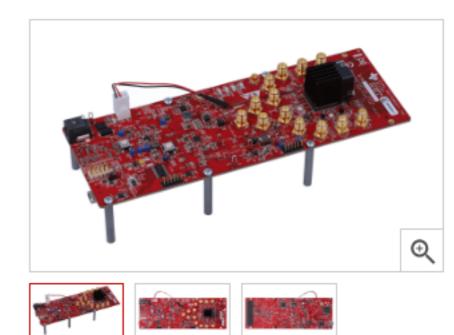

### AFE7900EVM

AFE7900 evaluation module for four-transmit, six-receive, 5-MHz to 7400-MHz, RF-sampling AFE

Order now

Overview

Order & start development

Technical documentation

Related design resources

Support & training

#### Overview

Description & features

What's included Supported products

The AFE7900 evaluation module (EVM) is an RF-sampling transceiver platform that can be configured to support up to four-transmit, four-receive, and two-feedback (4T4R+2FB) channels simultaneously.

The module evaluates the AFE7900, which is a quad-channel RF-sampling analog front end (AFE) with

14-bit, 12-GSPS digital-to-analog converters (DACs), 14-bit, 3-GSPS analog-to-digital converters (ADCs), and an on-chip integrated phase-locked loop/voltage-controlled oscillator (PLL/VCO) for high-frequency clock generation for DACs and ADCs. AFE7900EVM has options to use dual digital upconverters and downconverters in each channel to

simultaneously synthesize and digitize multiple wideband signals with high dynamic range. On-chip integrated digital step attenuator (DSA) for the receiver channels and DSA functionality for the transmitter channels is supported. Eight JESD204B/C-compatible serializer/deserializer (SerDes) transceivers running up to 29.5 Gbps can be used for providing inputs and outputs to/from the AFE7900 through the onboard field-programmable gate array (FPGA) mezzanine card (FMC) connector.

AFE7900EVM includes the LMK04828 clock generator that provides a reference signal to the AFE on-chip PLL and generates the required SYSREF signals for the JESD204B/C protocol. Also included is the option for providing an ultra-low-phase noise external clocking solution.

View all 💙

## Important note

AFE7900EVM user's guide, design files, software and other support information are available. Request now

## Order & start development

EVALUATION BOARD

AFE7900EVM — AFE7900 evaluation module for four-transmit, sixreceive, 5-MHz to 7400-MHz, RF-sampling AFE

Buy from a distributor

TI's Standard Terms and Conditions for Evaluation Items apply.

## Technical documentation

## Related design resources

## Hardware development

EVALUATION BOARD

TSW14J57EVM — Data capture/pattern generator: data converter EVM with 16 JESD204B lanes from 1.6-15Gbps

## Support & training

## TI E2E™ forums with technical support from TI engineers

#### AFE7900EVM: Regarding AFE7900EVM specifications Part Number: AFE7900EVM Hello support team, we are planning to use AFE7900EVM with ZCU102 xilinx evaluation platform board. For AFE7900EVM, I have

below list of queries, request you to please gui...

## AFE7950EVM: configuration

Part Number: AFE7950EVM Hello, We are using the eval boards of both AFE7900 and AFE7950 (EVMs) connected to a ZCU102. Background: We have a design that works on the AFE7900EVM (specifically c...

## AFE7900EVM: Regarding the AFE7900EVM configuration using ZCU102 eval board using JESD IP core

Part Number: AFE7900EVM Hello support team, We are planning to use AFE7900EVM with ZCU102 Evalutaion board using JESD IP core and interfacing. I have gone through the details and I have below quer...

#### AFE7900EVM: Unknown registers on AFE7900 chip

Part Number: AFE7900EVM Hello, I have been working with an AFE7900EVM board and a zyng FPGA. I have managed to get the combination working using the latte tool to configure the AFE7900EVM module, ...

# AFE7900EVM: AFE7900EVM and TSW14J57EVM pin-mapping over FMC

Part Number: AFE7900EVM I am attempting to map my TSW14J57EVM FPGA design IO via the FMC to an AFE7900EVM. Even though I have both schematics and provided documentation, it is unclear as to how I ...